# BRNO UNIVERSITY OF TECHNOLOGY

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

DEPARTMENT OF COMPUTER GRAPHICS AND MULTIMEDIA ÚSTAV POČÍTAČOVÉ GRAFIKY A MULTIMÉDIÍ

# HARDWARE ACCELERATION OF OBJECT DETECTION IN IMAGES

HARDWAROVÁ AKCELERACE DETEKCE OBJEKTŮ V OBRAZE

PHD THESIS DISERTAČNÍ PRÁCE

AUTHOR AUTOR PRÁCE **Ing. PETR MUSIL**

SUPERVISOR ŠKOLITEL Prof. Dr. Ing. PAVEL ZEMČÍK

**BRNO 2020**

### Abstract

Nowadays, an increasing number of cameras and surveillance systems can be observed. The amount of information that these devices produce is enormous, and it is not in human power to process it all, therefore using computing power is needed. Modern computer vision algorithms, especially object detection, already achieve excellent results. One of the disadvantages of current vision algorithms is high computational complexity. Therefore, it is desired to implement these algorithms into a suitable device with better performance to power ratio. FPGA represents a reliable option due to its parallel and power-efficient computing. This dissertation aims to propose methods for optimising the object detector in an image running on an FPGA. These detectors use boosted soft cascades of classifiers with local image feature like weak classifiers. The proposed detectors use sequential evaluation of weak classifiers. More positions in the image are evaluated in parallel to increase the detection performance. Also, a new approach for multiscale object detection is proposed; its advantage is no need for external memory. The new detectors were experimentally verified on the tasks of detecting faces and license plates. The results outperform the current stateof-the-art, allow to create object detectors with higher detection performance, better power to resources ratio and better detection accuracy.

### Abstrakt

V dnešní době je patrný nárůst počtu kamer a dohledových systémů ve veřejném prostoru. Množství informací které tato zařízení produkují je enormní a není v lidských silách je všechny vyhodnotit a interpretovat. Použití výpočetních technologií je nezbytné. Moderní algoritmy počítačového vidění již dosahují skvělých výsledků, jejich širšímu použití v praxi zatím brání nízký výkon zařízení a vysoké požadavky na výpočetní zdroje a energii. Jednou z možností je využití vysokého paraelního výkonu FPGA pro efektivní zpracování těchto algoritmů. Cílem této disertační práce je představit navržené metody optimalizace detektoru objektů v obraze běžících na FPGA. Tyto detektory využívají boostovatelné soft kaskády klasifikátorů spolu s lokálními obrazovými příznaky, které slouží jako slabé klasifikátory. Navržené postupy využívají sekvenční vyhodnocení slabých klasifikátoru. Pro zvýšení výkonu detekce je vyhodnocováno současně více pozic v obraze. Je navržen nový přístup pro detekci objektů různé velikosti nevyžadující externí paměť. Vytvořené detektory byly experimentálně ověřeny na úlohách detekce obličejů a poznávacích značek automobilů. Dosažená výsledky překonávají současný stav poznání, umožňují vytvořit detektory objektů s vyšším detekčním výkonem, lepším poměrem výkonu a spotřebovaných zdrojů FPGA a s lepší přesností detekce.

## Keywords

Object Detection, AdaBoost, WaldBoost, Acceleration, FPGA

### Klíčová slova

Detekce objektů, AdaBoost, WaldBoost, Akcelerace, FPGA

## Reference

MUSIL, Petr. Hardware acceleration of object detection in images. Brno, 2020. PhD thesis. Brno University of Technology, Faculty of Information Technology. Supervisor Prof. Dr. Ing. Pavel Zemčík

# Hardware acceleration of object detection in images

### Declaration

Hereby I declare that this dissertation thesis is my original work and that I have written it under lead of Prof. Dr. Ing. Pavel Zemčík. All the relevant information sources, which were used during preparation of this thesis, are properly cited and included in the list of references.

Petr Musil August 30, 2020

### Acknowledgements

I would like to acknowledge and thank the people who have supported me, not only during my doctoral studies. First of all, to Pavel Zemčík, my supervisor, for his guidance, knowledge and sustained support. To my colleagues and friends for their personal and professional support, especially to Michal Hradiš, Roman Juránek and Martin Musil. I would also like to thank my family for their patience and my girlfriend, Karolina for language corrections, and her support and love.

# Contents

| 1 | Introduction                                                                                                                                                                                                                   | 4                                                                                  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 2 | 2.4 SVM based hardware detectors                                                                                                                                                                                               | 6<br>7<br>9<br>10<br>11<br>12<br>14                                                |

| 3 | Goals and Contributions                                                                                                                                                                                                        | <b>15</b><br>16<br>18<br>19<br>20                                                  |

| 4 | High Performance Architecture for Object Detection in Streamed Video4.1Introduction                                                                                                                                            | <ol> <li>22</li> <li>23</li> <li>24</li> <li>26</li> <li>30</li> <li>34</li> </ol> |

| 5 | Cascaded Stripe Memory Engines for Multi-Scale Object Detection inFPGA5.1Introduction5.2Detector model5.3Related work5.4Design choices5.5Classifier model5.6The architecture5.7Results and Evaluation5.8Discusion5.9Conclusion | <b>35</b><br>36<br>38<br>40<br>41<br>43<br>46<br>51<br>57<br>57                    |

| 6 | Unconstrained License Plate Detection in FPGA6.1 Introduction6.2 License plate localization                                                                                                                                    | <b>58</b><br>59<br>61                                                              |

|    | <ul> <li>6.3 FPGA architecture</li></ul> | 65        |

|----|------------------------------------------|-----------|

| 7  | Applications and Future Work             | 68        |

| 8  | Conclusion                               | 72        |

| Bi | bliography                               | <b>74</b> |

# Glossary

- **ACF** Aggregated Channel Features.

- BRAM Block Random Access Memory element on FPGA.

**CLK** FPGA clock speed in MHz.

**CNN** Convolution Natural Network.

**DSP** Digital Signal Processing element on FPGA.

**FF** Flip Flop register on FPGA.

FPGA Field-Programmable Gate Array.

${\bf FPS}\,$  Frame Peer Second.

**HSG** Histogram of Significant Gradients.

LBP Local Binary Patterns.

**LRD** Local Rank Difference.

LUT Look Up Table on FPGA.

${\bf SVM}$  Support Vector Machine.

# Chapter 1

# Introduction

Nowadays, an increasing number of cameras and surveillance systems can be observed. We can see cameras at toll gates, security cameras in buildings or police surveillance systems. The amount of information that these devices produce is enormous, and it is not in human power to process and interpret it all. The only option is to use computing power to analyse the huge number of videos and frame sequences. Modern computer vision algorithms have passed the point, where it is reasonable to start implementing them widely. Algorithms for object detection and recognition, for example of human faces, pedestrians, cars, or traffic signs already outperform human. In general, one of the disadvantages of advanced vision algorithms is high computational complexity. For this reason, it is necessary to use powerful computer systems with high energy consumption and cost. Also, it would be convenient to process most data locally without the need for remote servers, so-called edge computing.

One solution can be the hardware acceleration of computer vision algorithms on FPGA or ASIC chips. The aim is to create low-cost, low-power devices for real-time video processing. The deployment of algorithms to FPGA and ASIC circuits is specific and differs greatly from deployment to conventional computing systems. Usually, a direct implementation of computer vision algorithms without their modification is inefficient, slow and resource-intensive. The acceleration of computer vision algorithms in hardware has long been the goal of many scientific works. This topic is attractive due to its potential practical application, and a combination of different research fields: image processing and hardware acceleration.

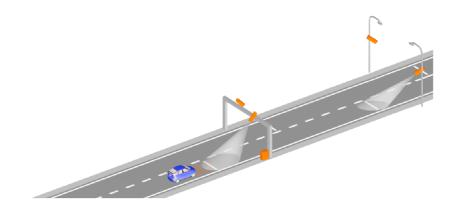

This thesis presents my contributions to the state-of-the-art in the topic of visual object detection in FPGA. Specifically, the work is focused on fast and powerful object detectors with low demands on resources. Such detectors could be applied mainly in transport, industry or security. One of the applications of the detector will be demonstrated on the task of detecting license plates for parking control in residential zones. The benefits will be shown in comparison to current technologies.

The contribution itself is in proposing methods for optimizing object detection on FP-GAs. The main focus is on detectors using boosted soft cascades of classifiers with local image features as weak classifiers. Sequential evaluation of weak classifiers has been upgraded with parallelization by evaluation of several independent image positions simultaneously. Also, a new approach for multi-scale object detection has been proposed; its advantage is no need for external memory. Using these methods to create effective detector verifies the hypothesis: that it is possible to design an object detector based on soft cascade deployed in programmable hardware with resulting precision comparable to the state-of-the-art, with real-time performance, with lower power consumption and less computing resource demands comparing to existing ones.

The thesis consists of a commented set of articles. Next chapter introduces related state-of-the-art. Chapter 3 presents the main contribution of the work. Chapters 4,5 and 6 are core of my dissertation thesis, representing commented re-formatted copies of my papers [1, 2, 3]. The chapter 7 describes the application of the detector into practice, using it in several research projects and outlines future work. The work finishes with a conclusion.

# Chapter 2

# Object detection in images using embedded devices

This part of the dissertation thesis provides an overview of the state of the art of object detection on hardware platforms. The focus is mainly on general object detection using boosted classifiers and on a summary of other authors' work on the topic of detection in hardware. This chapter is included to introduce the reader into the topic because the papers I published did not offer enough space for more detailed information. Recent scientific contributions on the topic are also described, as our articles were published through the years 2013-2020, and the state-of-the-art has evolved since then.

Object detection in image is one of the fundamental algorithms of computer vision. The definition of object varies and it is largely application dependent. It is often defined by a set of annotated example images [4]. Object detection in image is a popular topic in the scientific community with wide practical scope. Over the years, many approaches to object detection have been proposed. From the first methods based on hand-designed ad-hoc detectors [5, 6] or template matching [7] trough part-based methods [8, 9, 10] the field progressed to appearance-based detectors [11, 12, 13, 14, 15, 16, 17, 18].

The appearance-based detectors use statistical analysis and supervised machine learning methods to learn distinctive object characteristics. The first of these methods used Support Vector Machines (SVM)[19] in combination with Haar's features[20] or Gabor filters[21]. SVM is a mathematical method for searching best separating hyperplane in a feature space. It produces classifiers with a simple structure suitable for parallel implementation. Modern approaches use SVM and Histograms of Oriented Gradient(HOG) for detection of pedestrians[22, 23, 24, 25, 26], cars[27], traffic sign[28], etc. The most successful detection methods designed for devices with limited computational resources are based on sliding windows and boosted classifiers [11, 12, 13, 14, 29, 30, 31, 32, 33, 34, 35]. These methods enable creating powerful and accurate universal detectors of relatively rigid and visually distinct objects such as faces [11, 36, 33, 30], pedestrians[14], traffic signs[37], licence plates[38, 39], etc. Another large class of appearance-based detectors builds on deep learning, specifically on Convolutions Neural Networks (CNN) [40]. These methods represent state-of-the-art in terms of detection accuracy and variability of objects they can handle [15, 16, 17, 41].

Over the years, many hardware implementations of various object detectors have been proposed. The implementations typically belong to following categories of detection methods:

- Ada-Boost based detectors cascades of boosted classifiers [11] with Haar image features [29, 30, 31, 32, 33, 34, 35] or soft-cascades [12] typically with LBP/LRD features [42, 43, 44].

- SVM [19] typically in combination with HOG [23, 24, 25, 27, 28].

- Boosted decision tree with Aggregate channel feature(ACF) detector [45, 46].

- CNN in various forms [47, 48, 49, 50, 51].

- Other methods implementing detection using background subtraction [52], keypoints [53] or ad-hoc detection algorithms [54].

#### 2.1 Object detection using boosted classifiers

Viola and Jones [11] in 2001 presented the first practical general object detector. It it uses an efficient cascade of boosted classifiers with Haar-like image features (weak classifiers) in a sliding window fashion to gradually classify overlapping image windows into background and object classes. Viola and Jones used the learning algorithm Adaptive Boosting (AdaBoost) [55] which selects and sorts weak classifiers each based on a single computationally simple image feature by their importance. Haar-like features encode local image freqency and can be efficiently calculated using integral image in constant time. The main advantage of the detector is the use of the attentional cascade of classifiers, which is a mechanism that decides very quickly on simple background areas and spends more time at ambiguous positions. This ultimately reduces the computational complexity of detection by several orders of magnitude. The combination of efficient features, powerfull classifiers and the cascade structure resulted in a first real-time detector of the frontal face (running at 15 frames per second on 384x288 pixel images at the time of publication). The Viola-Jones detector had gained immense popularity and was the basis to a significant number of modifications [12, 13, 56, 57, 14].

The most effective modifications of the attentional cascade of Viola-Jones is to let the individual cascade stages to share information and to increase the number of rejection decisions. For example, the soft-cascade of Bourdev and Brand [12] produces one long classifier and thresholds for rejection decisions after each weak classifier. The rejections in the Viola and Jones detector occur after the end of each stage, one of which usually contains tens of weak classifiers. The combination of more frequent rejection decisions and a single continuous classifier results in much faster detectors while maintaining the same accuracy. However, the threshold selection method proposed by Bourdev and Brand is far from optimal.

Šochman and Matas [13] proposed optimal rejection threshold selection scheme for softcascades inspired by Wald's Sequential Probability Ratio Test (SPRT). They used SPRT to generate an optimal sequential decision strategy on weak classifiers selected by AdaBoost which can additionally include also positive acceptance thresholds. The resulting WaldBoost algorithm can be considered the state-of-the-art in the field of boosted detectors.

Boosted classifier used for object detection can be build on various types of week classifiers and image features. The main requirements on weak classifiers are high discriminative power and low computational complexity. Viola and Jones [11] and follow-up works [12, 29, 30, 31, 32, 33] utilised Haar-like image features. Haar features are wavelet features that extract local frequency information. They originated from the theoretical

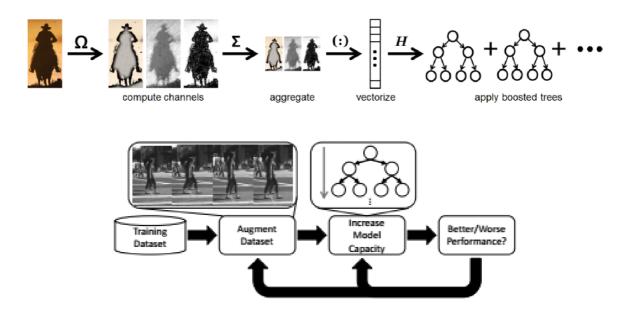

Figure 2.1: (Top) ACF detector principle [57]. (Bottom) The principle of boosted cascade training optimization as suggested by Bar et al. [14]

work by A. Haar [58]. Haar wavelets respond to oriented edges and bars in images and Haar features can be calculated by convolution of an input image with the Haar wavelets. The advantage of Haar features is constant time calculation from an integral representation of an image.

Very popular features for object detection [42, 43, 59] are local binary patterns (LBP) [60] which capture local shape of image intensity. They use sampling of the local neighbourhood to construct a binary code from intensity values which is invariant to monotonous changes in image intensity and can be calculated in constant time. Similar features named Local Rank Differences (LRD) [61] and Local Rank Patterns (LRP) [62] were proposed to reduce memory requirements for weak classifier coefficient and for effective implementation on GPUs [63, 59] and FPGA [64].

Dollar et al. [56] suggested to combine more types of image features as precomputed image channels to improve detection accuracy (named aggregated channel features - ACF). They use a combination of gradient histograms (HOG), colour (including grayscale, RGB, HSV, and LUV), and gradient magnitude. For better performance, the features are precalculated to separate image channels and optionally aggregated to lower resolution. Dollar et al. also proposed simple decision trees as weak classifiers in the soft-cascade. ACF was further extended by an effective multi-scale detection using Fast Feature Pyramids [57] which calculates feature channels only for a sparse set of image scales which are used to efficiently approximate the rest of the scales. This saves computing power and possibly memory of hardware platforms.

Ohn-Bar and Trivedi [14] focused on the limitations of the boosted classifiers and described the relationship between the capacity of boosting classifier, dataset size, and dataset properties. They introduced knowledge from neural network training as data augmentation into the training of boosting classifiers. Besides, they inspected the effect of increasing model capacity on accuracy. They demonstrated that combining these approaches improves the accuracy of detection. The resulting detectors (ACF+ and LDCF+) provide the best-known accuracy among non-CNN techniques while operating in real-time.

#### 2.2 Ada-Boost based hardware detectors

Since Viola and Jones published their real-time detector [11], there has been much effort to implement the detector in hardware, typically in FPGAs [29, 30, 31, 32, 33, 34, 35, 42, 43, 44, 65].

One of the first FPGA implementations was proposed by Lai et al. [29]. Their parallel implementation of the original Viola and Jones detector achieved a speeds up to 143 frames per second (FPS) at 640x480 resolution and a single scale. Due to high demands on FPGA resources, they had to limit the cascade to only the first three stages (52 features), which led to low detection accuracy and the other stages had to be computed on CPU. Cho et al. [30] proposed a similar approach with several parallel blocks computing classifiers at different locations to accelerate the processing speed. Their implementation supports multi-scale detection at the cost of storing the whole image to FPGA memory. This leads to high memory demands and limited image resolution. These implementations of the original detector used Haar feature with an integral image which is not really suitable for FPGAs for several reasons. The integral image increases memory requirements — each pixel requires a higher bit depth depending on the Haar feature size (even 20 and more bits per pixel are need). However, the calculation of the features without the integral image directly from the image data is very computationally demanding and not possible in constant time. The integral image allows calculation in constant time and the maximum number of memory reads required is 9 from different parts of the detection window depending on the specific Haar feature shape and position. Such memory reads can not be aligned and result in inefficient memory access. Reading these values from BRAM is restricted by the number of memory ports and the parallelization is limited by the non-uniform memory access pattern. Typicaly, the memory access limitation is mitigated by scaling the image and implementing the sliding window as a register array with FIFO line buffers (stored in BRAM) to enable fast reading of integral image in a single clock cycle. It allows for parallel access to all pixels in the window using a multiplexer network. The size of this multiplexer network increases linearly with the size of the detection window and with the number of pixels accessed in parallel. This causes enormous demands on logic resources and limits the implementations to using only small and fixed window sizes.

Huang and Vahid [34] partially solved the multiplexer network size problem by limiting feature positions. They developed a method with automatically generates a minimal multiplexer network for a specific detector. Brousseau and Rose [35] reduced the multiplexer network size by preloading adjacent pixels, allowing parallel evaluation of classifiers in adjacent scanning windows. However, this requires the use of a very complex evaluation control mechanism which is necessary to rearrange execution of classifiers after some are terminated in order to maintain high utilization of the parallel memory accesses.

Other works used local image patterns instead of Haar features. Jin et al. [42] proposed a design of a fully pipelined monolithic Ada-boost classifier with LBP which executes a all features for one detection window position in parallel per one clock cycle. This results in a high-speed detector; however, the demands on logic and register resources are enormous. Kadlcek and Fučik [43] proposed similar fully pipelined architecture with LBP features utilizing unique and unusual LBP shapes selected by a genetic algorithm. However, the high expense of FPGA resources allows only for the implementation of a limited number of weak classifiers.

Zemčik and Žadnik [44] suggested an approach based on the Wald-Boost detection algorithm with local rank differences (LRD) features. They precompute and store several

Figure 2.2: Complex memory access structure for LRD feature evaluating proposed by Zemcik[44].

Table 2.1: Comparison of performance and power consumption of Ada-Boost based hardware detectors. \*Only a pre-dection with a shortened classifier is done in FPGA, further post-processing is needed.

|                    | Feature | Image size         | FPGA           | LUT             | $\mathbf{FF}$ | BRAM | CLK | $\mathbf{FPS}$ |

|--------------------|---------|--------------------|----------------|-----------------|---------------|------|-----|----------------|

| Lai 2007* [29]     | Haar    | $640 \times 480$   | Virtex2 VP30   | 21K             | 8K            | 44   | 126 | 143            |

| Granat 2007 [31]   | Haar    | $256{\times}256$   | Virtex2 LX250  | _               | _             | 100  | 24  | < 5            |

| Zemcik 2007 [44]   | LRD     | $640 \times 480$   | Virtex-II      | 1490(SL)        | _             | 14   | 100 | 22             |

| Hiromoto 2008 [32] | Haar    | $640 \times 480$   | Virtex5 LX330  | 63K             | 56K           | _    | 160 | 30             |

| Cho 2009 [30]      | Haar    | $640 \times 480$   | Virtex5 LX110T | $67 \mathrm{K}$ | 22K           | 41   | _   | 7              |

| Kyrkou 2011 [33]   | Haar    | $320 \times 240$   | Virtex2 VP30   | 26K             | 24K           | 24   | 100 | 64             |

| Huang 2011 [34]    | Haar    | $320 \times 240$   | Virtex5 LX155T | 80K             | _             | _    | 65  | 100            |

| Brouss 2012 [35]   | Haar    | $320 \times 240$   | Stratix4 GX530 | _               | _             | _    | 125 | 50             |

| Jin 2012* [42]     | LBP     | $640 \times 480$   | Virtex5 LX330  | 128K            | 75K           | 286  | 125 | 300            |

| Kadlcek 2013* [43] | LBP     | $1024{\times}1024$ | Virtex2 LX250  | 1007(SL)        | _             | 31   | 130 | 130            |

smoothed images corresponding each to a different shape of LRD features. A sophisticated memory pattern allows reading block of 3x3 values to evaluate one weak classifier in one clock cycle. However, storing the precomputed values increases demands on memory, and the complex memory access structure requires too many logic resources.

#### 2.3 ACF based hardware detectors

Object detectors based on ACF [57] are very popular due to their excellent performance, good accuracy, and an available set of ready-to-use classifiers (faces, pedestrians, traffic signs, cars) and a toolkit to train user-specific classifiers [66]. Song et al. [67] proposed the first implementation of ACF in FPGA for pedestrian detection in the driver assistance system. This non-parallel implementation of the original ACF detector used ten feature channels. Multi-scale detection, however, requires multiple readings of the image from an external memory.

Mitsunari et al. [45] introduced a more effective implementation of ACF. They focused on problematic parts of the algorithm to enable parallelization on FPGA. The calculation of the HOG feature (using trigonometric functions and a square root) was replaced by an approximation (using only multiplication and addition). Further, they reduced memory requirements with only 2% accuracy penalty by quantizing both classifier's coefficient and thresholds (from 32 to 2 bits). Decision trees used in ACF as weak classifiers requires

Table 2.2: Comparison of performance and power consumption of ACF and SVM based hardware detectors. \*Only feature preprocessing done in FPGA. \*\*Only a pre-dection with a shortened classifie

|                                 | Type           | $\operatorname{Stride}$ | Image size         | FPGA            | LUT       | $\mathbf{FF}$    | BRAM      | DSP | $\operatorname{CLK}$ | $\mathbf{FPS}$ |

|---------------------------------|----------------|-------------------------|--------------------|-----------------|-----------|------------------|-----------|-----|----------------------|----------------|

| Martelli 2011 <sup>*</sup> [68] | SVM+Covariance | 8                       | $640 \times 480$   | XC6VLX240T      | 1553 (SL) | _                | 3         | 22  | 154                  | 132            |

| Yazawa 2015 [69]                | SVM+HOG        | 5                       | $640 \times 480$   | CycloneIII      | 17K (LE)  | 11K              | _         | _   | 70                   | 13             |

| Ma 2015 [23]                    | SVM+HOG        | 4                       | $1620{\times}1200$ | XC6VLX760       | 46K       | $187 \mathrm{K}$ | 381       | 190 | 150                  | 10             |

| Said 2016 <sup>*</sup> [70]     | SVM+Covariance | 4                       | $640 \times 480$   | XC6VLX240T      | 1357 (SL) | _                | 8         | 46  | 222                  | 292            |

| Song 2016 [67]                  | ACF            | 4                       | $640 \times 480$   | _               | _         | _                | _         | _   | 166                  | 30             |

| Kyrkou 2016 [65]                | SVM+LBP        | 5                       | $800 \times 600$   | Spartan6 LX150T | 33K       | 20K              | 256       | 59  | 70                   | 40             |

| Bilal 2017 [71]                 | SVM+HSG        | 4                       | $640 \times 480$   | Cyclone IV      | 751       | 496              | 3         | 0   | 50                   | 25             |

| Mitsunari 2018 [45]             | ACF            | 4                       | $1920{\times}1080$ | ZX7Z045         | 138K      | 149K             | 389       | 128 | _                    | 176            |

| Durre 2018 [25]                 | SVM+HOG        | 8                       | $1920{\times}1080$ | Stratix V       | 3529      | 2657             | $\sim 41$ | 26  | 142                  | 68             |

| Wang 2018 <sup>*</sup> [24]     | SVM+HOG        | 4                       | $640 \times 480$   | Cyclone IV      | 17K       | 7K               | 338       | 144 | 108                  | 60             |

| An 2019 [72]                    | SVM+HOG        | 8                       | $1920{\times}1080$ | Stratix IV      | 7625      | 4503             | $\sim 7$  | 41  | _                    | 60             |

| Li 2019** [73]                  | SVM+HOG        | 8                       | $512{\times}512$   | Stratix IV      | 313K      | 90K              | 859       | 268 | 320                  | 10000          |

complicated memory access because selected decision nodes depend on the input data. Thus, parallel processing is complicated due to memory access conflicts. Mitsunari et al. resolved this issue by storing each channel in a separate memory bank in combination with SIMD-like processing which enabled channel-wise parallel implementation. To maximize the efficacy, the memory access conflicts are minimized by a complex processing order scheduling.

#### 2.4 SVM based hardware detectors

SVM is a prevalent classification algorithm utilized for implementing object detectors in FPGA [23, 68, 69, 70, 65, 71, 25, 72, 73]. This is thanks to the fact that the SVM detectors have simple rigid structure suitable for parallel implementation — they include spaceuniform feature extraction and a multi-channel convolution. SVM classifiers with HOG features [22] have support in OpenCV [74] which also includes set of pre-trained classifiers (pedestrians, traffic signs, cars, etc.). This facilitates experimentation and testing. However, the absence of an attention method in the basic SVM detectors is disadvantageous. Unlike boosted detectors, SVM detectors do not incorporate early rejection, therefore it is necessary to evaluate all features at all image positions. That leads to increased demands on computing resources and/or processing time with the associated increased power consumption. HOG feature evaluation on FPGA requires a large number of complex computations on floating-point arithmetic. Square root, arctangent, and normalization (division) evaluations are necessary. [75]

Martelli et al. [68], and Said and Atri [70] proposed a SVM detector with set of image features extracted by learned linear filters. The calculation of the above is much easier than HOG evaluation. They use FPGA to accelerate the feature extraction. The SVM calculation itself takes place in a connected general purpose processor.

Ma et al. [23] implemented the Opencv version of the HOG+SVM detector [22]. They applied a fixed-point arithmetic instead of the original floating-point arithmetic. In their implementation, HOG feature rows are processed in parallel. Since cells in one row can be used for block normalization of the next row, alternating between odd and even rows prevents computing histograms twice, and leads to a processing speed-up. Bilal et al. [71] use Histogram of significant gradients (HSG) instead of HOG. The hardware for HSG calculations is simplified and does not require floating-point arithmetic.

|                    | CNN           | Image size       | FPGA     | LUT              | $\mathbf{FF}$ | BRAM | DSP  | CLK | FPS |

|--------------------|---------------|------------------|----------|------------------|---------------|------|------|-----|-----|

| Nakahara 2018 [47] | Light YOLOv2  | $224 \times 224$ | XCZU9EG  | 135K             | 370K          | 1706 | 377  | 300 | 300 |

| Ma 2018 [48]       | SSD           | $300 \times 300$ | GX2800   | 532K             | —             | 3844 | 4363 | 300 | 34  |

| Nguyen 2019 [49]   | Simple YOLOv2 | $416 \times 416$ | XC7VC707 | 155K             | 115K          | 1144 | 272  | 200 | 60  |

| Kang 2019 [50]     | VGG16+SSD     | $640 \times 480$ | XC7VX690 | $181 \mathrm{K}$ | 497K          | 1470 | 3074 | 210 | 42  |

| Wu 2019 [51]       | MobileNet+SSD | _                | XCZU2    | $161 \mathrm{K}$ | 301K          | 771  | 2070 | 430 | 31  |

Table 2.3: Comparison of performance and power consumption of selected CNN based hardware detectors

Li et al. [73] suggested a high-speed vision platform for detection of multiple highly distinctive objects. They use a short SVM classifier with HOG features in a highly parallel system that receives the input of 64 pixels per clock cycle. This allows detection of fast-moving objects at 10000 fps.

#### 2.5 CNN based hardware detectors

Historically, the first hardware object detectors used [76] neural networks. They were typically designed to handle one specific problem and did not achieve satisfactory performance and accuracy. The use of neural networks was then temporarily abandoned, and the focus was on methods based on boosted classifiers. Along with the growing popularity of deep learning for object detection [15, 16, 17], a large number of articles discussed the possibilities of their practical implementation on hardware platforms [77, 78, 49, 51, 47].

CNN are computationally intensive. Graphic Processing Units (GPUs), which have massive parallel performance, enable to compute CNN-based detectors in a reasonable time. However, GPUs have very high power consumption, so the use of FPGAs could have significant benefits due to massive parallel and power-efficient computing. However, it is hard to deploy standard neural networks into embedded devices because of a large number of operations and parameters CNN-based detectors have. Another disadvantage is the use of floating-point arithmetic in standard networks, which is resource-intensive on FPGAs.

Several early FPGA implementations used the floating-point representation that has enormous computation costs [77, 78]. Some works [83, 84, 85] demonstrated that a floatingpoint representation is unnecessarily redundant and the CNNs coefficients and intermediate results can be retrained and quantized to a very low-bit precision (even 1 or 2 bits for network weights) without a significant loss of accuracy. The quantization approach has been adopted for FPGAs by multiple authors [49, 51, 47]. Nakahara et al. [47] used standard YOLOv2 CNN [16] and implemented a mixed-precision CNN, which consists of binarized input layers and half-precision (16 bit) output CNN layers. The resulting detector achieved better accuracy than a fully quantized detector. Nguyen et al. [49] used a binarized version of YOLO CNN [15] and found that memory access and memory throughput to external DRAM memory is the main factor limiting performance. They focused on decreased dynamic random access to memory in order to increase performance.

Another approach how to optimize CNN-based detector is to use lightweight architectures such as Xception [18] and MobileNetV2 [17] which use depthwise separable convolutions as a replacement to the standard convolutions. Depthwise separable convolutions significantly reduce the number of operations and parameters with only a limited loss of accuracy. Wu et al. [51] compared standard convolution with separable convolution, and in addition, they rearranged input features and weights to increase performance.

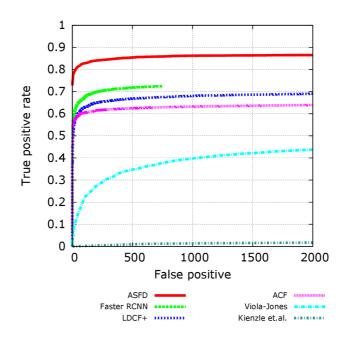

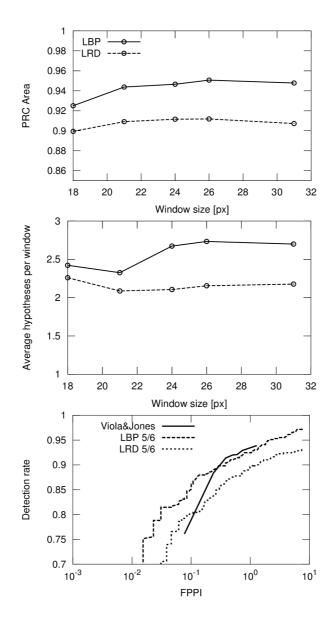

Figure 2.3: ROC curves of selected detectors on FDDB: A Benchmark for Face Detection in Unconstrained Settings [79]. ASFD [80] - the best current method using CNN; Faster RCNN [41] - very popular CNN based method; LDCF+ [14] - the best current boosted classifier based method(ACF+); ACF [57] - boosted decision tree classifier; Viola-Jones [11] - original algorithm Viola-Jones using AdaBoost and Haar features; Kienzle et. al. [81] -SVM based detector with HOG features

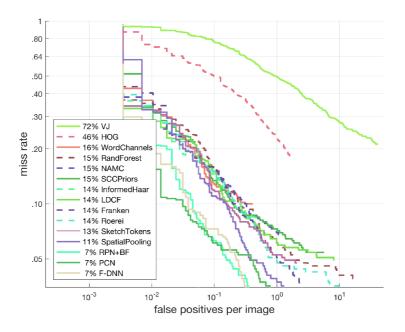

Figure 2.4: ROC curves of selected detectors on Caltech Pedestrian Dataset [82]. Important algorithms: VJ [11] - original Viola-Jones detector using AdaBoost and Haar features; HOG [22] - SVM based detector with HOG features; LDCF [57] - boosted decision tree classifier with ACF; F-DNN [26] - the best current CNN based method

#### 2.6 Summary

Figure 2.3 and Figure 2.4 illustrate a comparison of selected types of detectors for faces [79] and pedestrians [82]. These datasets are standardly used to benchmark detection methods and they include highly challenging scenarios including partially overlapped objects, overand underexposure, tiny and big objects, and various rotations. Comparisons on older datasets (as used by Viola and Jones [11]) would make no practical sense nowadays because CNN-based methods achieve nearly 100% accuracy at the moment. The ROC curves show that algorithms based on CNN achieve the best accuracy in both detection tasks. Advanced boosted algorithms ACF [57] and ACF+ [14]) provide a slightly lower accuracy but still outperform the original algorithms by Viola-Jones and SVM+HOG based [26, 22]. This is especially evident in face detection, where SVM+HOG based algorithms running on a CPU or GPU. Efficient CNN detector implementations in hardware use optimization methods such as quantization of coefficients or network size limitation which, in general, reduce detection accuracy [83, 84] almost to the level of the boosted classifier based algorithms.

Overview Tables 2.1, Tables 2.2 and Tables 2.3 display the speed and amount of resources required for various implementations of the object detector in hardware. SVM based detectors achieve seemingly excellent performance; for example, Li [73] reports 10000 fps at resolution 512x512 pixels. However, direct comparison of the reported frame-rates is almost meaningless as the detectors are designed for different types of objects, they provide different detection accuracy, the scan images at different resolutions and with different window strides. Moreover, the individual detectors significantly differ in the resources and power they consume. In general, modern boosted classifiers provide very good accuracy and speed trade-off in high-throughput and resource limited scenarios, where only a small number of object classes with relatively consistent appearance need to be detected. CNNs excel at more complex detection tasks where resource and power effectiveness is not that crucial.

# Chapter 3

# Goals and Contributions

This thesis focuses on object detection in images on hardware platforms. The scope of the work is to shift the scientific knowledge and apply it into the practice.

Presumed usage of object detectors developed here is industrial, transport or security applications, i.e. in tasks such as the detection of faces, pedestrians, products, licence plates. Practical deployment of such object detectors needs to meet specific requirements. The resolution of the processed image is an important parameter. This resolution depends a) on the resolution of the input image, b) on the expected size ranges of the searched objects and c) on the size of the detection window. Thus, the expected object size ranges significantly affect the required performance of the detector. Traffic and security applications require approximately 10 to 20 frames per second for suitable object tracking. Industrial applications often require even higher processing speeds. High-speed detectors also allow for processing image data in the camera without storing them on a fast external memory; the absence of external memory further reduces the price of the resulting device.

A typical requirement is that the detectors should achieve the best accuracy possible. In general, object detectors often balance a speed-precision trade-off. Detection of visually diverse, rotated, or distorted objects will either be less accurate or will require a complex system with a large number of computational resources. For example, in the task of licence plates detection in toll gates, where the approximate size and rotation is known, excellent accuracy can be expected. However, a similar task, licence plates detection for parking control in residential zones, is more challenging due to unconstrained conditions (variable position, scale, rotation, etc.), and therefore lower accuracy can be expected.

The technical goal is to create a powerful universal object detector for FPGA hardware with good accuracy and low resource consumption. Such detector should process at least FullHD video at 15 frames per second and should detect small and large objects with limited variability. The detector should achieve accuracy (recall with precision 0.70) of at least 95% for face detection and 99% for LP detection. Important parameters for the low price of the device are low power consumption and a small number of FPGA resources used. The detectors are expected to be utilised in smart cameras. Such smart camera should perform the maximum number of operations directly in-site and send out only the results for further processing. Thanks to this, it would be possible to reduce the data flow from the camera as expected by edge computing.

#### 3.1 Technical implications

At the beginning of my research work, there were already several successful attempts to create an object detector in hardware [30, 31, 32, 33, 34, 35, 42, 44]. A detailed overview of the individual solutions was given in the previous chapter. In summary, the results show that the practical use of these detectors is limited. In order to increase the performance and accuracy of detectors and the resolution of the processed image, it is necessary to improve current detection methods in hardware, modify detection algorithms and apply hardware-specific features.

#### Choice of classifier algorithm

Hardware detectors based on boosted classifiers have the most advantages for the applications mentioned above. The specifically targeted ad-hoc detectors have an excellent powerto-resource ratio in some applications. However, the ad-hoc detectors are not universal, the accuracy of detection is low, and they do not cope with changing conditions. Creating a detector for a new object class means a lot of work and an uncertain result. The SVM based detectors have good performance and relatively low resource consumption. However, they provide low detection accuracy not applicable in modern applications.

CNN based detectors provide the best accuracy and excel at complex detection task. Due to a large number of operations, they have high demands on logic and memory resources and have relatively low performance. Besides, the CNN optimisations for FPGAs means a loss of accuracy down to the level of a modern boosted classifier. Considered tasks such as face/pedestrian detection and licence plate detection have only a small number of object classes with a relatively consistent appearance, for which CNN seems unnecessarily complex. In conclusion, the modern boosted classifiers provide sufficient accuracy and speed trade-off considering these tasks with high-throughput and resource-limited scenarios.

Individual modifications of boosted classifiers, such as soft-cascade or Waldboost [11, 12, 13], only differ in the training process. The evaluation step does not vary much; the only difference is that soft-cascades and Waldboost allow rejecting after each weak classifier and the original Viola-Jones algorithm [11] allows rejecting after each stage (a set of several weak classifiers). The planned detector should evaluate all modifications of boosted classifiers. The best way to reach high detection accuracy and performance is training the boosted classifiers with Waldboost algorithm [13] and with augmentation, as suggested by Bar et al. [14].

Two approaches for implementation of boosted classifier based detector were developed — fully pipelined monolithic detector [42, 43] and sequential detector [44, 35, 33]. Fully pipelined detectors assess all features for one detection window position in parallel per one clock cycle. In general, the fully pipelined detectors are high-throughput and easy to implement. However, they have high demands on FPGA resources and usually evaluate only a limited number of weak classifiers, which leads to lower accuracy. Sequential detectors assess the features gradually. The parallelisation of sequential detectors is possible by processing multiple features or multiple positions at the same moment. They require fewer resources and allow for better accuracy, but they are more challenging to control. I have focused on sequential detectors because they meet the required parameters better and offer space for further development.

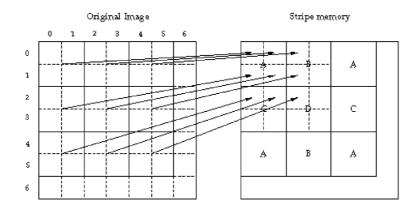

#### Choice of weak classifiers

Many authors [31, 32, 30, 33, 34, 35] use Haar-like features as weak classifiers. High bit depth for storing integral image and complex logic to access feature values make them resource demanding. Therefore, it isn't easy to increase the performance of such detectors. Other works [44, 42, 43] apply LBP or their modifications (LRD, LRP) as weak classifiers. Their advantage is in loading only surrounding pixels (block reading) for effective calculation. LBP-like features are mainly used in combination with fully pipelined detectors [42, 43]. Zemčík and Žádník [44] verified the sequential approach by developing a suitable object detector. Their detector used LRD features with a size of 3x3 and subsampling of the original image in the ratios 1x1, 1x2, 2x1 and 2x2. For direct evaluation of the feature, it may require loading blocks of up to 6x6 pixels. It seems unnecessary to read data from the sliding windows (usually created as a register array with FIFO line buffers), and a better option is to read it directly from the addressable memory composed of BRAM. An optimal structure of this BRAM memory allows data reading without the use of a complicated multiplexer network. Zemčík and Žádník reduced the logic resources required for reading such large blocks by precalculating the subsampled versions of the image into memory. Reading only 3x3 blocks already precalculated in memory becomes sufficient for feature evaluation. The disadvantages are increased memory requirements and the need for storing differently sized subsampled versions of the original image. This has led to a complicated memory structure and high logic and memory resources demands.

Hereby proposed detectors are inspired by the detector introduced by Zemcik and Zadnik [44]. The main difference is that local image features of different sizes are not calculated from precalculated values, but directly from the original image. It saves memory resources, but on the other hand, it means reading blocks of different sizes (3x3, 3x6, 6x3 and 6x6 pixels), which is more complicated compared to the original constant size of 3x3. For simplicity, a 6x6 block (the worst case) can always be read and then subsampled as needed. A well-designed memory structure allows reading of unaligned 6x6 blocks at the same time, thus reducing logic and memory requirements.

#### Multiscale-detection

Designing an effective multi-scale detection on FPGA is an unresolved issue. Many related works do not address multi-scale detection at all [29, 31, 44, 43]. Several works [30, 32] suggest storing the entire image in BRAM memory, but this is not always feasible, especially at higher resolutions. Other works solve multi-scale detection by multiple image loading from external memory [34, 35]. Kyrkou et al. [33] reduced the number of loading from external memory by using more classifiers with different window sizes.

We have proposed a more efficient method of multi-scale detection. It does not require multiple image readings and uses significantly less memory than needed when storing entire images. The core is that the single scale detection requires only a narrow strip of the image memory, with the minimum height as the detection window. The same principle can be used for smaller versions of the image in multi-scale detection. Furthermore, it enables generating these smaller versions from the previous ones with fixed scale unit onthe-fly. The proposed method allows detecting objects of different sizes directly from the data coming from the sensor; the resulting system may not contain external memory at all, which would reduce the cost of the device. This approach can be further combined with the use of multiple classifiers with different window sizes. However, the memory requirements for storing multiple classifiers using LBP/LRD features are often greater than the memory consumption when storing stripes of image. But the benefit always depends on the resolution of the input image, the height of detection window and the number of down-scaled versions.

#### **Detector optimization**

Parallel processing is one way to increase the performance of the detector on FPGA. Many authors [30, 29, 33] use parallel computation of more features in one position. Since the average number of evaluated features in one position is very small, it does not allow a high level of parallelization. When using the sliding window approach, it is necessary to evaluate all weak features and only then it is possible to move to the next one. In pipeline processing, premature rejection often results in a penalty meaning a speculative evaluation of other features or insertion of blank operations. Brousseau and Rose [35] suggested a method of evaluating features in neighbouring positions. The number of evaluated classifiers in specific positions is variable, which causes problematic divergence of the calculation. Besides, this approach combined with sliding windows leads to an increase of multiplexing network complexity, and thus an increase in logical resources. The detector introduced by Zemčík and Žádník [44], which is the basis for the proposed detectors, did not use any parallel processing.

We have proposed an approach for evaluating multiple positions in the pipeline simultaneously. This is possible by reading the data directly from BRAM memory, where the data for evaluating all positions of the entire line are accessed. It enables us to evaluate a bigger number of independent positions at the same time at various stages of evaluation. After evaluating the required features in one position, there is no need to wait for the evaluation of the surrounding positions; it is possible to move to the next position in the same line. This eliminates the issue with divergence and allows the creation of a longer pipeline without penalizing after the early rejection. The extension of the pipeline has a positive effect on the increase of the maximum circuit frequency and consequently, the rise of the detector performance.

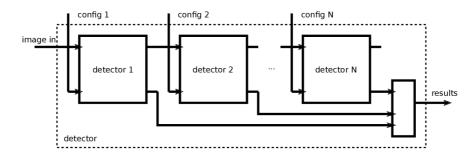

We also suggest using more detectors connected in a cascade to increase performance. Each of these detectors performs detection in a different part of the image and at a different scale version. The optimal distribution can be precalculated so that the number of positions evaluated by each detector is approximately the same. This modification allows the detector's performance to be scaled very well for the needs of a specific application.

#### 3.2 Goal of the thesis

The primary goal of this thesis is to improve the state-of-the-art in the field of object detection in the image on hardware platforms. The hypothesis is: It is possible to design an object detector based on soft cascade deployed in programmable hardware with resulting precision comparable to the state-of-the-art, with real-time performance, with lower power consumption and less computing resource demands comparing to existing ones.

The method of proof is creating a hardware detector that meets the required parameters and thus exceeds the state-of-the-art. Completing this task will require developing new methods and performing many experiments. In order to investigate of task the detector design, I have chosen to pursue the following methods:

• using local image features (LBP/LRD) and soft cascade classifiers in sequential engine with efficient block reading of image values for weak classifier evaluation,

- creating a multi-scale on-the-fly detector for high-resolution image data processing (without the need for external memory),

- using parallelization of weak classifier calculations by processing multiple positions at the same time, both at the level of sequential engine and cascade connection of multiple detectors.

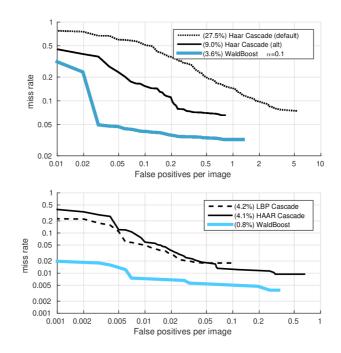

The above proposed methods are being examined with the aim to confirm the presented hypothesis. The experiments will be performed in the detection of faces, pedestrians and license plates. Comparisons with other authors will be made on the face detection task, which is usually presented on other papers. For a fair comparison of performance due to different resolutions, detection window size, detection stride, multi-scaling, etc. a conversion to the number of processed detection windows per clock cycle will be used.

#### **3.3** Core contributions

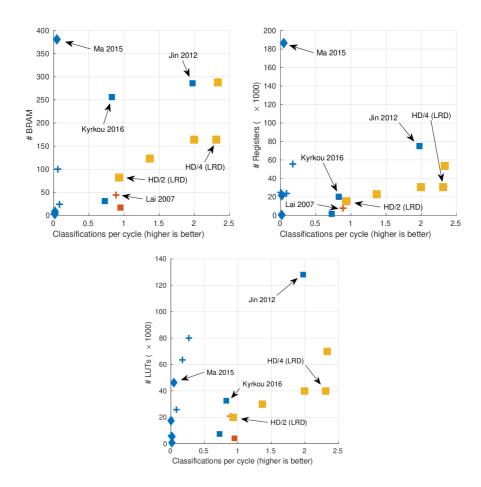

This thesis contributes to the state-of-the-art in the field of object detection in the image on hardware platforms. Three papers validating the hypothesis were published. They represent the experimental proof and demonstrate that it is possible to create the detector with defined parameters. The papers show that the proposed hardware detector outperformed the state-of-the-art in several aspects:

- better detection performance among boosted classifier multi-scale face detection on Full HD (1920×1080 pixels) video at 60 fps (for object size 21 pixels and more) versus 640×480 at 30 fps by Hiromoto et al. [32],

- better detection performance in processed detection windows per clock cycle among all hardware detectors up to 2.33 versus only processing detector with 1.97 by Jin [42] of full detector with 0.95 by Zemčík and Žádník [44],

- better performance/resources ratio in all resources: LUT, REG and BRAM; the graphical comparison is in paper [2],

- better accuracy in face detection on CMU dataset [11] recall 97 % with 0.2 false positives per image (FPPI) versus recall 91 % with 0.2 FPPI presented by Hiromoto et al. [32] and Kyrkou et al. [33],

- comparable accuracy in licence plate detection aligned licence plates recall 99 % with 0.2 FPPI and unconstrained recall 98 % with 0.2 FPPI on own dataset

The contributions that implement experimental proof of thesis were presented in the following papers:

• High performance FPGA object detector: Hardware prototype, FPL<sup>1</sup> 2013. Paper with introduce an architecture of an engine for high-performance multi-scale detection of objects in videos based on WaldBoost training algorithm. The key properties of the architecture include the processing of streamed data and low resource consumption. The engine is implemented in FPGA and that it can process 640×480pixel video streams at over 160 fps without the need of external memory.

<sup>&</sup>lt;sup>1</sup>International Conference on Field Programmable Logic and Applications

- Cascaded Stripe Memory Engines for Multi-Scale Object Detection in FPGA, TCSVT<sup>2</sup> 2019. Evolution of the previous paper witch expands performance and usability. FPGA detector can process a stream of image data so that it stores a narrow stripe of the input image and its scaled versions and uses a detector unit which is efficiently pipelined across multiple image positions within the memory. We show how to process images with up to 4K resolution at high framerates using cascades engine. As a detector algorithm use boosted soft cascade with simple image features that require only pixel comparisons and look-up tables; therefore, they are well suitable for hardware implementation.

- Unconstrained License Plate Detection in FPGA, submitted to VEHITS<sup>3</sup>. This paper shows the practical use of the previous detector in traffic application on the task of detecting unconstrained License Plate. To detect and localize license plates is use multiple sliding window detectors based on simple image features, each tuned to a certain range of projections. On a large dataset is detection rate 98%.

Results presented in these papers proof the hypothesis of this thesis.

#### **3.4** Other publications

I am a co-author of some other publications dealing with other areas of image processing. I focused mainly on the effective implementation of the algorithm on the FPGA and the modification of the algorithm for stream image processing on the fly, ie without the use of external memory. List of my other publications in chronological order:

- Single-Loop Approach to 2-D Wavelet Lifting with JPEG 2000 Compatibility, SBAC-PADW<sup>4</sup> 2015 [86]. In this paper is presented a novel approach to 2-D single-loop wavelet lifting with can be efficiently pipelined in hardware. A newly developed 2-D core of CDF 5/3 wavelet filter is presented that, using a new sequence of operations, simplify the design. Moreover, the proposed approach, that uses one pass for 2-D transform, directly produces final output and reduces significantly the need for storing intermediate results into memory.

- High Dynamic Range Video Concepts, Technologies and Applications, Real-Time HDR Video Processing and Compression Using an FPGA, 2016 [87]. The chapter in the book deals with hardware acceleration of HDR video acquisition and compression. Individual HDR images are obtained by composing several differently exposed images obtained with a standard camera. Description of HDR compression and its implementation on FPGA.

- True HDR camera with bilateral filter based tone mapping, SCCG<sup>5</sup> 2017 [88]. In paper is presented a real-time HDR processing system evaluated on a custom hardware camera platform. They are proposal modifications of the the State-of-the-arts algorithms enabling efficient implementation on FPGA platform and real-time performance. The main focus of the paper is on acceleration of Durand local tone-mapping operator involving real-time bilateral filter. The proposed solution is compared to the existing research results in terms of speed, resource consumption, and numerical accuracy.

$<sup>^{2}\</sup>mathrm{IEEE}$  Transactions on Circuits and Systems for Video Technology

<sup>&</sup>lt;sup>3</sup>International Conference on Vehicle Technology and Intelligent Transport Systems

<sup>&</sup>lt;sup>4</sup>International Symposium on Computer Architecture and High Performance Computing Workshop

<sup>&</sup>lt;sup>5</sup>Spring Conference on Computer Graphics

The publications presented above do not directly contribute to the scientific goal and hypothesis validation of the dissertation. However, technologically they add to the options of using object detection in images. In some applications, for example, in bad light conditions such as sharp backlight, it is advantageous to combine object detection with HDR image processing to improve accuracy. In addition, the platforms created in these publications were used for experimental work with object detection.

## Chapter 4

# High Performance Architecture for Object Detection in Streamed Video

Before 2013, when this article was published, several successful attempts to create an object detector in hardware were proposed. However, their parameters were insufficient, and the practical use of these detectors was limited. In this paper, we have proposed a practical object detector in hardware that allows detected objects on video with resolution  $640 \times 480$  and 160 frame per second.

Main contribution is to use boosted soft cascades of classifiers with local image features as weak classifiers. The combination of the unique structure of the memory and the local features enabled the effective sequential evaluation of weak classifiers. Another advantage is the new detection method, which allows the detection of objects of different sizes on-thefly, i.e. without reloading the image and extreme demands on FPGA memory resources. Proposed detector outperformed state-of-the-art in better detection performance and better performance/resources ratio.

The work was also selected for a presentation within the FPL Demo Night [89], where it had good reviews.

The work builds on the previous work of Pavel Zemčík [44]. My contribution in this paper was designing a memory structure for efficient reading of image values per block for effective evaluation of a weak classifier. Also, I suggested on-the-fly multi-scale detection and implemented a detector simulator in C language to verify detector properties. Finally, I implemented and tested the detector in the VHDL language.

### High Performance Architecture for Object Detection in Streamed Video

ZEMČÍK Pavel, JURÁNEK Roman, MUSIL Martin, MUSIL Petr a HRADIŠ Michal. High Performance Architecture for Object Detection in Streamed Videos. In: Proceedings of FPL 2013. Porto: IEEE Circuits and Systems Society, 2013, s. 1-4. ISBN 978-1-4799-0004-6 [1]

Author participation: 30 %Conference ranking: A2 (Qualis<sup>1</sup>)

#### Abstract

Object detection is one of the key tasks in computer vision. It is computationally intensive and it is reasonable to accelerate it in hardware, and especially in programmable hardware. The possible benefit of the acceleration is reduction of the computational load of the host computer system, increase of the overall performance of the applications, and reduction of the power consumption. In this paper, we shortly review the WaldBoost-based object detection algorithm and introduce a novel architecture of engine for high performance multiscale detection of objects in video. We implemented the engine in FPGA and we show that it can process  $640 \times 480$  pixel video streams at over 160 fps without the need of external memory, and with only modest consumption of FPGA resources. We evaluate the design, compare it to state of the art designs, and discuss its features and limitations. We conclude with remarks for future work.

#### 4.1 Introduction

Object detection is one of the key methods used by the contemporary image and video processing applications, such as security and surveillance, production control, quality inspection, and human-machine interaction. One of most widely used methods [11] uses classifier to evaluate every sub-window of an input image in order to determine whether the area contains target object or not. In case of objects occurring in multiple sizes, the detection should be performed in multiple scales of the images or multiple sizes of the classification window.

Several authors proposed hardware implementations of object detectors [30, 34, 90, 33, 29, 44]. In most cases, they use cascade of boosted classifiers proposed by Viola and Jones [11] but other approaches to the detection, such as neural networks [91], are also used. Many object detectors use the original detection cascade with Haar features [30, 33] that are not particularly suitable for hardware implementation. Moreover, most of the designs use relatively large memory structures to store the input image. These drawbacks are avoided in the presented design.

The key properties of our architecture are the following. We use very simple feature extractors – Local Binary Patterns (LBP) [92] and Local Rank Functions (LRF) [93]. We replaced the cascade of boosted classifiers with WaldBoost [13] classifier, which provides improved detection speed and accuracy. At the same time, the engine does not need external memory storage as it requires only a narrow image buffer stripe which fits in the on chip memory.

<sup>&</sup>lt;sup>1</sup>http://www.conferenceranks.com/

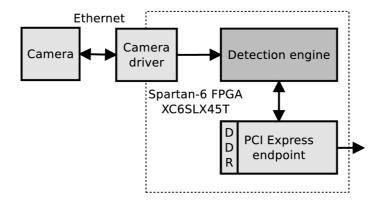

The architecture can handle streamed input, process it, and add detection results into the video stream in real-time A single instance of the detection engine implemented in FPGA can process  $640 \times 480$  pixel video stream faster than in real-time – at over 160 frames per second with the clock speed of 152 MHz while consuming around 0.5 W of power. The accuracy of the detection measured on the task of face detection reaches over 85 % with one false positive detection per image. When synthesized, it consumes only modest amount of FPGA resources and thus multiple instances of the detection engine can be implemented in a single FPGA chip in order to boost the performance, or to enable detection of multiple object types at the same time. Special focus was put on minimization of the expensive memory structures usage and on low energy demand.

The paper describes the architecture, its implementation in Xilinx Spartan 6 LX45T FPGA, evaluates its properties on the face detection task, and compares it to the state of the art detection architectures.

#### 4.2 Related Work

The following sections briefly review object detection with classifiers, methods of feature extraction, and methods of implementation of the detectors in hardware platforms.

#### **Object Detection with Classifiers**

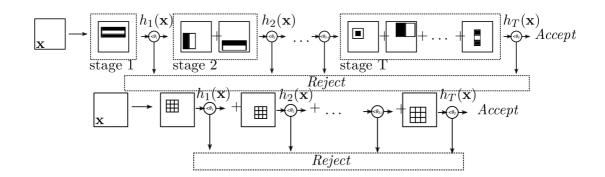

Object detection with classifiers is one of the fastest methods for robust object detection in images. The best known and most widely used detector training algorithm is Cascade of boosted classifiers proposed by Viola and Jones [11]. The detection *cascade* subdivides the classifier into several increasingly complex classifiers (called *stages*). After evaluation of a stage, a decision about the class of the input image is made. Early stages can reject majority of background samples and thus the computational complexity is kept quite low. Every stage is composed from very simple elementary classifiers called *weak hypotheses*. More advanced method, *Soft cascade* [12], learns a *sequential classifier* which makes decision about image class after evaluation of every weak hypothesis. In this work, we use WaldBoost algorithm [13], which produces soft cascade classifier represented by a sequence of weak hypotheses  $h^{(t)} = (\phi^{(t)}, \alpha^{(t)}, \theta^{(t)})_{t=1}^T$  where *T* is the total number of weak hypotheses. Every hypothesis contains parameters of feature extraction  $\phi^{(t)}$ , a list of responses  $\alpha^{(t)}$  and a threshold  $\theta^{(t)}$ . Response of *t*-th weak hypothesis  $h^{(t)}$  on image sub-window *X* is obtained by indexing  $\alpha^{(t)}$  using the response of the corresponding image feature  $f(X, \phi^{(t)})$ , see Section 4.2.

$$H^{(t)}(X) = \sum_{k=1}^{t} \alpha_{f(X,\phi^{(k)})}^{(k)}$$

(4.1)

$$S^{(t)}(X) = \begin{cases} 0 \quad H^{(t)}(X) < \theta^{(t)} \\ S^{(t+1)}(X) \quad \text{otherwise} \end{cases}$$

(4.2)

The response of the strong classifier  $H^{(t)}$  in every step is accumulated (4.1), and tested against  $\theta^{(t)}$  (4.2). When the sum falls below the threshold, the evaluation ends as the input is likely to be the background. If the evaluation reaches the last weak hypothesis, the final decision is positive and it is likely that the object has been detected.

Figure 4.1: Nine cells C are taken from X according to feature parameters  $\phi$ . Central cell c is marked by red, and border cells  $C^B$  are marked by green (applies for LBP evaluation).

Given an input image, the classifier is presented with its sub-images X from every position. Thus, every image area is classified and the positive final decisions are treated as detections. Multi-scale detection is usually solved either by *scaling of classifier window*, or *scaling of the image*. In this work, we explored both options.

#### Feature Extraction

So far, most widely used image features in both software and hardware are Haar features [94] as they proved to be a good information extraction tool for various tasks [34, 33, 29]. Haar features calculate differences of image intensities in adjacent rectangular areas. Other features, such as Local Binary Patterns (LBP) [92] or Local Rank Functions (LRF) [93], perform comparably or better than Haar features, and they offer interesting properties from the implementation point of view [93, 95, 44]. Another features, quite frequently exploited for detection, are Histograms of Oriented Gradients (HOG) [22], 3D Haar features [96], and others [97, 90]. Such features typically have good properties for various tasks, including detection of faces or pedestrians, but they are not suitable for hardware implementation.

In the presented work, we use LBP and LRD (subset of LRF) features, and parametrize them by their geometrical properties. LBP features are defined as  $\phi^{LBP} = (x, y, u, v)$ where x, y corresponds to position in image X, and  $u, v \in \{1, 2\}$  is size of feature cells in pixels. LRD features additionally contain identifiers of two selected cells a and b, thus  $\phi^{LRD} = (x, y, u, v, a, b)$ . A feature is evaluated from  $3 \times 3$  grid of cells C represented by sums of their values in X, see Figure 4.1. Equations (4.3) and (4.4) evaluate LBP and LRD features respectively ([·] returns 1 when the comparison is true, 0 otherwise). Parameters X and  $\phi$  impose C as mentioned above. LBP features compare central cell c with all other cells  $C^B$ . The results are concatenated to produce 8-bit word. LRD features calculate ranks of the cells a and b, and subtract them, producing results in range  $\langle -8; 8 \rangle$ . Rank is the number of positive comparisons of the cell value to all other cells.

$$f^{LBP}(X, \phi^{LBP}) = \sum_{i=1}^{8} 2^{i-1} \left[ C_i^B > c \right]$$

(4.3)

$$f^{LRD}(X, \phi^{LRD}) = \sum_{i=1}^{9} [C_i > C_a] - \sum_{i=1}^{9} [C_i > C_b]$$

(4.4)

In both cases, the results of feature evaluation do not significantly depend on brightness and contrast in the image. Therefore, normalization of the image of any kind is not required.

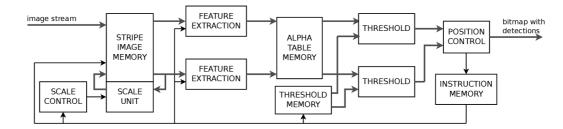

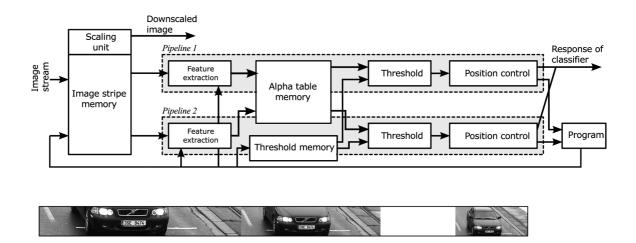

Figure 4.2: Block diagram of the proposed engine. The data for *Feature Extraction* blocks are loaded from *Stripe Image Memory*, weak hypotheses are evaluated using *Alpha Table Memory* blocks, and *Threshold* blocks evaluate strong classifier responses. *Instruction Memory* block holds the classifier program controlling the operation of the engine.

All the operations used in the feature evaluation are very simple (comparison, addition, subtraction) and thus the hardware implementation is relatively straightforward and it consumes only very little resources as shown in experiments.

#### **Object Detection in Hardware**

Since Viola and Jones published their real-time detection framework, much effort has been put into implementation of the detector in hardware, typically in FPGAs. Several designs for specific applications were introduced as well as general purpose detectors. Kim et al. [90] introduced real-time eye detector for FPGA based on AdaBoost classifier and MSC local image features. Cho et al. [30] proposed architecture implementing AdaBoost cascade detector with Haar features. In their approach, large memory is used to perform multiscale detection on a pyramid of integral images. Huang and Vahid [34] also used Cascade classifier with Haar features and they tried to reduce resource requirements of integral image memory by a multiplex network and by constraints during the training process. A relatively low resources detection system was proposed by Zemčík and Žádník [44]. They used a WaldBoost classifier and LRD image features. They used only a small image strip to save resources of FPGA. Multi-scale detection was made possible only by an external DSP unit which precalculates an image pyramid. Kyrkou and Theocharides [33] introduced AdaBoost Cascade detector which combines two approaches to perform multi-scale detection – image downscaling and scaling of scanning window. Such design, however, does have relatively high consumption of resources as it uses classifiers with Haar features and normalization must be performed – in this case using square integral image. Moreover, usage of memory is high due to an extensive image buffering.

The proposed architecture is based on design proposed by Zemčík and Žádník [44]. Alike their architecture, LRD features and strip image memory are used. Proposed architecture brings a significant improvement in multi-scale object detection (no need of external memory resources), higher input image resolution, stream video processing and average FPS, all of this with only small FPGA resource footprint.

#### 4.3 **Proposed Architecture**

The detector is designed as microprogrammed unit specialized in evaluation of weak hypotheses. Microprogram is synthesized from the results of machine learning process.

#### **Representation of a Detector**

Figure 4.2 shows block diagram of the engine. It works as a programmable automata driven by an instruction set with fixed size. Detector implements equations (4.1) and (4.2). It executes a classifier consisting of a long sequence of weak hypotheses on every image position and compares cumulative response to thresholds. A position is marked as positive when all weak hypotheses are evaluated. An instruction code for a stage t stores parameters for feature extraction  $\phi^{(t)}$ , stage identifier t for addressing table  $\alpha^{(t)}$  and  $\theta^{(t)}$ , and additional information for engine control. The position of a feature is stored on 10 bits, size on 2 bits, ranks a and b for  $\phi^{LRD}$  on 4 bits each, and identifier t on 10 bits. The whole instruction takes 64 bits. Items in  $\alpha$  tables are quantized to 9 bits, and thresholds  $\theta$  are stored on 16 bits.

The weak hypothesis evaluation block is pipelined to increase an overall performance. The pipeline has 9 stages, and therefore 9 weak hypotheses are processed in parallel. The instructions are loaded from the instruction memory and passed to the execution modules through delay units. The utilization of pipeline is almost 100 % given the ratio between the number of weak hypotheses to evaluate and clock cycles to fill the pipeline.

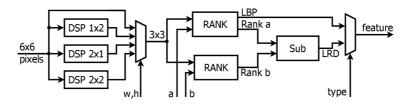

#### Feature Extraction Units

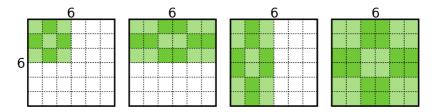

The detection engine implements LBP and LRD image features described in Section 4.2. The size of feature cell  $(u, v \text{ in } \phi)$  is limited to maximum 2 pixels and thus the features are limited to  $6 \times 6$  pixel area. The position of a feature is not limited. Figure 4.3 shows four versions of cells that can be extracted form a feature area. The limitation to  $6 \times 6$  pixels per feature does not adversely affect accuracy of the classifiers as shown earlier [93].

Figure 4.3: Cell configurations considered in this work. From  $6 \times 6$  pixel area, four versions of  $3 \times 3$  grid (shown in green) are extracted.

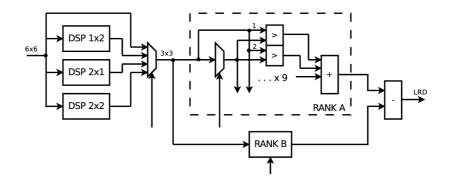

The block scheme of LRD feature evaluation, is shown in Figure 4.4. In the principle, DSP blocks extracts the grid of cells  $3 \times 3$  cells. One of the versions is selected for evaluation according to feature parameters u, v. The ranks for a and b are calculated as a number of positive comparisons of selected cell values. The feature response is then calculated as the difference between the two ranks. Evaluation of LBP feature is similar – it is based on parallel comparison of central cell with the cells at the boundary.

The response of a weak hypothesis is finally obtained from the look-up table assigned to the feature using the result of the feature evaluation described above. The number of entries in the table for depends on the type of the feature. Typically it is 256 entries are used for LBP, and 17 for LRD (for implementation reasons 32 items are used).

Figure 4.4: Circuit for LRD feature evaluation implementing (4.4). DSP blocks on the left extracts the four versions of cells. One versions is selected according to the current instruction. Two ranks are then calculated (circuit for calculation of one rank is shown in dashed block).

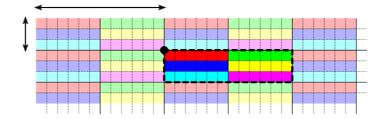

#### Memory Access Unit

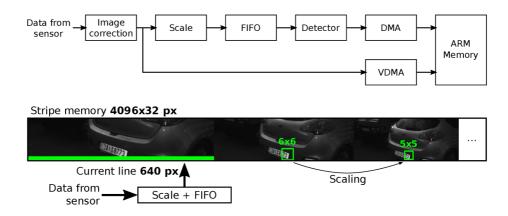

One of the key requirements for the detection engine is the ability to process streamed data without excessive use of resources. Therefore, the proposed engine stores only a narrow image stripe holding a small part of the currently processed image and and its scaled versions. The scaled versions are calculated on the fly. The image strip is illustrated in Figure 4.5.

The memory is organized as a circular buffer of rows. In the proposed design, each 36bit memory cell stores 6 image pixels (with 6-bit per pixel). For the purpose of the FPGA implementation, we convert 8-bit source image into 6-bit by discarding 2 least significant bits in order to save resources. This does not measurably reduce detection rate due to the properties of image features that are based on comparison of pixels only. Moreover, the image conversion can be reflected in the classifier training process.

Memory addressing is optimized for reading of  $6 \times 6$  pixel blocks in every clock cycle. To enable this feature, interleaved addressing and 12 separately addressable memory structures must be used. This approach has significantly lower resource requirements than switching networks used for loading data from integral image for Haar feature evaluation. Also, the proposed solution outperforms the designs with external memory, DSPs, or large synthesized memory in FPGAs. In our experimental design, Xilinx Spartan 6 LX45T FPGA is used, and the memory is implemented in 12 BRAM blocks that store 32 lines of the image. The width of the buffer in pixels and the required number of the BRAMs used depends on the width of the input image (640 pixels in our case).

#### Image Scale Unit

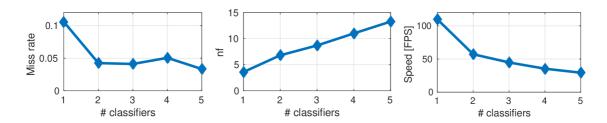

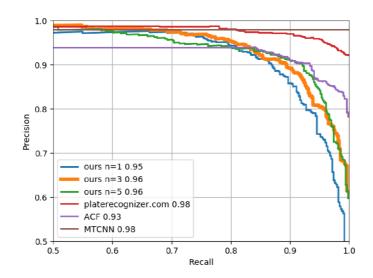

The multi-scale detection is performed using scaled versions of the image (pyramid) in the image stripe stored in the image buffer. We explored two solutions that can be implemented in the engine.