# BRNO UNIVERSITY OF TECHNOLOGY

Faculty of Electrical Engineering and Communication

MASTER'S THESIS

Brno, 2021

Bc. JAKUB FRÁNEK

# BRNO UNIVERSITY OF TECHNOLOGY

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING

# AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

# DEPARTMENT OF MICROELECTRONICS

ÚSTAV MIKROELEKTRONIKY

# INJECTION LOCKED RING OSCILLATOR DESIGN FOR APPLICATION IN DIRECT TIME OF FLIGHT LIDAR

NÁVRH INJEKCÍ ZAVĚŠENÉHO KRUHOVÉHO OSCILÁTORU PRO APLIKACI V SYSTÉMECH LIDAR PŘÍMO MĚŘÍCÍCH ČAS PRŮLETU

## MASTER'S THESIS

DIPLOMOVÁ PRÁCE

#### AUTHOR AUTOR PRÁCE

Bc. Jakub Fránek

ADVISOR VEDOUCÍ PRÁCE

Ing. Vilém Kledrowetz, Ph.D.

BRNO 2021

# **Master's Thesis**

Master's study program Microelectronics

**Department of Microelectronics**

Student: Bc. Jakub Fránek Year of study:

*ID:* 186059

Academic year: 2020/21

TITLE OF THESIS:

### Injection locked ring oscillator design for application in Direct Time of Flight LIDAR

#### **INSTRUCTION:**

Provide an introduction to Direct Time of Flight (DToF) LIDAR technology, describe the operation of the singlephoton avalanche diode, identify the main challenges of implementing DToF systems with sub-centimeter resolution. Compare different types of time to digital converters (TDC) in CMOS technologies. Analyze the operation of injection locked oscillators and describe the advantages of their application in DToF measuring TDCs. Create a MATLAB model of an injection locked ring oscillator, which takes the main non-idealities of their practical implementation in CMOS technologies into account. In ONK65 processing technology, design an injection locked ring oscillator capable of achieving 50 ps temporal resolution along with its biasing circuits, including the Delay Locked Loop (DLL), and evaluate its performance with computer simulations.

#### **RECOMMENDED LITERATURE:**

According to recommendations of supervisor

Date of project 8.2.2021 specification:

Supervisor: Ing. Vilém Kledrowetz, Ph.D.Consultant: Ing. Ivan Koudar, Ph.D., ON Design Czech s.r.o.

Deadline for submission: 25.5.2021

**doc. Ing. Lukáš Fujcik, Ph.D.** Chair of study program board

WARNING:

The author of the Master's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

Faculty of Electrical Engineering and Communication, Brno University of Technology / Technická 3058/10 / 616 00 / Brno

# Diplomová práce

magisterský navazující studijní program Mikroelektronika

Ústav mikroelektroniky

*Student:* Bc. Jakub Fránek *Ročník:* 2

*ID:* 186059 *Akademický rok:* 2020/21

#### NÁZEV TÉMATU:

### Návrh injekcí zavěšeného kruhového oscilátoru pro aplikaci v systémech LIDAR přímo měřících čas průletu

#### POKYNY PRO VYPRACOVÁNÍ:

Seznamte se s technologií LIDAR využívající přímého měření času průletu fotonu, popište operaci jednofotonové lavinové diody, identifikujte hlavní výzvy systémů LIDAR s lepším než centimetrovým rozlišením. Srovnejte způsoby realizace časově digitálních převodníků v technologiích CMOS. Popište funkci injekcí zavěšených oscilátorů a výhody jejich použití pro implementaci časově digitálních převodníků pro přímé měření času průletu. Ve výpočetním programu MATLAB vytvořte model injekcí zavěšeného kruhového oscilátoru, který zohledňuje hlavní neideality jejich praktické realizace v technologiích CMOS. Ve výrobní technologii ONK65 navrhněte injekcí zavěšený kruhový oscilátor poskytující časové rozlišení 50 ps společně s jeho biasovacími obvody, včetně závěsu zpoždění (DLL). Funkci navržených obvodů vyhodnoťte počítačovými simulacemi.

#### DOPORUČENÁ LITERATURA:

Podle pokynů vedoucího práce

Termín zadání: 8.2.2021

Vedoucí práce: Ing. Vilém Kledrowetz, Ph.D. Konzultant: Ing. Ivan Koudar, Ph.D., ON Design Czech s.r.o.

Termín odevzdání: 25.5.2021

doc. Ing. Lukáš Fujcik, Ph.D. předseda rady studijního programu

UPOZORNĚNÍ:

Autor diplomové práce nesmí při vytváření diplomové práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

Fakulta elektrotechniky a komunikačních technologií, Vysoké učení technické v Brně / Technická 3058/10 / 616 00 / Brno

# ABSTRACT

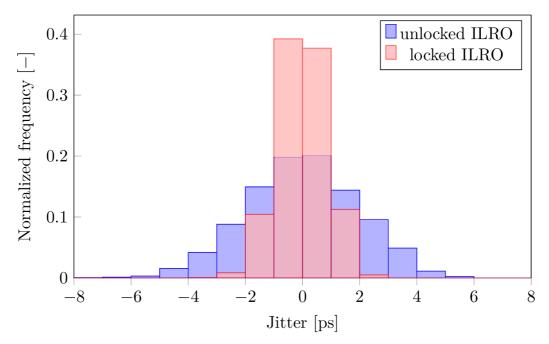

The diploma thesis provides an introduction to Direct Time of Flight LIDAR systems and Time to Digital Converters used in these systems. It discusses the problem of clock distribution in LIDAR Time to Digital Converter arrays, and examines one of the possible solutions to this problem based on injection locked oscillators. The injection locking phenomenon is thoroughly mathematically described and a Matlab model of an injection locked ring oscillator is presented, confirming the analytic predictions. In ONK65 processing technology, an injection locked ring oscillator biased by a delay locked loop meant specifically for application in Time to Digital Converters for LIDAR systems has been designed. The designed oscillator has been verified by computer simulations taking process, voltage and temperature variations into account and offers specified time resolution of 50 picosecond as well as two times less clock jitter than an equivalent free-running oscillator in the given processing technology.

# **KEYWORDS**

LIDAR, time of flight, time to digital converter, injection locked oscillator, CMOS

# ABSTRAKT

Diplomová práce přibližuje systémy LIDAR přímo měřící čas průletu a časově digitální převodníky určené k použití v těchto systémech. Představuje problematiku distribuce hodinových signálů napříč soubory časově digitálních převodníků v LIDAR systémech a věnuje se jednomu z nových řešení této problematiky, které je založené na injekcí zavěšených oscilátorech. Technika injekčního zavěšení oscilátorů je důkladně matematicky popsána. V programu Matlab byl vytvořen simulační model injekcí zavěšeného kruhového oscilátoru, který potvrzuje správnost uvedených analytických predikcí. Ve výrobní technologii ONK65 byl navržen injekcí zavěšený kruhový oscilátor stabilizovaný pomocí smyčky závěsu zpoždění, určený pro implementaci časově digitálního převodníku pro systém LIDAR. Navržený injekcí zavěšený kruhový oscilátor byl verifikován počítačovými simulacemi zohledňujícími vliv procesních, napěťových i teplotních variací. Oscilátor poskytuje specifikované časové rozlišení 50 pikosekund a dosahuje dvakrát nižší hodnoty fázového neklidu než ekvivalentní volnoběžný oscilátor v dané technologii.

# KLÍČOVÁ SLOVA

LIDAR, čas průletu, časově digitální převodník, injekcí zavěšený oscilátor, CMOS

Typeset by the thesis package, version 4.03; http://latex.feec.vutbr.cz

## ROZŠÍŘENÝ ABSTRAKT

Vynález jednofotonové lavinové diody a možnost její integrace do řady standardních CMOS výrobních procesů umožnily rozvoj nových snímacích a zobrazovacích technologií. Citlivost tohoto fotodetektoru na jednotlivé fotony a schopnost detekovat čas dopadu s pikosekundovým rozlišením využívají pozitronové emisní tomografy, různé druhy spektroskopie a mikroskopie nebo právě systémy LIDAR s přímým měřením doby průletu.

Základním principem těchto systémů je měření časového intervalu od okamžiku, kdy je vyslán laserový paprsek, do okamžiku, kdy je opětovně detekován detektorem, který se skládá právě z jednofotonových lavinových diod. Jelikož je rychlost světla v prostředí známá konstanta, lze s pomocí změřeného časového intervalu vypočítat vzdálenost k překážce, od které se paprsek odrazil. Systémy LIDAR proto fungují jako zobrazovací snímače, které místo vlnové délky nebo intenzity dopadajícího elektromagnetického záření snímají čas průletu, a tedy vzdálenost k objektům v jejich zorném poli. Ve srovnání s ostatními metodami měření vzdáleností v 3D prostoru, jako jsou například ultrazvukové senzory, stereoskopické kamerové systémy nebo mikrovlné radary, mohou systémy LIDAR nabídnout lepší rozlišení, větší dynamický rozsah, nižší náročnost na výpočetní výkon a schopnost pracovat v prostředích s denním světlem i ve tmě.

Systémy LIDAR často nachází uplatnění v automobilovém průmyslu, kde tvoří jednu z klíčových komponent moderních pokročilých asistenčních systémů, protože umožňují přesné měření vzdáleností k překážkám v prostoru. Už nyní také existují prototypy samořídících automobilů, které se při orientaci v prostoru spoléhají právě na systémy LIDAR [1].

První kapitola semestrální práce se věnuje systémům LIDAR a jejich hlavním komponentám. Představuje dva základní přístupy snímání vzdáleností v zorném poli, tedy metodu skenování, která zorné pole ozařuje postupně po jednotlivých segmentech, a metodu záblesku, která zorné pole ozáří rozptýleným světlem v jediný okamžik a snímá jej celé současně. Další sekce první kapitoly se pak zabývá laserovými zdroji a požadavky, které jsou na ně kladeny. Výběr vlnové délky nebo optického výkonu laseru určuje do velké míry odstup signálu od šumu celého systému.

Velká část první kapitoly je věnována jednofotonovým lavinovým diodám, které jsou optimálními fotodetektory pro systémy LIDAR. Je popsána jejich struktura, jednotlivé fáze průrazu, šum a přeslechy, účinnost detekce nebo tzv. "hasicí" obvody. Protože se od systémů LIDAR očekává vysoké prostorové rozlišení, jsou diskutovány i možnosti zapojení těchto detektorů do větších souborů.

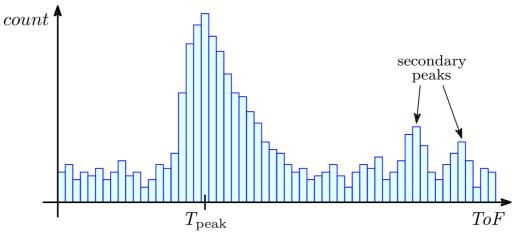

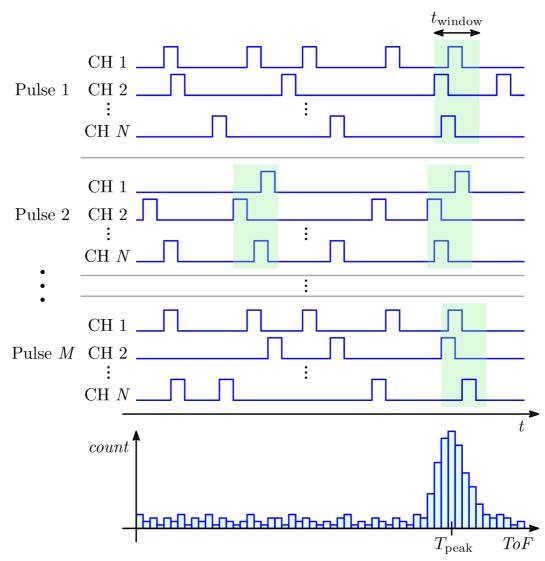

V poslední sekci první kapitoly je pak osvětlena důležitá technika, která umožňuje přesnou rekonstrukci času průletu fotonů i v zašuměných venkovních prostředích. Tato technika se nazývá časově korelované čítání fotonů. Principem této metody je měření času průletu v několika cyklech, kdy je každý výsledek měření uložen do histogramu. Na

konci měření je pak výsledný čas průletu určen jako modus jednotlivých konverzí. Jsou diskutovány i další možnosti zlepšení tohoto algoritmu.

Druhá kapitola se věnuje časově digitálním převodníkům, které měří čas průletu. Jejich parametry, jako dynamický rozsah, rozlišení, šum apod., jsou tedy určující pro přesnost celého systému. V této kapitole jsou přiblíženy techniky používané při jejich realizaci pro LIDAR systémy, sloužící pro zvýšení linearity převodní charakteristiky nebo snížení výkonové spotřeby. Výkonová spotřeba těchto převodníků je obzvláště důležitá, protože LIDAR systémy obsahují velké soubory fotodetektorů, a tedy i velké soubory časově digitálních převodníků.

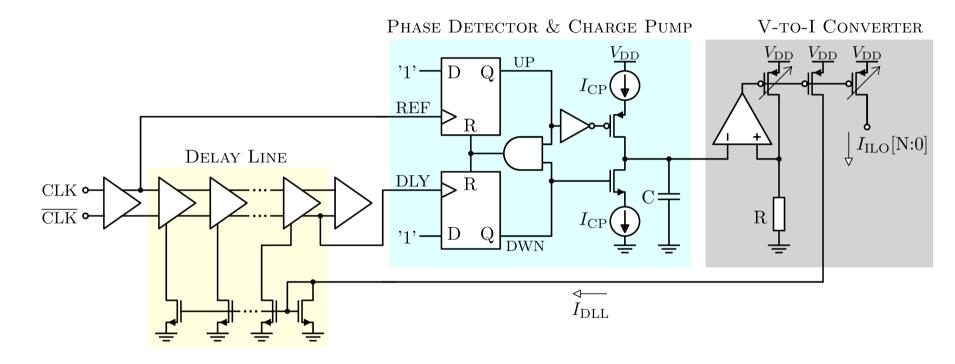

Dále jsou představeny jednotlivé typy převodníků – hrubé převodníky s velkým dynamickým rozsahem založené na jednoduchých čítačích, dále tzv. "jemné" převodníky spoléhající na propagační zpoždění digitálních signálů a umožňující dosažení rozlišení v řádu desítek pikosekund, i skutečně pokročilá řešení umožňující dosažení rozlišení v řádu jednotek pikosekund. Protože nastavení operačního bodu zpožďovacích buněk jemných časově digitálních převodníků se v praktických řešení nastavuje pomocí tzv. závěsů zpoždění (DLL), část druhé kapitoly se věnuje i jim a způsobům implementace řízených zpožďovacích buněk v CMOS výrobních procesech.

Na závěr druhé kapitoly je představena problematika distribuce hodinových signálů napříč soubory časově digitálních převodníků. Jelikož je v LIDAR systémech velký počet převodníků, vzdálenosti mezi nimi jsou na poměry integrovaných obvodů vysoké a při distribuci hodinových signálů na dlouhé vzdálenosti může vlivem parazitních vlastností kovových propojovacích vrstev docházet k velkým dynamickým ztrátám. Alternativním přístupem je generování hodinových signálů lokálně pomocí kruhových oscilátorů, což je z pohledu výkonových ztrát optimální řešení, avšak vzájemný nesouběh těchto oscilátorů se projeví náhodnou chybou zisku a vzorovým šumem jednotlivých "pixelů" LIDAR systému.

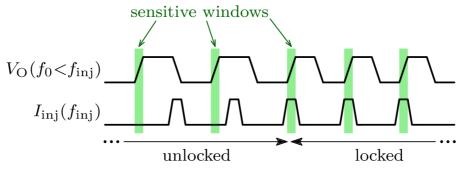

Nový přístup řešení tohoto problému reprezentují tzv. injekcí zavěšené oscilátory. To jsou oscilátory, které je možné pomocí periodických injekcí relativně malé energie (nejčastěji v podobě proudových pulzů, resp. dávek náboje) zavěsit na frekvenci injekcí. Třetí kapitola je věnována tomuto fenoménu, který je vysvětlen jak pomocí modelu harmonického LC oscilátoru, tak pomocí modelu kruhového oscilátoru. Třetí kapitola obsahuje kompletní matematické postupy vedoucí k odvození rovnic pro tzv. rozsah závěsu, což je rozsah frekvencí injekcí, na které je oscilátor schopen se zavěsit. Je také představeno konkrétní řešení problému distribuce hodinových signálů napříč soubory časově digitálních převodníků, které díky injekčnímu zavěšení dokáže garantovat synchronizaci frekvencí jednotlivých kruhových oscilátorů, a to za pomoci slabých, a tudíž relativně energeticky nenáročných periodických injekcí.

Dosavadní literatura o injekcí zavěšených kruhových oscilátorech se však nevěnuje některým neidealitám jejich reálné implementace. Jednou z nich je například vliv střídy hodinového signálu, od kterého se odvozují injekce, na rozsah závěsu injekcí zavěšeného oscilátoru.

Ve čtvrté kapitole je tudíž představen makromodel injekcí zavěšeného kruhového oscilátoru vytvořený v programu Matlab Simulink, s jehož pomocí byla prostřednictvím řady analýz ověřena správnost analytických odvození představených ve třetí kapitole, a díky němuž byla prozkoumána citlivost oscilátoru na variaci střídy injektovaného signálu. Bylo zjištěno, že asymetrie střídy injektovaného signálu snižuje rozsah závěsu, avšak oscilátor je na tento jev méně citlivý, pokud jsou injektované pulzy delší v čase. To se shoduje s hypotézou tzv. "citlivého okna", která je v této práci představena a intuitivně vysvětluje princip zavěšení injekcí zavěšených kruhových oscilátorů na jednoduchém modelu invertoru.

Pátá kapitola se zabývá návrhem injekcí zavěšeného kruhového oscilátoru řízeného pomocí závěsu zpoždění, který je určen pro konstrukci časově digitálního převodníku pro systém LIDAR s rozlišením 50 pikosekund. Návrh proběhl ve výrobní technologii ONK65, což je standardní 65nm CMOS technologie. Pátá kapitola vysvětluje důležitá návrhová rozhodnutí jako volbu frekvence kruhových oscilátorů (625 MHz) nebo počet jejich stupňů (16). Velká část kapitoly je také věnována rozboru vzorové architektury celého časově digitálního převodníku, protože ač je v této diplomové práci navrhována jen jeho část, pro návrháře dílčích obvodů je důležité rozumět tomu, jakou roli navrhované bloky v rámci systému splňují, aby mohl optimalizovat jejich klíčové parametry.

Samotný návrh na tranzistorové úrovni začal návrhem a optimalizací jednotlivých zpožďovacích buněk, z kterých se kruhový oscilátor skládá. Poté následoval návrh injekčního obvodu, jehož hlavním cílem bylo zachovat co nejvyšší rozsah zavěšení, ale zároveň neplýtvat energií, k čemuž byly využity poznatky ze čtvrté kapitoly, ve které byl injekcí zavěšený oscilátor modelován v programu Matlab Simulink. Dále se pátá kapitola věnuje návrhu závěsu zpoždění, který slouží k stabilizaci injekcí zavěšených oscilátorů vůči procesním, napěťovým nebo teplotním výchylkám. Obvody závěsu zpoždění byly rozšířeny o trimovací obvody, které umožňují kompenzovat chyby způsobené výrobním rozptylem.

Funkce navržených obvodů byla ověřena počítačovými simulacemi zohledňujícími procesní, napěťové a teplotní (PVT) extrémy. Až na jednu statisticky nepravděpodobnou a z hlediska celkové výtěžnosti zanedbatelnou kombinaci těchto extrémů bylo prokázáno, že jsou navržené injekcí zavěšené kruhové oscilátory schopny záchytu na cílovou frekvenci 625 MHz i v nepříznivých podmínkách. Výše zmíněná problematická kombinace PVT extrémů byla analyzována a potenciální řešení společně s jejich případnými nevýhodami byla diskutována. Simulace zohledňující šum navržených obvodů dále potvrzují, že fázový neklid zavěšeného oscilátoru je až o polovinu nižší oproti volnoběžnému stavu, což je v souladu s teoretickými poznatky. Počítačové simulace také dokládají, že střední hodnota časového rozlišení, které navržené oscilátory poskytují, je skutečně specifikovaných 50 pikosekund, přičemž směrodatná odchylka tohoto časového rozlišení je cca 17 %, což je dáno zejména vlivem nesouběhu jednotlivých stupňů oscilátoru. Dosažení lepšího souběhu a přesnosti časového rozlišení by bylo možné pouze za cenu zvýšení velikosti jednotlivých stupňů, a tudíž i zvýšení jejich parazitních kapacit, navazujícího snížení rychlosti oscilátorů, nutnému navýšení proudové spotřeby pro kompenzaci snížené rychlosti a v konečném důsledku nezanedbatelného zhoršení výtěžnosti v případě "pomalých" procesních odchylek. Toto byl jen jeden z mnoha kompromisů učiněných během návrhu, jež dokládají, že specifikace rozlišení 50 pikosekund je na hranici praktické dosažitelnosti pro danou výrobní technologii. Pátá kapitola je zakončena krátkou diskuzí několika alternativních řešení, které byly objeveny během návrhu a které by mohly přispět k řešení některých výše zmíněných problémů nebo k odstranění jednoho z trimovacích kroků.

FRÁNEK, Jakub. *Injection locked ring oscillator design for application in Direct Time of Flight LIDAR*. Brno: Brno University of Technology, Faculty of Electrical Engineering and Communication, Department of Microelectronics, 2021, 194 p. Master's Thesis. Advised by Ing. Vilém Kledrowetz, Ph.D.

# Author's Declaration

| Author:        | Bc. Jakub Fránek                                                                               |

|----------------|------------------------------------------------------------------------------------------------|

| Author's ID:   | 186059                                                                                         |

| Paper type:    | Master's Thesis                                                                                |

| Academic year: | 2020/21                                                                                        |

| Торіс:         | Injection locked ring oscillator design for<br>application in Direct Time of Flight LI-<br>DAR |

I declare that I have written this paper independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the paper and listed in the comprehensive bibliography at the end of the paper.

As the author, I furthermore declare that, with respect to the creation of this paper, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation  $\S$  11 of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll. of the Czech Republic, Section 2, Head VI, Part 4.

Brno .....

.....

author's signature\*

$<sup>^{*}\</sup>mathrm{The}$  author signs only in the printed version.

## ACKNOWLEDGEMENT

I wish to express my gratitude to Ing. Ivan Koudar, Ph.D. for the opportunity to deepen my analog circuit design expertise by writing a thesis about this contemporary topic under his guidance.

I am also grateful to Ing. Tomáš Rozkopal and other design engineers from Analog & Memory IP team at ON Design Czech s.r.o. whose seemingly endless willingness to provide advice was invaluable to me. Last but not least, I want to thank Ing. Vilém Kledrowetz, Ph.D. for his helpful advice on the formal aspects of the thesis.

# CONTENTS

| In       | trod | uction  |                                                                                                      | <b>20</b> |

|----------|------|---------|------------------------------------------------------------------------------------------------------|-----------|

| 1        | Dire | ect Tir | me of Flight LIDAR                                                                                   | 22        |

|          | 1.1  | Syster  | m overview                                                                                           | 22        |

|          | 1.2  | Imagin  | ng methods $\ldots$ | 23        |

|          |      | 1.2.1   | Scanning LIDAR                                                                                       | 23        |

|          |      | 1.2.2   | Flash LIDAR                                                                                          | 25        |

|          |      | 1.2.3   | Comparison                                                                                           | 26        |

|          | 1.3  | Laser   | sources                                                                                              | 26        |

|          |      | 1.3.1   | Wavelength                                                                                           | 26        |

|          |      | 1.3.2   | Output power and eye safety                                                                          | 27        |

|          |      | 1.3.3   | Diode lasers                                                                                         | 28        |

|          | 1.4  | Single  | Photon Avalanche Diodes                                                                              | 29        |

|          |      | 1.4.1   | Avalanche Photodiode                                                                                 | 29        |

|          |      | 1.4.2   | Basic operation of SPAD                                                                              | 30        |

|          |      | 1.4.3   | Timing characteristics                                                                               | 31        |

|          |      | 1.4.4   | Dead time, quenching circuits and afterpulsing                                                       | 32        |

|          |      | 1.4.5   | photon detection efficiency $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$           | . 33      |

|          |      | 1.4.6   | Dark count rate and crosstalk                                                                        | . 35      |

|          |      | 1.4.7   | SPAD imagers and Silicon Photomultipliers                                                            | . 36      |

|          | 1.5  | Time    | Correlated Single Photon Counting                                                                    | . 38      |

|          |      | 1.5.1   | Coincidence counting                                                                                 | . 40      |

| <b>2</b> | Tin  | ne to I | Digital Converters                                                                                   | 43        |

|          | 2.1  | Gener   | al considerations                                                                                    | 43        |

|          |      | 2.1.1   | Full scale and resolution                                                                            | . 43      |

|          |      | 2.1.2   | TDC array architecture                                                                               | . 44      |

|          |      | 2.1.3   | Reverse timing scheme                                                                                | . 45      |

|          |      | 2.1.4   | Sliding scale technique                                                                              | . 46      |

|          | 2.2  | Count   | ter based TDCs                                                                                       | . 47      |

|          | 2.3  | Delay   | Locked Loops                                                                                         | . 48      |

|          |      | 2.3.1   | Delay Line Unit circuits                                                                             | . 51      |

|          | 2.4  | Propa   | agation delay based TDCs                                                                             | . 53      |

|          | 2.5  | Sub-g   | ate delay based TDCs                                                                                 | . 55      |

|          | 2.6  | Clock   | distribution schemes                                                                                 | . 58      |

|          |      | 2.6.1   | Global counting                                                                                      | . 58      |

|          |      | 2.6.2   | Local counting                                                                                       | . 60      |

|          |      | 2.6.3   | Summary                                                                                                                                         |

|----------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | Inje | ction 1 | Locked Oscillators 62                                                                                                                           |

|          | 3.1  | Oscilla | ation criteria $\ldots \ldots 62$      |

|          | 3.2  | LC ta:  | nk based ILO $\ldots \ldots 64$                             |

|          |      | 3.2.1   | Phasor analysis $\ldots \ldots 65$                          |

|          |      | 3.2.2   | Locking range derivation                                                                                                                        |

|          |      | 3.2.3   | Paradox of locking and phase noise performance 70                                                                                               |

|          | 3.3  | Injecti | ion Locked Ring Oscillators                                                                                                                     |

|          |      | 3.3.1   | Ring oscillator time domain analysis                                                                                                            |

|          |      | 3.3.2   | Ring oscillator under injection                                                                                                                 |

|          |      | 3.3.3   | Limitations of the analytical model                                                                                                             |

|          | 3.4  | Injecti | ion Locked Ring Oscillator based TDCs                                                                                                           |

| <b>4</b> | Inje | ection  | Locked Ring Oscillator Modelling 83                                                                                                             |

|          | 4.1  | Motiv   | ation and goals $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 83                                                               |

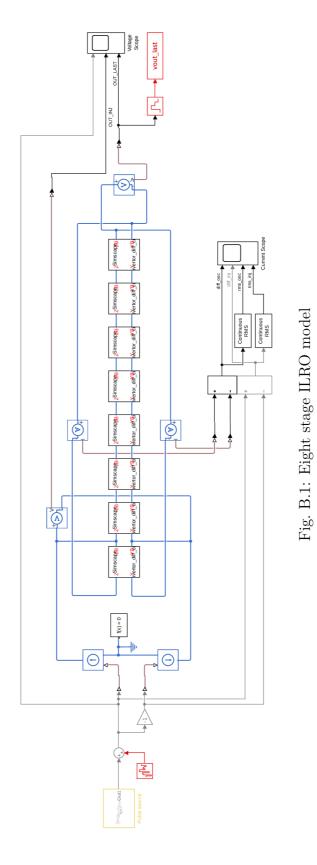

|          | 4.2  | Model   | l overview                                                                                                                                      |

|          |      | 4.2.1   | Differential inverter model                                                                                                                     |

|          |      | 4.2.2   | Injection signal                                                                                                                                |

|          |      | 4.2.3   | Default simulation parameters                                                                                                                   |

|          | 4.3  | Simul   | ation outputs $\ldots \ldots $ 87                           |

|          |      | 4.3.1   | Transient waveforms                                                                                                                             |

|          |      | 4.3.2   | Frequency domain                                                                                                                                |

|          |      | 4.3.3   | Spectrogram                                                                                                                                     |

|          | 4.4  | Analy   | $\operatorname{rses} \ldots 90$ |

|          |      | 4.4.1   | Locking range                                                                                                                                   |

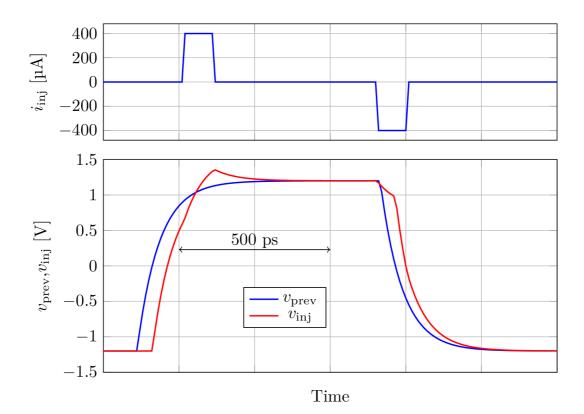

|          |      | 4.4.2   | Time domain measurements $\dots \dots 93$                                           |

|          |      | 4.4.3   | Phase noise                                                                                                                                     |

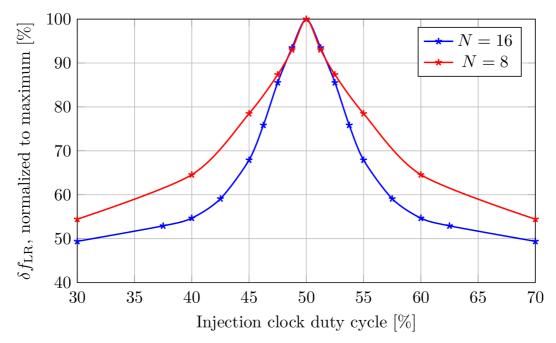

|          |      | 4.4.4   | Injection clock duty cycle                                                                                                                      |

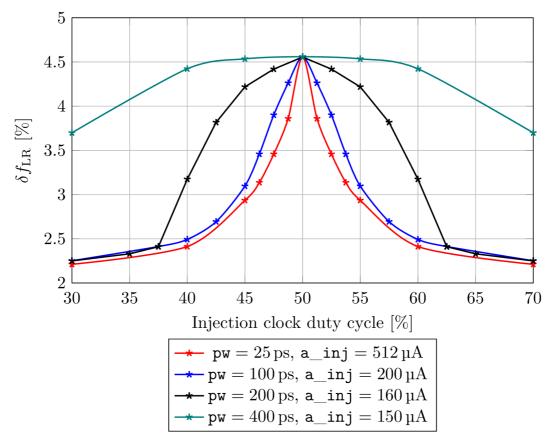

|          |      | 4.4.5   | Injection pulse width                                                                                                                           |

|          |      | 4.4.6   | Summary                                                                                                                                         |

| <b>5</b> | Inje | ection  | Locked Ring Oscillator Design 104                                                                                                               |

|          | 5.1  | Techn   | ology overview $\ldots \ldots 104$            |

|          | 5.2  | Choic   | e of ILRO operating frequency                                                                                                                   |

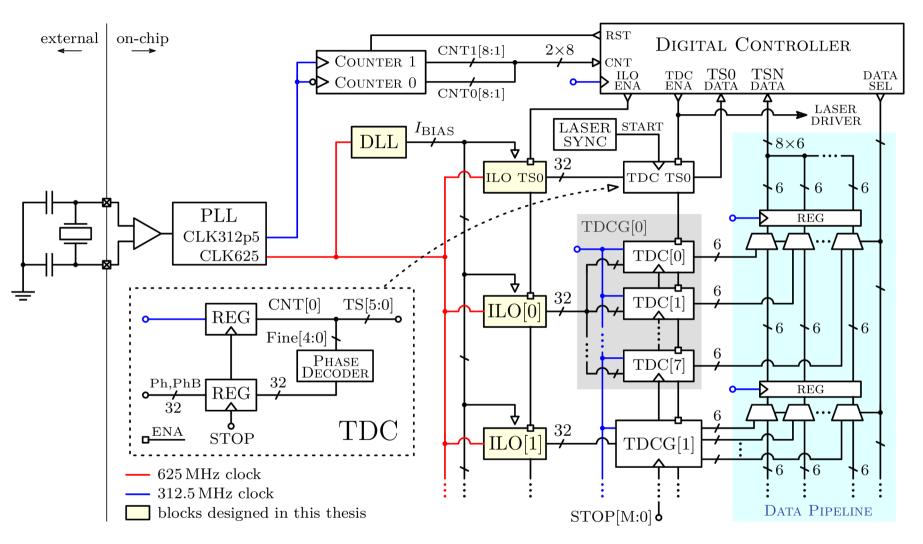

|          | 5.3  | TDC     | architecture overview                                                                                                                           |

|          |      | 5.3.1   | SPAD and TDC array architecture                                                                                                                 |

|          |      | 5.3.2   | TDC conversion timing scheme                                                                                                                    |

|          |      | 5.3.3   | Clock source, PLL and DLL                                                                                                                       |

|          |      | 5.3.4   | ILROs and clock phase latches                                                                                                                   |

|          |      |         |                                                                                                                                                 |

|                              | 5.3.5   | Coarse TDC counters and digital controller | . 116 |

|------------------------------|---------|--------------------------------------------|-------|

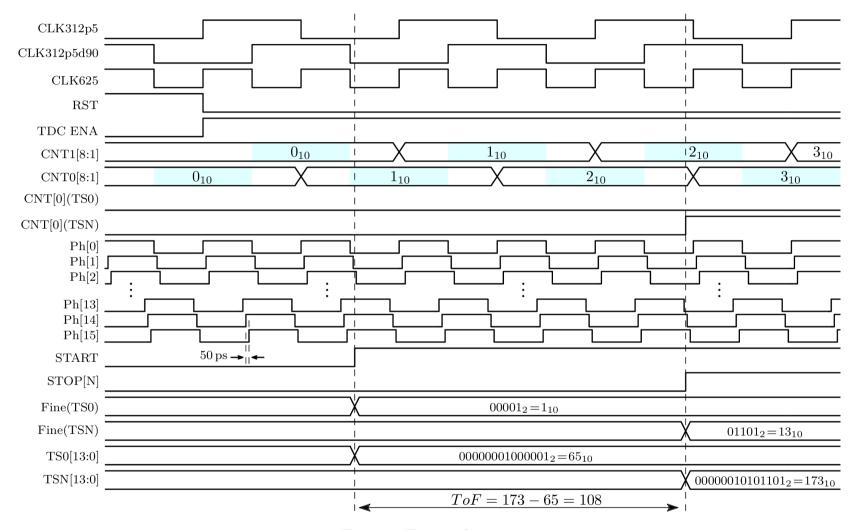

|                              | 5.3.6   | Timing diagram                             | . 117 |

| 5.4                          | Simula  | ation conditions                           | . 120 |

| 5.5                          | Injecti | on locked ring oscillator design           | . 121 |

|                              | 5.5.1   | Ring oscillator design                     | . 121 |

|                              | 5.5.2   | Biasing mirror design                      | . 127 |

|                              | 5.5.3   | Injection circuit design                   | . 129 |

|                              | 5.5.4   | Locking simulations                        | . 133 |

| 5.6                          | Delay   | Locked Loop design                         | . 138 |

|                              | 5.6.1   | Overview                                   | . 138 |

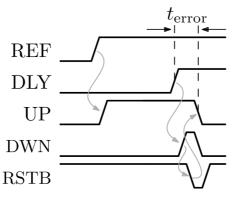

|                              | 5.6.2   | Frequency Phase Detector and Charge Pump   | . 140 |

|                              | 5.6.3   | Voltage to Current converter               | . 146 |

|                              | 5.6.4   | Trimming                                   | . 152 |

| 5.7                          | Top-le  | evel simulations                           | . 159 |

| 5.8                          | Altern  | native solutions                           | . 168 |

| Summary 171                  |         |                                            | 171   |

| Bibliography 173             |         | 173                                        |       |

| Symbols and abbreviations 18 |         | 181                                        |       |

| List of                      | apper   | ndices                                     | 187   |

# LIST OF FIGURES

| 1.1  | DToF LIDAR system diagram                                             | 22 |

|------|-----------------------------------------------------------------------|----|

| 1.2  | Illustration of scanning LIDAR                                        | 23 |

| 1.3  | Illustration of flash LIDAR                                           | 25 |

| 1.4  | Computed NIR atmospheric transmission spectrum from ATRAN $$          | 27 |

| 1.5  | Direct normal solar spectral irradiance at 1.5 air mass               | 28 |

| 1.6  | SPAD I-V characteristic with key stages of the avalanche breakdown    |    |

|      | highlighted                                                           | 30 |

| 1.7  | Typical passive quenching SPAD circuit                                | 30 |

| 1.8  | Two-step PQAR circuit                                                 | 33 |

| 1.9  | PDE as a function of incident photon wavelength for two commercial    |    |

|      | SPAD based Silicon Photomultipliers, biased at $AP = 0.9 \dots \dots$ | 34 |

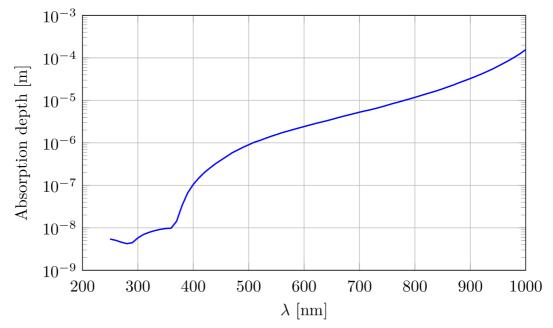

| 1.10 | Mean absorption depth of photons in silicon at 300 K as a function    |    |

|      | of wavelength                                                         | 35 |

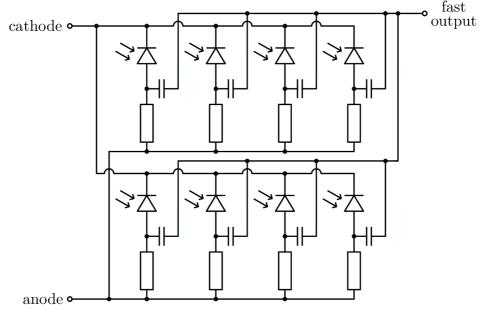

| 1.11 | Simplified SiPM schematic                                             | 37 |

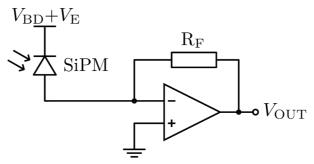

| 1.12 | Standard SiPM readout with a TIA                                      | 38 |

| 1.13 | Illustration of a TCSPC histogram                                     | 39 |

|      | Illustration of coincidence counting                                  | 41 |

| 2.1  | Time of flight of a reflected photon as a function of distance to the |    |

|      | obstacle                                                              | 44 |

| 2.2  | Sliding scale TDC illustration                                        | 47 |

| 2.3  | Asynchronous ripple counter                                           | 48 |

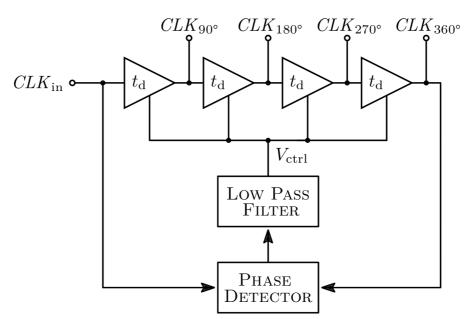

| 2.4  | Delay Locked Loop illustration                                        | 49 |

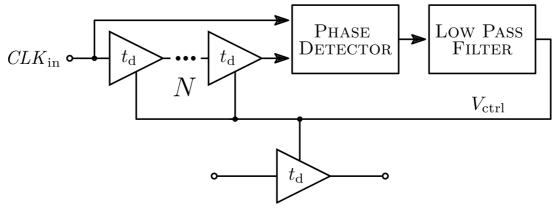

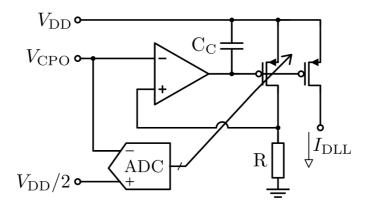

| 2.5  | DLL-assisted PVT immune VCDLU biasing                                 | 49 |

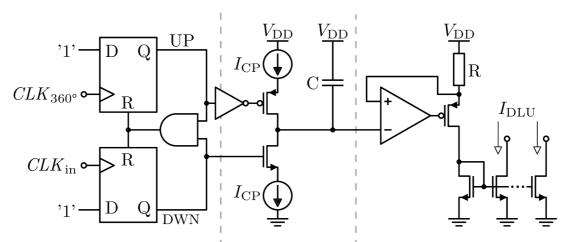

| 2.6  | Simplified charge pump based Delay Locked Loop control circuits       | 50 |

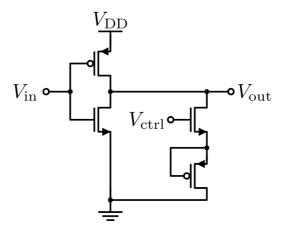

| 2.7  | Current starved inverter                                              | 51 |

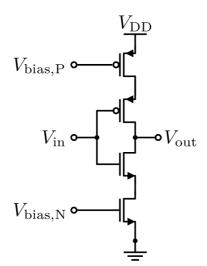

| 2.8  | High linearity Voltage Controlled Delay Line Unit                     | 52 |

| 2.9  | Differential Current Controlled Delay Line Unit                       | 52 |

| 2.10 | Flash TDC illustration                                                | 53 |

| 2.11 | Sliding scale flash TDC illustration                                  | 54 |

| 2.12 | Gated ring oscillator based flash FTDC with a counter based CTDC .    | 55 |

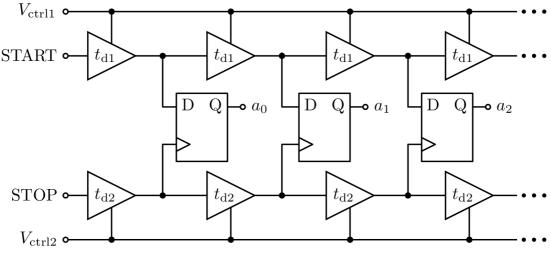

| 2.13 | Simplified Vernier line SFTDC schematic                               | 56 |

| 2.14 | Simplified cyclic Vernier line SFTDC schematic                        | 57 |

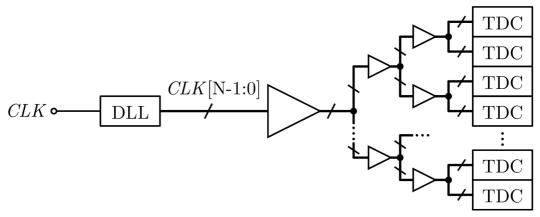

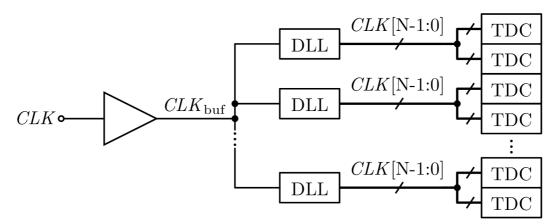

| 2.15 | Global clock counting with single buffer                              | 59 |

| 2.16 | Global clock counting with multiple stage clock tree                  | 59 |

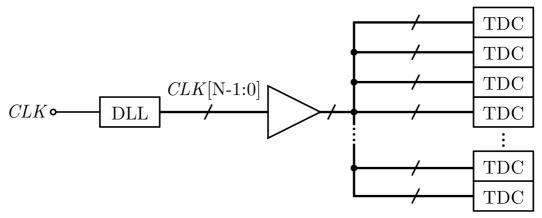

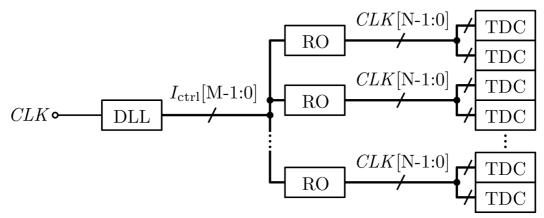

| 2.17 | Local clock counting with DLLs                                        | 60 |

| 2.18 | Local clock counting with ring oscillators                            | 61 |

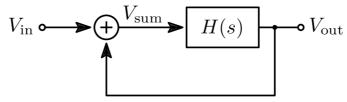

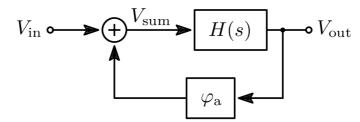

| 3.1  | General feedback system                                               | 62 |

|      |                                                                       |    |

| 3.2  | General feedback system with additional phase shift                               | 63  |

|------|-----------------------------------------------------------------------------------|-----|

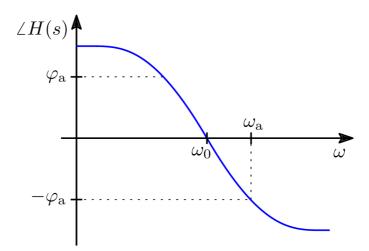

| 3.3  | Phase response of a general feedback system with additional phase shift           | 64  |

| 3.4  | Half circuit of a differential negative resistance LC tank based ILO              | 65  |

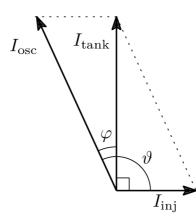

| 3.5  | LC tank ILO current phasor diagram                                                | 66  |

| 3.6  | LC tank ILO current phasor diagram at the edge of the locking range               | 69  |

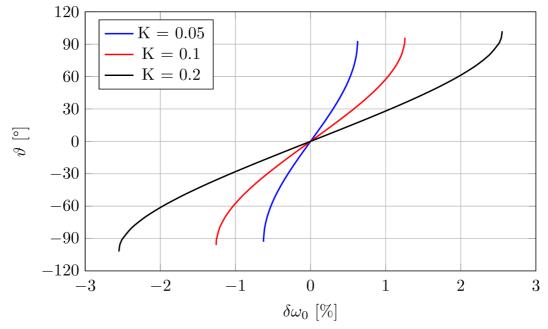

| 3.7  | Injection angle as a function of $\Delta \omega_0$ for various $K$                | 70  |

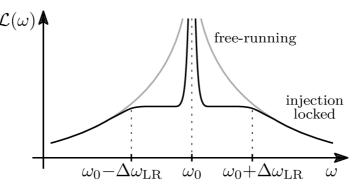

| 3.8  | Phase noise of a free-running and injection locked oscillator                     | 71  |

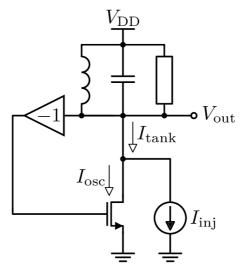

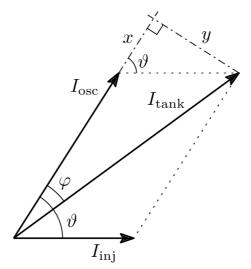

| 3.9  | Differential injection locked ring oscillator model                               | 72  |

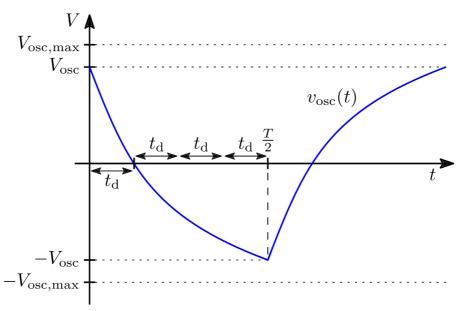

| 3.10 | Ring oscillator model voltage waveform                                            | 73  |

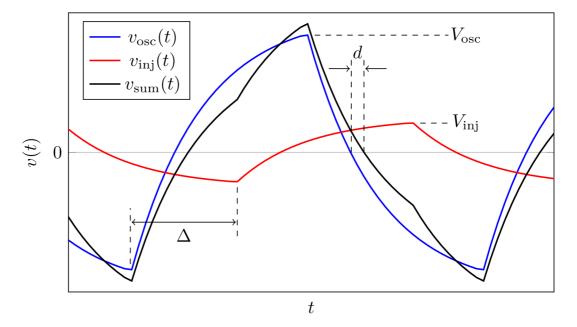

| 3.11 | Time domain based model of injection locking $\ldots \ldots \ldots \ldots \ldots$ | 75  |

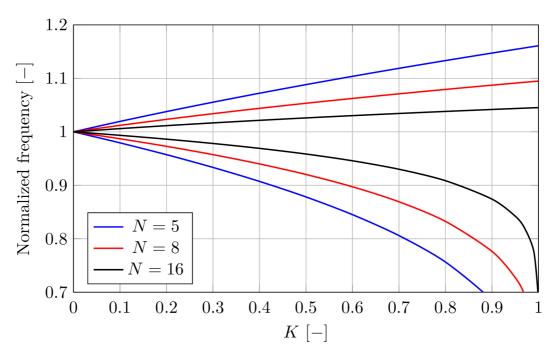

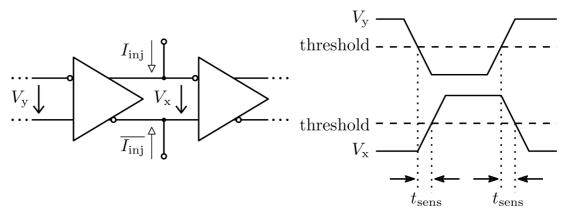

| 3.12 | Locking range of ILRO for various number of stages                                | 78  |

| 3.13 | Ring oscillator injection sensitivity time window                                 | 79  |

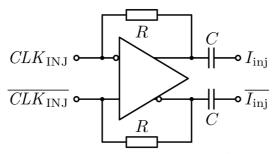

| 3.14 | Pulse injection circuit                                                           | 80  |

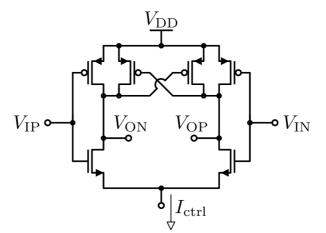

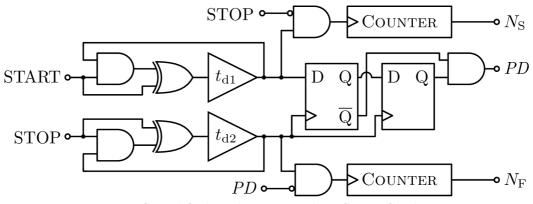

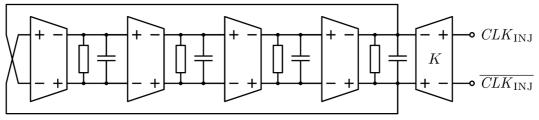

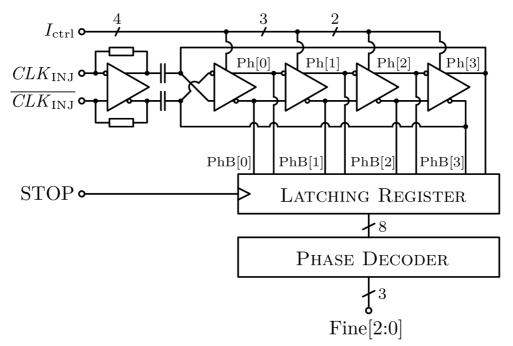

| 3.15 | Differential ILRO based 3-bit flash FTDC                                          | 81  |

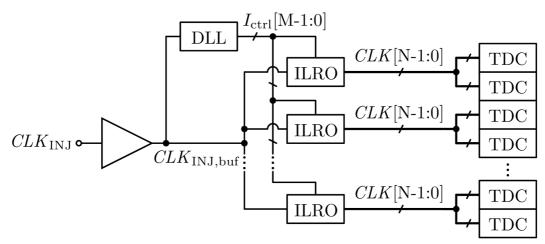

| 3.16 | Local clock counting with ILROs                                                   | 82  |

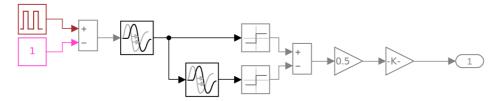

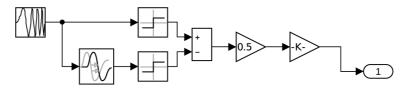

| 4.1  | Differential inverter model in Simulink                                           | 85  |

| 4.2  | Injection pulse train generator                                                   | 86  |

| 4.3  | Injection pulse chirp generator                                                   | 86  |

| 4.4  | ILRO model period of oscillation for $f_{inj} < f_0$                              | 88  |

| 4.5  | ILRO model period of oscillation for $f_{inj} > f_0$                              | 88  |

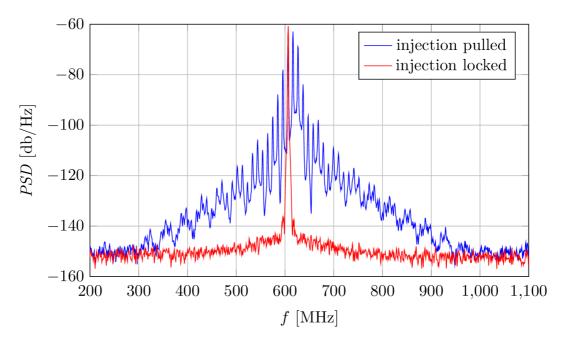

| 4.6  | PSD of ILRO model when injection pulled and locked                                | 89  |

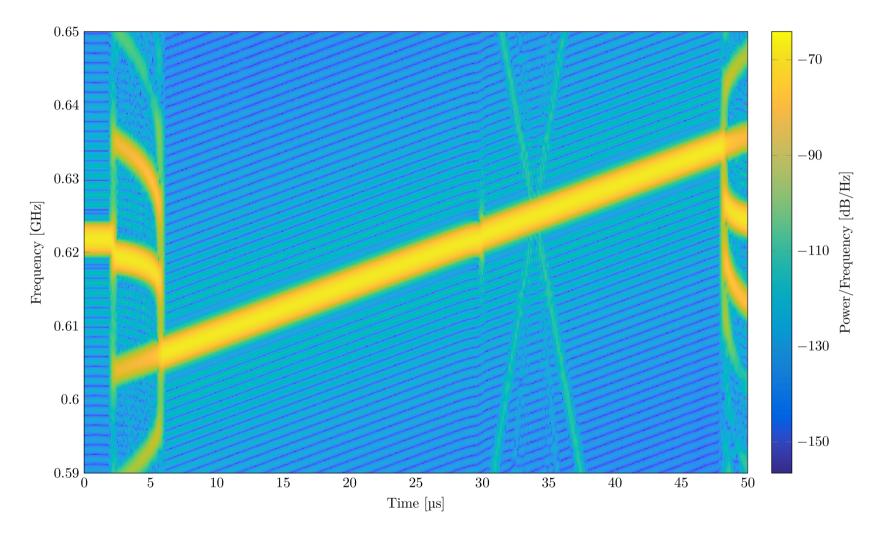

| 4.7  | Spectrogram of a clock phase first harmonic with chirp injection signal           | 91  |

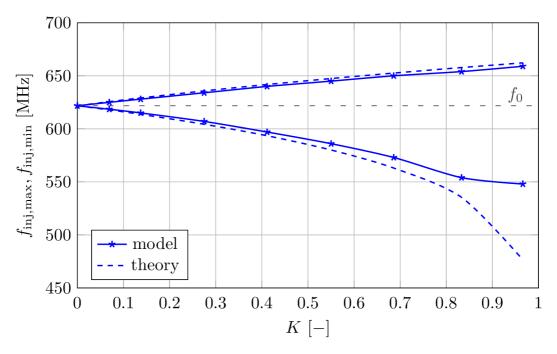

| 4.8  | Locking range of the ILRO model as a function of injection ratio                  | 92  |

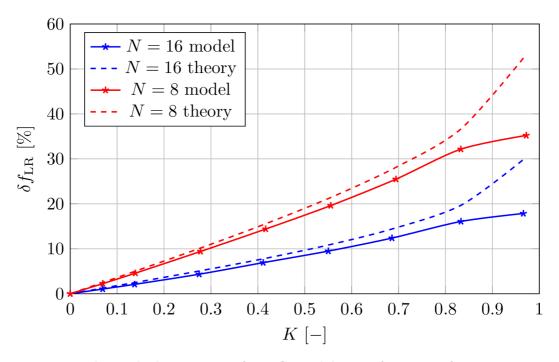

| 4.9  | Relative locking range of ILRO models as a function of injection ratio            | 93  |

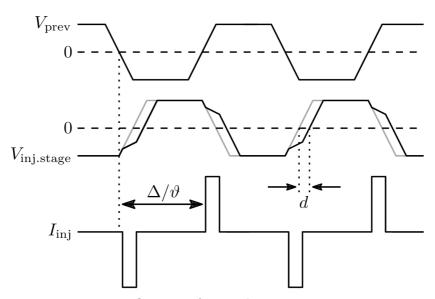

| 4.10 | Definition of time domain measurements                                            | 94  |

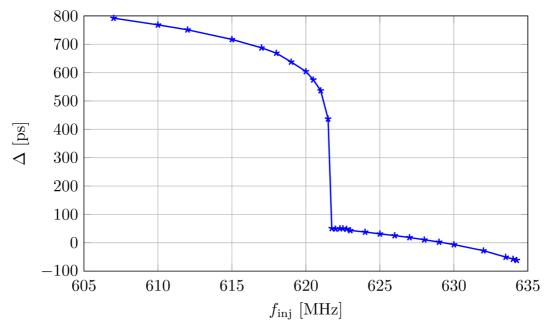

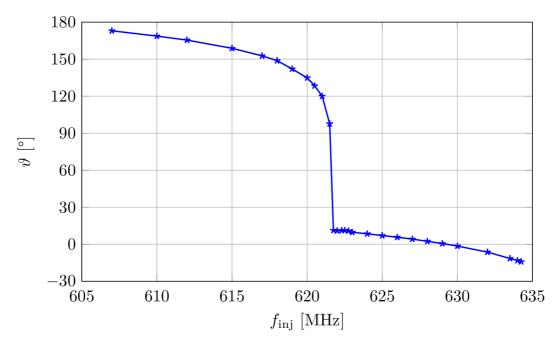

| 4.11 | The phase shift $\Delta$ of the ILRO model as a function of $f_{inj}$             | 95  |

| 4.12 | The injection angle $\vartheta$ of the ILRO model as a function of $f_{\rm inj}$  | 95  |

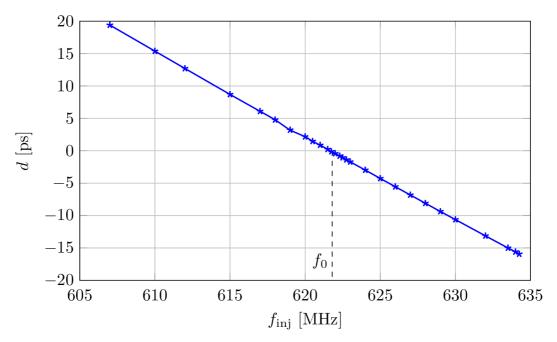

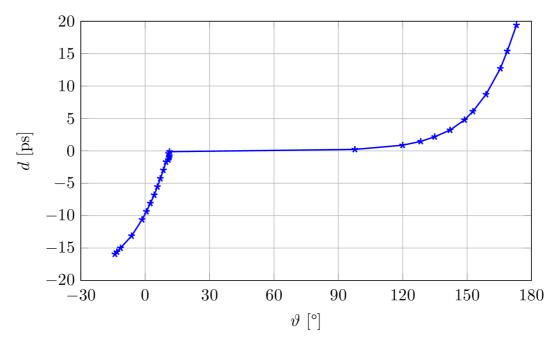

| 4.13 | The zero cross delay $d$ of the ILRO model as a function of $f_{\rm inj}$         | 97  |

| 4.14 | The zero cross delay $d$ of the ILRO model as a function of $\vartheta$ $\ .$     | 97  |

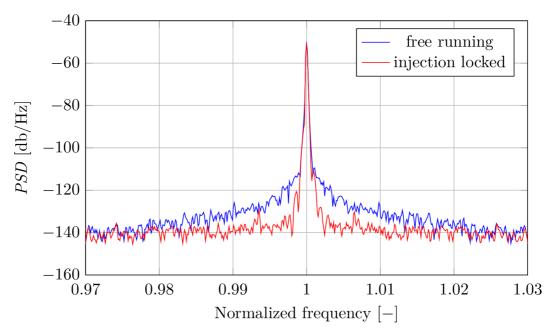

| 4.15 | Power spectral density of a free-running and injection locked ILRO $$ .           | 98  |

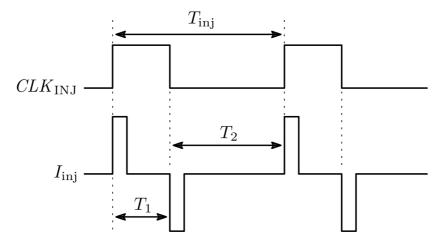

| 4.16 | The effect of injection clock duty cycle on injection pulse timing $\ldots$       | 99  |

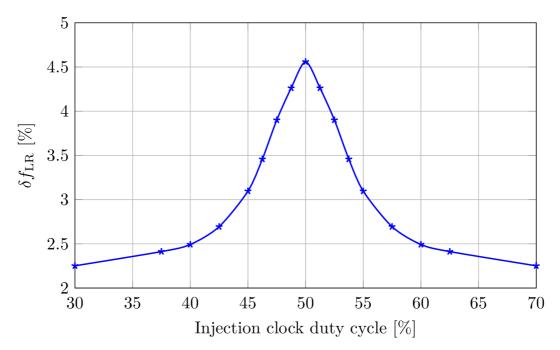

| 4.17 | Relative locking range of the ILRO model as a function of injection               |     |

|      | clock duty cycle                                                                  | 100 |

| 4.18 | Normalized relative locking range of ILRO models as a function of                 |     |

|      | injection clock duty cycle                                                        | 100 |

| 4.19 | ILRO model period of oscillation for $DC = 40\%$ , $f_{inj} > f_0 \dots \dots$    | 101 |

| 4.20 | Relative locking range of the ILRO model for various injection pulse              |     |

|      | sizes                                                                             | 102 |

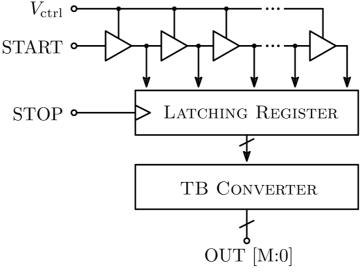

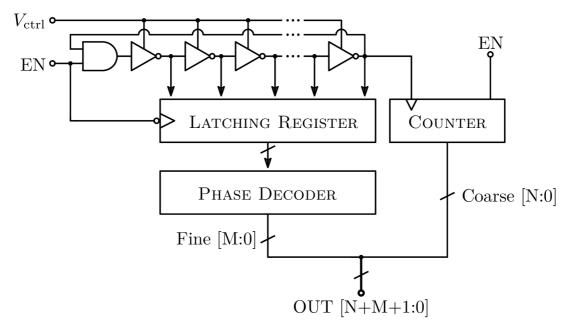

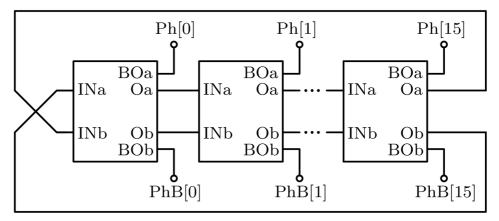

| 5.1  | Overview of an ILRO-based TDC architecture                                        | 108 |

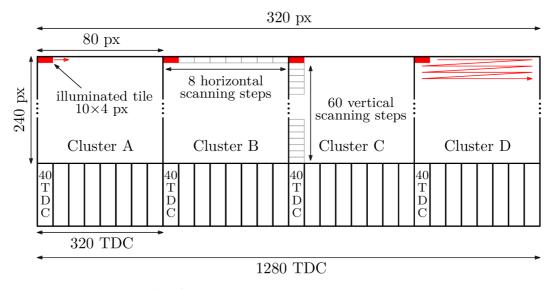

| 5.2  | SPAD & TDC array scanning and converting scheme $\ .$ 109                                  |

|------|--------------------------------------------------------------------------------------------|

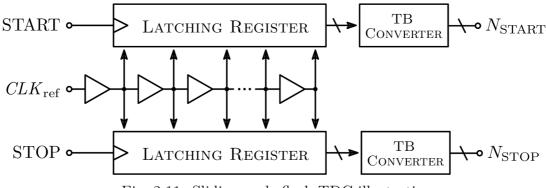

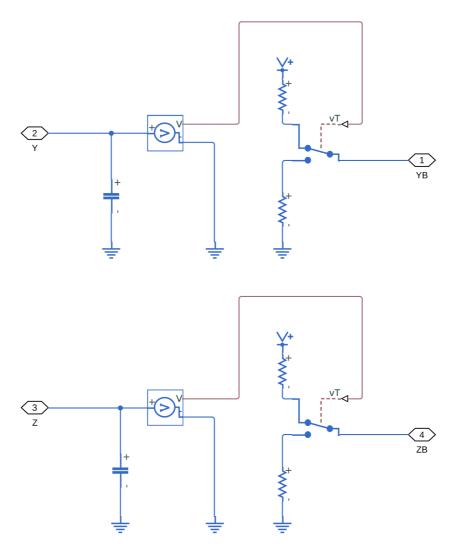

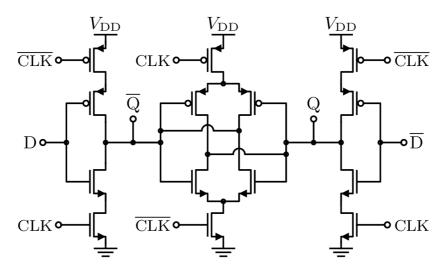

| 5.3  | Differential ILRO clock phase latch example                                                |

| 5.4  | Timing diagram                                                                             |

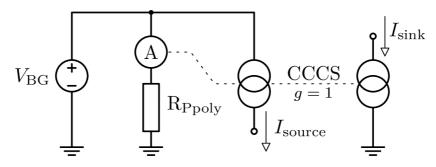

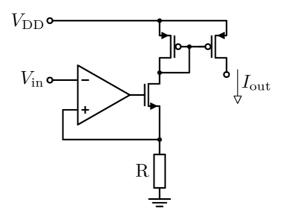

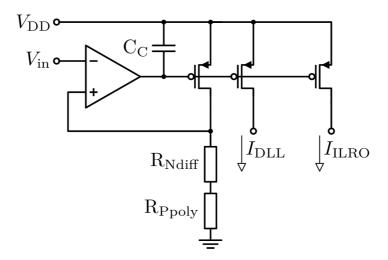

| 5.5  | Realistic biasing current generator                                                        |

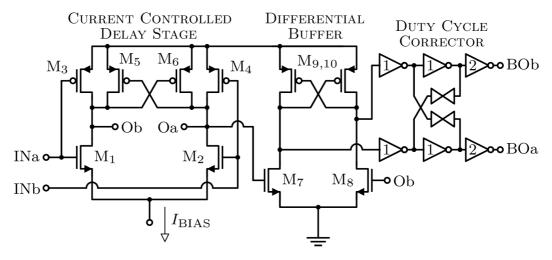

| 5.6  | Buffered differential CCDLU topology                                                       |

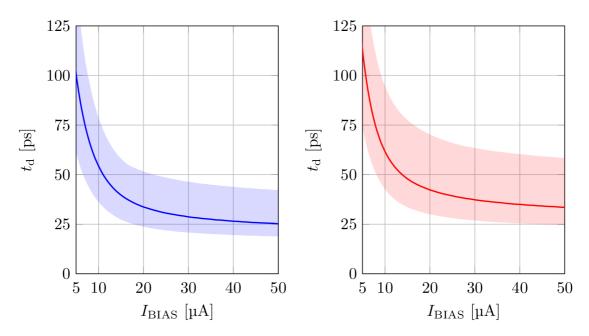

| 5.7  | Simulated propagation delay dependency on biasing current for low                          |

|      | $V_{\rm th}$ (left) and normal $V_{\rm th}$ (right) minimum-sized CCDLU                    |

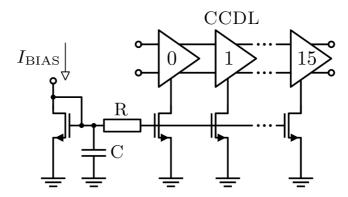

| 5.8  | ILRO connection overview                                                                   |

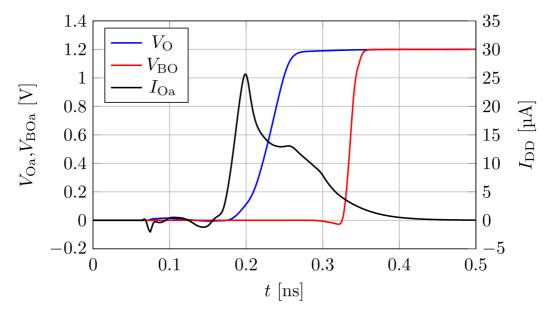

| 5.9  | Simulated CCDLU typical transient signals                                                  |

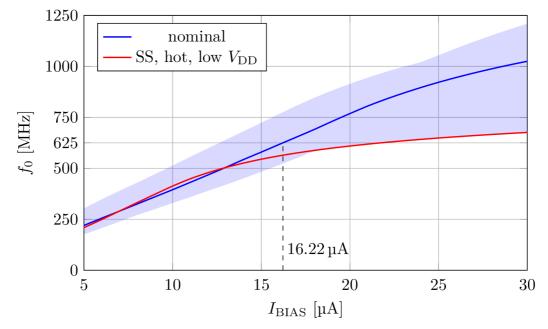

| 5.10 | Free-running frequency $f_0$ as a function of $I_{\text{BIAS}}$ for the designed ILRO125   |

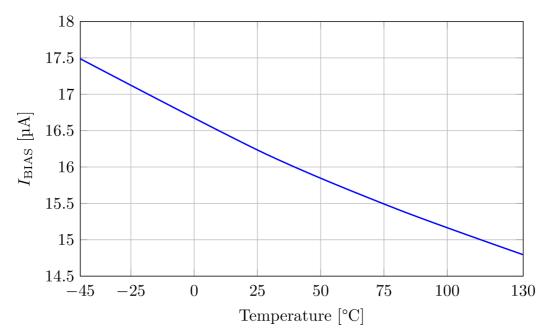

| 5.11 | ILRO nominal biasing current for $f_0 = 625 \text{ MHz} \dots \dots \dots \dots \dots 126$ |

| 5.12 | CCDL NMOS biasing current mirror                                                           |

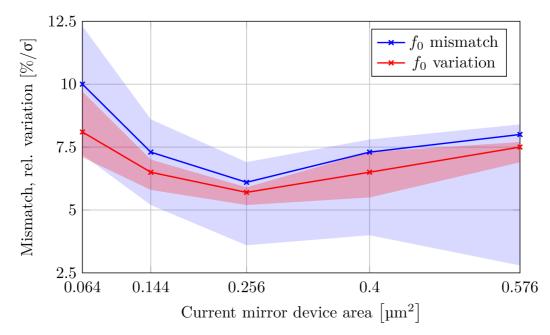

| 5.13 | ILRO free-running frequency variation and mismatch for various bi-                         |

|      | asing current mirror device sizes                                                          |

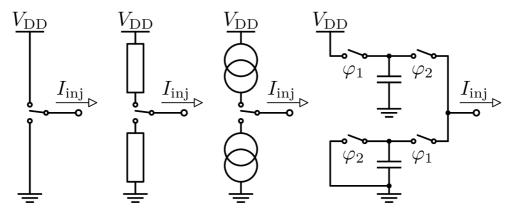

| 5.14 | Alternative injection methods                                                              |

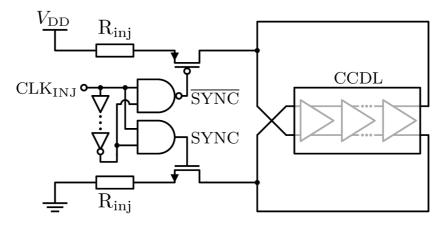

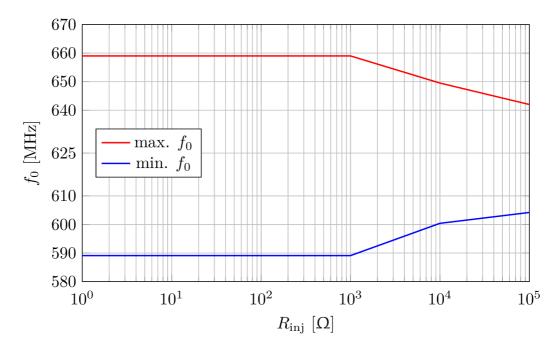

| 5.15 | Designed injection circuit                                                                 |

| 5.16 | Locking range of the designed ILRO for various sizes of $R_{inj}$ 131                      |

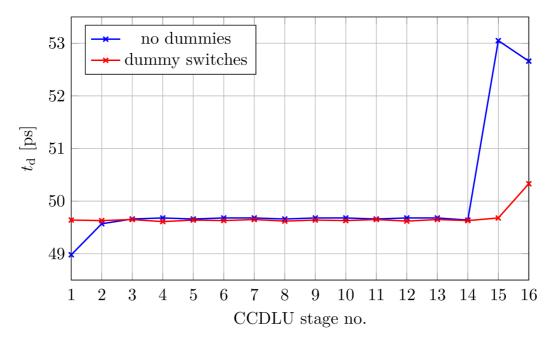

| 5.17 | Propagation delay distribution within the ILRO with and without                            |

|      | dummy switches, when free-running at $f_0 = 625 \text{ MHz}$                               |

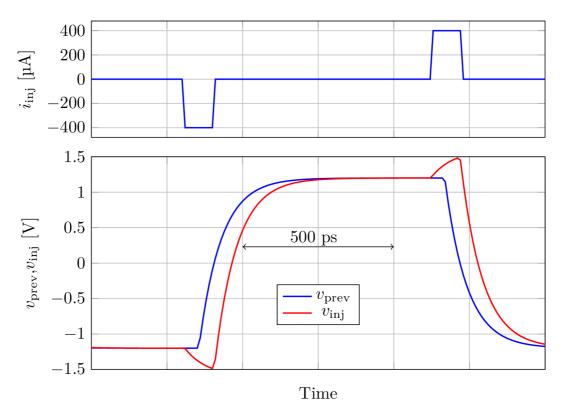

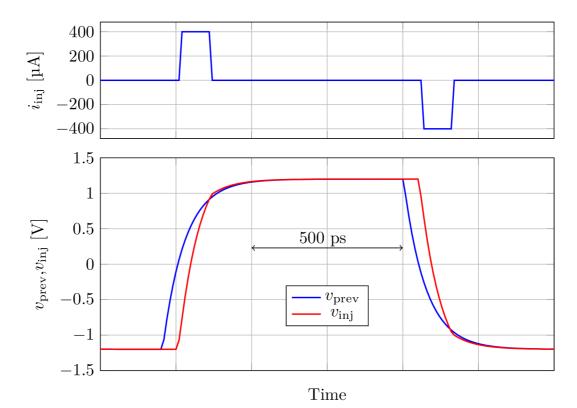

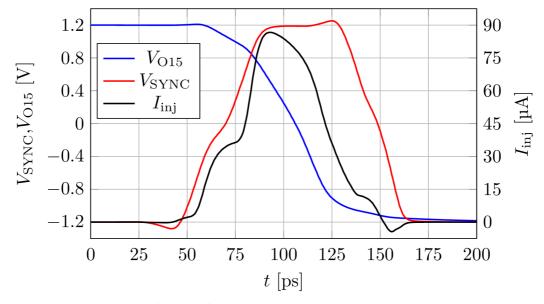

| 5.18 | Typical waveforms of the injection stage voltage, the injection pulse                      |

|      | and the injected current for a locked ILRO of $f_0 = 590 \text{ MHz}$ 133                  |

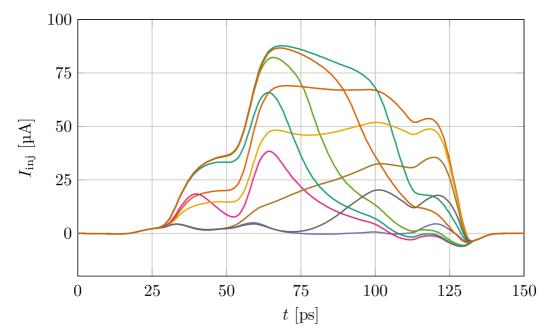

| 5.19 | Various waveforms of injected current into ILROs of various $f_0$ when                     |

|      | locked to 625 MHz                                                                          |

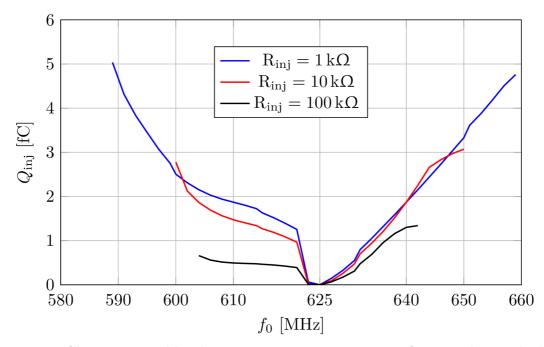

| 5.20 | Charge injected by the injection circuit into an ILRO per cycle once                       |

|      | locked to $625\mathrm{MHz}$ as a function of initial free-running frequency $135$          |

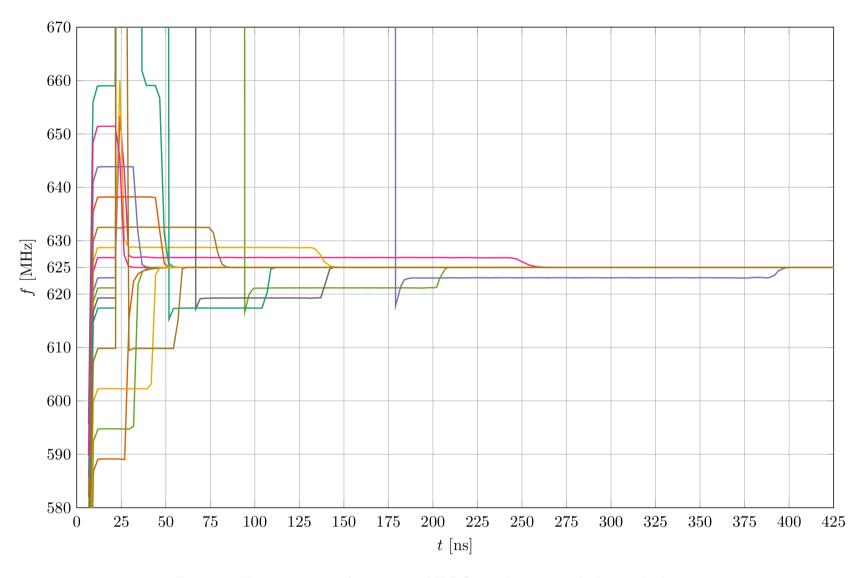

| 5.21 | Instantaneous frequency of ILROs with various $f_0$ during locking 136                     |

| 5.22 | Injection locking process                                                                  |

| 5.23 | Simplified overview of the DLL                                                             |

| 5.24 | FPD signal sequence                                                                        |

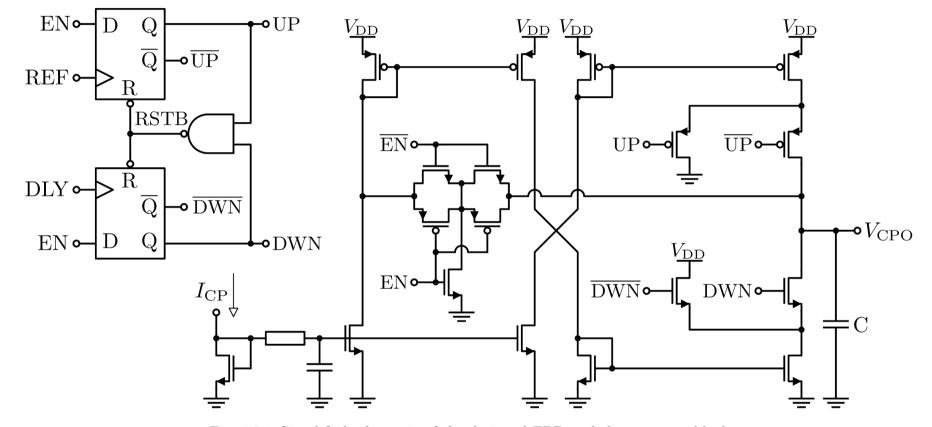

| 5.25 | Simplified schematic of the designed FPD and charge pump block $$ .<br>. 141               |

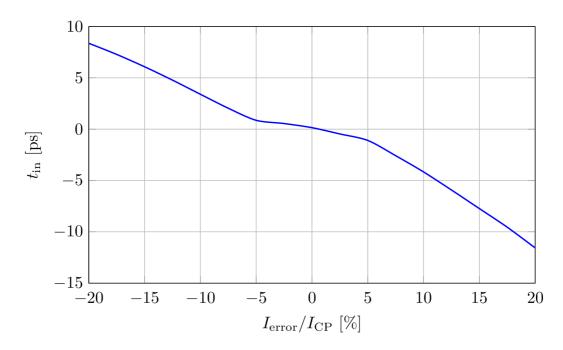

| 5.26 | FPD input phase shift as a function of charge pump current source                          |

|      | mismatch when connected in a DLL                                                           |

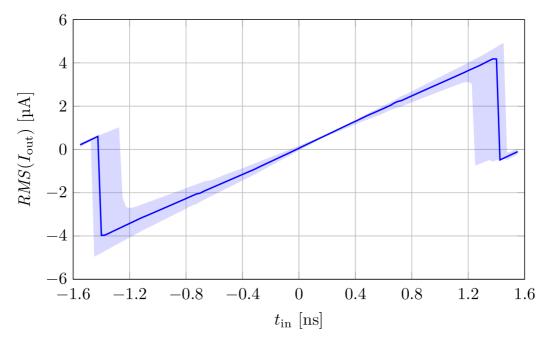

| 5.27 | RMS charge pump output current as a function of FPD input phase                            |

|      | shift                                                                                      |

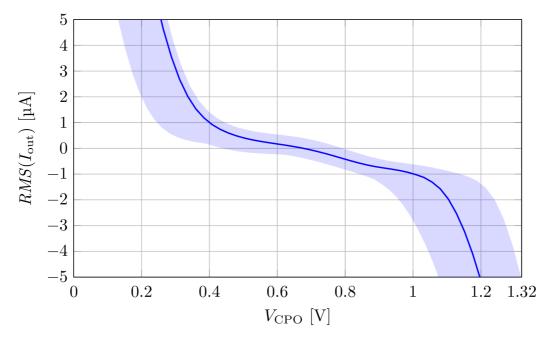

| 5.28 | $RMS$ charge pump output current as a function of $V_{\rm CPO}$ when UP                    |

|      | and DWN signals are both active                                                            |

| 5.29 | Standard V-to-I converter                                                                  |

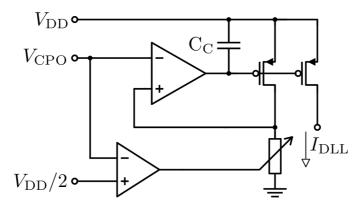

| 5.30 | Designed DLL V-to-I converter                                                              |

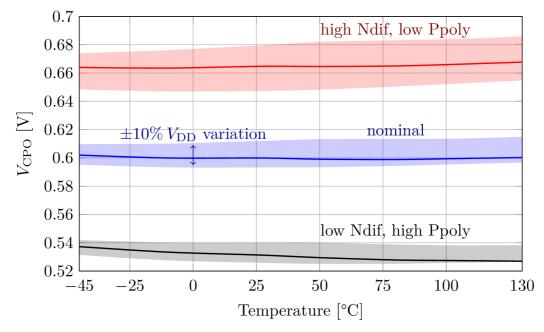

| 5.31 | Charge pump output voltage stability over temperature for nominal          |     |

|------|----------------------------------------------------------------------------|-----|

|      | and cross resistor corners                                                 | 150 |

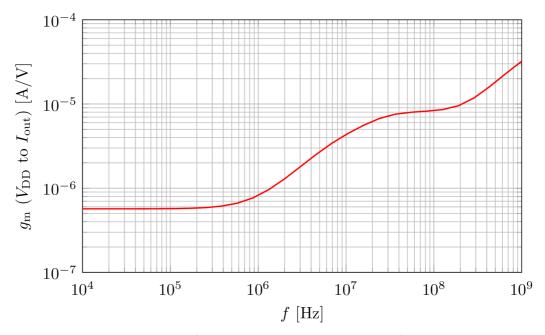

| 5.32 | Transconductance from $V_{\rm DD}$ to output current of V-to-I converter's |     |

|      | current mirror                                                             | 151 |

| 5.33 | Designed DLL V-to-I converter with trimmed devices highlighted             | 154 |

| 5.34 | Trimmed PMOS current mirror devices                                        | 156 |

| 5.35 | Error of the injection stage propagation delay as a function of the        |     |

|      | free-running frequency error                                               | 158 |

| 5.36 | ILRO trimming trim code and residual error histograms                      | 158 |

| 5.37 | DLL start-up waveforms                                                     | 159 |

| 5.38 | ILRO free-running frequency over VT variation when biased by a             |     |

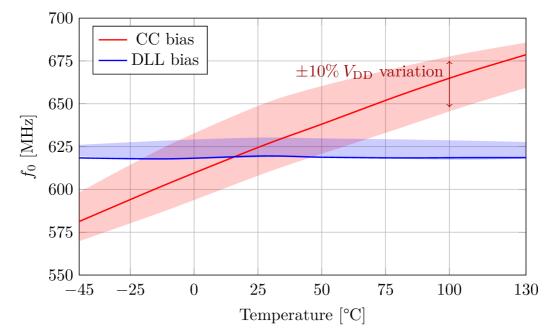

|      | constant current versus a DLL                                              | 160 |

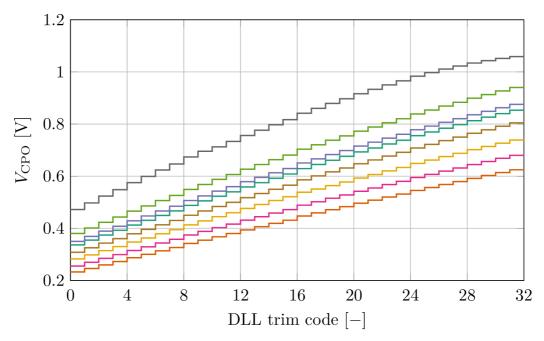

| 5.39 | DLL trim code sweep across process corners                                 | 161 |

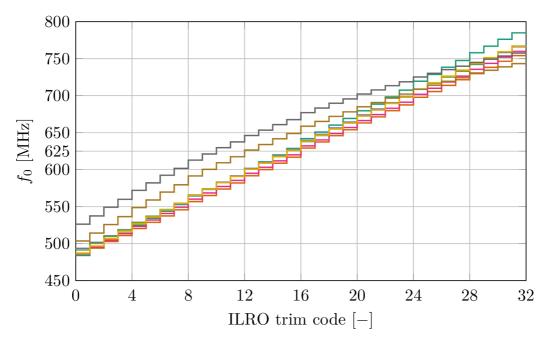

| 5.40 | ILRO trim code sweep across process corners                                | 162 |

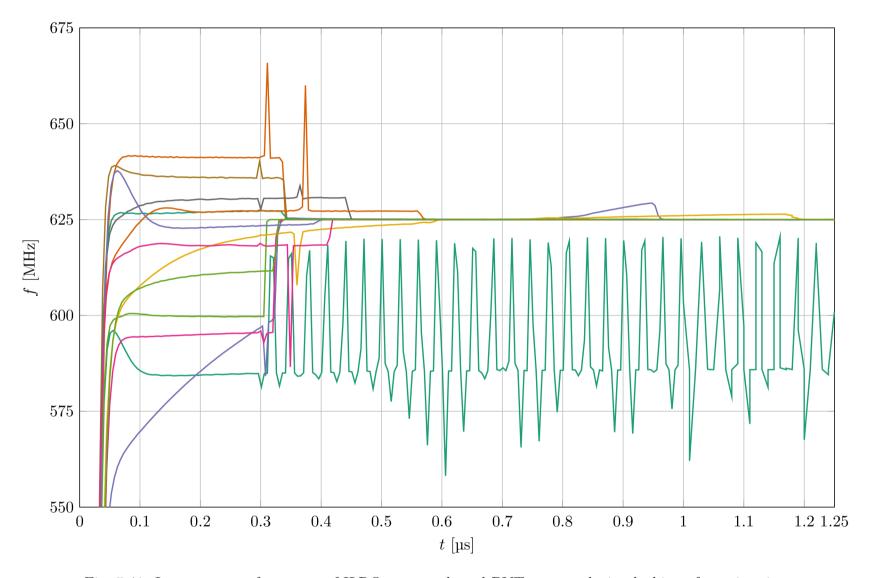

| 5.41 | Instantaneous frequency of ILRO across selected PVT corners during         |     |

|      | locking after trimming                                                     | 164 |

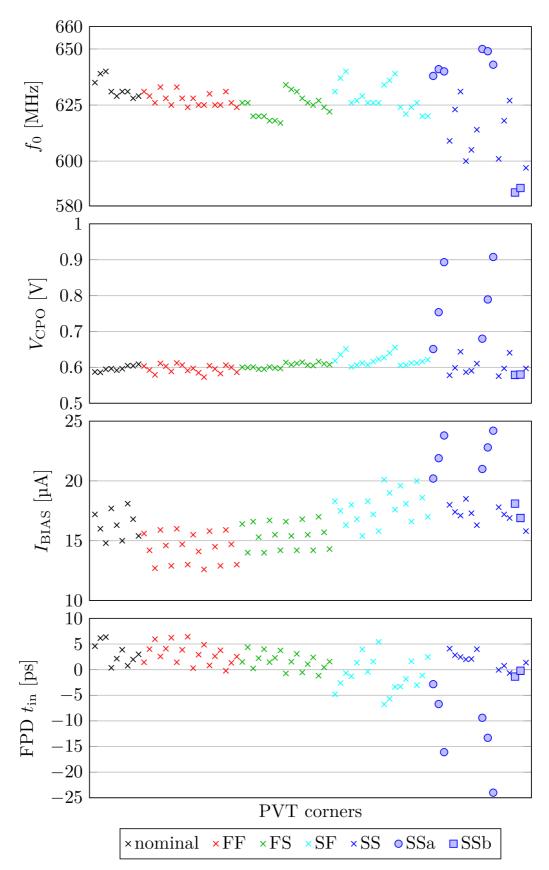

| 5.42 | PVT corner overview of free-running trimmed ILRO biased by a               |     |

|      | trimmed DLL                                                                | 165 |

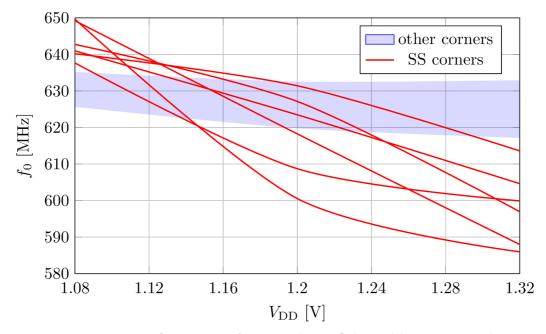

| 5.43 | Free-running frequency of trimmed ILRO biased by a trimmed DLL             |     |

|      | as a function of $V_{\text{DD}}$                                           | 166 |

| 5.44 | Jitter histogram of a locked and unlocked ILRO $\ . \ . \ . \ . \ .$       | 168 |

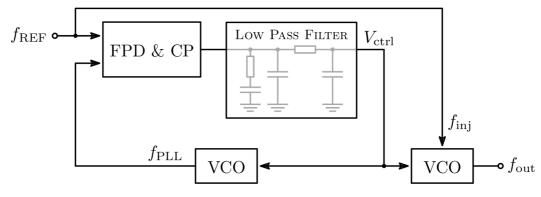

| 5.45 | PLL based ILRO biasing                                                     | 169 |

| 5.46 | Alternative dynamic ADC-based DLL trimming method                          | 170 |

| 5.47 | Alternative dynamic VCR-based $V_{\rm CPO}$ stabilizing method             | 170 |

|      |                                                                            |     |

# LIST OF TABLES

| 4.1 | Default simulation parameters                                                |

|-----|------------------------------------------------------------------------------|

| 5.1 | Benefits and detriments of higher number of ILRO stages 106                  |

| 5.2 | Clock phases of 16-stage differential ILRO                                   |

| 5.3 | Default simulation conditions                                                |

| 5.4 | CCDLU device sizes                                                           |

| 5.5 | ILRO performance                                                             |

| 5.6 | FPD performance                                                              |

| 5.7 | V-to-I converter performance                                                 |

| 5.8 | Overview of V-to-I converter's current mirror trimmed PMOS units $\ . \ 157$ |

# INTRODUCTION

The invention of the Single Photon Avalanche Diode (SPAD) and its integration in standard Complementary Metal Oxide Semiconductor (CMOS) fabrication processes has enabled rapid growth of a wide range of new imaging applications. The single photon sensitivity and picosecond level temporal jitter of SPADs has been utilized for low illuminance imaging, positron emission tomography, various types of spectroscopy, fluorescence lifetime imaging microscopy, diffuse optical tomography or Direct Time of Flight (DToF) based Light Detection and Ranging (LIDAR).

The DToF based LIDAR measures the time interval between the instant when a laser pulse was transmitted, illuminating the scene, and the instant the reflected photons have returned and were detected by the receiver. The time interval is then used to calculate the distance to the obstacle. Compared to other 3D imaging and ranging techniques such as ultrasonic sensors, stereo vision cameras or millimetre wave radars, LIDAR can provide superior resolution and competitive dynamic range, while requiring less computing power and operating reliably in environments with uncontrolled ambient light or low illuminance conditions. This is achieved by utilizing *Time Correlated Single Photon Counting* (TCSPC), a statistical technique capable of restoring photon arrival times with picosecond resolution.

The superior spatial and longitudinal resolution of LIDAR has attracted attention from the automotive industry in particular, as it not only allows the detection of road traffic, but also relatively small obstacles such as pillars, wires or road defects at a distance. This information can be used by the *Advanced Driver Assistance System* (ADAS), which incorporates advanced cruise control, autonomous emergency braking, pedestrian detection, forward collision warning etc. As new car assessment programs across the world are expanding their safety rating criteria to include the safety of pedestrians as well as the passengers, it is expected that in the near future, safety systems like ADAS will be commonplace in cars across all price points. An even more advanced driving system, autonomous driving, is another application for LIDAR technology, as proven by Waymo, which uses a 360° LIDAR based computer vision to operate their driverless car prototypes [1].

The main disadvantage of LIDAR has historically been its cost and size. To scan the whole scene with a sufficient *Signal to Noise Ratio* (SNR), laser scanning is needed, which requires complex optomechanical systems. The recent efforts are therefore focused on bringing the cost and the size down by integrating the whole scanning system on a single CMOS integrated circuit.

A DToF measurement system consists of the following main parts: the laser source, the photodetector, the *Time to Digital Converter* (TDC) and the data processing circuits. The TDC measures the time interval between the transmitted laser pulse and its reflected echo, and as such is one of the most critical parts, determining the dynamic range and the resolution of the system. The key challenges of TDC design are achieving the sub-nanosecond resolution, and the generation and routing of the counting signals in a power efficient manner.

The chapter 1 of this thesis will introduce the general principles of DToF based LIDAR systems, the operation of SPADs or the TCSPC technique. The chapter 2 will focus on TDCs, their key parameters, practical design techniques and their various implementations. In the chapter 3, a novel approach to TDC architecture, utilizing *Injection Locked Oscillators* (ILOs) to achieve power efficient clock generation and resolution on the order of tens of picoseconds will be described. In chapter 4, a MATLAB model of an *Injection Locked Ring Oscillator* (ILRO) will be presented. Finally, in chapter 5, an ILRO will be designed and simulated in a 65 nm CMOS processing technology.

## 1 DIRECT TIME OF FLIGHT LIDAR

This chapter will provide an overview of DToF LIDAR systems, as well as basic insight into imaging strategies, laser sources, photodetectors and signal processing techniques used in contemporary art. TDCs will be described later in chapter 2 in more detail.

### 1.1 System overview

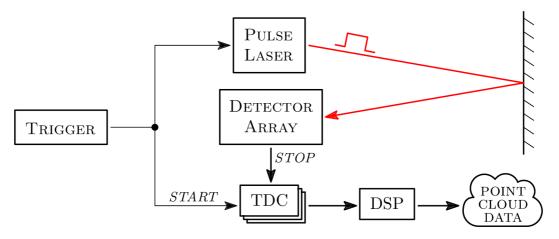

The basic structure and operation of DToF LIDAR systems is illustrated on Figure 1.1.

Fig. 1.1: DToF LIDAR system diagram

An electronically driven pulsed laser emits a light pulse, illuminating the scene, also known as the *Field of View* (FoV). The same trigger signal, which fired the laser pulse, is used to start the TDC measurement. As the travelling pulse hits objects inside the FoV, a portion of the pulse, which (amongst other factors) depends on the distance, the incident angle or the reflectivity of the surface of the object, is reflected back and hits the detector. Upon detection, the detector produces an electrical pulse, freezing the TDC. The TDC consequently outputs a digital value, corresponding to the time interval between the firing of the laser and the detection of its reflection. This time is called the *Time of Flight* (ToF), and can be used to determine the distance travelled by the light pulse, which is simply

$$d = \frac{c}{2} \cdot ToF \tag{1.1}$$

where d is the distance to the obstacle and c is the speed of light. The division by 2 needs to be included, because the reflected photons have travelled the distance between the LIDAR device and the obstacle twice. A Digital Signal Processing (DSP) block performs various filtering and noise rejection techniques on the TDC readings, namely *Time Correlated Single Photon Counting* (TCSPC) which is described in more detail in section 1.5. The processed data can be then used to build a "point cloud", which is the desired representation of the FoV with the distance measurements represented by points in a 3D coordinate space.

# 1.2 Imaging methods

Since the final output of the LIDAR system is a 3D point cloud of the objects in the FoV, and the FoV for applications such as automotive spans tens of degrees in angular size, the method of its illumination has to be carefully considered.

There are two main types of DToF LIDAR differing in their approach to FoV illumination. In this section, these methods will be briefly described and compared according to their advantages.

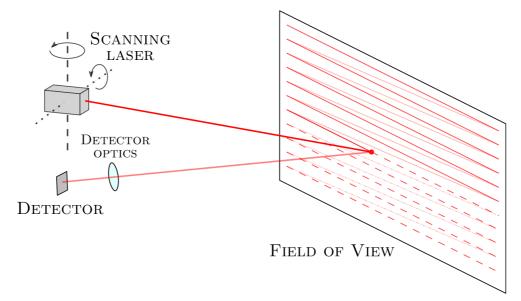

### 1.2.1 Scanning LIDAR

The "scanning LIDAR" utilizes a laser beam with low angular divergence to scan the FoV step by step using dual axis scanning. The beam needs to be steered across the FoV over time, which is a challenge of its own. The precision and speed of the scanning mechanism are now another factor determining the overall performance of the system, and depending on the implementation, the scanning system can add both significant costs and reliability issues.

Fig. 1.2: Illustration of scanning LIDAR

There are two main types of scanners which utilize actual mechanical movement to direct the laser beam. The movement can be done with electrical stepper motors, which has the benefit of a wide FoV but brings larger cost, power consumption, size and reliability issues. In these cases, a polygon mirror reflecting the laser beam can be rotated instead of the whole laser or LIDAR assembly, as demonstrated in [2]. Despite the disadvantages, this is still the dominant method of scanning in automotive applications because of its long range performance and wide, up to 360° FoV [3, p.12].

A promising alternative are *Micro-electro-mechanical System* (MEMS) actuators, which steer the laser beam using electrically driven micromirrors. The advantages of such optical systems are clear: low weight, compactness, low cost and low power consumption. Although the technology is already proven at short to medium range (25 m range demonstrated by [4]), it has not been able to reach the FoV and the long range of rotational scanners. This technique is however getting increased attention and the company Innoviz Technologies is claiming they achieved 600 m range and  $73^{\circ} \times 20^{\circ}$  FoV with their new product [5], which could be the best commercially released MEMS LIDAR so far.

Optical Phased Array (OPA) is a novel fully solid state method of beam steering. The operating principle is identical to phased array antennas, where the direction of the beam is determined by the phase difference between neighbouring transmitters, allowing constructive interference of the electromagnetic waves in the desired direction and destructive interference in others. OPA scanners share the same advantages of MEMS scanners, but since there are no moving parts at all in OPA scanners, they can reach even higher scanning speeds (100 kHz reported by [6, p.409]) and better reliability. However, the method does have issues with insertion power loss of the phase shifting waveguides. Quanergy is a company aiming to provide a commercial automotive OPA based LIDAR in the near future, claiming 120° FoV, 150 m range and mean time between failure (MTBF) of more than 100 000 h [7].

Finally, another novel option of implementing fully solid state beam steering is to use an array of *Vertical Cavity Surface Emitting Lasers* (VCSELs) and a special optical lens. An identical lens can be used for the detector array, which has the same size and number of pixels as the VCSEL array. Because the arrays and the optical systems match, by activating certain pixels of the laser array, a small section of the FoV is illuminated and the reflected photons arrive at the corresponding detector array pixels. Ibeo Automotive, a company which has implemented multiple products of this type, calls the method "sequential flash", as it combines the philosophy of both scanning and flash LIDAR. Their product ibeoNEXT Generic contains 10240 pixels in both the VCSEL and detector array, and claims 250 m range, FoV ranging up to  $60^{\circ} \times 30^{\circ}$  and angular resolution as good as  $0.05^{\circ}$  [8].

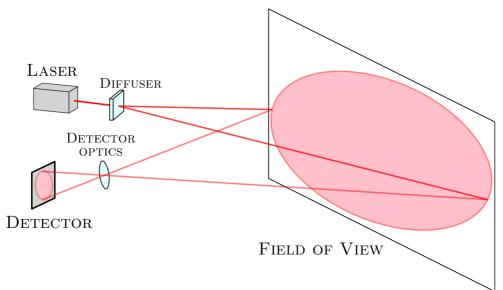

### 1.2.2 Flash LIDAR

The other approach known as "flash LIDAR" uses an optical diffuser to increase the angular divergence of the laser, illuminating the scene as a whole in a single pulse. The challenge is therefore shifted away from the transmitter to the detector, which needs to detect the reflections of the diffused laser, and the optical system, which needs to restore the directional information in order to determine the distance to obstacles in various regions of the FoV. Detectors positioned at the focal plane of a lens are called *Focal Plane Array* (FPA) detectors. A natural advantage of the flash LIDAR is the absence of moving parts and high refresh rate, as the whole FoV is illuminated at once.

Fig. 1.3: Illustration of flash LIDAR

The detector optical system is designed to match the divergence of the laser diffuser, so that all the detector array pixels are illuminated simultaneously. The spatial resolution is therefore determined by the pixel density of the array, which is limited by the process node, the size of the chip and cost.

The main challenge with flash LIDAR is the SNR. Because the output power of the laser is spread across the whole FoV, the reflections are weaker. Therefore there is a clear inverse relationship between the size of the FoV and the maximum detectable range. Special attention has to be given to the detector array design in order to maximize its optical sensitivity and efficiency. Another potential issue is the power consumption and associated thermal dissipation. With flash LIDAR, a large number of TDCs need to be active simultaneously, requiring significant power and producing large amount of heat.

An example of a flash LIDAR system implementation is described in [9], where a  $252 \times 144$  detector array was used, achieving 50 m range.

### 1.2.3 Comparison

Although currently most widely used automotive LIDAR systems are based on rotating mirror scanners, "there is a quite general agreement that mechanically scanning LIDARs need to move towards a solid-state version" [3, p.11]. While their up to 360° wide FoV is desirable, the size, cost and overall unreliability and maintenance complexities, which are critical factors in automotive systems, will outweigh the benefits in the future.

If solid state systems are to be compared, there are promising solutions on both the scanning and flash LIDAR side, as well as somewhere in between like the sequential flash technology. Generally though, it can be said that flash LIDAR seems to be better suited for short to medium range applications, which require high frame rate. The fact that the whole FoV is illuminated and detected virtually simultaneously is also beneficial for automotive, where the LIDAR system is moving relative to the surrounding objects at high velocity, as in such applications, scanning the FoV (an inherently slower process) can cause movement artefacts and distortions in the resulting image.

On the other hand, scanning LIDAR solutions promise higher maximum detectable range, as the output power of the laser is focused into a much smaller angular diameter, at the cost of slower frame rate. Further development of fast scanning OPA systems could however erase this disadvantage.

### **1.3** Laser sources

The laser source is a key part of the DToF LIDAR system, as its parameters define or contribute to many performance characteristics of the overall product. Quantities like peak output power, wavelength, pulse with, spectral purity, power efficiency, size, weight and many others are of interest.

### 1.3.1 Wavelength

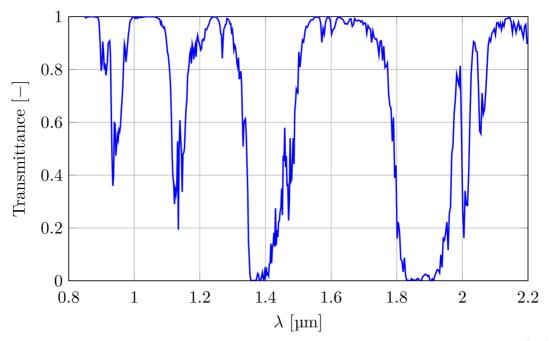

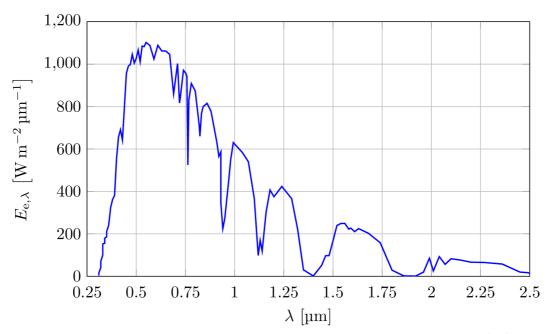

Perhaps the most important of these specifications is the wavelength. Naturally, wavelengths invisible to human eyesight are necessary. In order to transmit the laser pulse as far as possible and subsequently differentiate the reflected photons from the surrounding ambient light, a wavelength with both high atmospheric transmittance (see Figure  $1.4^1$ ) and low solar irradiance (see Figure 1.5) needs to be chosen. These two conditions do not necessarily go hand in hand, therefore a compromise is necessary.

$<sup>^1\</sup>mathrm{ATRAN}$  parameters: altitude 2500 ft, latitude 39°, 2 atmospheric layers, zenith angle 20° [10]

Fig. 1.4: Computed NIR atmospheric transmission spectrum from ATRAN [10]

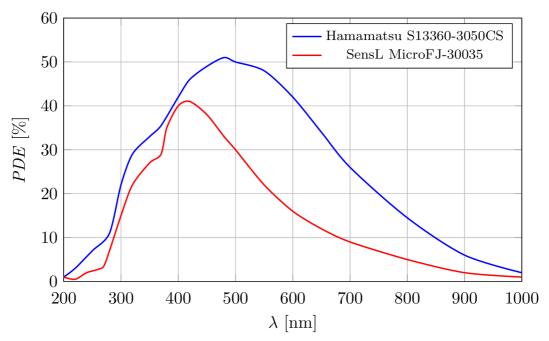

There are three regions of interest: 0.8 to  $0.95 \,\mu\text{m}$ ,  $1.06 \,\mu\text{m}$  and  $1.55 \,\mu\text{m}$  [3, p.18]. The third region would be the ideal one in terms of the distance to the optical range (due to safety concerns, as will be detailed later in this section), the high atmospheric transmittance and the low solar irradiance in the region, but it is outside the optical window of silicon (more details in subsection 1.4.5) and requires InGaAs or InP detectors, which are expensive and due to processing technology limitations do not reach pixel densities comparable to traditional silicon nodes [11].

The most commonly utilized range is the 0.8 to 0.95 µm one. Although it suffers from power limitations due to eye safety, slightly worse atmospheric transmittance and potentially larger solar activity (although there is a noticeable dip around 0.93 µm, as visible on Figure 1.5), silicon based detectors are the most sensitive to electromagnetic radiation in this region and offer best sensitivity. The cost efficiency of CMOS processes is vastly superior to more exotic InGaAs technologies and as such lasers working at these wavelengths are chosen for primarily economical reasons.

### 1.3.2 Output power and eye safety

Another important specification of the laser source is the peak output power transmitted by the pulse. The higher the peak power transmitted by the laser, the higher the power of the reflection, and the higher the probability of its detection. This improves the SNR of the system, and effectively increases the maximum detectable range.

Fig. 1.5: Direct normal solar spectral irradiance at 1.5 air mass [12]

The relationship between the transmitted and collected power is described by the "LIDAR equation" [11, p.16]:

$$P_{\rm c} = \frac{\rho}{\pi R^2} P_{\rm t} A_{\rm d} \cos(\theta) e^{-2\alpha R}$$

(1.2)

where  $P_{\rm c}$  is the collected power,  $\rho$  is the reflection constant, R is the distance to the reflector,  $P_{\rm t}$  is the transmitted power,  $A_{\rm d}$  is the detector optical receiving area,  $\theta$ is the incident angle respective to surface normal and  $\alpha$  is the absorption coefficient. It is clear that R is the most dominant factor.

The limit to the peak optical power is however regulated by eye safety standards such as IEC 60825-1, which determine the *Maximum Permissible Exposure* (MPE) limits, commonly expressed as the maximum allowable exposure time for a given irradiance (given in Watts per cm<sup>2</sup>) for the given wavelength.

Because LIDAR systems need to be safe under all conditions (Class 1 as defined by IEC 60825-1), the MPE limits are quite strict especially for the *Near Infrared* (NIR) range. To decrease the energy delivered to a unit area and meet the standards, either the pulse length can be decreased, or, for flash LIDAR systems, the diffusion angle can be increased so that the energy is spread over larger FoV.

### 1.3.3 Diode lasers

While the use of fiber or microchip lasers in LIDAR systems is possible (and they offer superior pulse rate and pulse widths as well [3, p.21]), the most widely used devices are diode lasers because of their compactness and price. This is especially

the case for systems relying on an array of lasers, as semiconductor diode lasers are the only economical option of fabricating laser arrays.

Semiconductor diode lasers come in two types: *Edge Emitting Laser* (EEL) and *Vertical Cavity Surface Emitting Laser* (VCSEL). EELs are well established diode lasers, based on PN or PIN junctions. The laser shines from the edge, i.e. in parallel to the plane of the silicon wafer it is constructed from. After fabrication, EELs need to be cleaved and coated with reflective materials on the sides to create a cavity with high optical gain. A disadvantage is that the beam they produce is not spherical and needs to be shaped with optical components [13].

VCSELs have been receiving increased attention recently. As the name suggests, the beam produced by the VCSEL device is emitted in a direction perpendicular to the top surface of the semiconductor die. Instead of using reflective coating, the mirrors are made from thin layers of planar Bragg reflectors. In [14], InGaAs Bragg reflectors were used to produce a 940 nm VCSEL.

The direction of the beam is a significant advantage for testing, as VCSEL devices can be tested before the wafer is cleaved, which is faster and more economical. The beam produced by VCSELs is also spherical even in the absence of additional lens [14] and less divergent. Finally, VCSEL arrays enable technologies like OPA scanners [15] or sequential flash imaging, which were discussed previously in subsection 1.2.1. The main challenge in current VCSEL development is the heat generation and transfer, as it is the factor limiting the maximum power or the VCSEL array size [16].

## **1.4** Single Photon Avalanche Diodes

The Single Photon Avalanche Diode (SPAD), also known as Geiger-mode Avalanche Photodiode (GAPD), is the dominant photodetector used in DToF LIDAR systems. It is capable of detecting a single photon with a high temporal resolution (on the order of low tens of picoseconds), while also being compatible with standard CMOS processes, which is critical for the viability of commercial products.

In this section, the operation and characteristics of SPADs will be described in more detail, in order to understand the implications for the LIDAR system architecture and performance.

### 1.4.1 Avalanche Photodiode

The SPAD is structurally nearly identical to the Avalanche Photodiode (APD). The APD consists of a PN junction, operated in the reverse region, close to but not above the SPAD breakdown voltage  $(V_{BD})$ , which is usually between 10 to 50 V [17].

A depletion region is created, where no charge carriers exist and virtually no current flows through the junction. As soon as an incoming photon hits the depletion region, it can be absorbed, generating an electron-hole pair, which is immediately separated by the electric field in the depletion region. If the reverse voltage and the power of the incident light are both high enough, the generated charge carriers multiply along the way via impact ionization, producing an avalanche.

The intensity of the avalanche is proportional the power of the incident light, therefore the APD provides both the ToF information as well as an analog current representation of the intensity of the reflection. In order to convert the current to voltage while preserving the resolution of both time and intensity, a *Trans-impedance Amplifier* (TIA) capable of satisfying high bandwidth, high gain and low noise requirements is required.

### 1.4.2 Basic operation of SPAD

Contrary to the APD, which is biased below  $V_{\rm BD}$ , the SPAD is biased above  $V_{\rm BD}$  in the so-called Geiger mode. The name comes from the Geiger-Müller tube, which operates in a similar manner. The difference between the applied reverse voltage and  $V_{\rm BD}$  is the SPAD excess bias voltage ( $V_{\rm E}$ ), also known as the overvoltage, and it commonly ranges from 2 to 7 V.

While the avalanche in APDs eventually stops on its own, the avalanche in the SPAD devices is self-sustaining, as the PN junction breaks down completely and the impact ionization multiplication process produces an evergrowing number of charge carriers. In order to save the diode from overheating and self-destruction, the avalanche has to be quenched externally.

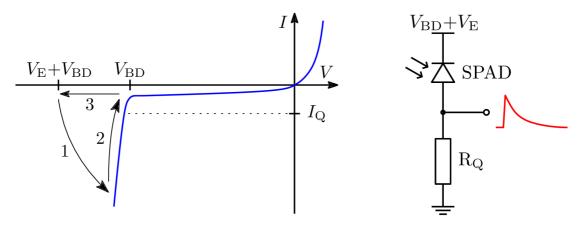

Fig. 1.6: SPAD I-V characteristic with key stages of the avalanche breakdown highlighted

Fig. 1.7: Typical passive quenching SPAD circuit

The avalanche breakdown mechanism in SPADs will be described in more detail. Figure 1.6 depicts an I-V characteristic of a SPAD, including the three main phases of its operation, and Figure 1.7 shows a typical SPAD circuit connection with passive quenching. At the start of the cycle, there is no current flowing through the diode and the full  $V_{\rm BD}+V_{\rm E}$  voltage is applied across the junction in reverse. While this voltage exceeds  $V_{\rm BD}$ , the diode can exist in this pseudo-stable state for an extended period of time, as long as no charge carriers exist inside the depletion region. As soon as a charge carrier appears inside the depletion region, a run-away avalanche develops and the current through the diode spikes within a few tens of picoseconds, moving the operating point of the diode from the pseudo-stable state to the steady state I-V curve (phase 1 – seeding and spreading). The current spike is fed into the quenching resistor  $R_Q$ , producing a growing voltage drop at the expense of the voltage across the diode (phase 2 – quenching). As the voltage across the diode decreases, the diode current eventually becomes lower than the *latching current*  $(I_Q)$ , the avalanche is no longer self-sustaining and it stops shortly thereafter. When there are no more charge carriers in the depletion region left, the junction capacitance of the diode is charged to  $V_{\rm BD}+V_{\rm E}$  and the diode can detect incident photons again (phase 3 - recharge).

Since the optical gain of the SPAD is theoretically infinite (a single photon can produce a self-sustaining avalanche), the information about the power of the incident light provided by the APD is traded off for single photon sensitivity and superior temporal resolution (on the order of low tens of picoseconds). Because the SPAD is essentially a digital photodetector, the read-out circuitry is also significantly simpler. The digital STOP pulse (required by the TDC, as depicted by Figure 1.1) can be provided with a simple fast positive-feedback inverter gate connected directly to the SPAD as opposed to a more complex TIA.

### **1.4.3** Timing characteristics

Perhaps the key characteristic of the SPAD is the timing jitter, which quantifies the statistical fluctuation of the delay between the photon arrival time and the SPAD response. The timing jitter essentially defines the best possible achievable temporal resolution of the DToF LIDAR system containing the SPAD device. It is commonly expressed as the *Full Width at Half Maximum* (FWHM) of the statistical distribution of the SPAD reaction time. Most published SPAD implementations report under 100 ps FWHM jitter [17, p.7], and a FWHM timing jitter as low as 7.8 ps has been achieved in [18].

The timing uncertainty arises from several factors. According to [19, p.14], "the most important timing factor is whether the carrier is generated in the depletion region itself, or if it must diffuse into the depletion region". This diffusion process follows exponential distribution. If and once the avalanche is started, the impact

ionization events follow Gaussian distribution (for example because of thermal vibrations etc.) and contributes some cumulative uncertainty [20, p.31], therefore it is important to detect the avalanche with the following circuitry as soon as possible to minimize the jitter accumulation.

### 1.4.4 Dead time, quenching circuits and afterpulsing

The time it takes for the diode to be quenched and recharged after detection is called the *dead time*, because during this time, the SPAD is unable to detect any incident photons.

If a passive quenching and recharging circuit as shown on Figure 1.7 is used, the quenching resistor  $R_Q$  has to be sized carefully. High values of the resistance speed up the quenching phase at the expense of the recharging phase and vice versa. There is an optimum value of resistance which minimizes the dead time, usually in the region of tens of k $\Omega$ , but a dead time shorter than a few microseconds is impossible to achieve with resistor based passive quenching [21].

This is not necessarily a negative aspect, as having a quenching circuit which quenches and recharges the SPAD too quickly is undesirable because of an effect called *afterpulsing* [19, p.14]. Fabrication defects inside the PN junction can act as traps in the forbidden energy band, which become filled with charge carriers once the avalanche builds up. The relaxation time of these traps can be as long as tens of nanoseconds, depending on the quality of the fabricated SPAD, which places a minimum dead time constraint. For example, suppose the SPAD was quenched and recharged virtually instantly, i.e. well within a nanosecond. The excited traps would relax several nanoseconds later, releasing the trapped carriers back into the depletion region, starting another avalanche. This "false positive" afterpulse would be indistinguishable from avalanches caused by incident photos, acting as a timecorrelated noise source.

Transistor current sources can be used for passive quenching as well, providing some level of control over the length of the phase, but thick oxide *Metal Oxide Semiconductor* (MOS) devices have to be used, as SPAD diodes are biased with relatively high voltage (10 V and more).

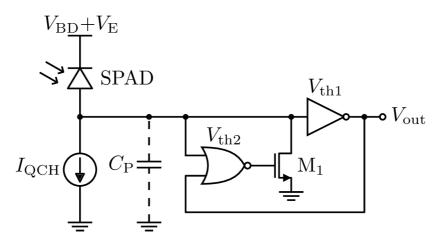

The current state of the art is commonly based on *Passive Quenching Active Recharge* (PQAR) circuits, an example of which from [22] is depicted on Figure 1.8. When the avalanche starts, the anode of the SPAD is rapidly pulled high, quenching the diode, and the inverter output goes low. The parasitic capacitance  $C_{\rm P}$ , which represents the total capacitance of the devices connected to this node as well as the free charge carriers in the PN junction of the SPAD, is slowly discharged by the current  $I_{\rm QCH}$ , which is smaller than  $I_{\rm Q}$ , guaranteeing that afterpulsing cannot

Fig. 1.8: Two-step PQAR circuit [22]

occur. This slow discharge phase continues until the voltage at the anode of the SPAD crosses  $V_{TH2}$ . At that point the NOR gate output goes high, turning  $M_1$  on, which discharges the rest of the parasitic capacitance quickly, recharging the diode junction capacitance and completing the detection cycle as the invertor gate output goes low again, shutting  $M_1$  off.

The advantage of this two-step PQAR circuit is the ability to control the dead time via  $I_{\text{QCH}}$  as necessary (low  $I_{\text{QCH}}$  safely prevents afterpulsing at the cost of longer dead time).

According to a survey of current art [23], the dead time of actively recharged SPADs usually ranges from 10 to 100 ns, and a 6 ns dead time has been achieved by [22]. It has to be noted that a large part of the decrease of dead time has been caused by the progress of SPAD manufacturing, as higher quality processes decreased the chance of afterpulsing dramatically and the recharge phase could be hastened [24]. This is demonstrated by [25], where a dead time of 8 ns was reached with an afterpulsing probability of 0.08%.

#### 1.4.5 photon detection efficiency

To quantify the quality of a SPAD diode, its photon detection efficiency (PDE) can be evaluated. The PDE is defined as a product of the geometric fill factor (FF) and the photon detection probability (PDP), which is, in turn, a product of avalanche probability (AP) and quantum efficiency (QE) of the SPAD [24]:

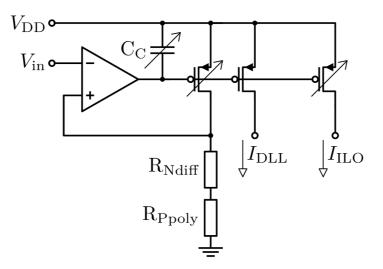

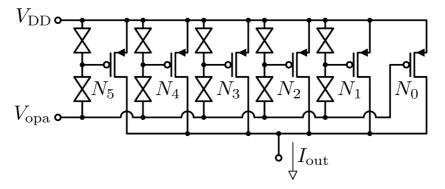

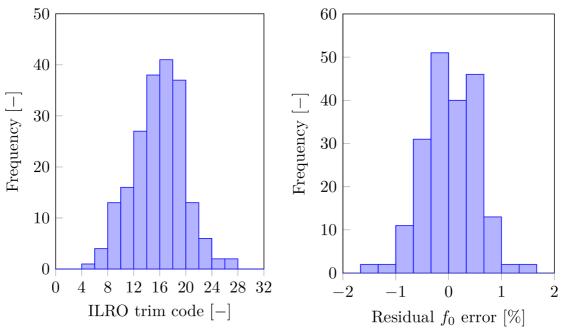

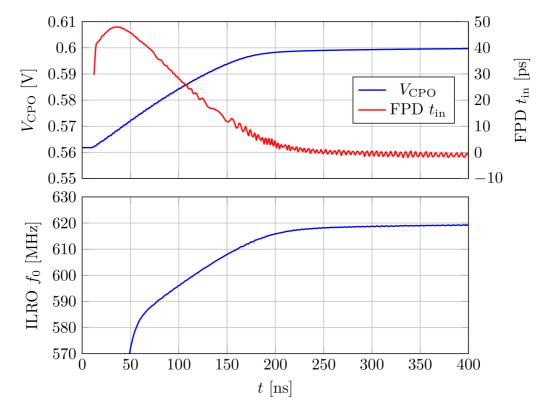

$$PDE = FF \cdot PDP = FF \cdot AP \cdot QE \tag{1.3}$$