# BRNO UNIVERSITY OF TECHNOLOGY

# Faculty of Electrical Engineering and Communication

# MASTER'S THESIS

Brno, 2024

Bc. Dominik Klement

# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

### **DEPARTMENT OF RADIO ELECTRONICS**

ÚSTAV RADIOELEKTRONIKY

# MULTILEVEL CONVERTER WITH ACTIVE GATE DRIVERS FOR FAULT RIDE-THROUGH

VÍCEÚROVŇOVÝ MĚNIČ S AKTIVNÍMI HRADLOVÝMI BUDIČI PRO FAULT RIDE-THROUGH

#### MASTER'S THESIS DIPLOMOVÁ PRÁCE

AUTHOR<br/>AUTOR PRÁCEBc. Dominik KlementSUPERVISOR<br/>VEDOUCÍ PRÁCEdoc. Ing. Tomáš Götthans, Ph.D.

#### **BRNO 2024**

### **Master's Thesis**

Master's study program Space Applications

Department of Radio Electronics

Student:Bc. Dominik KlementYear of<br/>study:2

*ID:* 211152

Academic year: 2023/24

TITLE OF THESIS:

#### Multilevel Converter with Active Gate Drivers for Fault Ride-Through

#### **INSTRUCTION:**

This thesis aims to make a significant contribution to the advancement of fault tolerance in power electronics converters, specifically focusing on the Nested Neutral Point Piloted (NNPP) multilevel converter. Rooted in a thorough review of state-of-the-art literature, the research aims to identify gaps, limitations, and challenges in existing approaches. The goals encompass a comprehensive description of the NNPP converter and other multilevel topologies. The thesis will propose and implement a fault-tolerant algorithm utilizing active gate driving technology, including space vector modulation and active capacitor voltage balancing control. This algorithm is to be implemented in simulation software, and the converter's hardware is to be designed for further real-world testing. The thesis will conclude with a comparative analysis of existing fault-tolerant methods, highlighting their respective advantages and disadvantages. In its final section, the thesis will summarize key findings, discuss potential applications, and propose topics for future research.

Goals

1. Conduct an in-depth analysis and comparison of various multilevel converter topologies, exploring their applications, use cases, functional principles, and differences to provide a broader understanding of their utilization in power electronics.

2. Develop an algorithm that addresses identified limitations in existing nested neutral point piloted converter designs and validate the proposed algorithm through simulation software implementation.

3. Design the converter's hardware and active gate driver to enable future real-world testing, ensuring it aligns with the algorithm's specifications for compatibility with control and measurement signals.

4. Perform a comparative analysis of existing fault-tolerant methods and the proposed method, outlining specific advantages and disadvantages and potential topics for future development of multilevel converters.

#### **RECOMMENDED LITERATURE:**

1. CHEN, Jiangui, Yan LI a Mei LIANG, 2019. A Gate Driver Based on Variable Voltage and Resistance for Suppressing Overcurrent and Overvoltage of SiC MOSFETs. Energies [online]. 12(9), 1640. ISSN 1996-1073. Dostupné z: doi:10.3390/en12091640

2. MEYNARD, T.A., H. FOCH, P. THOMAS, J. COURAULT, R. JAKOB a M. NAHRSTAEDT, 2002. Multicell converters: basic concepts and industry applications. IEEE Transactions on Industrial Electronics [online]. 49(5), 955–964. ISSN 1557-9948. Dostupné z: doi:10.1109/TIE.2002.803174

3. ROJAS, Félix, Cristóbal JEREZ, Christoph Michael HACKL, Oliver KALMBACH, Javier PEREDA a Jonathan LILLO, 2022. Faults in Modular Multilevel Cascade Converters—Part I: Reliability, Failure Mechanisms, and Fault Impact Analysis. IEEE Open Journal of the Industrial Electronics Society [online]. 3, 628–649. ISSN 2644-1284. Dostupné z: doi:10.1109/OJIES.2022.3213510

4. YU, Jianghui, Rolando BURGOS, Qiong WANG a Ismail AGIRMAN, 2019. Design of a SiC-based Five-Level Stacked Multicell Converter for High-Speed Motor Drives. In: 2019 IEEE Energy Conversion Congress and Exposition (ECCE): 2019 IEEE Energy Conversion Congress and Exposition (ECCE): 2019 IEEE Energy Conversion Congress and Exposition (ECCE) [online]. s. 4063–4068. ISSN 2329-3748. Dostupné z: doi:10.1109/ECCE.2019.8912728

Date of project specification: 16.2.2024 Deadline for 20.5.2024 submission:

Supervisor:doc. Ing. Tomáš Götthans, Ph.D.Consultant:Dr. Jun Wang, University of Nebraska–Lincoln

doc. Ing. Tomáš Götthans, Ph.D. Chair of study program board

WARNING:

The author of the Master's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

Faculty of Electrical Engineering and Communication, Brno University of Technology / Technická 3058/10 / 616 00 / Brno

# Abstract

This thesis explores multilevel converters, highlighting their benefits and current/potential future applications. It focuses on the Nested Neutral Point Piloted (NNPP) topology and develops a fault ride-through control algorithm with active capacitor voltage balancing and space vector modulation. The algorithm is validated through simulation. A prototype is designed for experimental validation. The thesis concludes by comparing the proposed fault-tolerant algorithm with existing methods.

# Keywords

Nested Neutral Point Piloted Converter, Fault Ride-through, Active gate driver, Multilevel converters, SiC MOSFET, Power Electronics, Stacked Multicell Topology, High reliability

# Abstrakt

Tato práce se zabývá víceúrovňovými měniči, popisuje jejich výhody a současné/potenciální budoucí aplikace. Zaměřuje se na "Nested Neutral Point Piloted (NNPP)" topologii a vývoj algoritmu řízení s aktivním vyrovnáváním napětí kondenzátoru a pokročilou vektorovou modulací pro tuto topologii. Tento algoritmus je ověřen pomocí simulací. Součástí práce je i návrh prototypu pro experimentální ověření. Práce je uzavřena porovnáním vyvinutého algoritmu s již existujícími metodami.

# Klíčová slova

Nested Neutral Point Piloted měnič, Fault Ride-through, Aktivný hradlový budič, Víceúrovňový měnič, SiC MOSFET, Výkonová elektronika, Stacked Multicell topologie, Vysoká spolehlivost

# Rozšířený abstrakt

Tato práce zkoumá aplikace a výhody víceúrovňových měničů, od trakčních měničů a HVDC přenosových vedení až po potenciální vesmírné aplikace, přičemž zdůrazňuje jejich schopnost snižovat elektromagnetické rušení a zvyšovat spolehlivost. Popisuje pět specifických topologií vhodných pro integraci do HFPP SiC FET modulů. Zaměřuje se na NNPP topologii, zdůrazňuje její výhody a popisuje její princip. Analýza identifikuje potenciální chyby v této topologii, tato analýza vede k vývoji řídicího algoritmu schopného jim odolávat. Algoritmus integruje základní části řízení měniče, včetně aktivního vyrovnávání napětí kondenzátoru a pokročilé vektorové modulace, a je ověřen pomocí simulace. Je navržen prototyp měniče pro experimentální měření a aktivní hradlový budič, který je navržen podle požadavků algoritmu. Práce je uzavřena porovnáním navrženého algoritmu s již existujícími metodami.

# **Bibliographic citation**

KLEMENT, Dominik. Multilevel Converter with Active Gate Drivers for Fault Ride-Through [online]. Brno, 2024 [cit. 2024-05-16]. Available from: https://www.vut.cz/studenti/zav-prace/detail/159880. Master's Thesis. Vysoké učení technické v Brně, Fakulta elektrotechniky a komunikačních technologií, Department of Radio Electronics. Supervisor Tomáš Götthans.

### **Author's Declaration**

| Author:        | Bc. Dominik Klement                                                     |

|----------------|-------------------------------------------------------------------------|

| Author's ID:   | 211152                                                                  |

| Paper type:    | Master's Thesis                                                         |

| Academic year: | 2023/24                                                                 |

| Topic:         | Multilevel Converter with Active Gate<br>Drivers for Fault Ride-Through |

I declare that I have written this paper independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the project and listed in the comprehensive bibliography at the end of the project.

As the author, I furthermore declare that, with respect to the creation of this paper, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation S 11 of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll., Section 2, Head VI, Part 4.

Brno, May 16, 2024

author's signature

### Acknowledgement

I extend my gratitude to my supervisor, doc. Ing. Tomáš Götthans Ph.D., for his guidance and support throughout this thesis. I also thank Dr. Jun Wang for his professional consultations, which have greatly contributed to the development of this work. His expertise has been invaluable in shaping the direction of my research. Furthermore, I acknowledge the University of Nebraska-Lincoln and Brno University of Technology for their support and resources, without which this thesis would not have been possible. Additionally, I acknowledge the use of AI for text formatting assistance.

Brno, May 16, 2024

Author's signature

# Contents

| <b>F</b> ] | IGURES  |                                     | 9  |

|------------|---------|-------------------------------------|----|

| T.         | ABLES . |                                     | 11 |

| I          | TRODU   | JCTION                              |    |

| 1.         | MUI     | TILEVEL CONVERTERS                  |    |

|            | 1.1     | APPLICATIONS                        |    |

|            | 1.2     | CONVERTER TOPOLOGIES                |    |

|            | 1.2.1   | Neutral Point Clamped               |    |

|            | 1.2.2   | Flying Capacitor                    |    |

|            | 1.2.3   | Modular Multilevel Converter        |    |

|            | 1.2.4   |                                     |    |

|            | 1.2.5   | Active Neutral Point Clamped        |    |

| 2.         | NES'    | TED NEUTRAL POINT PILOTED CONVERTER |    |

|            | 2.1     | SUBINTERVAL ANALYSIS                |    |

|            | 2.2     | TYPES OF FAULTS                     |    |

|            | 2.2.1   | Outer cell fault                    |    |

|            | 2.2.2   | Inner cell fault                    |    |

| 3.         | CON     | NTROL ALGORITHM                     |    |

|            | 3.1     | ACTIVE CAPACITOR VOLTAGE BALANCING  |    |

|            | 3.2     | COORDINATE TRANSFORMATIONS          |    |

|            | 3.2.1   | Clarke transformation               |    |

|            | 3.2.2   | Park transformation                 |    |

|            | 3.3     | SPACE VECTOR MODULATION             |    |

|            | 3.4     | FAULT DETECTION                     | 39 |

|            | 3.5     | FAULT RIDE-THROUGH                  |    |

|            | 3.6     | SIMULATION                          |    |

|            | 3.6.1   | Normal operation                    |    |

|            | 3.6.2   | 2 Fault condition                   |    |

| 4.         | . CON   | NVERTER PROTOTYPE                   |    |

|            | 4.1     | SWITCHING DEVICE                    | 50 |

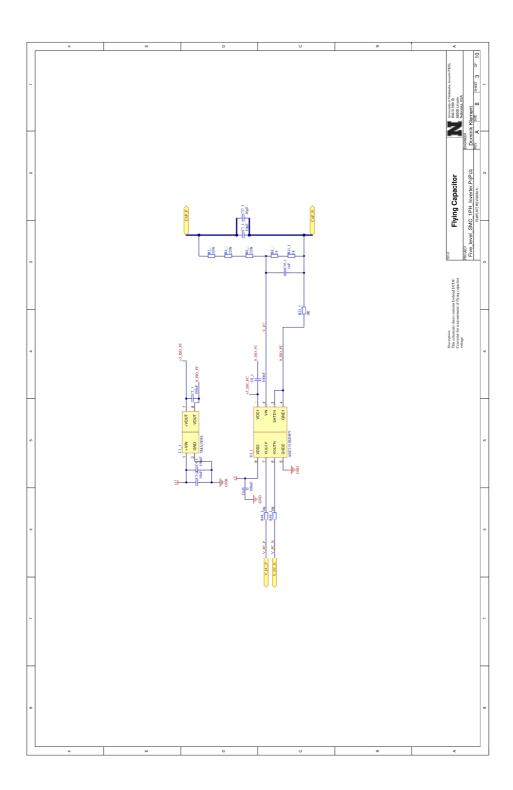

|            | 4.2     | CAPACITORS                          |    |

|            | 4.3     | MEASUREMENT                         | 55 |

|            | 4.3.1   | Current                             | 55 |

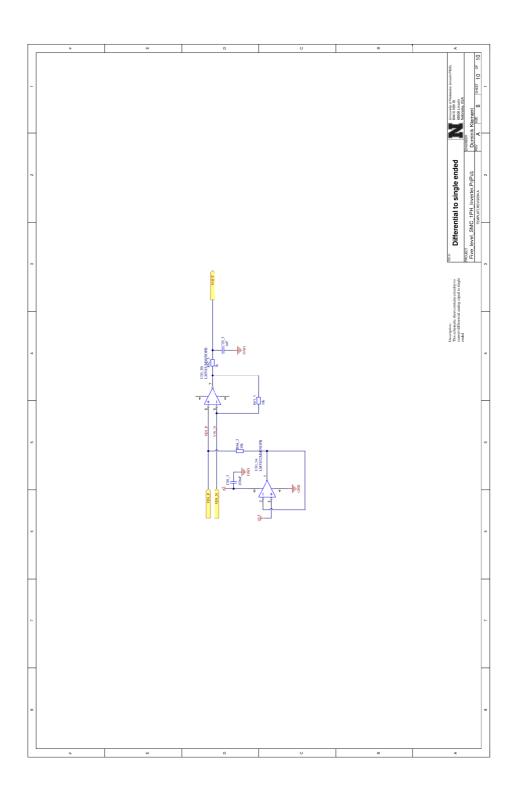

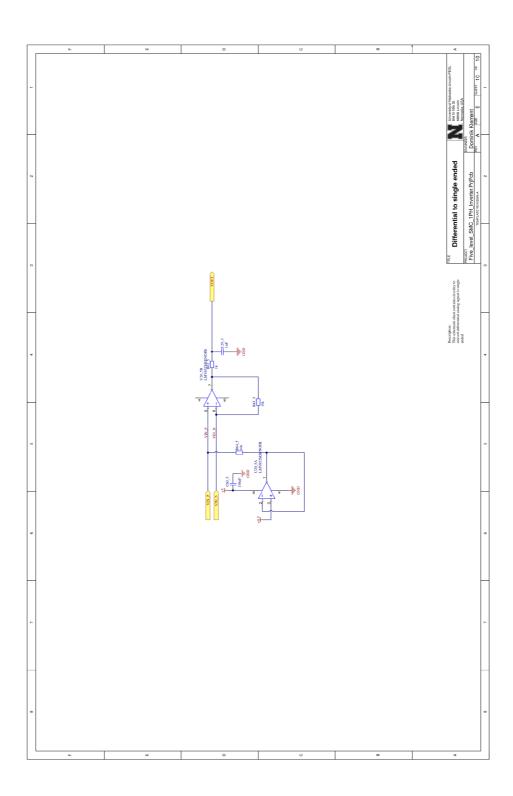

|            | 4.3.2   | 2 Voltage                           | 57 |

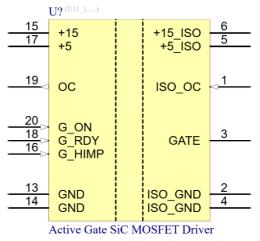

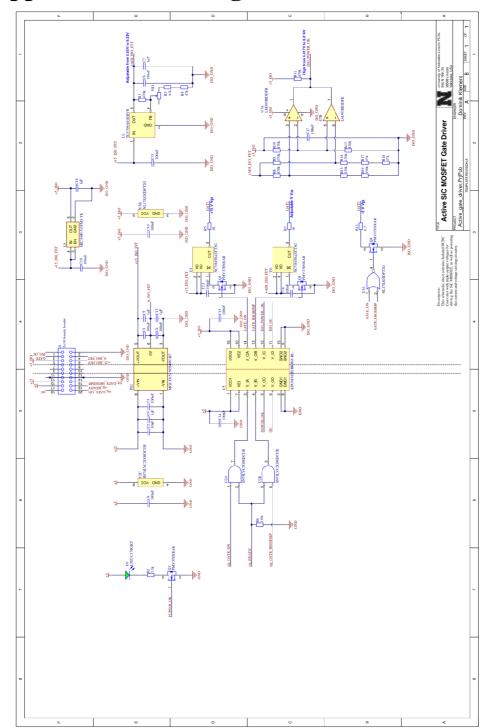

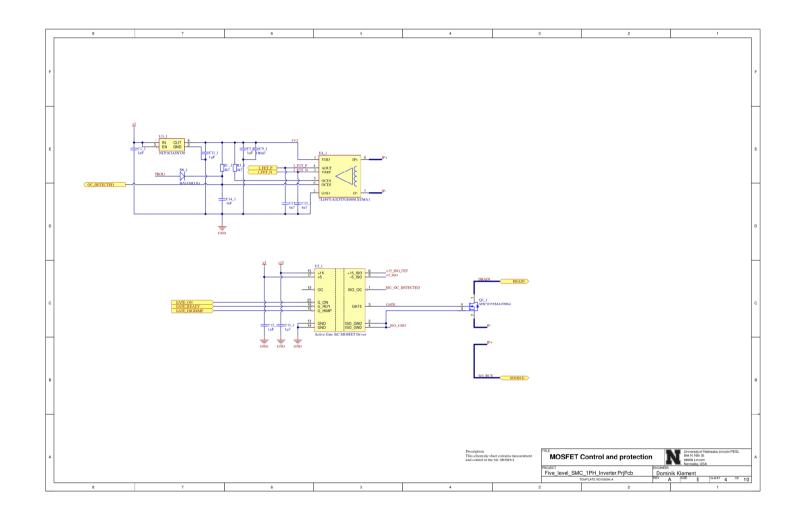

|            | 4.4     | ACTIVE GATE DRIVER                  |    |

|            | 4.4.1   | Requirements                        | 59 |

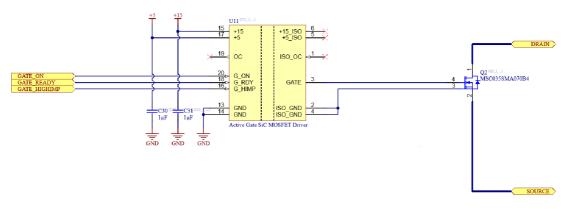

|            | 4.4.2   | 2 Implementation                    | 60 |

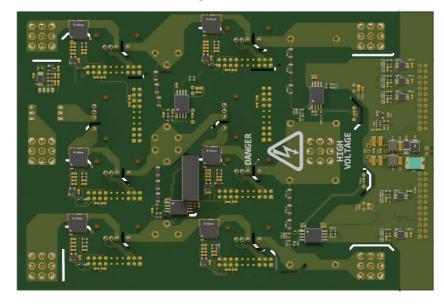

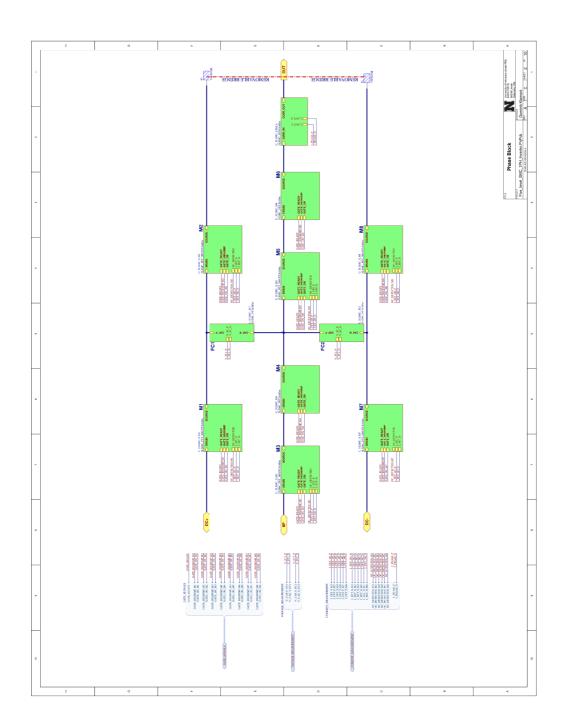

|            | 4.5     | PROTOTYPE DESIGN                    |    |

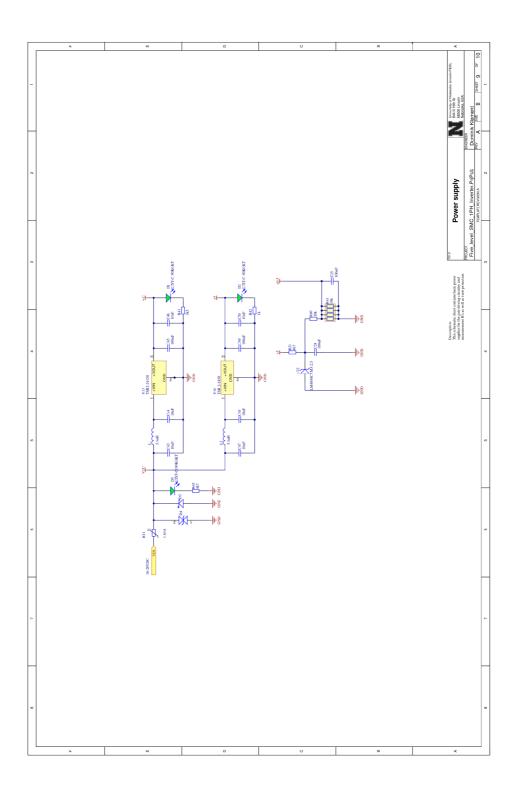

|            | 4.5.1   | Schematic                           |    |

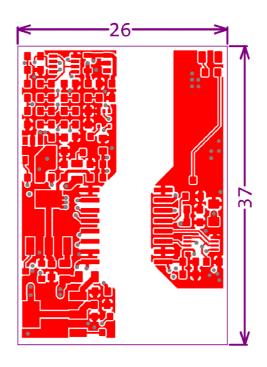

|            | 4.5.2   | 2 Printed circuit board             | 66 |

| 5          | . CON   | NCLUSION                            |    |

| 5.1       | COMPARATIVE ANALYSIS | 71 |

|-----------|----------------------|----|

| 5.2       | SUMMARY              | 72 |

| LITERAT   | URE                  | 75 |

| ABBREVI   | ATIONS               | 89 |

| LIST OF A | APPENDICES           | 91 |

# **FIGURES**

| 1.1  | Comparison of output phase voltage waveforms (a) two level converter, (b) three level converter,         |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | (c) nine level converter [14].                                                                           |     |

| 1.2  | GE Vernova MM7 modular multilevel converter [18]                                                         | .15 |

| 1.3  | BorgWarner 850-Volt Multi Level High Speed Converter [20]                                                | .15 |

| 1.4  | Overview of multilevel converter-driven applications [27].                                               | .16 |

| 1.5  | Overview of power converter topologies [31]                                                              | .17 |

| 1.6  | Three-phase Neutral Point Clamped Multilevel converter topology [33].                                    | .18 |

| 1.7  | Neutral Point Clamped converter single leg states (a) state "Positive", (b) state "Zero", (c) state      |     |

|      | "Negative" [35]                                                                                          | .18 |

| 1.8  | Neutral Point Clamped converter output waveforms a) leg output b) phase-to-phase [36]                    | .19 |

| 1.9  | Flying Capacitor topology (a) general converter, (b) single cell [39]                                    | .20 |

| 1.10 | Three-phase four level Flying Capacitor Converter [41].                                                  | .20 |

| 1.11 | Modular Multilevel Converter submodules (a) half-bridge, (b) full-bridge, (c) CCSM, (d) NPCSM            | Λ   |

|      | [46]                                                                                                     | .21 |

| 1.12 | Modular Multilevel Converter submodule arm arrangements (a) single-phase, (b) three-                     |     |

|      | phase/(DC/single-phase), (c) B2B [47].                                                                   |     |

| 1.13 | Nested Neutral Point Piloted topology derivation (a) three level FC cell, (b) 4L NNPC converter,         |     |

|      | (c) NNPP converter [31]                                                                                  | .22 |

| 1.14 | Nested Neutral Point Piloted Converter general single leg topology [56]                                  | .23 |

| 1.15 | Initial Active Neutral Point Clamped Converter topology [58].                                            | .24 |

| 1.16 | Simplified Active Neutral Point Clamped Converter topology                                               | .24 |

| 2.1  | HFPP SiC Module topologies: (a) 5L-NNPP, (b) 5L-Vienna-NNPP, (c) 5L-ANPC, (d) 5L-FC, (e                  | )   |

|      | 5L-MMC [48]                                                                                              | .25 |

| 2.2  | General five level single phase NNPP Topology.                                                           |     |

| 2.3  | NNPP Topology subintervals (a) V <sub>9</sub> , (b) V <sub>8</sub>                                       | 27  |

| 2.4  | Results of survey on power converter fault causes                                                        |     |

| 2.5  | NNPP Converter fault type division                                                                       | 28  |

| 2.6  | NNPP Converter inner cell fault current loops during (a) subinterval $V_6$ , (b) subinterval $V_7$ , (c) |     |

|      | subinterval V <sub>9</sub>                                                                               |     |

| 3.1  | Flying capacitor selection process flowchart [91].                                                       | 32  |

| 3.2  | Active Capacitor Voltage Balancing block in simulation software (a) internal structure, (b) block        | in  |

|      | schematic                                                                                                | 33  |

| 3.3  | Three-phase control block diagram [95].                                                                  | 33  |

| 3.4  | Clarke transformation implementation in simulation.                                                      | 34  |

| 3.5  | Input and output of the Clarke transformation.                                                           | 35  |

| 3.6  | Park transformation implementation in simulation.                                                        |     |

| 3.7  | Input and output of the Park transformation                                                              | 36  |

| 3.8  | Reference voltage vector in the alpha-beta plane [109].                                                  | 37  |

| 3.9  | Five level converter voltage space [91].                                                                 | 37  |

| 3.10 | Simulation block schematic (a) control part, (b) modulation part.                                        | 38  |

| 3.11 | Input and output of the Space Vector Modulation block                                                    | 38  |

|      | Propose fault ride-through control-flow graph                                                            |     |

| 3.13 | Fault of switch $S_3$ during $V_8$ subinterval (a) $i_x > 0$ , (b) $i_x < 0$                             | 40  |

| 3.14 | MOSFET Drain current vs. Gate-source voltage dependance [121].                                           | 41  |

|      | Converter block diagram.                                                                                 |     |

| 3.16 | Flying capacitor voltage measurement                                                                     | 43  |

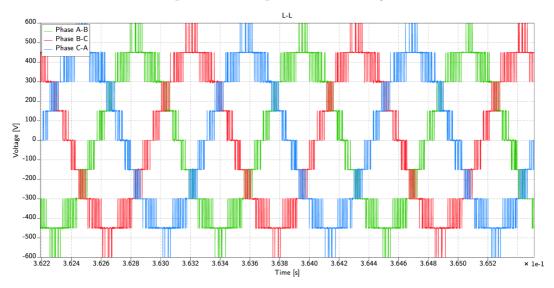

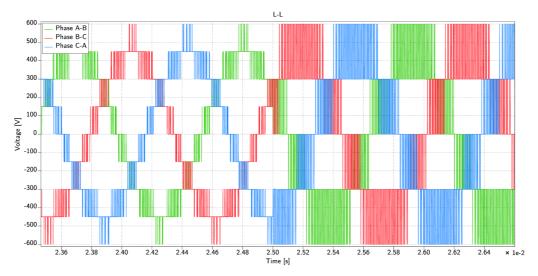

| 3.17 | Phase to phase voltage measurement of the converter.                                  | 43 |

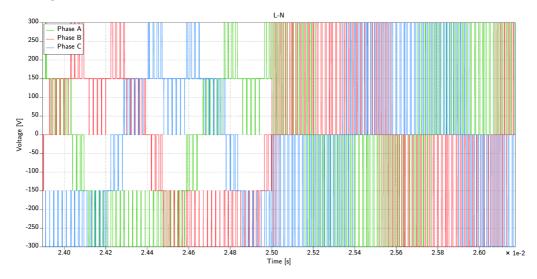

|------|---------------------------------------------------------------------------------------|----|

| 3.18 | Phase to neutral voltage measurement of the converter.                                | 44 |

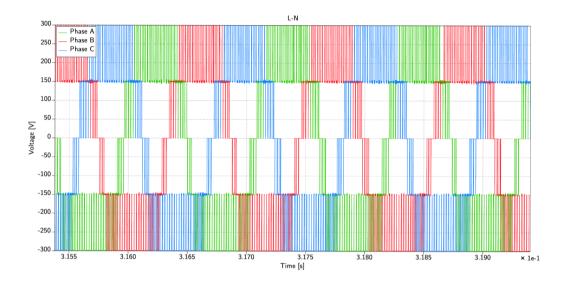

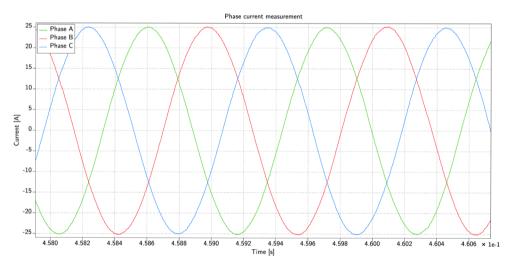

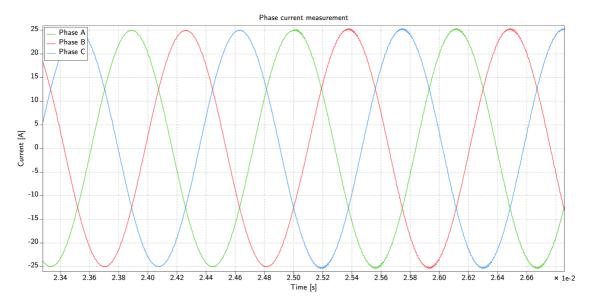

| 3.19 | Phase current measurement of the converter                                            | 44 |

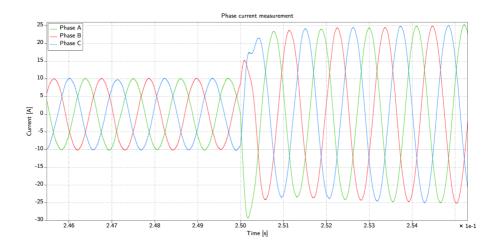

| 3.20 | Phase current measurement of the converter during transient.                          | 45 |

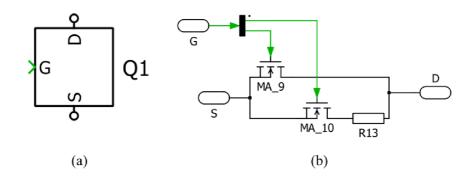

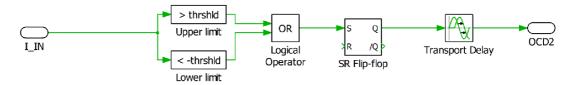

| 3.21 | Simplified MOSFET model (a) subsystem, (b) internal structure                         | 46 |

| 3.22 | Model of the OCD2 output of the TLI4791 current sensor in simulation.                 | 46 |

| 3.23 | Phase to phase voltage measurement of the converter for fault transition              | 47 |

| 3.24 | Phase to neutral voltage measurement of the converter for fault transition            | 47 |

| 3.25 | Phase current measurement of the converter for fault transition                       |    |

| 4.1  | Fischer Elektromotoren TI085-052-070-04B7S-07S04BE2.                                  | 49 |

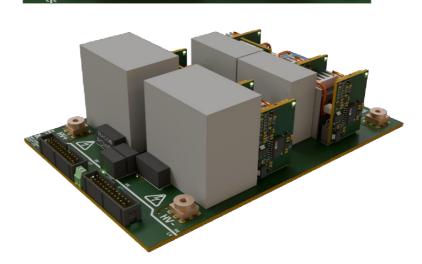

| 4.2  | Three-phase five level NNPP Converter.                                                | 50 |

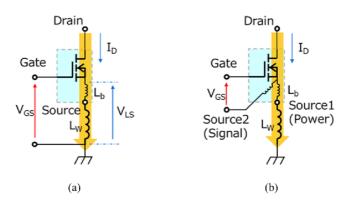

| 4.3  | MOSFET Packages (a) 3 pin – no kelvin connection, (b) 4 pin – kelvin connection [145] | 52 |

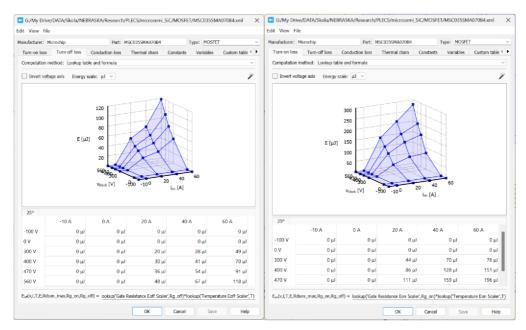

| 4.4  | Turn-off/on loss lookup table of the MSC035SMA070B4 model                             | 52 |

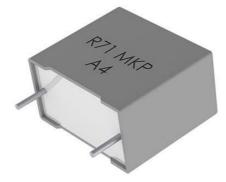

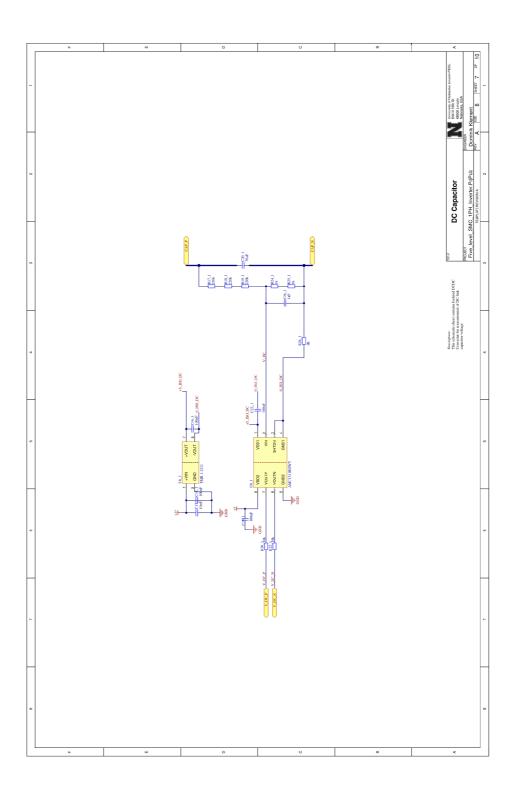

| 4.5  | Chosen DC-link capacitor package [150]                                                | 53 |

| 4.6  | Chosen flying capacitor package [154].                                                | 54 |

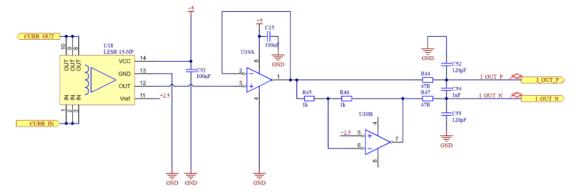

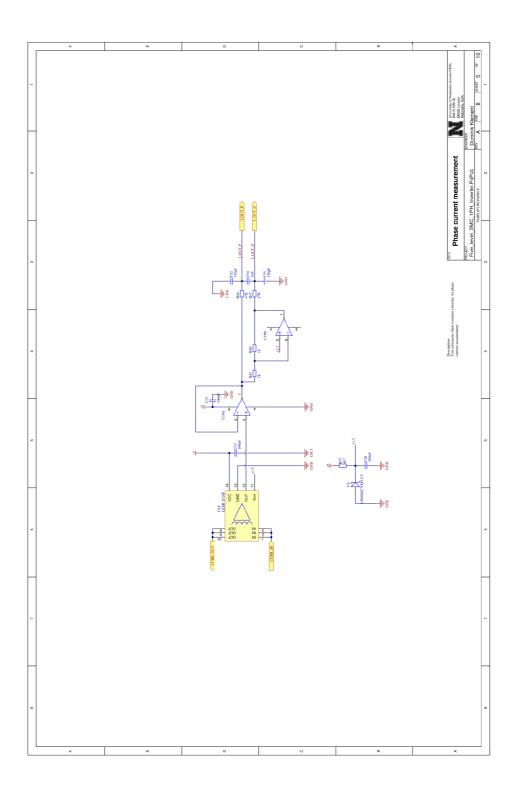

| 4.7  | Phase current measurement schematic.                                                  | 56 |

| 4.8  | TLI4791 Current sensor package.                                                       |    |

| 4.9  | MOSFET Current measurement schematic.                                                 |    |

| 4.10 | DC-link capacitor voltage measurement schematic.                                      | 58 |

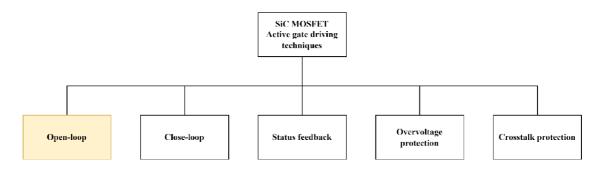

| 4.11 | Active gate driving methods overview [173].                                           | 59 |

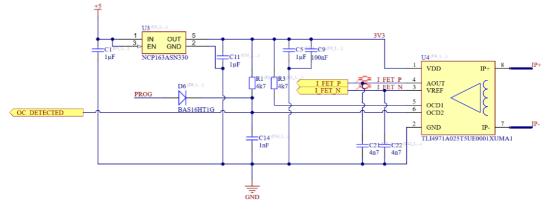

| 4.12 | Isolated DC/DC Converter MGJ1D151505MPC [181].                                        | 61 |

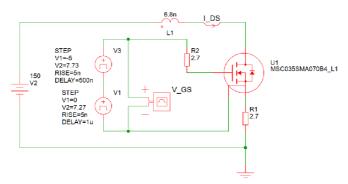

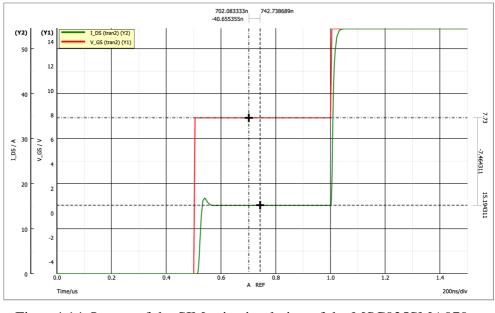

| 4.13 |                                                                                       |    |

| 4.14 | Output of the SIMetrix simulation of the MSC035SMA070 MOSFET                          | 62 |

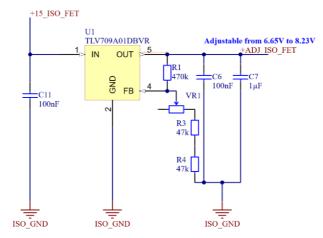

|      | Low conductivity mode power supply schematic.                                         |    |

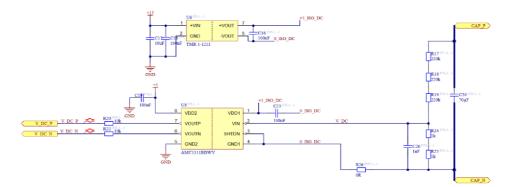

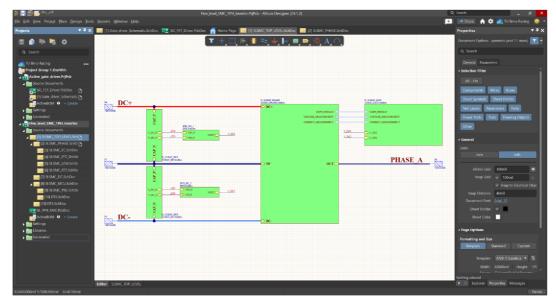

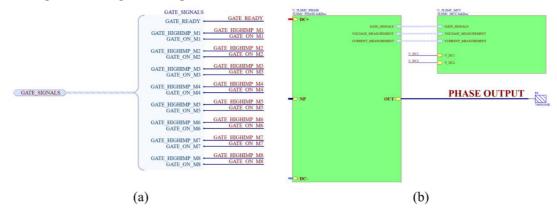

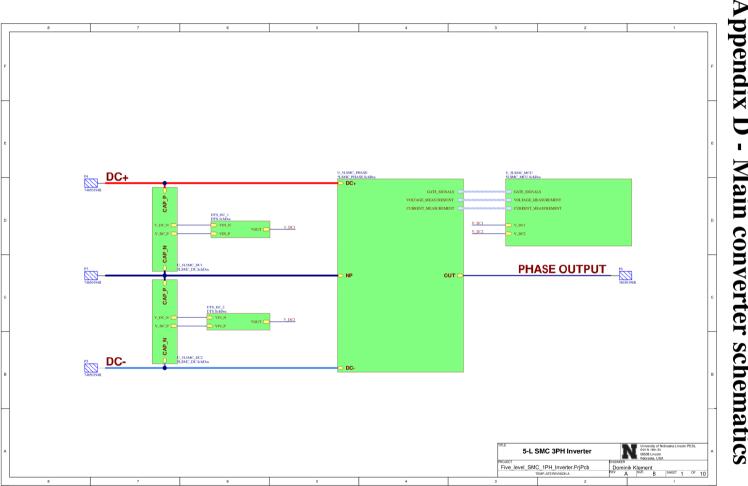

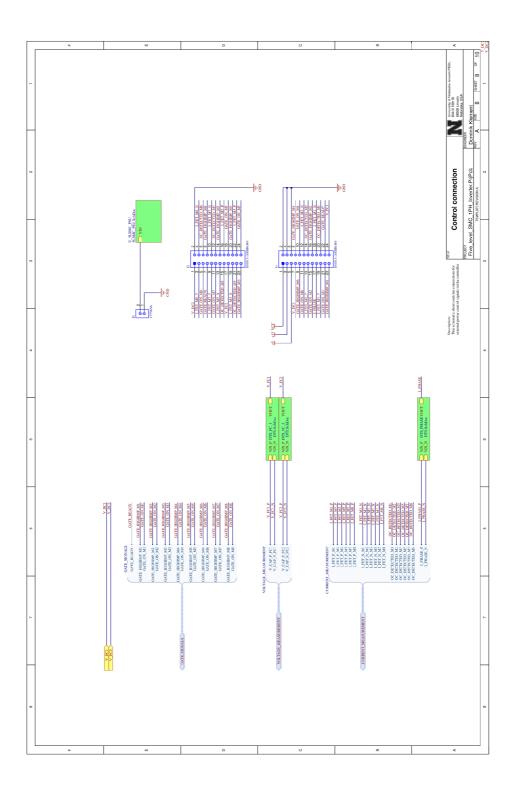

|      | Hierarchical schematic of the converter system.                                       |    |

|      | IPC-2221B Electrical conductor spacing [188].                                         |    |

|      | Altium designer clearance rule definition.                                            |    |

|      | Active gate driver schematic symbol.                                                  |    |

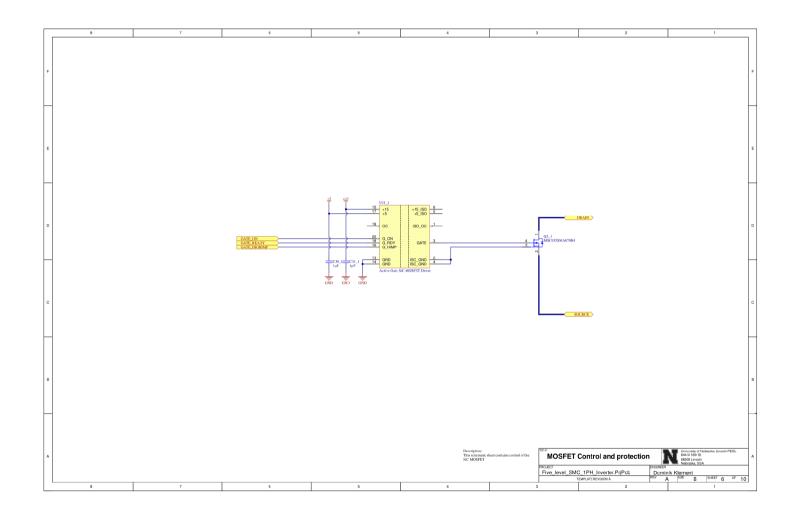

|      | MOSFET Control schematic sheet                                                        |    |

|      | Signal harness (a) group creation, (b) usage in hierarchical design.                  |    |

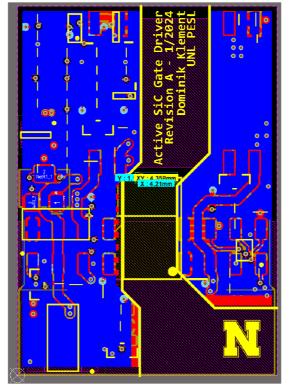

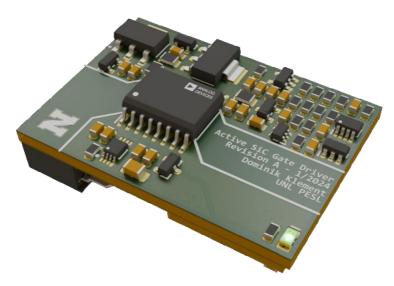

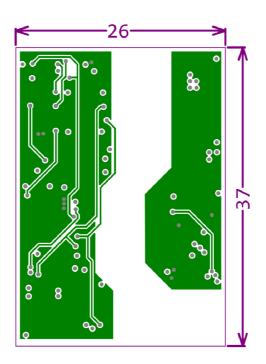

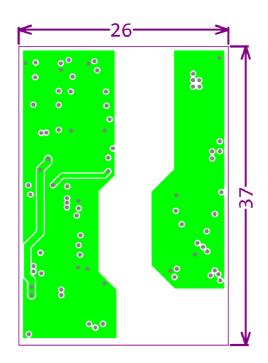

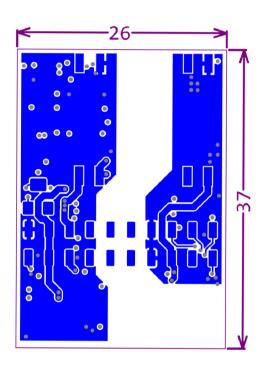

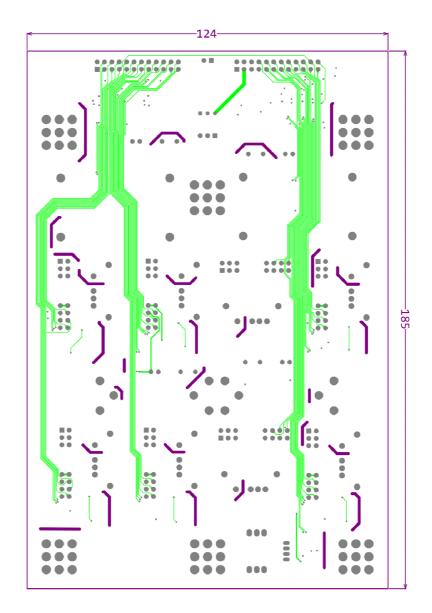

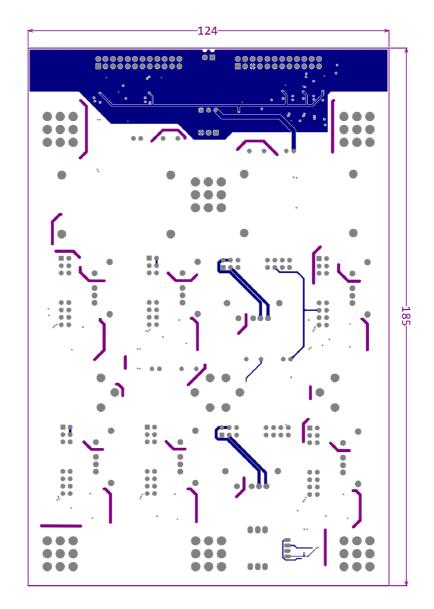

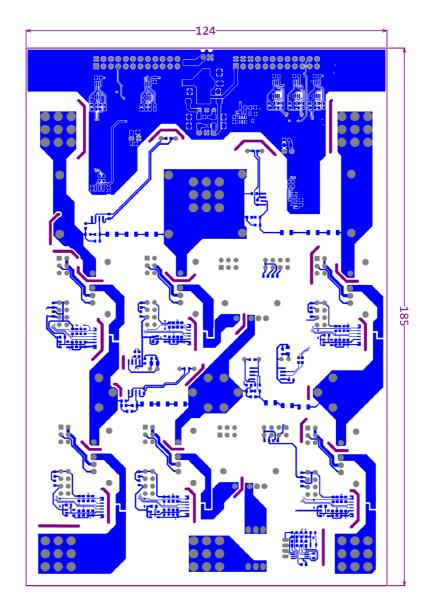

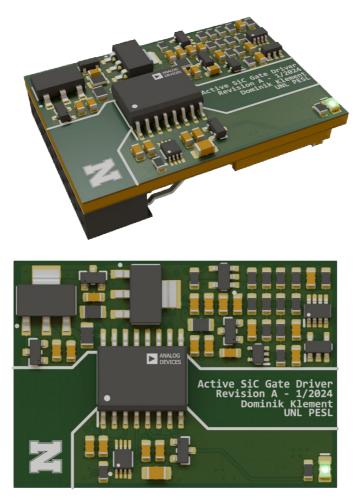

| 4.22 | Active gate driver PCB layout                                                         | 67 |

|      | Saturn PCB Design tool example calculation                                            |    |

|      | Rendering of the active gate driver PCB.                                              |    |

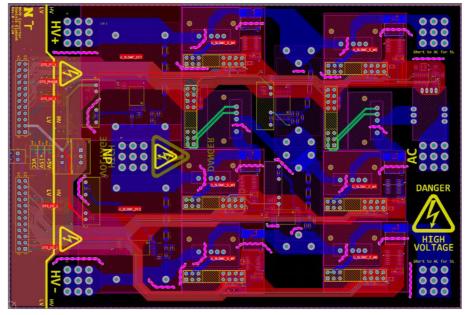

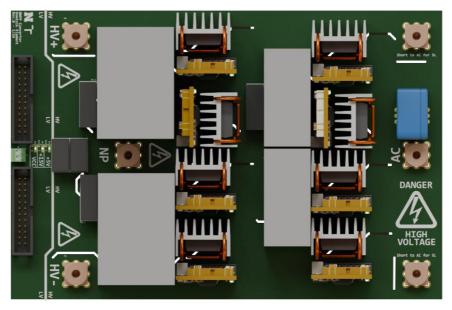

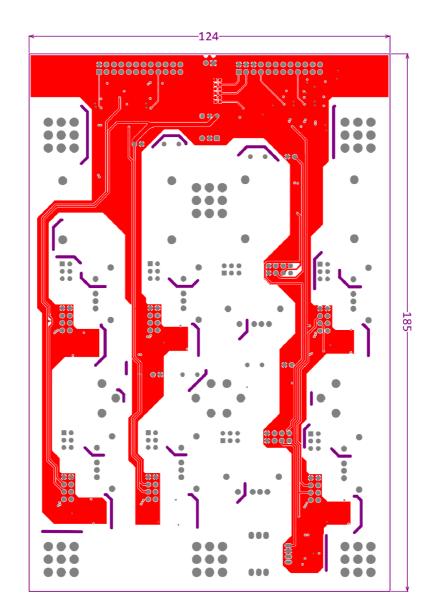

| 4.25 | Single phase of the converter PCB layout.                                             | 69 |

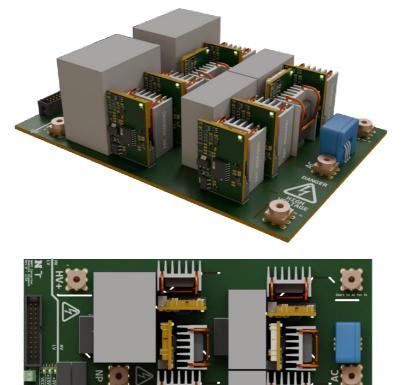

| 4.26 | Rendering of the top side of the converter PCB.                                       | 69 |

| 4.27 | Rendering of the bottom side of the converter PCB                                     | 70 |

# TABLES

| 42 |

|----|

| 46 |

| 49 |

| 50 |

| 51 |

| 55 |

| 72 |

|    |

### INTRODUCTION

The focus of this work is to develop a general algorithm for controlling a three-phase multilevel power converter. The algorithm aims to maintain functionality when a fault occurs with reduced output waveform quality until the converter is serviced resulting in fault ride-through capability. This solution is particularly valuable for high-reliability applications in extreme environments. The converter will be simulated and additionally, a physical prototype meeting the algorithm's requirements will be designed for future experimental validation.

Power converters are instrumental in transforming electrical power from one form to another in various applications. These range from low-power, low-voltage systems such as electric bikes to high-power, high-voltage applications such as HVDC grids, wind farms, and heavy industrial machinery as well as the automotive sector, where multilevel converters are a rising trend [1]. In addition, power converters are critical in space applications, enabling efficient power management and distribution aboard spacecraft and satellites [2].

The multilevel converter addresses several shortcomings of a more traditional twolevel topology, as low-order harmonics in the output waveform [3] or high overvoltage on the output terminals caused by reflections [4]. However, the improvements in output waveform quality comes at a cost of control complexity [5] and additional components that can lead to fault susceptibility [6].

The current state-of-the-art control solutions mainly focus on the open circuit fault [5], [6], [7], the short circuit fault of multilevel converters is studied, however the proposed solution requires additional components in the current carrying path [8]. The design of the converter and the focus is given on the short circuit failure mode of the switching device as it is the main failure mode [9] of a novel Press-pack type SiC IGBT [10] that was developed in parallel and that is to be used as a switching device in the future versions of this power converter, as well as the fail-to-short behavior being the preferred failure mode for HVDC and FACTS applications [11], [12].

The thesis consists of four chapters. The first chapter provides an overview of multilevel converters, including a comparison with two-level converters and an exploration of current and potential future applications. Various converter topologies are compared to select one for the prototype and control algorithm design. The second chapter delves deeper into the chosen converter topology, analyzing switching subintervals, voltage stresses on main components, and conducting fault state analysis. The third chapter focuses on the detailed development of a specific fault ride-through capable control algorithm tailored to the chosen topology. Hardware control and measurement interface requirements are outlined, and simulation results of the control algorithm are presented. Finally, the last chapter centers on the hardware design of the power converter, selecting components compatible with the control algorithm's requirements.

### **1. MULTILEVEL CONVERTERS**

Multilevel converters are converters where the output voltage waveform is synthesized as a combination of several DC voltages, thus they have the ability to generate a highquality output with lower total harmonic distortion, with a zero harmonic distortion of the output waveform being obtained with an infinite number of output levels. More levels mean higher voltages can be spanned by series devices without device voltage sharing problems [7].

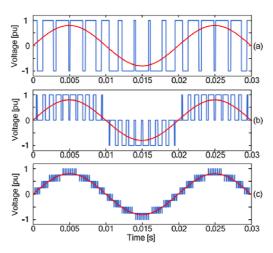

Depending on the topology, a multilevel converter is usually comprised of identical sub-modules whose series and parallel combinations give the convert the ability to staircase the output voltage waveform and more accurately represent the requested waveform, the difference in the output waveforms can be seen in Figure 1.1.

With the increase of power requirements of many applications a higher voltage is required, for example in the case of HVDC and UHVDC transmission lines, where the voltages can reach levels upwards of 800 kV [8], however the current commercially available semiconductor technology tops up at 6.5 kV [9], [10]. Multilevel converters allow the use of lower voltage switching devices in high voltage applications [11], [12], [13].

Fig. 1.1 Comparison of output phase voltage waveforms (a) two level converter, (b) three level converter, (c) nine level converter [14].

The advantages of multilevel converters include:

- High-quality output waveform,

- use of lower voltage switching devices for high voltage applications,

- modularity and expandability,

- depending on topology: switch combination redundancy,

- improved efficiency due to switching at fundamental frequency.

Multilevel converters have a number of advantages over traditional two-level converters;

however, they also present some disadvantages. The use of series connection of lower voltage switching devices as opposed to use of switching devices rated for operation at the voltage level of the system leads to increase part count, which inherently decreases the reliability due to potential manufacturing defects or faulty components, this has been mostly solved in the current days [15], but still needs to be taken into account during the failure rate assessment.

When implementing a multi-level converter in a low voltage application, the increase in cost of the components may offset the advantages of increased output waveform quality, that is why multi-level topologies are still a domain of high-voltage converters.

As opposed to a traditional three phase two-level topology, where only six switching devices are controlled, multi-level converters usually have a much greater number of switches with different switching combinations that have different effect on the output voltage as well as in the case of some multi-level topologies the current and its direction flowing through the DC-link capacitors, the voltage balance of them as well as the neutral point current. This results in the need for complex control algorithms that may require significant computational power for the converter to operate at high switching frequencies, which is the case of control of a high-speed electric motor with a high pole pair count resulting in high fundamental frequency.

If care is not taken in the hardware design of a multi-level converter, big commutation loops may occur, which may result in high EMI of the converter, which can in turn affect the performance of sensitive voltage and current sensors used for control, rendering the converter inoperable as well as affect the surrounding subsystems onboard the device.

The disadvantages of multilevel converters include:

- Increased part count,

- control complexity when compared to two-level converters,

- improper design may result in EMI issues,

- depending on topology and number of levels: higher switching losses.

### **1.1 Applications**

Multilevel converters have found successful industrial applications in various fields, including renewable energy integration, high-voltage DC transmission, motor drives, and more. Recent advances in multilevel converter technology have led to new commercial topologies and modulation and control techniques that have improved their performance and efficiency [16].

An example of a use of a multilevel converter may be an MM7 modular multilevel converter from GE Vernova shown in Figure 1.2, such a converter may be used in many applications ranging from MVDC transmission with voltages of up to 100 kV all the way to STATCOM applications with power ranging from 30 to 150 MW. The main advantages of using a multilevel converter topology include the containment of a single

failure at a local submodule level and a transform-less design for applications of up to 36 kV [17].

Fig. 1.2 GE Vernova MM7 modular multilevel converter [18].

Another example of the use of multilevel converters is a Multilevel Highspeed Inverter from BorgWarner shown in Figure 1.3. This converter can, thanks to the multilevel technology operate high-speed electric motors at speeds of up to 180 000 rpm [19]. Such speeds would be very difficult to achieve with traditional topologies due to the extremely high dV/dt on the output terminal.

Fig. 1.3 BorgWarner 850-Volt Multi Level High Speed Converter [20].

High dv/dt can cause voltage spikes and ringing on the leading edge of the voltage pulse, which can lead to high-frequency EMI and damage to the motor windings if the peak voltage is too high. The main problems associated with high dV/dt are motor insulation failure, motor bearing failure and increased levels of RFI [21].

A filter may be introduced at the output of the converter, which will decrease the high dV/dt, but will lead to losses, which can in certain cases be as high as 11.7% [22]. The inclusion of a filter also lowers the volumetric and gravimetric density of the converter,

which can in some applications be highly undesired, such applications may include an extraterrestrial mining machinery, whose cost to launch from earth would be increased and payload capacity reduced.

Application of multi-level converter in motor controllers can due to the lower overvoltage values on the output terminals [4], increase the lifespan of electric motors, reducing their potential downtime and increasing the servicing interval. This can in both terrestrial and space applications mean cost savings.

Multi-level converters are currently being developed for a more potential use in the aerospace industry [23], the number of redundant switching states, when implemented correctly offer added redundancy and can result in fault tolerant systems [24]. With future space developments, including the potential permanent habitations of extraterrestrial objects such as Mars or the Moon, the comfort of the crew needs to be taken into account, the power demand will increase [25], where it will be necessary to increase the voltage of the systems beyond the current norms [26], by using multi-level converters in such applications, redundancy can be achieved with low EMI and RFI.

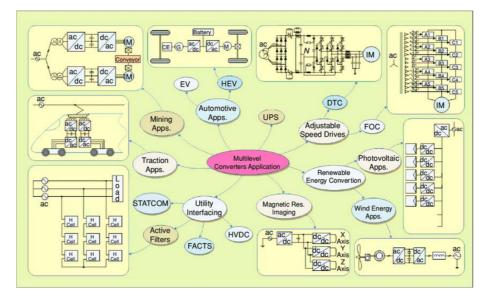

Fig. 1.4 Overview of multilevel converter-driven applications [27].

The use of multilevel converters is extremely broad, an overview is shown in Figure 1.4. Their utilization is only growing, where the advantages in many applications outweigh the disadvantages.

### **1.2** Converter topologies

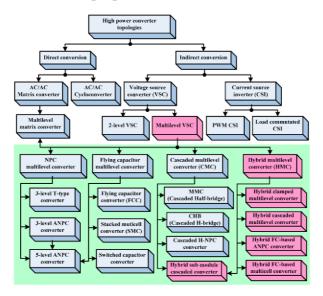

Multilevel converter topologies have been widely studied and developed for various applications. A review of existing topologies of multilevel inverters is presented in the following chapters.

This is not a comprehensive comparison as the number of topologies is constantly growing as can be seen in [28], [29], [30] and in the Figure 1.5, where the most popular power converter topologies are shown. Only the five major multi-level converters are considered in this comparison as there is sufficient information available regarding their functional principle and inherent properties.

Fig. 1.5 Overview of power converter topologies [31].

This comparison is conducted to gain a better understanding of the underlying concepts of achieving a multi-level output, for most of the topologies compared, the individual switching states are not described as that is not the focus of this thesis, only their functional principle is shown.

Individual topologies have distinctive features, which have their advantages and disadvantages and the choice between them must be made according to the system requirements such as the efficiency target, total harmonic distortion, fundamental frequency, system voltage etc. For the development of the control algorithm a Nested Neutral Point Piloted topology was chosen, the choice is described in more detail in chapter 2 of this thesis.

#### **1.2.1** Neutral Point Clamped

Neutral Point Clamped (NPC) converter is the most commonly used multilevel converter topology [32]. And is widely used in medium voltage applications [33]. The topology is characterized by the use diodes to clamp the output voltage and is shown in Figure 1.6.

Fig. 1.6 Three-phase Neutral Point Clamped Multilevel converter topology [33].

Care needs to be taken to keep the DC midpoint balanced as at high modulation indices a low frequency ripple occurs on the neutral-point voltage and steady-state unbalance in the neutral-point voltage may arise due to a variety of factors such as component imperfections, transients and other nonidealities and imbalances [34].

The Neutral point clamped converter has three output levels per phase and varies between three states "*Positive*", "*Zero*" and "*Negative*" as shown in Figure 1.7, where the current flow for one leg of the converter can also be seen [35].

Fig. 1.7 Neutral Point Clamped converter single leg states (a) state "Positive", (b) state "Zero", (c) state "Negative" [35].

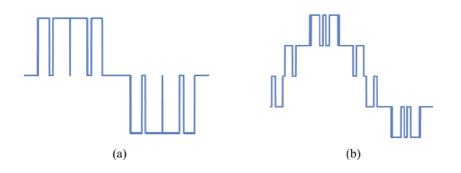

The resulting output then is +E, 0 and -E, respectively. Whereas the two-level converter only switches between +E and -E. The output waveforms of the converter are shown in Figure 1.8.

Fig. 1.8 Neutral Point Clamped converter output waveforms a) leg output b) phase-to-phase [36].

Table 1.1 contains an overview of the basic switching states of a single leg of the neutral point clamped converter topology from Figure 1.7. For each of the three switching states the conduction state of each of the switching devices is presented as well.

| S   | witching d | evice state |     | Output voltage | Switching state |  |  |

|-----|------------|-------------|-----|----------------|-----------------|--|--|

| Sx1 | Sx2        | Sx3         | Sx4 | Output voltage | Switching state |  |  |

| ON  | ON         | OFF         | OFF | +E             | Positive        |  |  |

| OFF | ON         | ON          | OFF | 0              | Zero            |  |  |

| OFF | OFF        | ON          | ON  | -Е             | Negative        |  |  |

Table 1.1

Neutral Point Clamped converter switching states

Overall, the three-level output of the neutral point clamped has clear advantages over the traditional two-level converter, such as reduced switching losses due to only half of the voltage being switched, this also gives the topology an advantage of for lower voltage rating of switching devices such as MOSFETS or IGBTs, which may result in lower cost and lower conduction losses due to more mature technology.

The output will also only have lower current ripple and half of the voltage transient [37]. These advantages come at a cost of more complex control, the unequal loss distribution among switching devices and the need for DC link capacitor voltage balancing [38].

#### 1.2.2 Flying Capacitor

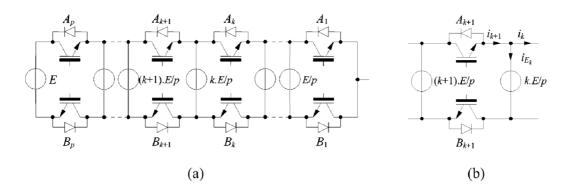

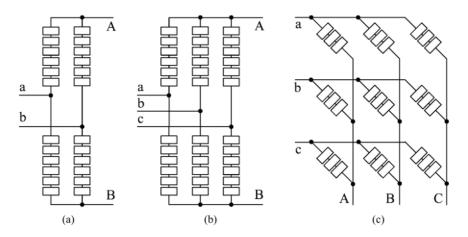

The flying capacitor topology, often referred to as the multicell topology, is a type of multilevel converter that consists of a series of elementary cells. The general converter topology is shown in Figure 1.9a. The topology is comprised of p pairs of three quadrant switches, separated by p-1 flying voltage sources [39] shown in Figure 1.9b.

Fig. 1.9 Flying Capacitor topology (a) general converter, (b) single cell [39].

The number of output levels  $N_{output_lvls}$  is directly proportional to the number of cells in series and can theoretically be infinite and can be expressed by an equation [40]

$$N_{output \ lvls} = p + 1, \tag{1.1}$$

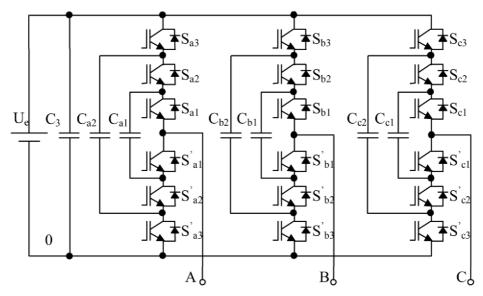

where p is the number of single cells in the converter leg. Figure 1.10 shows connection of three elementary cells and two flying capacitors per phase with a shared DC link capacitor C<sub>3</sub>.

Fig. 1.10 Three-phase four level Flying Capacitor Converter [41].

The voltage on the flying capacitors may become unbalanced, in the past an open-loop balance booster was used [39], that however adds additional components to the circuit and may introduce losses, the solution for active closed-loop control was proposed in [42].

In summary, flying capacitor converters consist of multiple cells connected in series to distribute the voltage constraints amongst them and to improve the output waveform. They have been shown to be suitable for various applications such as for example the input converter of GEC/ACEC T13 Locomotives and three-phase Alstom electric motor inverters [43].

#### 1.2.3 Modular Multilevel Converter

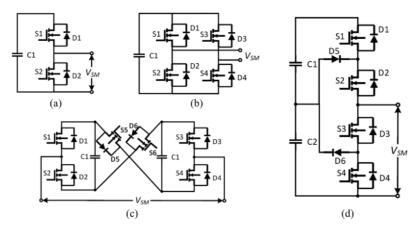

The modular multilevel converters consist of submodules that can be of different types, Although the most commonly used submodules are the half- and full-bridge topologies [44], several alternative submodules topologies to fulfill different objectives have been proposed, such as a modified active neutral point clamped submodule proposed in [45]. Several submodule configurations are shown in Figure 1.11

Fig. 1.11 Modular Multilevel Converter submodules (a) half-bridge, (b) fullbridge, (c) CCSM, (d) NPCSM [46].

Modular multilevel converter is a cascaded connection of a large number of the described submodules, they are arranged in groups called arms, which can be connected in several configurations as shown in Figure 1.12.

Fig. 1.12 Modular Multilevel Converter submodule arm arrangements (a) single-phase, (b) three-phase/(DC/single-phase), (c) B2B [47].

A five level output can be achieved in a three layer stack of the HFPP module design proposed in [48]. The half-bridge based multilevel converter is a highly customizable converter with modular and transformer-less construction, half-bridge cell is essentially a DC-chopper, where the voltage is either equal to the voltage of the intermediate capacitor or it is zero, the states of the switching devices are complementary [49].

The advantages and disadvantages are similar to other topologies, the output waveform has a better quality, but over the two-level converter, there is need for more power semiconductor switches and their gate driving circuitry, which in turn increases the footprint as well as costs of the converter [50]. This topology also requires an inductor on each side of a single leg of the converter [51].

#### 1.2.4 Nested Neutral Point Piloted

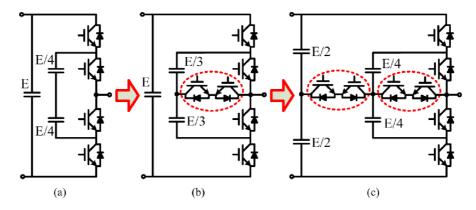

Nested Neutral Point Piloted sometimes also called Stacked Multicell topology [31] is a hybrid multilevel topology . The topology is inherently modular and exhibits a natural flying capacitor voltage balancing properties, however input variations can occur, which can influence the balancing property and can negatively influence the performance of the converter [52], this can be solved by an external balance booster circuit as in [53], [54], [55] or an active voltage balancing can be implemented, which will be described in further detail in the chapter 3.1.

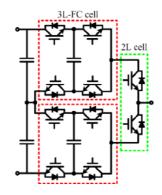

Fig. 1.13 Nested Neutral Point Piloted topology derivation (a) three level FC cell, (b) 4L NNPC converter, (c) NNPP converter [31].

The topology for a single leg of a five-level three-phase stacked multicell is shown in Figure 1.13c, the topology is derived as a combination of a Flying Capacitor cell and an Nested Neutral Point Clamped converter topology [31].

Fig. 1.14 Nested Neutral Point Piloted Converter general single leg topology [56].

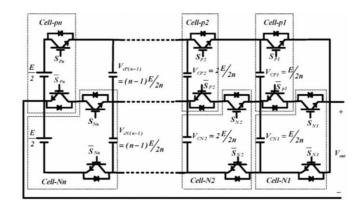

A general topology for a nested neutral point piloted leg is shown in Figure 1.14. The circuit is made up of elementary commutation cells connected in n stages with p cells connected in a  $n \times p$  structure, where the number of output levels  $N_{output\_lvls}$  can be calculated by the following equation [57]

$$N_{output\_lvls} = (n \cdot p) + 1. \tag{1.2}$$

For this thesis, only  $2x^2$  (two cells in series and two stacks) configuration is considered as five-level output waveform can be achieved using three layers of the HFPP Press-pack design. As the implementation of a NNPP topology with fault ride-through is the focus of this thesis the switching states as well as the potential faults are described in more detail in chapter **X**. The voltage  $V_{C_{ij}}$  across the flying capacitors is [57]

$$V_{C_{ij}} = \frac{i \cdot E}{n \cdot p},\tag{1.3}$$

where *i* is the index of the capacitor in a circuit, *E* is the input voltage, *n* is the number of stages and *p* is the number of cells in series [53]. The voltage constraint  $V_{sw}$  on the switching devices is the same across all switches and is equal to [57]

$$V_{sw} = \frac{E}{n \cdot p}, \tag{1.4}$$

where E is the input voltage, n is the number of stages and p is the number of cells in series [54]. The main advantage of this topology over a classical multilevel converter is the possibility to share the voltage constrains across the circuit, therefore the voltage rating of the flying capacitors and switching devices are reduced. The disadvantages are similar to the majority of the multilevel converter topologies, a large number of power semiconductor switches are needed, which inherently reduces the reliability of the converter. Although low-voltage-rated switches can be utilized in a multilevel converter, each switch requires a gate driver and protection circuits [55].

#### **1.2.5** Active Neutral Point Clamped

The initial proposed concept is shown in Figure 1.15, but the topology was due to the three floating capacitors excessive in terms of costs as well as the volumetric density, to reduce the number of floating capacitors, capacitors C2 and C3 can be eliminated resulting in a simplified topology shown in Figure 1.16.

Fig. 1.15 Initial Active Neutral Point Clamped Converter topology [58].

Active Neutral-point-clamped converter is a hybrid multilevel converter based on a cascade of a three-level Flying capacitor topology and a traditional two-level topology. The switches of 3L FC cells operate in low (fundamental) frequency while switches of the two-level cell operate in high (switching) frequency [49].

Fig. 1.16 Simplified Active Neutral Point Clamped Converter topology.

The removal of capacitors C2 and C3 however resulted in the elimination of the natural balancing aspect of the converter, this was solved in [59], [60] by the implementation of active capacitor voltage control.

The advantage of this topology is that it requires only one more capacitor per phase than a NPC three-level converter [59] to achieve a five level output waveform, but the disadvantage is the unequal distribution of the switching device losses, this is however potentially solvable by the use of different optimization strategies as shown in [60].

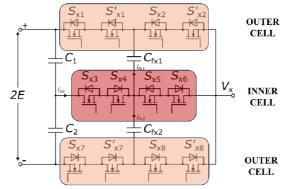

### **2. NESTED NEUTRAL POINT PILOTED CONVERTER**

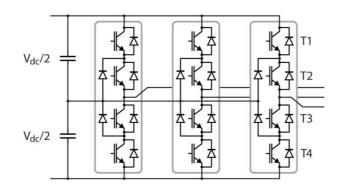

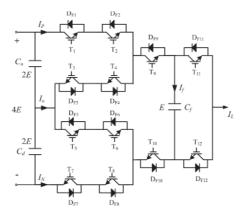

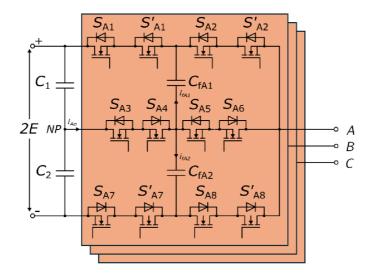

The selection of the multilevel converter topology was based on a paper, where a novel high-frequency press-pack (HFPP) SiC FET module was proposed. This paper was a part of development from the same laboratory as this thesis is. The nested neutral point piloted topology is easily scalable and has switching state redundancy properties, which allows for a fault tolerant/ride-through capabilities, where a fail-to-short behavior of the switching device is expected, a five-level circuit can be achieved within a three layer structure of the HFPP module and can be seen in Figure 2.1a allowing for operation under medium voltage, high current and fast switching transients [10], in Figure 2.1 other multilevel topologies achievable within the three layer HFPP structure can be seen.

Fig. 2.1 HFPP SiC Module topologies: (a) 5L-NNPP, (b) 5L-Vienna-NNPP, (c) 5L-ANPC, (d) 5L-FC, (e) 5L-MMC [48].

The aim of this thesis is to develop a prototype that uses components available off the shelf, to evaluate and gain experience with the control of such a converter topology at a lower voltage and lower power. The control algorithm that is to be developed is then to be used during the experimental phase of the implementation of the HFPP module, the focus of current state of the art papers in this field are on the open circuit fault, where the short-circuit fault is only studied briefly and for fault tolerance capability external devices are used in [61].

In this chapter the nested neutral point piloted topology is to be analyzed further with focus on its subinterval analysis, the effect of the switching states on the capacitor voltages and neutral point current as well as the types of faults which can occur.

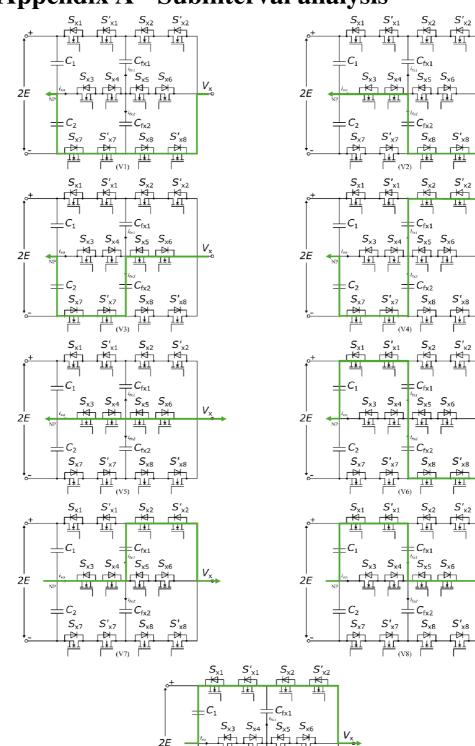

#### 2.1 Subinterval analysis

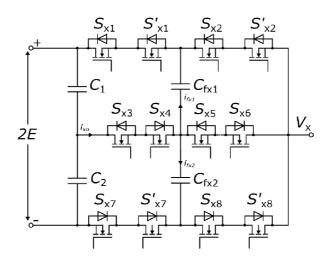

For this chapter only a five-level topology is considered as that is the focus of this work and the limitation of the HFPP SiC module. A general single phase five-level nested neutral point piloted converter circuit is shown in Figure 2.2.

Fig. 2.2 General five level single phase NNPP Topology.

The five-level output can be achieved using nine combinations, each with different effects on the flying capacitors and neutral point current, which is important for achieving a balanced capacitor voltage and the effect is used in the active capacitor voltage balancing algorithm, which is described in chapter 3.1, this balance is important for acquiring a high-quality output waveform. Table 2.1 shows the state of the switching devices for each of the nine combinations as well as the effect on the currents in the circuit [62].

| $V_N$   | $S_{XI}$ | $S_{X2}$ | $S_{X3}$ | $S_{X4}$ | $S_{X5}$ | $S_{X6}$ | $S_{X7}$ | $S_{X8}$ | Vox  | $I_{FX1}$        | $I_{FX2}$        | I <sub>X0</sub> |

|---------|----------|----------|----------|----------|----------|----------|----------|----------|------|------------------|------------------|-----------------|

| $V_1$   | 1        | 1        | 1        | 0        | 1        | 0        | 0        | 0        | Е    | 0                | 0                | 0               |

| $V_2$   | 1        | 0        | 1        | 0        | 1        | 1        | 0        | 0        | E/2  | Iox              | 0                | 0               |

| $V_3$   | 0        | 1        | 1        | 1        | 1        | 0        | 0        | 0        | E/2  | -I <sub>ox</sub> | 0                | Iox             |

| $V_4$   | 1        | 0        | 1        | 0        | 0        | 1        | 0        | 1        | 0    | Iox              | Iox              | 0               |

| $V_5$   | 0        | 0        | 1        | 1        | 1        | 1        | 0        | 0        | 0    | 0                | 0                | Iox             |

| $V_6$   | 0        | 1        | 0        | 1        | 1        | 0        | 1        | 0        | 0    | -I <sub>ox</sub> | -I <sub>ox</sub> | 0               |

| $V_7$   | 0        | 0        | 0        | 1        | 1        | 1        | 1        | 0        | -E/2 | 0                | Iox              | Iox             |

| $V_8$   | 0        | 0        | 1        | 1        | 0        | 1        | 0        | 1        | -E/2 | 0                | -I <sub>ox</sub> | 0               |

| $V_{9}$ | 0        | 0        | 0        | 1        | 0        | 1        | 1        | 1        | -E   | 0                | 0                | 0               |

Table 2.1NNPP Converter Switching states overview

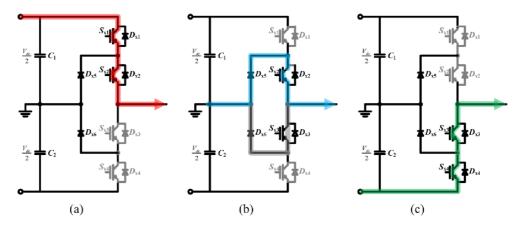

In Figure 2.3 two of the nine combinations are shown, the rest is in appendix A. These combinations are shown for a single leg of a three-phase converter, where the neutral point is referred to as ground point for the output voltage measurement. The switching devices were replaced by SPST switches to better animate the conductive path.

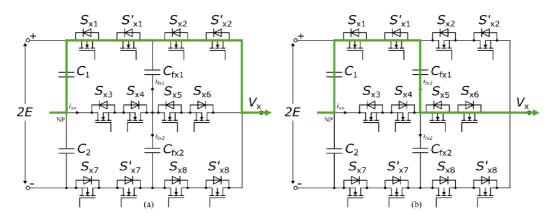

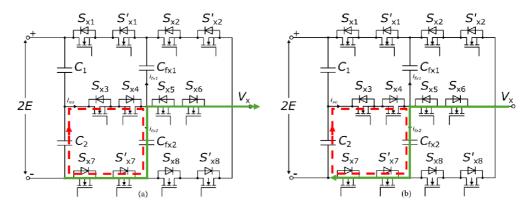

Fig. 2.3 NNPP Topology subintervals (a) V<sub>9</sub>, (b) V<sub>8</sub>.

### 2.2 Types of faults

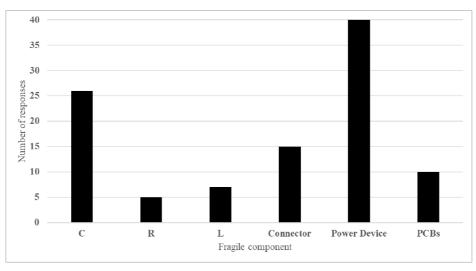

According to [63], approximately 51% of faults in power converters is caused by semiconductors and capacitors. In a survey from [64] power device was selected by 31% of the respondents as the most fragile component, making it the most selected option as can be seen in Figure 2.4.

Fig. 2.4 Results of survey on power converter fault causes.

Based on these sources, the focus is put on the fault analysis of the switching devices and fault of other devices such as capacitors, gate drivers etc... is not considered. The failure rate of the switching devices and the converter configuration itself is also not described as it was already sufficiently described in [65] as well as other literature.

Two common fault modes of a traditional switching device are open- and short-circuit faults, but considering the use of HFPP Press-pack switching module, where the aim is to have a fail-to-short behavior the open-circuit fault is less prevalent then in case of a wire-

bond, where a bond wire fusing leads to an open circuit [66], only short-circuit faults are to be analyzed and considered in the development of the control algorithm.

A short-circuit fault is the inability of a switch to stop conducting when a turn on signal is no longer present. This can due to the amount of energy present in power electronics converters cause severe consequences not only on the switch, but also on the connected components, such as the capacitors or the PCB of the converter and can, if present for longer than the short-circuit withstand capability guarantee of the manufacturer lead to thermal runaway [67].

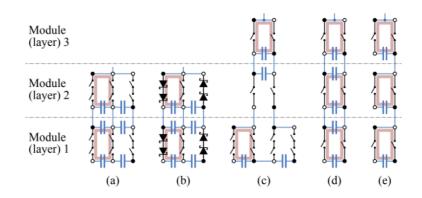

According to [61], where a short-circuit analysis of the nested neutral point piloted circuit topology was conducted, the fault of the converter can be grouped into two groups; the outer cell fault and the inner cell fault in figure 2.5 the group division is shown.

Fig. 2.5 NNPP Converter fault type division.

#### 2.2.1 Outer cell fault

The outer cell fault is fault of the switching devices  $S_{x1}$ ,  $S'_{x1}$ ,  $S_{x2}$ ,  $S'_{x2}$ ,  $S_{x7}$ ,  $S'_{x7}$ ,  $S_{x8}$  and  $S'_{x8}$ , where x is the phase leg marking of the converter. As each of the switches is redundant, and when failure occurs, on for example  $S_{x1}$ , the switch  $S'_{x1}$  can still be used to control the circuit, however the switch would have to withstand a bigger voltage that it may be rated to, therefore the solution would be to either use another pair of switching devices in series or to increase the voltage rating of the switching device used. Due to this reason and the simplicity of solving this fault, it is not considered during the development of the proposed control algorithm but should be considered for commercial applications.

#### 2.2.2 Inner cell fault

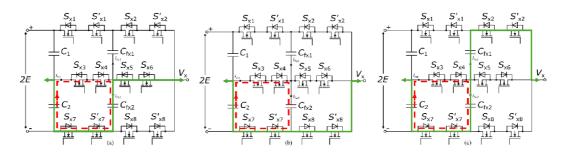

The inner cell fault is defined as the short circuit failure of the switching devices  $S_{x3}$ ,  $S_{x4}$ ,  $S_{x5}$  and  $S_{x6}$ . When, for example, the switching device  $S_{x3}$  fails, the effect on the circuit is during the subintervals  $V_6$ ,  $V_7$  and  $V_9$ , during which a current loop would be formed by switching devices  $S_{x3}$ ,  $S_{x7}$ ,  $S'_{x7}$  and  $S_{x4}$ . This current loop would force the energy from the DC link capacitor  $C_2$  to flow to the flying capacitor  $C_{fx2}$ , this current would be extremely high as the capacitors used in power converters have low ESR and ESL and could cause damage to the components in the circuit.

Fig. 2.6 NNPP Converter inner cell fault current loops during (a) subinterval V<sub>6</sub>, (b) subinterval V<sub>7</sub>, (c) subinterval V<sub>9</sub>.

The resulting current loops for this example are shown in Figure 2.6. Where the effect of the short-circuit failure of the switch  $S_{x3}$  can be seen. Similar procedure was taken during the evaluation of the rest of the switching devices in the inner cell group. The conclusion is summarized in table 2.2.

Table

2.2

NNPP Converter inner cell fault current loop overview

| Switch at fault            | Current loop formed in subinterval               |

|----------------------------|--------------------------------------------------|

| S <sub>x3</sub>            | V <sub>6</sub> , V <sub>7</sub> , V <sub>9</sub> |

| $\mathbf{S}_{\mathrm{x4}}$ | $V_1, V_2, V_4$                                  |

| S <sub>x5</sub>            | $V_4, V_8, V_9$                                  |

| $S_{x6}$                   | $V_1, V_3, V_6$                                  |

The inner cell fault has the potential to be destructive and influence the functionality of the converter. Therefore, an algorithm is to be proposed in this thesis to deal with the issue of current loops forming when a short-circuit fault occurs in one of the described switches. In [61] external devices such as mechanical switches and fuses are used to achieve this, but this requires additional components in the high current path, which is undesirable. An active gate control is to be implemented to mitigate the external components in the high current path and instead, use the active region of the switch utilizing gate-source voltage manipulation of the switching device to detect and to resolve a short-circuit fault, this is described in detail in the chapter 4.4.

### **3.** CONTROL ALGORITHM

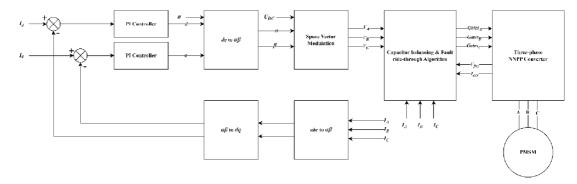

The control algorithm is the main part of this thesis, the goal is to develop an algorithm to control a three-phase nested neutral point piloted converter with a fault ride-through capability as well as advanced features such as active capacitor voltage balancing, space vector modulation of the output voltage for an optimal performance when operating with AC motors as well as third harmonic injection to improve the performance of the converter. Feedback loop to control the direct axis and the quadrature axis current is also to be implemented to allow Field-Oriented Control of the connected motor. High switching frequency is to be used to allow the use of motors with a high number of pole pairs. Additional features such as Flux-weakening, MTPA and other high-performance motor specific features shown to have the ability to improve the overall system performance are not considered in the design of the control algorithm nor the converter as they have been previously implemented as shown in [68], [69], [70], [71].

Most of the features listed have been previously implemented and are mostly commercially available, except for the method for fault ride-through, which is described in the chapter 3.5. At the time of writing, no paper has been presented to use the proposed method.

### 3.1 Active capacitor voltage balancing

In order to achieve an optimal performance of a nested neutral point piloted converter, it is crucial to achieve balance of the voltages of the capacitors [72], [73]. This balance can be in many multicell converter cases be achieved naturally [74], [75], [76], however such balancing property is usually dependent on the properties of the connected load and on the use of Phase Shifted Pulse Width Modulation control scheme as shown in [77] and [78]. A balance booster is proposed in [79], it is a resonant RLC circuit, that accelerates the natural balancing property of the converter [80], this however introduces power losses. As fault ride-through capability is the main requirement for the control algorithm, a reliance on the natural balancing property either with or without the use of a balance booster is not sufficient as the load condition in a three-phase circuit may change dynamically depending on the motor/grid load as described in [81], [82] and [83]. Therefore, an active capacitor voltage balancing algorithm needs to be implemented, many solutions have already been presented such as [84], [85] and [86]. These algorithms use the properties of the different subintervals and their effect on the current flowing through the neutral point and the two flying capacitors.

A balance of the capacitors voltages was in the first version of the algorithm achieved by slightly modifying the ACVB solution described in [87], where a dynamic model of the neutral-point voltage of the nested neutral point piloted topology is established. This model is then used to calculate the zero-sequence voltage component. Such a solution has been previously used in different topologies such as ANPC in [88] and NPC in [89]. A zero-sequence component is zero in case of symmetrical load, however due to conditions described previously an asymmetrical load may be formed on the output of the converter, therefore between the neutral points, there is a voltage difference, which is referred to as the zero sequence voltage [90], which in turn influences the DC-link capacitor balance.

From the measured voltages  $V_{c1}$  and  $V_{c2}$  of the DC-link capacitors, we can calculate the voltage imbalance and using the known capacitance C of the DC-link capacitor we can calculate the neutral point current  $I_{balance}$  which is required to achieve their balance

$$I_{balance} = \frac{C \frac{(V_{c2} - V_{c1})}{K}}{T_s},$$

(3.1)

where  $I_{balance}$  is the neutral point current, C is the capacitance,  $V_{c1}$  and  $V_{c2}$  are the voltages of the DC-link capacitors, K is the number of switching cycles that are used to achieve the neutral-point voltage-balance and  $T_s$  the switching cycle.

By applying  $I_{balance}$  for K switching cycles a balanced state of the DC-link capacitors is achieved. To achieve the  $I_{balance}$  current a zero-sequence voltage component is calculated from the geometric relationship and is summed together with the reference signals for the three phases of the converter. The actual reference voltage signals  $u_x$  for each of the phases then are

$$u_{x} \begin{cases} u_{a} = u_{a0} + u_{z} \\ u_{b} = u_{b0} + u_{z} \\ u_{c} = u_{c0} + u_{z} \end{cases}$$

(3.2)

where  $u_{a0}$ ,  $u_{b0}$  and  $u_{c0}$  are the reference voltages of the three phases before adjustment and  $u_z$  is the zero-sequence voltage, to also achieve the regulation of the flying capacitors an optimal zero-sequence voltage selection method is proposed in [73].

This method results in a stable and fast balancing of both of the DC-link capacitors as well as the flying capacitors, however due to the requirements to control a high-speed motor resulting in high switching frequency as well as the additional computational burden of the fault ride-through capability and space vector modulation a simpler method was used. Slightly sacrificing the balancing accuracy of the converter but giving greater flexibility in the development of the fault ride-through capability by simplifying the subinterval selection procedure.

The method used in the final control algorithm is described in detail in [91]. First based on a space vector modulation algorithm that is described in Chapter 3.3 target vector is determined, from the target vector and the sector of the voltage space vector diagram in which the target vector lies, the three basic vectors with the lowest resulting common mode voltage can then be calculated

$$U_{com} = \frac{E \cdot [(V_a - 2) + (V_b - 2) + (V_c - 2)]}{12},$$

(3.3)

where  $V_a$ ,  $V_b$ ,  $V_c$  are the phase voltage outputs. Based on their distance  $d_i$  of to the target referce vector  $V_{ref}(V_g^*, V_h^*)$  in the *gh* coordinate system the two nearest vectors are selected; the distance is calculated as

$$d_{i} = \sqrt{\left(V_{g}^{*} - V_{gi} + \frac{1}{2}V_{h}^{*} - \frac{1}{2}V_{hi}\right)^{2} + \frac{3}{4}(V_{h}^{*} - V_{hi})^{2}},$$

(3.4)

where  $(V_{gi}, V_{hi})$  is the coordinate of  $\mathbf{V}_i$  (i = 1, 2, 3), from the two vectors then based on the state of the flying capacitor voltages  $V_{fx11}$  and  $V_{fx12}$  subintervals are chosen, which minimize the voltage deviation of their voltages, the flowchart of the selection process is then shown in Figure 3.1.

Fig. 3.1 Flying capacitor selection process flowchart [91].

After choosing the two subinterval candidates the average value of the neutral point current  $I_{on}$  can be calculated for each of them

$$I_{on} = \sum_{x=a,b,c} (S'_{x1} + S_{x4} - 1) I_x, \tag{3.5}$$

where x represents each of the three phases and  $S'_{x1}$  the negation of the state of the switching device  $S_{x1}$  and  $I_x$  the output current. Subinterval with the minimal result of the following equation is selected as the final one to be used

$$\Delta v'_{on} = \Delta v_C + \Delta v_0 = \frac{v_{fC1} - v_{fC2}}{2} - \frac{l_{on}T_s}{2C},$$

(3.6)

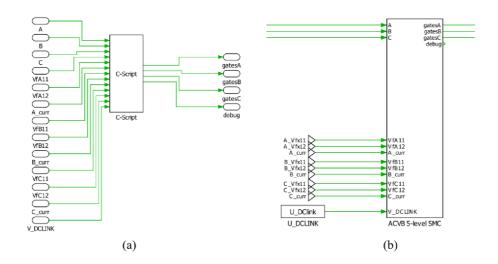

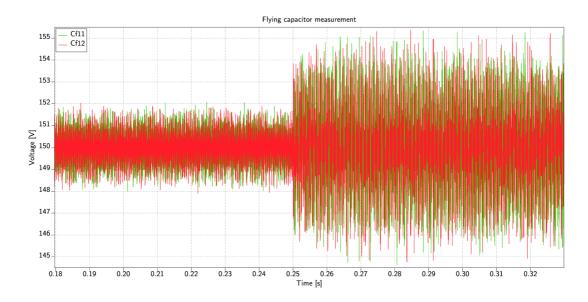

Where  $v_{fC1}$  and  $v_{fC2}$  are the voltages of the capacitors,  $I_{on}$  the neutral point current, *C* their capacitance and  $T_s$  the switching cycle. This algorithm is then implemented in the simulation as a block shown in Figure 3.2 and the results of the balancing properties are shown in Figure 3.16 as a part of the simulation chapter 3.6.1.

Fig. 3.2 Active Capacitor Voltage Balancing block in simulation software (a) internal structure, (b) block in schematic.

#### 3.2 Coordinate transformations

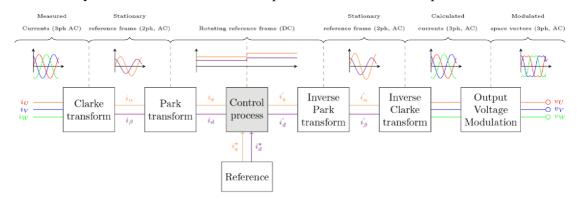

Coordinate transformations play a crucial role in advanced control of three-phase circuits, particularly in motor control applications. These transformations enable the conversion of three-phase AC values from and into  $\alpha\beta$  reference frame or to the dq reference frame, allowing for more straightforward implementation of control algorithms and improved regulation of speed and torque of an electric motor. Coordinate transformations are an integral part of three-phase circuit control as shown in [92], [93] and [94]. Figure 3.3 shows the layout of the transformation implementation for a three-phase motor.

Fig. 3.3 Three-phase control block diagram [95].

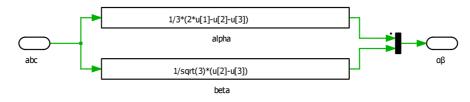

#### 3.2.1 Clarke transformation

Clarke transformation also known as *alpha-beta* ( $\alpha\beta$ ) [96] transformation is utilized to simplify the analysis and control for example of three-phase electric motors, where the measured current from each of the three phases on the output in case of a balanced load

into two axis in a stationary reference frame allowing for simpler processing. Together with Park transform and their inverse transformations it is commonly used in Field Oriented Control employed in motor drives for example [97], [98] and [99].

The following equation [100] shows how the components are calculated for a general three-phase system in a matrix form:

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \\ V_{0} \end{bmatrix} = \frac{2}{3} \times \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} V_{a} \\ V_{b} \\ V_{c} \end{bmatrix},$$

(3.7)

where  $V_{\alpha}$ ,  $V_{b}$ ,  $V_{c}$  are the three-phase components, in this case the output voltage and  $V_{\alpha}$ ,  $V_{\beta}$  the alpha and beta components respectively and  $V_{0}$  the zero component, which is in case of a balanced system equal to zero [100]. The individual components can then be calculated

$$\begin{cases} V_{\alpha} = \frac{1}{3} (2 \cdot V_{a} - V_{b} - V_{c}) \\ V_{\beta} = \frac{1}{\sqrt{3}} (V_{b} - V_{c}) \\ V_{0} = \frac{1}{3} (V_{a} + V_{b} + V_{c}) \end{cases}$$

(3.8)

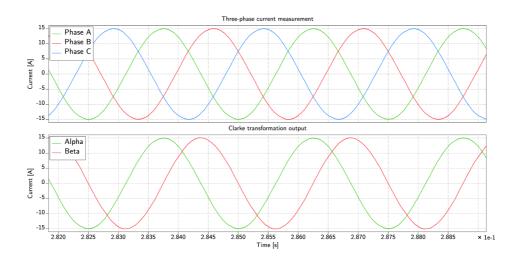

These calculations are implemented in the simulation as a subsystem block with two functions shown in Figure 3.4.

Fig. 3.4 Clarke transformation implementation in simulation.

Figure 3.5 shows the output of the subsystem block in simulation. This output is generated based on the current measurement obtained from a three-phase symmetrical load.

Fig. 3.5 Input and output of the Clarke transformation.

### 3.2.2 Park transformation

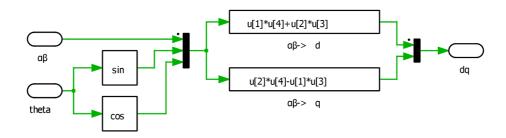

The previously described Clarke transformation is often used in conjunction with a Park transformation [101], [102]. The input of a Park transformation is in the case of motor control an output of a Clarke transformation, where the two components *Alpha* and *Beta* are converted from a stationary reference frame into a rotating reference frame, using *Theta*, in this case, the output of the motor position sensor with offset to obtain the electrical angle. The general equation for Park transformation is [103]

$$\begin{bmatrix} V_d \\ V_q \end{bmatrix} = \begin{bmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} V_\alpha \\ V_\beta \end{bmatrix},$$

(3.9)

where  $V_d$ ,  $V_q$  are the direct and quadrate axis components,  $\theta$  is the reference of the rotating frame, in case of motor control it is the electrical angle when the rotor flux is aligned with the stator phase A [104] and  $V_{\alpha}$ ,  $V_{\beta}$  are the outputs of the Clarke transformation. Each component of the transformation can be calculated

$$\begin{cases} V_d = \cos\theta \cdot V_\alpha - \sin\theta \cdot V_\beta \\ V_q = -\sin\theta \cdot V_\alpha + \cos\theta \cdot V_\beta \end{cases}$$

(3.10)

The Park transformation enables us to obtain a steady-state DC representation that reflects the currents within an AC three-phase system. This steady-state value can be effectively utilized for controlling the converter. Additionally, conventional control techniques like PI and PID controllers can be applied using this transformed representation for precise control and regulation of the system.

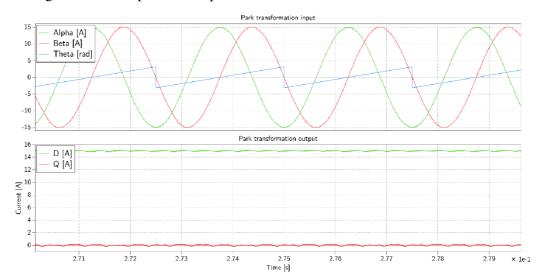

Fig. 3.6 Park transformation implementation in simulation.

The implementation of the Park transformation is similar to the Clarke transformation but involves the use of trigonometric functions applied to the *Theta* input. This addition simplifies the computation of the d and q functions and reduces the overall number of calculations required. Figure 3.6 shows the internal structure of the Park transformation and in Figure 3.7 the input and output of the transformation are shown.

Fig. 3.7 Input and output of the Park transformation.

# 3.3 Space vector modulation

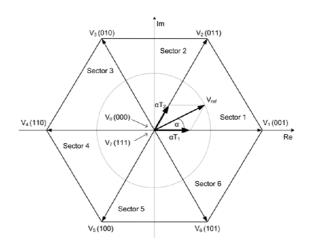

Space vector pulse width modulation (SVPWM) is a technique for synthesizing a desired reference voltage vector to a three phase PWM pattern at the output of the inverter without the use of a carrier as explained in [105] and [106] and as shown in Figure 3.8. Space vector modulation offers improved DC bus voltage utilization by up to 15.5%, simple implementation in a DSP and improved harmonic performance [107], [108].

Fig. 3.8 Reference voltage vector in the alpha-beta plane [109].

As field-oriented control is to be used, the space vector modulation is to be implemented, the inputs for the modulation algorithm are the output of an inverse park transformation, the d and q axis values can be converted to the gh coordinate system using the equation from [110]

$$\begin{bmatrix} V_g \\ V_h \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{\sqrt{3}} \\ 0 & \frac{2}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} V_d \\ V_q \end{bmatrix},$$

(3.11)

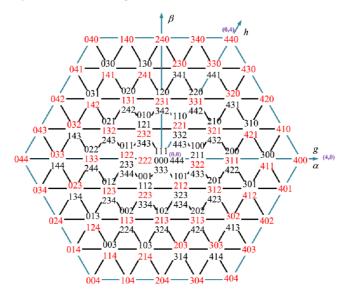

where  $V_d$  and  $V_q$  are the outputs of the PI controllers,  $\theta$  the angle of rotation as shown in [111]. Figure 3.9 shows the voltage space and switching state for a five-level converter in the *gh* coordinate system, the voltage levels are normalized to the DC-link voltage.

Fig. 3.9 Five level converter voltage space [91].

The closed interval sector for a reference vector  $V_{ref}(V_g^*, V_h^*)$  is a triangle consisting of three space points  $V_1$ ,  $V_2$ ,  $V_3$

$$\begin{cases} V_{1} = (V_{gf} + 1, V_{hf}) \\ V_{2} = (V_{gf}, V_{hf} + 1), \\ V_{3} = (V_{gf}, V_{hf}) \end{cases}$$

(3.12)

where  $V_{gf}$  and  $V_{hf}$  are the outputs of a floor function of  $V_g^*$  and  $V_h^*$  respectively. As per the subinterval analysis, there are multiple redundant states for some of the output levels. If a reference vector  $V_{ref}(V_g^*, V_h^*)$  is synthesized to one of such levels an active capacitor voltage balancing, and common mode voltage reduction algorithm described in chapter 3.1 is used to determine the final switching state combination, the duty cycle is then calculated to synthesize the reference vector accurately as described in [91].

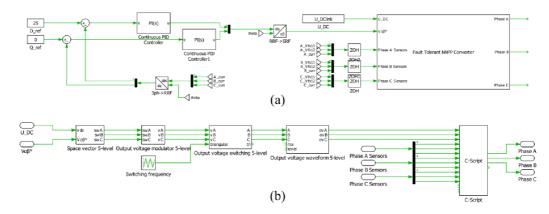

Fig. 3.10 Simulation block schematic (a) control part, (b) modulation part.

The Figure 3.10b shows the block layout of the space vector modulation part of the control algorithm, Figure 3.10a shows the output of the PI controllers for the *d* and *q* are fed into an inverse part transformation block RRF->SRF together with the sensor data, the output of which is then fed into a Fault Tolerant NNPP Converter in which.

Fig. 3.11 Input and output of the Space Vector Modulation block.

The input data as well as the space vector output is shown in Figure 3.11. The output is then used by the active capacitor balancing block to determine the actual states of the switching devices based on other sensor data.

# 3.4 Fault detection

In order for the algorithm to be able to have a fault ride-through capability, the fault first needs to be detected, there are many options available such as desaturation detection as described in [112] and [113], which is challenging to implement due to the fast switching properties of the wide bandgap semiconductor switches used in the design. Another option is to use a senseFET technology as shown in [114], where a scaled down current is measured across a shunt resistor usually integrated in the switching device itself, this increases the costs and reduces the selection due to the availability of such devices. The last considered option was the use of a shunt resistor or other form of current measurement of the current carrying path, this method can in some real world applications be less suitable due to the increased losses as described in [115], [116] and [117], but use of hall effect and new current sensors such as TLI4791 from Infineon may help with the loss problem as they offer high accuracy measurement with sufficiently fast overcurrent detection [118], the choice of the current sensor as well as the actual hardware configuration for fault detection is described in chapter 4.3.1.

For the sake of the simulation the fault of the switching device is controlled, an external switch is used to bridge the switching device and act as a short circuit. The algorithm uses the measured current as a form of detection of the state of the switching device and compares it to the desired current through the path in a particular subinterval. In case the two values do not match, the fault is evaluated, and a switch failure mode is determined. Based on that information and the desired output subinterval the control algorithm acts accordingly. This behavior is described in the next section and is the main contribution of this thesis to the topic of nested neutral point piloted converter development as it allows for a smooth fault ride-through operation, be it with minor performance degradation.

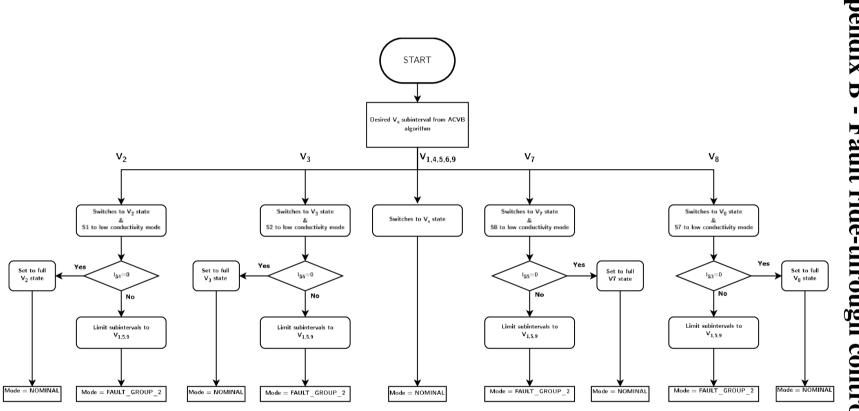

# 3.5 Fault ride-through

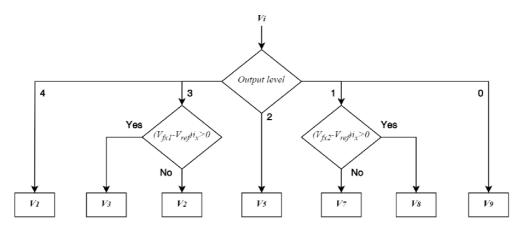

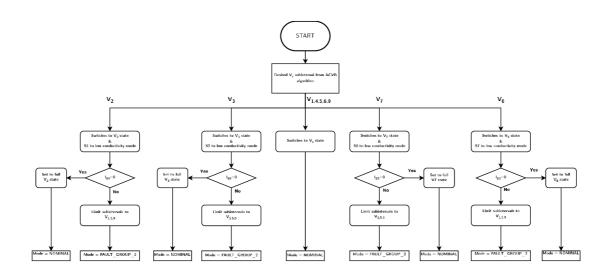

Based on the desired subinterval a strategy for the control of the actual switches is determined, the control-flow graph for the strategy is shown in Figure 3.12, the control-flow graph is also inserted as an Appendix B. As per the subinterval and types of fault analysis, only the subinterval faults for which the failure may be destructive are considered. At the time of writing no method without inserting additional devices in the high current path for fault ride-through has been presented.

Fig. 3.12 Propose fault ride-through control-flow graph.

The destructive failure of controller may occur when the desired subintervals are  $V_{2,3,7,8}$  as in these subintervals a high-current loop may be formed between the capacitors. Such a fault is shown in Figure 3.13, where a switch configuration for a subinterval  $V_8$  is presented. In this subinterval, in case of a failure of the switch  $S_3$  a short circuit is formed through the switches  $S_7$ ,  $S_3$ , the capacitors  $C_2$  and  $C_{fx2}$  and the diode in the switch  $S_4$ . This current will be extremely high and can reach thousands of amperes [119] due to the low resistance path formed between the two capacitors and the low ESR and ESL of the capacitors. Such high current can almost instantly damage the converter assembly and even cause an electrocution and fire [120].

Fig. 3.13 Fault of switch S<sub>3</sub> during V<sub>8</sub> subinterval (a)  $i_x > 0$ , (b)  $i_x < 0$ .

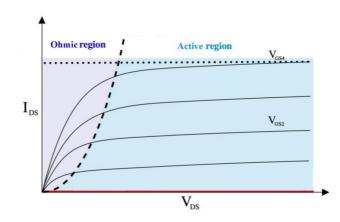

To prevent this risk the switching device, in the case of the prototype, where a SiC MOSFET is used an active gate control is implemented. In some instances of the subintervals the switches are operated in a region, where the drain current  $I_D$  is a function of the  $V_{GS}$  voltage and  $V_{DS}$ , which can be considered constant and MOSFET is therefore operated in the active region as shown in Figure 3.14.

Fig. 3.14 MOSFET Drain current vs. Gate-source voltage dependance [121].

By adjusting the  $V_{GS}$  voltage, the drain current  $I_D$  can be limited to a known value. This current is then measured by a fast current sensor and based on it either the full  $V_{GS}$  is applied, or the converter switches into a "*fault mode*" to prevent damage from occurring.

Such a fault tolerant method has its shortcomings, one of which is the need for a more advanced gate driver to be used as well as the increased number of control signals, these shortcomings are described in more detail in the chapter 4.4.

### 3.6 Simulation

Simulation of the control algorithm as well as the entire power converter was done in PLECS by Plexim. This software is designed for power electronics simulation [122] and was initially developed as a piece-wise linear electrical circuit toolbox under Simulink [123]. It also includes tools for thermal simulation allowing the estimation of switching and conduction losses [124] as well as code generation for implementation and execution of the algorithms developed in PLECS on real-world targets [125] such as the Texas Instruments C2000 [126], STMicroelectronics STM32 MCUs [127] and the RT Box HiL Platform [128]. The ability to generate code directly from the simulation model will in future testing allow for rapid changes to be made to optimize the algorithm.

Fig. 3.15 Converter block diagram.

A block diagram of the converter for the evaluation purposes of the proposed algorithm is presented in Figure 3.15. The simulation is carried out under ideal conditions, where disturbances, non-linearities and other external conditions which may influence the actual result in the real world such as gate driver dead-times etc. are not considered as the simulation model would be too complicated for the purpose of evaluating the proof of concept of the developed algorithm and would be beyond the scope of this thesis.

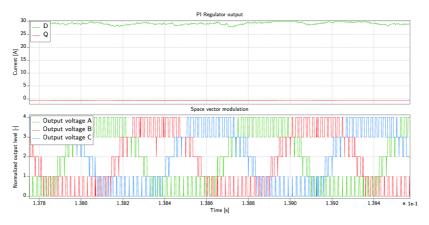

### 3.6.1 Normal operation

First a simulation of the basic control of the converter is conducted to ensure correct operation under normal conditions, in this simulation the active capacitor voltage balancing algorithm, the space vector modulation as well as the current regulation components are evaluated. The initially requested current changes at time  $t_{change}$  to check the stability of the current control loop and resilience to abrupt changes in load conditions. Parameters of the simulation are concluded in Table 3.1.

| Parameter                                   | Symbol                     | Value | Unit      |

|---------------------------------------------|----------------------------|-------|-----------|

| Simulation time                             | t <sub>sim</sub>           | 0.5   | S         |

| Maximum step size                           | t <sub>step</sub>          | 0.1   | μs        |

| Reference frequency                         | $\mathbf{f}_{ref}$         | 900   | Hz        |