### VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

BRNO UNIVERSITY OF TECHNOLOGY

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ ÚSTAV VÝKONOVÉ ELEKTROTECHNIKY A ELEKTRONIKY

FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION DEPARTMENT OF POWER ELECTRICAL AND ELECTRONIC ENGINEERING

# FIELD PROGRAMMABLE GATE ARRAYS USAGE IN INDUSTRIAL AUTOMATION SYSTEMS

UŽITÍ PROGRAMOVATELNÝCH HRADLOVÝCH POLÍ V SYSTÉMECH PRŮMYSLOVÉ AUTOMATIZACE

DIZERTAČNÍ PRÁCE

DOCTORAL THESIS

AUTOR PRÁCE

ZIAD NOUMAN

AUTHOR

VEDOUCÍ PRÁCE

doc. Ing. BOHUMIL KLÍMA, Ph.D.

**SUPERVISOR**

**BRNO 2015**

### Thesis Supervisor:

Supervisor: doc.Ing.Bohumil Klíma, Ph.D.

Department of Power Electrical and Electronic Engineering

Faculty of Electrical Engineering and Communication

Brno University of Technology

Technicka 10

616 00 Brno

Czech Republic

Copyright © 2015 **Author**: Ziad Nouman

### Abstract

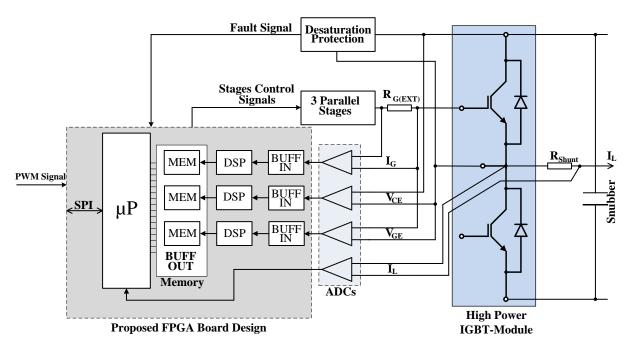

This doctoral thesis deals with the usage of Field Programmable Gate Arrays (FPGAs) in a diagnosis of power inverters which use the IGBTs transistors as switching devices. It is focused on the IGBT gate drives and their structures. As long as the transient phenomena and other quantities such as  $I_G$ ,  $V_{GE}$ ,  $V_{CE}$  shows the IGBT degradation during the switching process (turn-on, turn-off), a new IGBT gate driver architecture is proposed for measuring and monitoring these quantities. Quick measurements and monitoring during the IGBT switching process require high sampling frequencies. Therefore, high speed parallel ADC converters ( $> 50 \, \text{MSPS}$ ) are proposed.

The thesis is focused on the FPGA design (hardware, software). A new FPGA board is designed for desired functions implementation such as IGBT driving using multiple stages, IGBT monitoring and diagnosis, and interfacing to inverter controller.

### **Keywords**

Fault detection and diagnosis (FDD), Fault Tolerant Control (FTC), Field Programmable Gate Arrays (FPGA), Insulated-Gate Bipolar Transistor (IGBT), gate drive, ADC, monitoring, PC board, redundancy, Very High Speed Integrated Circuit Hardware Description Language(VHDL), Verilog, Fast Fourier Transform (FFT), DDR2SDRAM, Industrial automation.

### **Abstrakt**

Tato disertační práce se zabývá využitím programovatelných hradlových polí (FPGA) v diagnostice měničů, využívajících spínaných IGBT tranzistorů. Je zaměřena na budiče těchto výkonových tranzistorů a jejich struktury. Přechodné jevy veličin, jako jsou  $I_G$ ,  $V_{GE}$ ,  $V_{CE}$  během procesu přepínání (zapnutí, vypnutí), mohou poukazovat na degradaci IGBT. Pro měření a monitorování těchto veličin byla navržena nová architektura budiče IGBT. Rychlé měření a monitorování během přepínacího děje vyžaduje vysokou vzorkovací frekvenci. Proto jsou navrhovány paralelní vysokorychlostní AD převodníky (> 50 MSPS).

Práce je zaměřena převážně na návrh zařízení s FPGA včetně hardware a software. Byla navržena nová deska plošných spojů s FPGA, která plní požadované funkce, jako je řízení IGBT pomocí vícenásobných paralelních koncových stupňů, monitorování a diagnostiku, a propojení s řídicí jednotkou měniče.

### Klíčová slova

Detekce poruch a diagnostika (FDD), Řízení odolné vůči poruchám (FTC), Programovatelné hradlové pole (FPGA), Tranzistor IGBT, Budič, Analogově-digitální převodník, monitoring, PC deska, redundance, Jazyk VHDL, Verilog, Rychlá Fourierova transformace (FFT), DDR2-SDRAM, Průmyslová automatizace.

#### **DECLARATION**

I declare that I have elaborated my doctoral thesis on the theme of Field Programmable Gate Arrays Usage in Industrial Automation Systems, under the supervision of doc. Ing. Bohumil Klíma, Ph.D. and with the use of technical literature and other sources of information which are all quoted in the thesis and detailed in the list of literature at the end of the thesis.

\_\_\_\_

Ziad Nouman Brno, 2015

### Acknowledgements

First of all, I would like to express my gratitude to my supervisor doc. Ing. Bohumil Klíma, Ph.D. for creating the preconditions for the work guiding me through the process. His comments and support especially during the finalizing period of the work are greatly appreciated. I also wish to thank my colleagues in the department of Power Electrical and Electronic Engineering at Brno University of Technology for their comments, ideas, and suggestions during the work. I would like to express my thanks to Tishreen University in Syria for help and support.

I would like to thank all of my friends in Czech Republic.

I would like to express my heartfelt thanks to my fiancee for her support and encouragement during the execution of this work.

Finally, my greatest thanks go to my family members, for their infinite patience and care.

### Contents

|   | List | t of Figures                                                       | ix   |

|---|------|--------------------------------------------------------------------|------|

|   | List | t of Tables                                                        | xii  |

|   | Abl  | breviations                                                        | xiii |

| 1 | Intr | roduction                                                          | 1    |

|   | 1.1  | Motivation and Objectives                                          | 2    |

|   | 1.2  | Structure of the Thesis                                            | 2    |

| 2 | Bac  | ekground and State of the Art                                      | 4    |

|   | 2.1  | IGBT Basics                                                        | 5    |

|   |      | 2.1.1 Basic Structure and Operation                                | 5    |

|   |      | 2.1.2 Switching Characteristics of IGBT                            | 8    |

|   |      | 2.1.3 IGBT Switching Losses                                        | 9    |

|   |      | 2.1.4 IGBT Conduction Losses                                       | 10   |

|   |      | 2.1.5 Free Wheeling Diode (FWD)                                    | 11   |

|   |      | 2.1.6 Thermal Characteristics of IGBT Modules                      | 12   |

|   |      | 2.1.7 IGBT Gate Drive Circuit                                      | 13   |

|   | 2.2  | Present State in Inverter Diagnosis                                | 15   |

| 3 | Pre  | oposed IGBT Gate Driver Architecture                               | 34   |

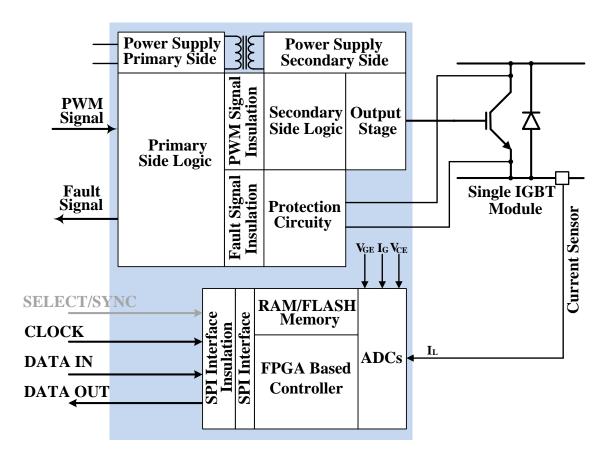

|   | 3.1  | Gate Driver Interface                                              | 35   |

|   | 3.2  | Data Exchange SPI Protocol                                         | 37   |

|   | 3.3  | The proposed IGBT Gate Driver                                      | 38   |

|   | 3.4  | Design of the Proposed IGBT Gate Driver                            | 40   |

|   |      | 3.4.1 Design of the Driver Stages of Proposed IGBT Gate Driver     | 41   |

|   |      | 3.4.2 Design of the Power Supply System for the Proposed IGBT Gate |      |

|   |      | Driver                                                             | 45   |

|   |      | 3.4.2.1 Design of the Positive and Negative Regulators for the Re- |      |

|   |      | quired Output voltages                                             | 47   |

|   |      | 3.4.2.2 Design of the Insulated DC/DC Converters                   | 51   |

|   |      | 3.4.2.3 Design of the PWM Controller                               | 53   |

| CONTENTS | vii |

|----------|-----|

|----------|-----|

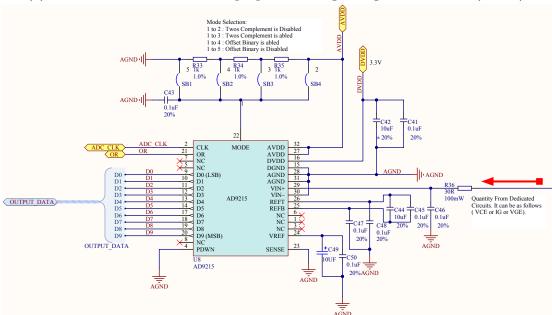

|              |                | 3.4.3    | The Proposed Analog to Digital Converters Design                       | 55           |  |  |

|--------------|----------------|----------|------------------------------------------------------------------------|--------------|--|--|

| 4            | FPO            | GA Bo    | oard Design for IGBT Control and Diagnosis                             | 57           |  |  |

|              | 4.1            | Introd   | luction                                                                | 57           |  |  |

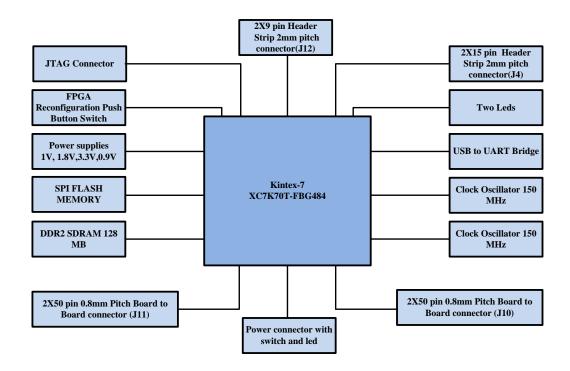

|              | 4.2            | Propos   | sed FPGA Board Design                                                  | 57           |  |  |

|              |                | 4.2.1    | Description of Hardware Components                                     | 59           |  |  |

|              |                |          | 4.2.1.1 Kintex-7 XC7K70T-FBG484 Structures                             | 59           |  |  |

|              |                |          | 4.2.1.2 Power Supply Structure                                         | 61           |  |  |

|              |                |          | 4.2.1.3 System Clock Sources                                           | 63           |  |  |

|              |                |          | 4.2.1.4 FPGA Configuration                                             | 64           |  |  |

|              |                |          | 4.2.1.5 Quad SPI Flash Memory 128 Mb                                   | 66           |  |  |

|              |                |          | 4.2.1.6 XADC Design                                                    | 68           |  |  |

|              |                |          | 4.2.1.7 DDR2 SDRAM Memory Design                                       | 73           |  |  |

|              |                |          | 4.2.1.8 USB to UART Bridge                                             | 78           |  |  |

|              |                |          | 4.2.1.9 User GPIO LEDs                                                 | 79           |  |  |

|              |                |          | 4.2.1.10 Board to Board Connector J11                                  | 79           |  |  |

|              |                |          | 4.2.1.11 Board to Board Connector J10                                  | 80           |  |  |

|              |                |          | 4.2.1.12 Board to Board Connector J12                                  | 81           |  |  |

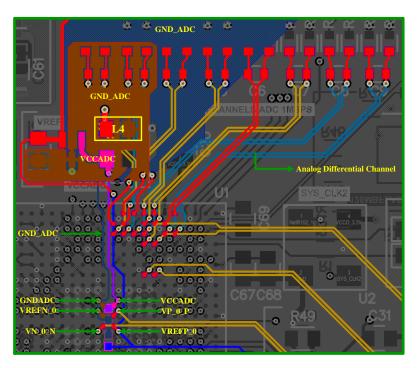

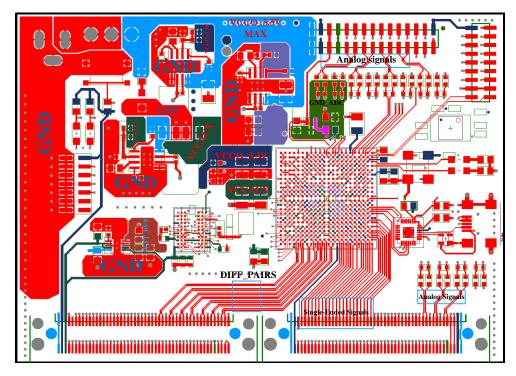

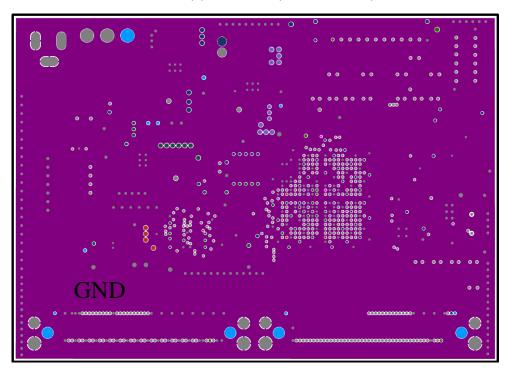

|              |                | 4.2.2    | PC Layout of the Proposed FPGA Board                                   | 81           |  |  |

|              |                | 4.2.3    | Testing the Proposed FPGA Board                                        | 86           |  |  |

|              |                | 4.2.3    | resting the Proposed Pr GA Board                                       | 00           |  |  |

| <b>5</b>     | Stag           | ges Co   | ntrol Signals Generator Design                                         | 91           |  |  |

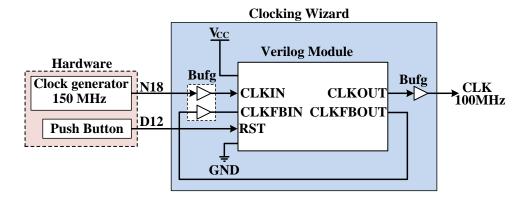

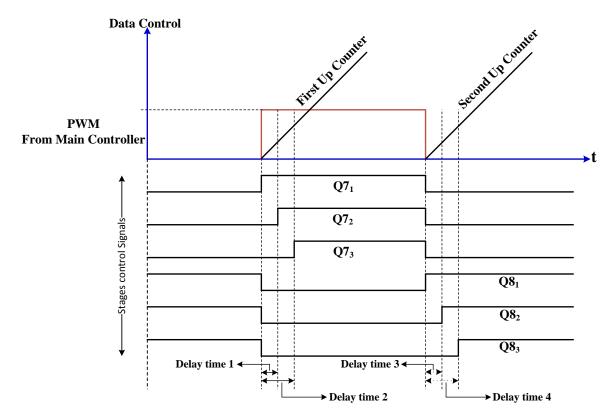

|              | 5.1            | Clocki   | ing Wizard                                                             | 92           |  |  |

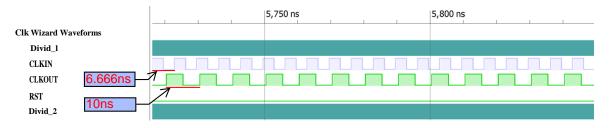

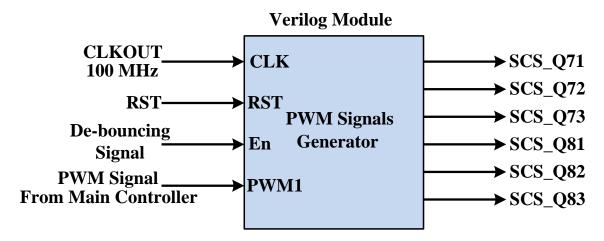

|              | 5.2            | Stages   | S Control Signals Generator                                            | 93           |  |  |

|              | 5.3            | The S    | witch De-bouncer Circuit                                               | 95           |  |  |

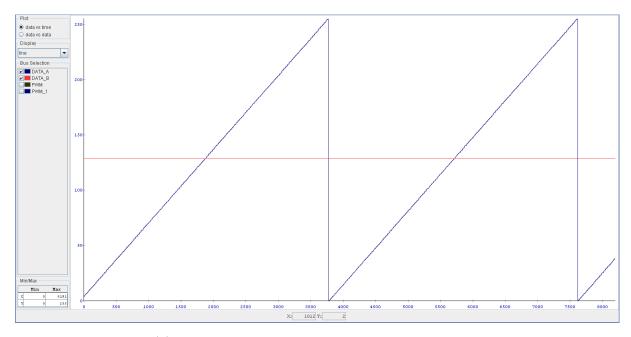

|              | 5.4            | Experi   | imental Results                                                        | 96           |  |  |

| 6            | Cor            | clusio   | n 1                                                                    | 102          |  |  |

| U            | 6.1            |          |                                                                        | 103          |  |  |

|              | 6.2            |          |                                                                        | 103          |  |  |

|              | 0.2            | Coller   | buttons of the Thesis                                                  | 100          |  |  |

|              | Bib            | liograp  | phy 1                                                                  | L05          |  |  |

|              | Puk            | olicatio | ons of the Author                                                      | L16          |  |  |

| $\mathbf{A}$ | The            | Conn     | ections Between (J11, J10, J20) and the FPGA                           | L <b>1</b> 8 |  |  |

|              | A.1            |          |                                                                        | 118          |  |  |

|              | A.2            |          |                                                                        | 121          |  |  |

|              |                |          |                                                                        | 124          |  |  |

| В            | UCF Design 125 |          |                                                                        |              |  |  |

|              | B.1            | The U    | Ser Constraint File (UCF) of Auxiliary Inputs Connected to J11 and J4: | 125          |  |  |

|              | B.2            |          | · /                                                                    | 126          |  |  |

|              | B.3            |          | of UART Port                                                           | 127          |  |  |

| CC           | ONTENTS                                           | viii |

|--------------|---------------------------------------------------|------|

|              | B.4 UCF of GPIO Leds                              | 127  |

|              | B.5 UCF of Board to Board Connector J11           | 127  |

|              | B.6 UCF of Board to Board Connector J10           | 129  |

|              | B.6.1 UCF of Differential Signal Pairs            | 129  |

|              | B.6.2 UCF of Single-Ended Signals                 | 130  |

|              | B.7 UCF of Connector J12                          | 130  |

| $\mathbf{C}$ | PCB Layout of the Design                          | 132  |

| •            | C.1 PCB Layout of the FPGA                        |      |

|              | O.1 1 OB Bayout of the 11 OH                      | 102  |

| D            | Verilog Codes VTL and VTF                         | 137  |

|              | D.1 Verilog Top Level (VTL)                       | 137  |

|              | D.2 VTF Code for Simulation Results               | 139  |

|              | D.3 User Constraint File of the Verilog Top Level | 142  |

|              |                                                   |      |

## List of Figures

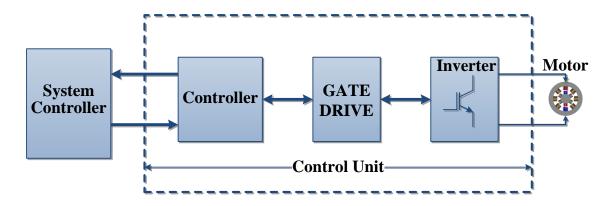

| 2.1  | General motor control system                                                         | 4  |

|------|--------------------------------------------------------------------------------------|----|

| 2.2  | Cross Section of IGBT Structure [44]                                                 | 6  |

| 2.3  | Equivalent circuit of an IGBT structure and its symbol [44]                          | 6  |

| 2.4  | Cross section of FS SA T IGBT structure [116]                                        | 7  |

| 2.5  | Schematic of IGBT module with its symbol [14]                                        | 7  |

| 2.6  | Switching characteristics of an IGBT $(T_1)$ in half-bridge inverter with in-        |    |

|      | ductive load [11]                                                                    | 8  |

| 2.7  | Switching waveforms of freewheeling diode in IGBT module [87]                        | 11 |

| 2.8  | The transient thermal impedance $Z_{thJC}$ as a function of the time $Z_{thJC}$ =    |    |

|      | f(t) [95]                                                                            | 12 |

| 2.9  | R/C Foster thermal model description [80]                                            | 13 |

| 2.10 | IGBT gate drive circuit diagram and waveforms of current and voltage [29].           | 14 |

| 2.11 | Waveform of IGBT gate charge characteristics [29]                                    | 15 |

| 2.12 | Types of snubber circuits used in IGBT applications [89]                             | 18 |

|      | Effect of short circuit inductance on IGBT module behavior [100]                     | 19 |

| 2.14 | Gate voltage effects on the collector current [14]                                   | 20 |

|      | Gate resistors with series diodes.                                                   | 21 |

| 2.16 | IGBT SC Protection circuit based on $di/dt$ feedback control [102]                   | 22 |

| 2.17 | Block diagram of the SC protection circuit based on gate voltage sensing [72].       | 23 |

| 2.18 | Block diagram of the SC protection circuit based on $V_{GE}$ and $Q_G$ sensing [31]. | 24 |

| 2.19 | Characteristic of $Q_G$ vs $V_{GE}$ [31]                                             | 25 |

|      | Block diagram of the basic proposed closed loop active gate driver [56].             | 26 |

| 2.21 | On state voltage drop sensing circuit [46]                                           | 27 |

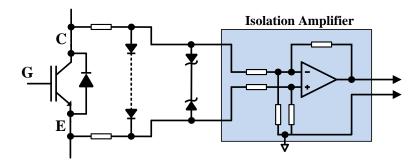

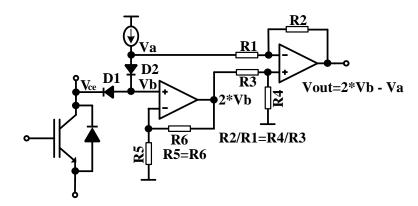

| 2.22 | Online $V_{CE}$ measurement circuit for the IGBT wear out monitoring [7]             | 27 |

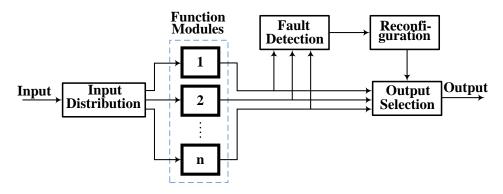

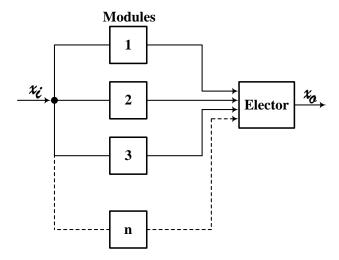

| 2.23 | Scheme of a fault tolerant system with redundant function modules [36].              | 29 |

| 2.24 | The schemes of FTC types [36]                                                        | 29 |

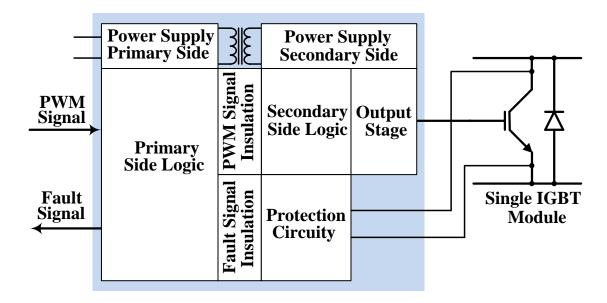

| 2.25 | Standard driver architecture [47]                                                    | 32 |

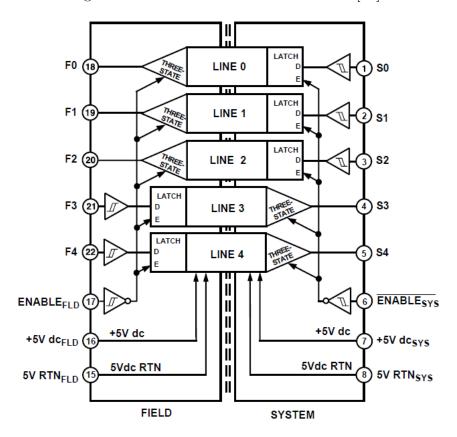

| 2.26 | Functional block diagram of the logic isolator "AD261" [22]                          | 32 |

| 3.1  | The Architecture of Proposed Gate Driver with ADCs Devices for Monitor-              |    |

|      | ing and diagnosis [70]                                                               | 34 |

| 3.2  | Interface Between One IGBT Gate Driver and Main FPGA Controller                      | 36 |

| 3.3  | Proposed SPI data transfer protocol                                                  | 37 |

LIST OF FIGURES x

| 3.4  | IGBT gate driver detail for one channel in IGBT module                         | 39         |

|------|--------------------------------------------------------------------------------|------------|

| 3.5  | Physical configuration of the proposed IGBT gate drivers based FPGA con-       |            |

|      | troller                                                                        | 40         |

| 3.6  | Block diagram of the parallel driver stages used in the proposed gate drive    |            |

|      | circuit                                                                        | 41         |

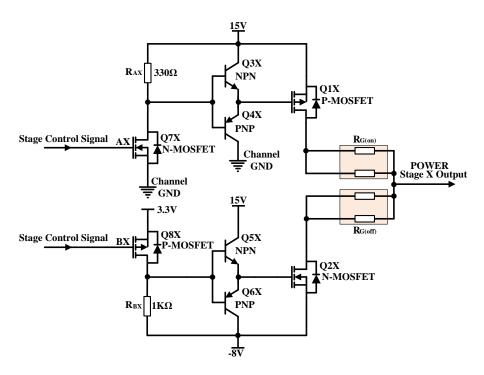

| 3.7  | Schematic diagram of single driver stage in one channel                        | 42         |

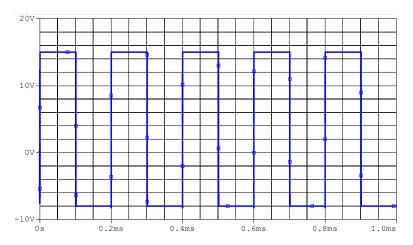

| 3.8  | The output signal of one stage for the proposed IGBT gate driver               | 43         |

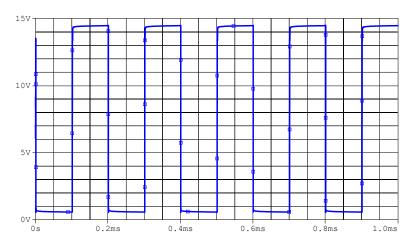

| 3.9  | The gate signal of P-MOSFET Q1X                                                | 43         |

| 3.10 |                                                                                | 43         |

| 3.11 |                                                                                | 44         |

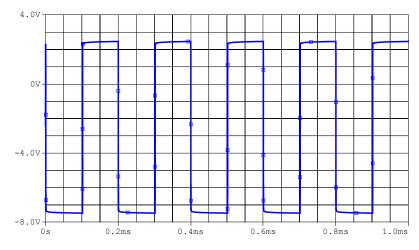

| 3.12 | The base signal of the emitter follower (Q5X, Q6X)                             | 44         |

|      | The digital signals used for controlling the input stages                      | 46         |

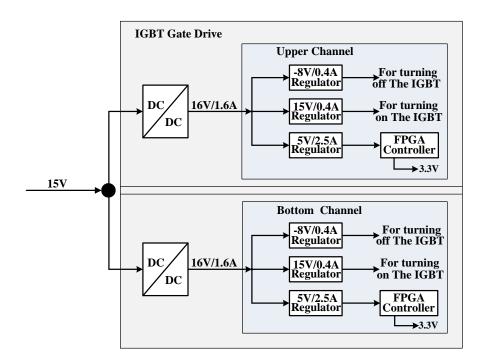

|      | Block diagram of power supply in the proposed gate drive                       | 48         |

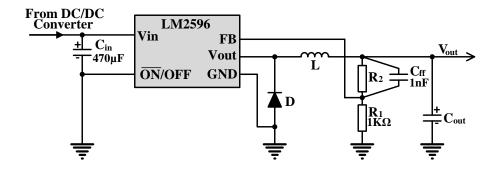

|      | The schematic circuit of the positive regulators                               | 49         |

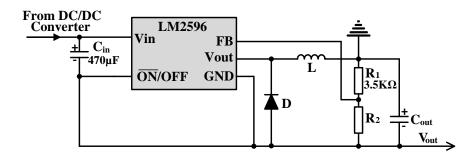

| 3.16 | The schematic circuit of the negative regulators                               | 49         |

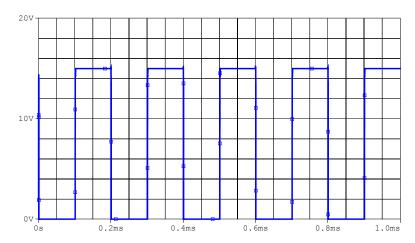

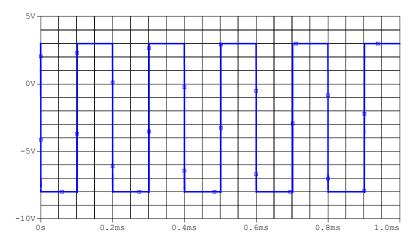

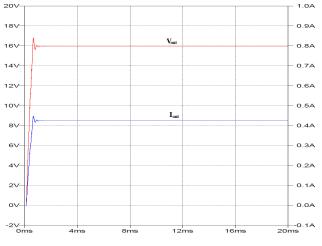

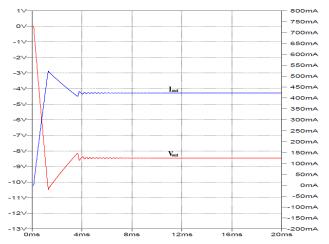

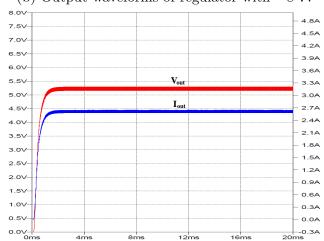

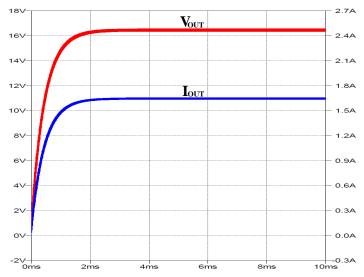

| 3.17 | Output waveforms of the regulators in the power supply system                  | 50         |

| 3.18 | The schematic circuit of the push pull DC/DC converters used in power          |            |

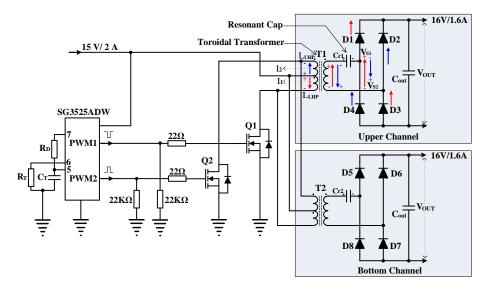

|      | supply system.                                                                 | 52         |

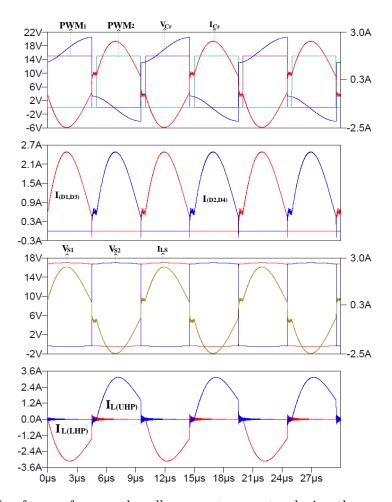

| 3.19 | Waveforms of one push pull resonant converter                                  | 54         |

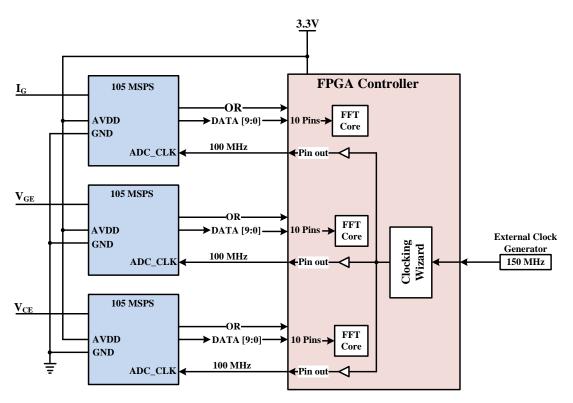

| 3.20 | ADC Devices interface to the FPGA controller                                   | 56         |

| 4 -  |                                                                                | <b>-</b> c |

| 4.1  | Block diagram of proposed FPGA design.                                         | 58         |

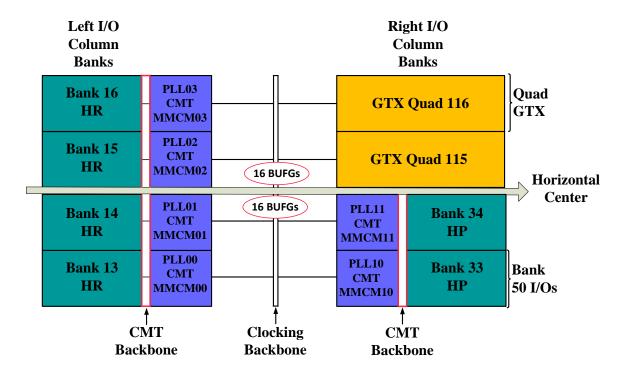

| 4.2  | IO and Transceiver banks for XC7K70T [108]                                     | 59         |

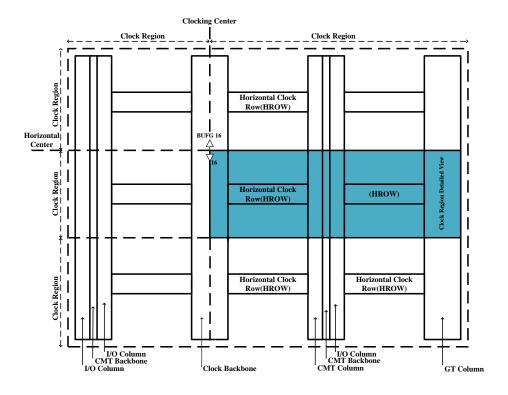

| 4.3  | Architecture of clock resources in a clock region [112]                        | 61         |

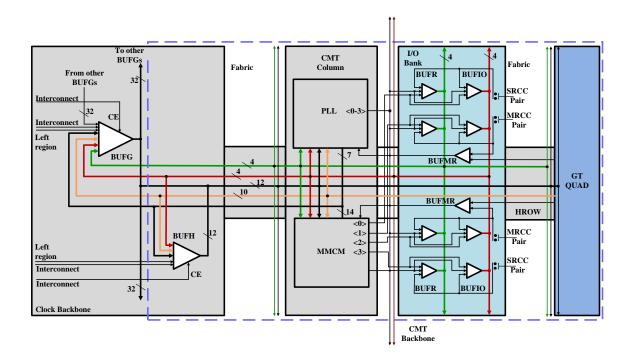

| 4.4  | BUFG/BUFH/CMT/BUFR/BUFMR/BUFIO Clock region detail [112].                      | 62         |

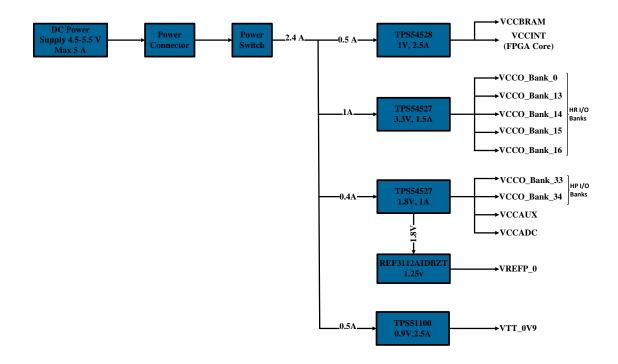

| 4.5  | Power supplies block diagram of Kintex-7 XC7K70t-3fbg484                       | 63         |

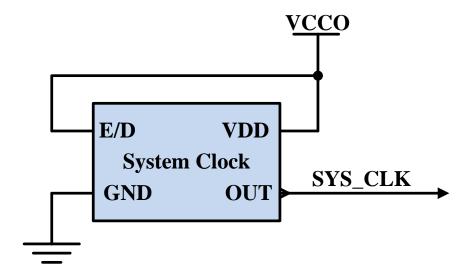

| 4.6  | Schematic circuit of the clock crystal oscillator.                             | 63         |

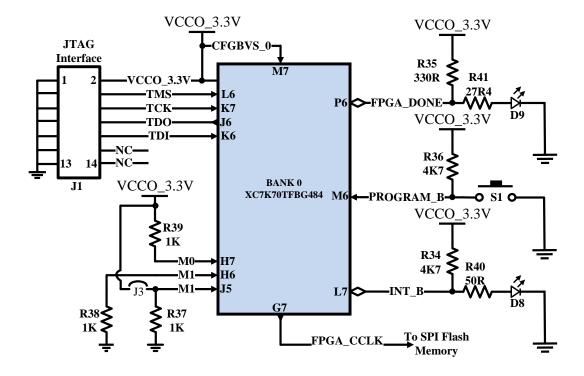

| 4.7  | Configuration mode pins circuit of bank 0 in proposed FPGA board               | 65         |

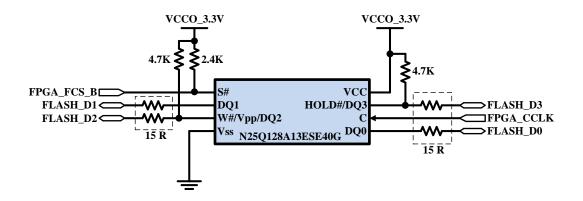

| 4.8  | QSPI flash memory circuit                                                      | 66         |

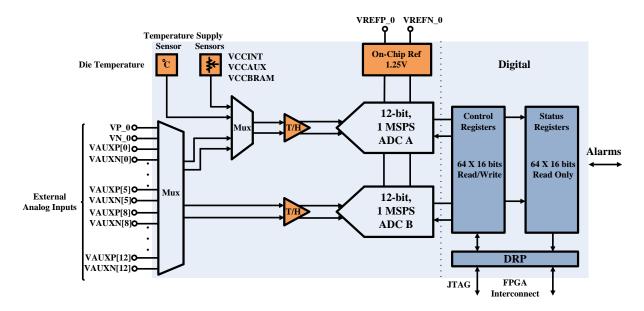

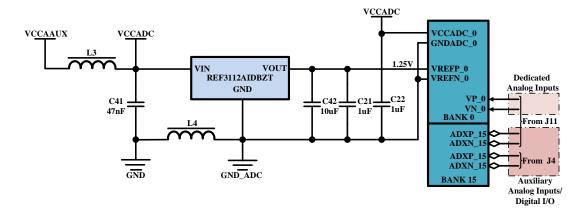

| 4.9  | XADC block diagram in Kintex 7 [111]                                           | 68         |

|      | 0 1                                                                            | 69         |

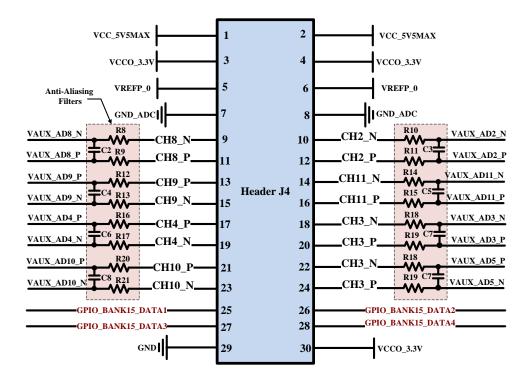

|      | XADC Header (J4)                                                               | 70         |

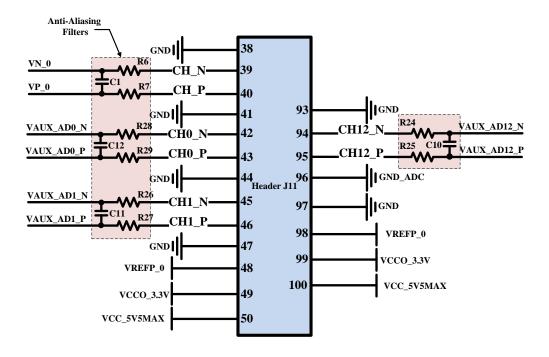

|      | Pins of Header (J11) used to provide analog inputs to FPGA                     | 70         |

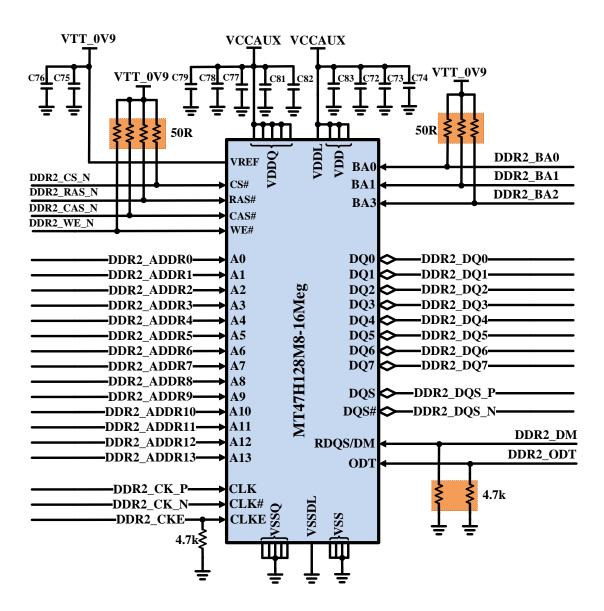

|      | DDR2 SDRAM memory schematic circuit                                            | 73         |

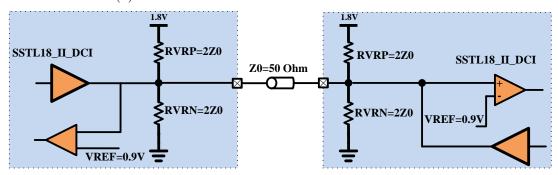

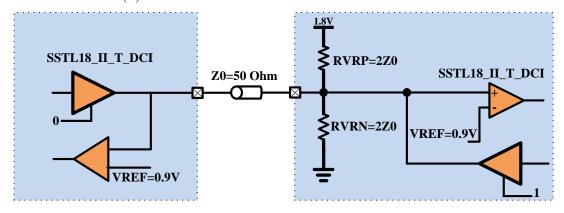

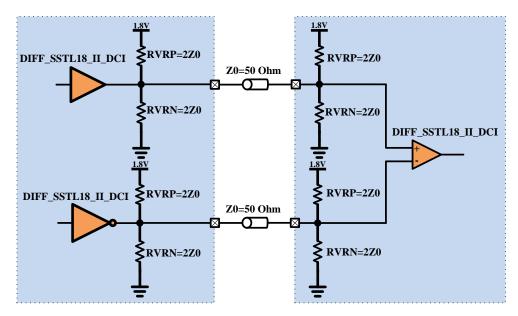

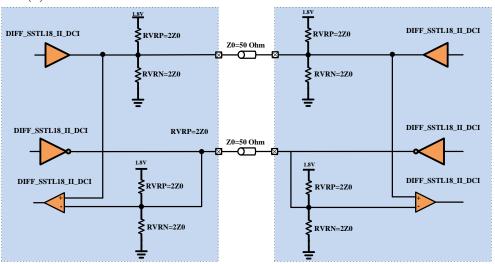

|      | SSTL18 class II sample circuits [110]                                          | 75         |

|      | Differential SSTL18 class II sample circuits [110]                             | 76         |

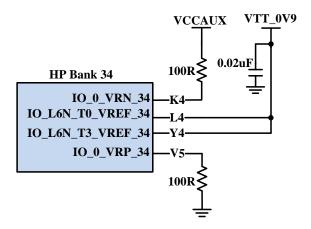

|      | Dedicated DCI VRP/VRN resistor and reference voltage schematic circuit.        | 77         |

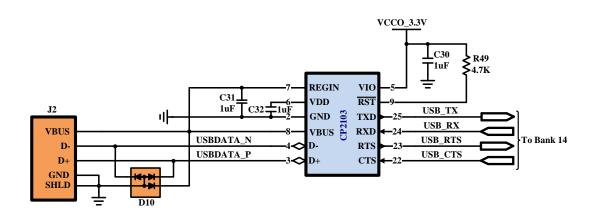

|      | USB TO UART bridge schematic circuit                                           | 78         |

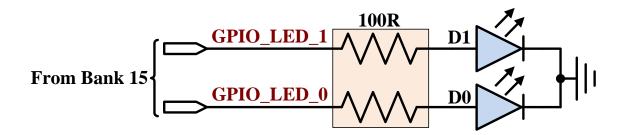

|      | Schematic circuit of the User GPIO LEDs                                        | 79         |

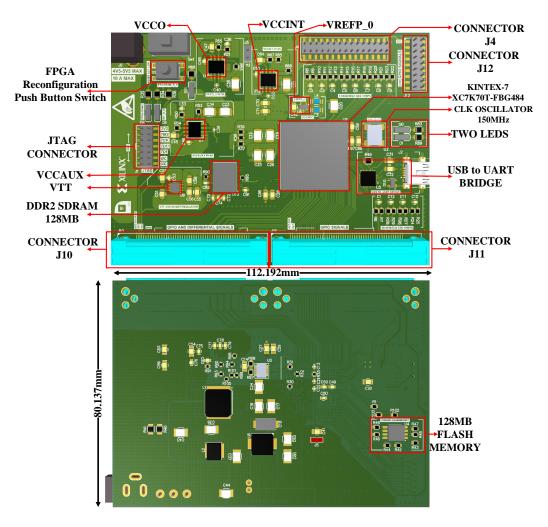

|      | Top and bottom view of the proposed FPGA board                                 | 81         |

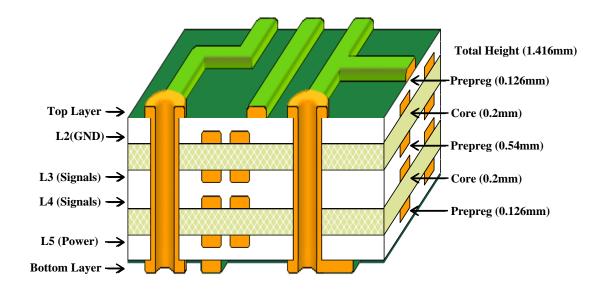

|      | The layer stack-up for 6 layers used in the FPGA board                         | 82         |

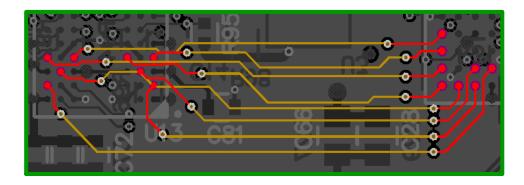

|      | The single-ended traces of DDR2 (DQ) with $50\Omega$ characteristic impedance. | 85         |

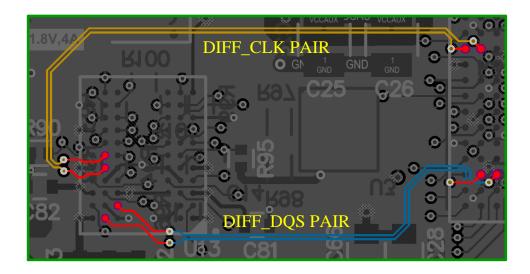

| 4.22 | The differential traces of DDR2 with $100 \Omega$ differential impedance       | 85         |

LIST OF FIGURES xi

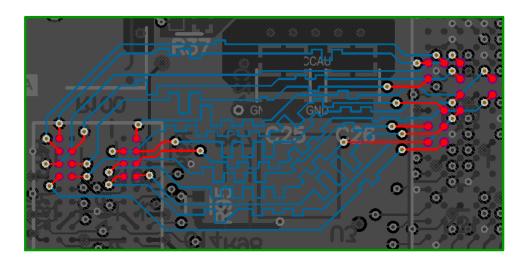

| 4.23 | The addresses traces of DDR2 with $50-60\Omega$ impedance                    | 8  |

|------|------------------------------------------------------------------------------|----|

|      |                                                                              | 86 |

|      |                                                                              | 88 |

|      |                                                                              | 89 |

|      |                                                                              | 89 |

|      | $\Theta$                                                                     | 90 |

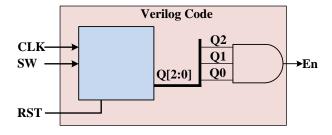

| 5.1  | Schematic block of Verilog top level in the proposed gate driver FPGA        | 91 |

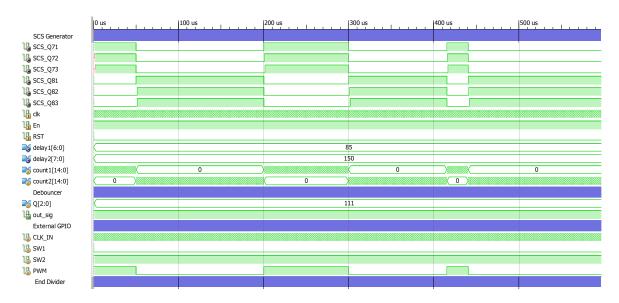

| 5.2  | Schematic block of the clocking wizard                                       | 92 |

| 5.3  | The digital signals of the clocking wizard.                                  | 92 |

| 5.4  |                                                                              | 93 |

| 5.5  | Up counters operation with SCS generator outputs and PWM edges               | 94 |

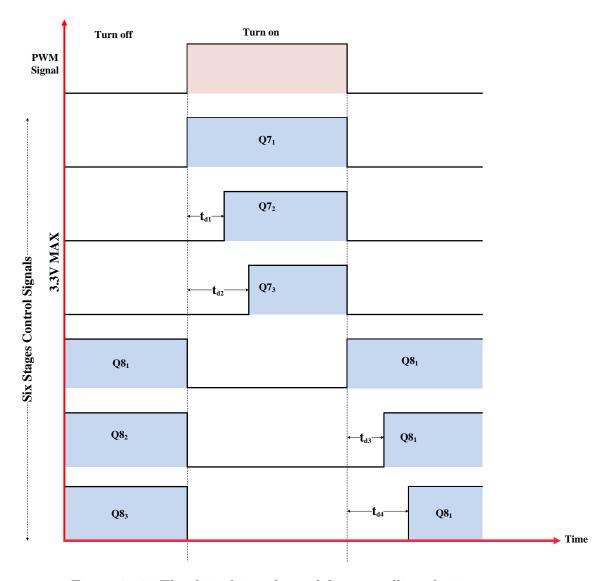

| 5.6  | Digital signals of the stages transistors with the delay times               | 95 |

| 5.7  | Schematic block of the digital de-bouncer circuit.                           | 95 |

| 5.8  | Digital signals of the digital de-bouncer circuit.                           | 96 |

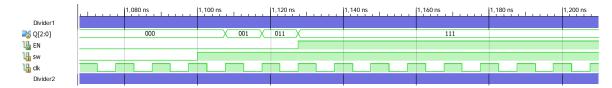

| 5.9  | Digital signals of SCS generator during the operation                        | 96 |

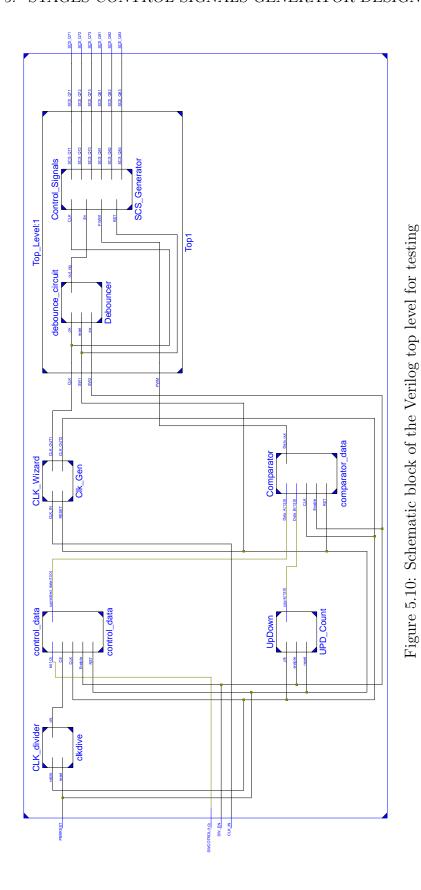

| 5.10 | Schematic block of the Verilog top level for testing                         | 9  |

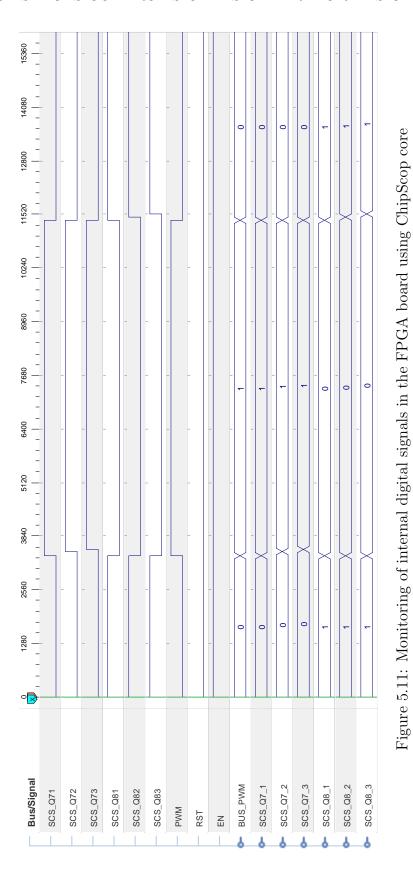

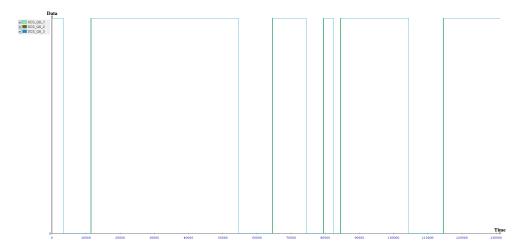

| 5.11 | Monitoring of internal digital signals in the FPGA board using ChipScop core | 96 |

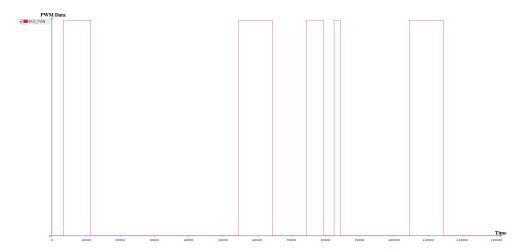

| 5.12 | Waveform of the generated PWM based on FPGA controller                       | 00 |

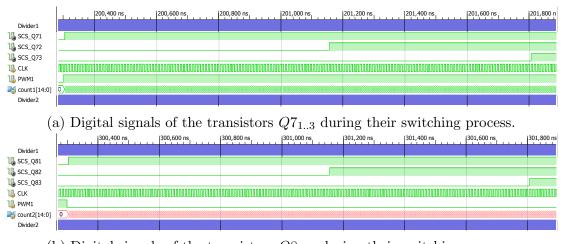

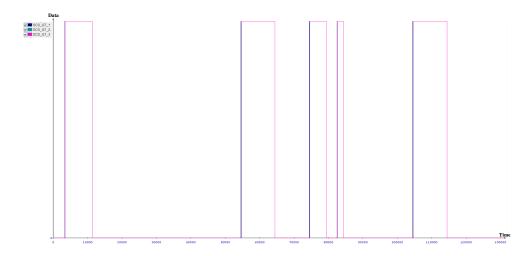

| 5.13 | Waveforms of the transistors $Q7_{13}$ during their switching operation 1    | 00 |

| 5.14 | Waveforms of the transistors $Q8_{13}$ during their switching operation 1    | 00 |

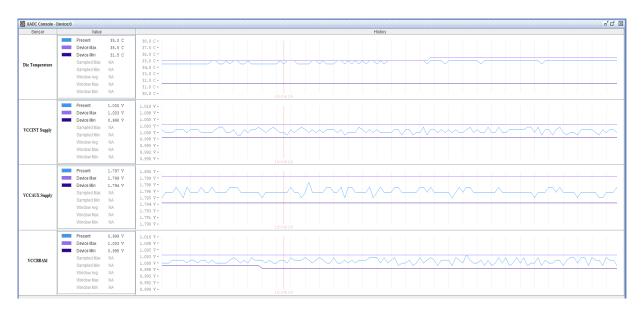

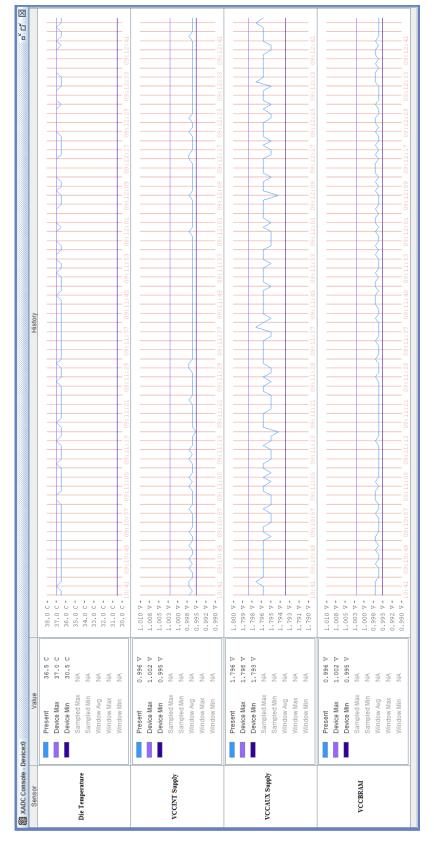

| 5.15 | Monitoring of powers supplies and Die temperature in the FPGA board          |    |

|      | during the SCS generator operation using ChipScop core                       | 0. |

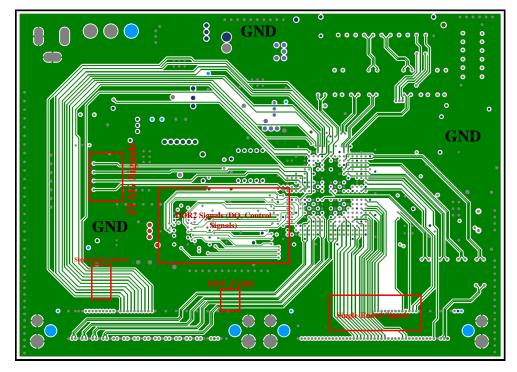

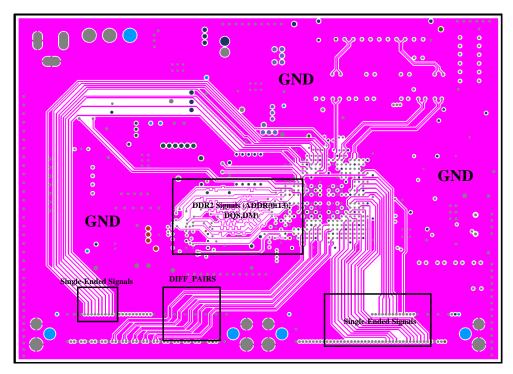

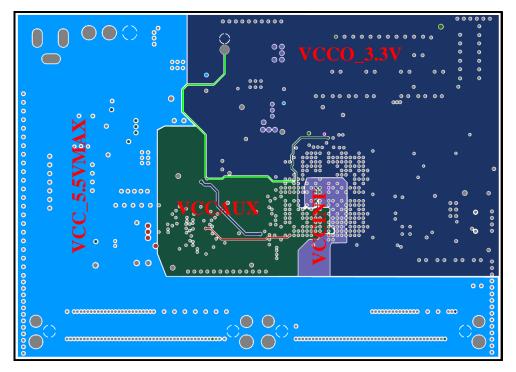

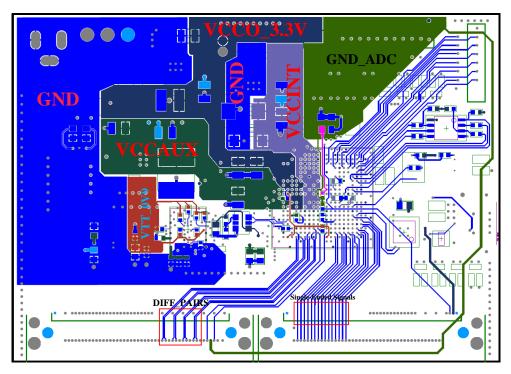

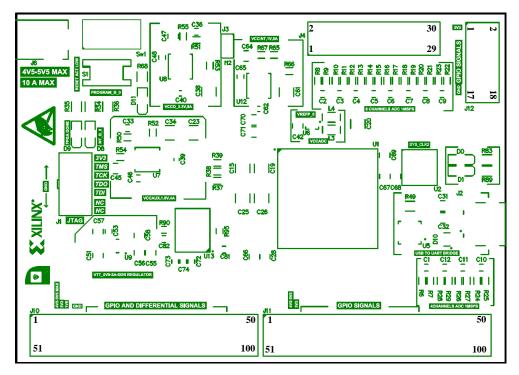

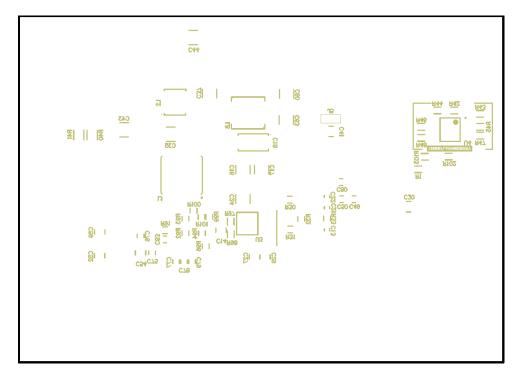

| C.1  | * *                                                                          | 32 |

| C.2  | PCB layout of the FPGA design                                                | 33 |

### List of Tables

| 3.1  | The complementary transistors used in the proposed gate drive stages   | 45  |

|------|------------------------------------------------------------------------|-----|

| 3.2  | The values of components required for positive and negative outputs of |     |

|      | power supply system                                                    | 51  |

| 4.1  | Features of 7 series FPGA device (Kintex-7 XC7K70t-3fbg484)            | 60  |

| 4.2  | Power supply voltage ratings for proposed FPGA board                   | 62  |

| 4.3  | Clock sources table                                                    | 64  |

| 4.4  | Configuration mode Pins used in proposed FPGA board                    | 65  |

| 4.5  | Quad SPI flash memory connections to FPGA pins                         | 66  |

| 4.6  | Configuration parameters for $f_{MCCLK}$ calculation                   | 67  |

| 4.7  | Auxiliary inputs connected to Headers (J11) and (J4)                   | 72  |

| 4.8  | The connections between the DDR2 SDRAM memory and the FPGA             | 74  |

| 4.9  | The required frequencies for The DDR2 SDRAM interface                  | 78  |

| 4.10 | The connection of UART to FPGA pins (HR Bank 14)                       | 79  |

| 4.11 | GPIO LEDs connection to the FPGA pins (HR Bank 15)                     | 79  |

|      | Layer stack-up detail for the FPGA board (PCB)                         | 82  |

| A.1  | The Connection Between board to board connector (J10) and the FPGA .   | 121 |

|      |                                                                        | 123 |

| A.3  | Connection between J12 and the FPGA                                    | 124 |

### Abbreviations

#### Mathematical Terminology

$E_{on}$  Loss of Energy

$f_{CCLK}$  Configuration Clock Frequency

$f_{CLK}$  Clock Frequency

$F_{RSELF}$  Self Resonant Frequency  $F_{RIS}$  Effective Resonant Frequency

$f_{sw}$  Switching Frequency

$G_{FE}$  Forward Transconductance

$I_C$  Collector Current  $I_L$  Load Current

$L_G$  Stray Inductance in the Gate Path

$L_{via}$  Via Inductance  $L_{trace}$  Trace Inductance

$L_{mount}$  Mounting Parasitic Inductance

$L_{self}$  Self Inductance

$L_{IS}$  Effective Parasitic Inductance

$L_C$  Main Collector Terminal Connection Parasitic Inductance  $L_{SC}$  Sensor Collector Terminal Connection Parasitic Inductance  $L_E$  Main Emitter Terminal Connection Parasitic Inductance  $L_E$  Kelvin Emitter Terminal Connection Parasitic Inductance

$L_q$  Gate Terminal Connection Parasitic Inductance

$egin{array}{ll} N_{cc} & {

m Clock~Cycles~Number} \\ R_g & {

m Internal~Gate~Resistor} \\ R_{on} & {

m On~State~Resistance} \\ \end{array}$

$R_{thJC}$  Thermal Resistance of Junction to Case

$T_{CH}$  Case-Heat-Sink Temperature

$t_{fv}$  Voltage Fall Time

TMCCKTOL Configuration Clock Tolerance

$T_{SPITCO}$  SPI clock to out

$T_{SPIDDC}$  FPGA data setup time  $T_{stg}$  Storage Temperature  $T_{vi,op}$  Junction Temperature

LIST OF TABLES xiv

$t_{sc,MAX}$  Maximum Short Circuit Time

$t_{d(on)}$  Turn on Delay Time  $t_{on}$  Turn on Time

$t_p$  Time Period  $t_{ri}$  Current Rise Time  $U_{DC}$  DC-Bus Voltage  $V_G$  Gate Drive Voltage

$egin{array}{lll} V_{CE} & ext{Collector-Emitter Voltage} \ V_{GE} & ext{Gate-Emitter Voltage} \ V_{th} & ext{Threshold Voltage} \ V_{CE(sat)} & ext{On-State Voltage Drop} \ \end{array}$

$Z_{thJC}$  Transient Thermal Impedance

#### **Miscellaneous Abbreviations**

AAF Anti-Aliasing Filter

AC Alternative Current

ADC Analog Digital Converter

AFTC Active Fault-Tolerant Control

**AGD** Active Gate Drive

**ASIC** Application Specific Integrated Circuit

**BGA** Ball Grid Array

BJT Bipolar Junction Transistor

BLVDS Bus Low Differential Signaling

BUFG Global Clock Buffer

BUFH Horizontal Clock Buffer

BUFIO Input/Output Buffer

BUFMR Multi-region Clock Buffers

BUFR Regional clock Buffers

C Collector Terminal

$C_S$  Collector Sensor Terminal CCLs CMOS configuration latches CFGBVS Configuration Bank Voltage Select

CLB Configurable Logic Blocks

CPLDs Complex Programmable Logic Devices

CMT Clock Management Tile

DAC Digital Analog Converter

DC Direct Current

DCI Digitally Controlled Impedance

DDR2 SDRAM double data rate synchronous dynamic random-access memory

LIST OF TABLES xv

**DFT** Discrete Fourier Transform

**DIN** Data In

**DIP** Dual In-line Package

**DOUT** Data Out

DRP Dynamic Reconfiguration PortDSP Digital Signal Processing

E Emitter Terminal

e Kelvin Emitter Terminal

**EEPROM** Electrically Erasable Programmable Read-Only Memory

**EMCCLK** External Master Configuration Clock

**EMI** Electro-Magnetic Interference

**EPROM** Erasable Programmable Read Only Memory

ESL Equivalent Series Inductance

ESR Equivalent Series Resistance

FDD Fault Detection and Diagnosis

FDI Fault Detection and Isolation

FFT Fast Fourier Transform

FPGA Field-Programmable Gate Array

FPLA Field-Programmable Logic Array

FTC Fault-Tolerant Control FUL Fault Under Load G Gate Terminal

GPIO General Purpose Input/Output HDL Hardware Description Language

**HP** High-Performance

**HR** High-Range

**HROW** Horizontal Clock Row

**HSTL** High-Speed Transceiver Logic

**HSF** Hard Switch Fault

**IDELAY** Programmable Input Delay

IGBT Insulated Gate Bipolar Transistor

I/O Input/Output INIT\_B Initialization Bar

JTAG Joint Test Action Group LSB Least Significant Bit LUT Look Up Table

LVCMOS Low Voltage Complementary Metal Oxide Semiconductor

LVTTL Low Voltage Transistor Transistor Logic

LVDS Low Voltage Differential Signaling

MC Memory Controller MF Multi-Functional

MIG Memory Interface Generator

MMCM Mixed-Mode Clock Manager

LIST OF TABLES xvi

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOSI Master-Output, Slave-Input

MPGAs Mask-Programmable Gate Arrays

MRCC Multi-Region Clock Capable

MSPS Mega Sample Per Second

NA Not Available

NC No Connected

**NPT** Non-Punch-Through

NU Not Used

ODELAY Programmable Output Delay

ODT On-Die Termination

OTP One-Time Programmable

PCB Printed Circuit Board

PCI Peripheral Component Interconnect

PDS Power Distribution System

PFTC Passive Fault-Tolerant Control

PHY Physical Layer

PI Proportional Integral Controller

PLL Phase-Locked Loop

**PPDS** Point-to-Point Differential Signaling)

PROGRAM\_B Program Bar

PROM Programmable Read Only Memory

PT Punch-Through

PTH Plated Through Hole

PUDC\_B Pull-Up During Configuration Bar

RCCM RC Component Model

**RSDS** Reduced Swing Differential Signaling

**RVM** Relevance Vector Machine

SAFST Shorted Anode Field Stop Trench

SC Short Circuit

SCRSilicon Controlled RectifierSCSStages Control SignalsSPISerial Peripheral InterfaceSRAMStatic Random-Access MemorySRCCSingle-Region Clock-CapableSSNSimultaneous Switching NoiseSSTLStub-Series Terminated Logic

TCK Test Clock

TDI Test Data Input

TDO Test Data Output

TIM Thermal Interface Material

TMS Test Mode Select

UART Universal Asynchronous Receiver/Transmitter

LIST OF TABLES xvii

UCF User Constraints File

USB Universal Serial Bus

VCP Virtual COM Port

VFD Variable Frequency Drive

VHDL Very High Speed Integrated Circuit Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLD Variation of lateral doping

VR Voltage Regulator

VSI Voltage Source Inverter

VTF Verilog Test Fixture

XADC Xilinx Analog to Digital Converter

XDTs Xilinx Design Tools

### Chapter 1

### Introduction

Today's, industrial automation systems are highly complex networks of embedded systems consisting of many sensors, drives, controllers, and intelligent I/O devices. Recently, Field Programmable Gate Arrays (FPGAs) are used throughout industrial automation systems to add intelligence, flexibility, and high precision control. Their applications include motion control, machine to machine communications, motor drives, diagnosis and fault-tolerant control, smart energy and smart grid, big data analytic, etc.

Generally, when the FPGAs are used in motor drives, they implement complex control algorithms and modulation switching. Additionally, they can provide functions for fault protection of motor such open circuit and short circuit. In other words, the FPGAs usage is limited to motor control and modulation switching, but they are not used to detect the problems of inverter components during the switching process. For example, the monitoring of the IGBT switching process (turn-on, turn-off) in a power inverter may lead to predict and diagnose the faults before the complete degradation occurrence in the drive system.

Mostly, no methods exist for continuous monitoring of inverter switching transistor condition or other parts of power inverter such as DC link capacitance, leakage resistance, or terminals contact resistances etc. Diagnostic methods based on continuous condition monitoring, which were developed for mechanical vibration monitoring or for many other fields - for example ball bearing condition monitoring or partial discharges in motor winding, do not exist for IGBT transistors proper operation. The quality of switching process is possible to observe only on transients, when the transistor switches on or off. Based on the study presented in chapter 2, it could be noted that several factors affect the switching transient in the transistor: transistor switching speed, gate resistance, gate current, gate voltage, DC link capacitance, snubbers capacitance, etc. Among these quantities, which can be measured, are collector-emitter voltage  $V_{CE}$ , gate-emitter voltage  $V_{GE}$  and gate current  $I_G$ . These quantities are only measurable in the IGBT gate driver in the inverter. Based on the quantities measurements and their quantitative evaluation, the degree of degradation in the power components (IGBT transistors, diodes, capacitors, etc.) may be predicted, where the characteristic of these components change during the degradation. Therefore, the diagnostic methods, which depend on measuring and monitoring the IGBT quantities during the switching process in the gate drive circuits, should lead to predict the critical degree of the components degradation. Accordingly, the maintenance can be scheduled to avoid the failure of the components during the operation.

As long as the IGBT gate driver is used to measure and monitor the required quantities for the diagnosis, a new hardware for the gate driver is required. In addition to its basic functions (turn-on, turn-off), the gate driver should be able to perform measurements, recording, and mathematical analysis during the IGBT switching process. The digital signal processing for the analysis and recording is required. Generally, Fast Fourier Transform (FFT) or Wavelet transform are used for this purpose. Therefore, the implementation of programmable devices, which are placed directly on the gate driver, are required. The programmable devices may be Field Programmable Gate Arrays (FPGAs) or microprocessors.

### 1.1 Motivation and Objectives

The idea is to integrate the diagnostic functions into the IGBT gate driver circuits. These functions should allow analysis of the required quantities in the IGBT transistor and its gate driver. The purpose is to measure and monitor these signals during the IGBT switching process. The quantitative evaluation of the measured parameters, which are recorded and analyzed using programmable devices, can indicate the degree of the degradation. As a result, the IGBT failure can be predicted and it would be able to plan the targeted service (replacement of specific IGBT, driver, capacitor).

The aim is to design a hardware of the IGBT gate driver, which would allow achieving the previous properties.

The structure of the proposed IGBT gate driver can be summarized as follows:

- 1. Multiple gate stages outputs for realization of variable gate resistance by sequential switching. It allows realization of liner charging of gate capacitance delayed sequential switching signals are generated in the FPGA and are programmed in HDL language.

- 2. Programmable devices (FPGAs) for recording and analysis of the digital signals.

- 3. Multiple power supplies for IGBT gate stages and for FPGA feeding.

- 4. Driver interface to inverter control system with data exchange capability except standard PWM signal. The insulated SPI interface is used for this purpose.

#### 1.2 Structure of the Thesis

The thesis is structured as follows:

1. Introduction: This chapter includes the usage of Field Programmable Gate Arrays (FPGAs) in the applications of industrial automation. It also describes the capability of their usage in the control and diagnosis of inverter faults during the switching

- process. Additionally, this chapter describes the motivation and the objective of the thesis.

- 2. Background and State of the Art: This chapter is dedicated to IGBT transistor description and its applications. This chapter also reviews the current state of the art of the IGBT transistor faults, fault detection and diagnosis and the fault-tolerant control.

- 3. Proposed IGBT Gate Drive Architecture: This chapter is concerned with the IGBT Gate driver design. A new IGBT gate driver architecture with integrated diagnostic functions is provided.

- 4. FPGA Board Design for IGBT Control and Diagnosis: This chapter focuses on the FPGA board design and the required components for implementation the diagnostic functions and the IGBT switching process control.

- 5. Stages Control Signals Generator Design: This chapter deals with the design steps of stages control signals generator which provides the signals that control the IGBT gate driver stages during the IGBT turn-on/turn-off.

- 6. Conclusions: This chapter summarizes the the results of the dissertation. This chapter also discuses the future work which can be the continuous of FPGA usage in the applications of the diagnosis and the fault-tolerant control.

- 7. Appendix A: Includes the connections between the conectors pins (J11, J10,J20) and The FPGA device.

- 8. Appendix B: Provides the User Constraint File (UCF) of the FPGA device for interfacing to the external devices.

- 9. Appendix C: Is the PCB layout of the FPGA board design.

- 10. Appendix C: The Verilog Top Level (VTL) and Verilog Test Fixture (VTF) designed for the simulation and experimental results.

### Chapter 2

### Background and State of the Art

The drive system can be divided into:

- Power semiconductor devices.

- Gate drive circuit.

- Control circuits.

- Sensors.

- Communication interfaces.

- Software.

A general motor control system can be illustrated as follows:

Figure 2.1: General motor control system

As can be seen from Figure 2.1, the control unit, which is composed of inverter, gate

driver, and controller, is the key of control system and if this part and all its functions are understood, all the faults and their causes can be diagnosed.

When the drive system works for a long time, it could go out of the service due to the fault occurrence. Therefore, the faults must be predicted. The fault may occur in the control unit (power semiconductor, gate driver, controller) or inside the electrical machine. Sometimes, the fault occurs in the area between the control unit and the electrical machine. Therefore, the system must be protected to prevent its failure and damage during the operation.

The scope of this chapter is focused on the detection of optimization operating state of the drive system. It presents diagnosis methods which are designed to predict drive system faults, where the robust and reliability are usually increased using the fault detection and fault tolerant solutions.

### 2.1 IGBT Basics

Nowadays, the full controlled power semiconductors (IGBTs and MOSFETs) are widely used in most power inverters of drive systems. The advantage of MOSFET is that it requires a little current to turn on, but its disadvantage is that it requires a high voltage to turn on. IGBT is developed to combine a high efficiency and a fast switching. IGBT is a cross between the bipolar junction transistor (BJT) and the MOSFET transistor, and it has the characteristics of the BJT (collector-emitter) and the drive characteristics of the MOSFET. Hence, the focus would be placed on IGBT power switches.

### 2.1.1 Basic Structure and Operation

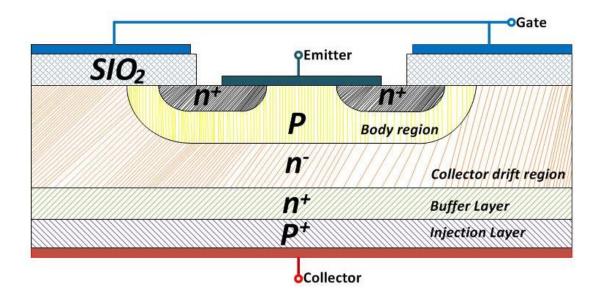

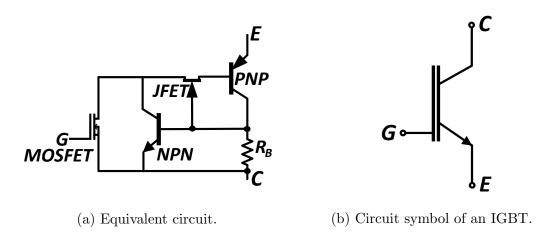

There are several structures for the IGBT transistors. Figure 2.2 illustrates one of these structures. The  $N^+$  layer at the top is the emitter, the  $P^+$  layer at the bottom forms the collector [44], with  $n^+$  buffer layer the IGBT is called a Punch-Through (PT) IGBT, the buffer layer improves the performance of the device (low on-state voltage drop, fast in switching). The IGBT without buffer layer is called a Non-Punch-Through (NPT) IGBT. The NPT IGBT improved the switching speed but it is unsuitable for the high power application due to its high  $V_{ce(sat)}$ . The equivalent circuit can be to simplify the structure, see drawn Figure 2.3a.

The equivalent circuit contains MOSFET, NPN, JFET and PNP transistors. Figure 2.3b shows the IGBT circuit symbol, which has three terminals called collector (C), emitter (E), and gate (G).

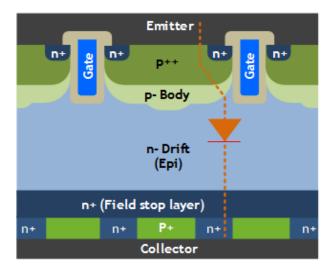

Improved characteristics of IGBTs have resulted in a higher switching speed and lower switching power losses. New generations of IGBTs have adopted the trench technology to reduce the losses of IGBTs [65]. The gate structure of IGBTs, which is dependent on the trench technologies differs from the conventional structure illustrated in Figure 2.2, where the gate electrode is built in deep narrow trench. The structure of trench IGBT is shown in Figure 2.4, where the trench gate structure reduces the on state voltage drop  $V_{CE(sat)}$

Figure 2.2: Cross Section of IGBT Structure [44].

Figure 2.3: Equivalent circuit of an IGBT structure and its symbol [44].

and the field stop layer reduces the turn off losses [116].

The trench concept with variation of lateral doping (VLD) technology have been introduced for  $4.5\,\mathrm{kV}/1.2\,\mathrm{kA}$  and  $6.5\,\mathrm{kV}/750\,\mathrm{A}$  IGBT modules [25] [6], this new generation of IGBTs (IGBT3) reduced the complexity of inverter designs that use previous IGBT modules (IGBT2) or GTOs. As a result, lower system costs and better reliability.

IGBT is robust but it suffers failures because of the electrical and thermal stress. However, thanks to its advantages, IGBT became the main component in the power electronic applications (transport, energy conversion, manufacturing, mining and petrochemical) and it can be used for application up to  $6.5\,\mathrm{kV}$  and  $1.2\,\mathrm{kA}$ .

The power IGBT module is build up from parallel IGBT chips,  $T_1$  through  $T_n$  and par-

Figure 2.4: Cross section of FS SA T IGBT structure [116].

- (a) Equivalent circuit of IGBT module.

- (b) Symbol of IGBT module.

Figure 2.5: Schematic of IGBT module with its symbol [14].

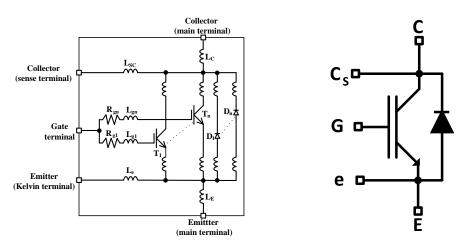

allel diode chips,  $D_1$  through  $D_n$ , as shown in Figure 2.5a, where  $(L_C, L_{SC}, L_{g1..gn}, L_E)$  are the parasitic inductances applied to the wire connections [14].  $R_{g1}$  and  $R_{gn}$  are the internal gate resisters. Due to these resistors, the oscillations between the parasitic capacitance of IGBT chips and the parasitic inductance of the internal gate wires are prevented. Figure 2.5b depicts the symbol of the IGBT module where it has five terminals. The external terminal e is called Kelvin emitter. Kelvin emitter is used for the IGBT gate driver. This feature improves the noise immunity during the IGBT switching operation. The collector sensor terminal  $C_{SC}$  is used for measurement.

#### 2.1.2 Switching Characteristics of IGBT

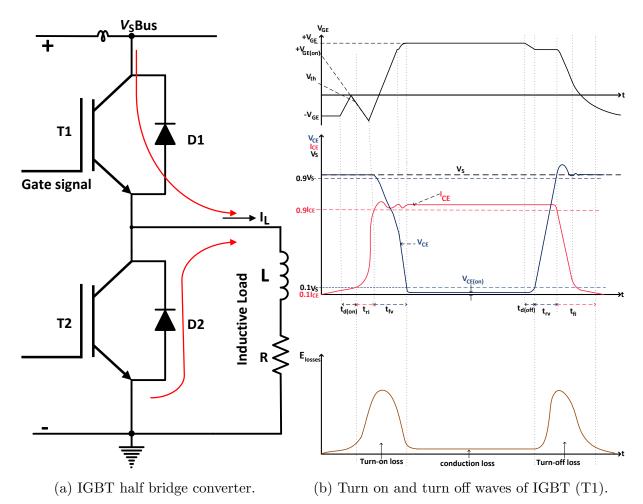

IGBT transistor is a controlled device. Therefore, a voltage between the gate and emitter  $V_{GE}$  is applied to turn it on or off, this voltage is fed from a circuit called gate drive circuit. This circuit acts as an interface between logic signals of controller (FPGA) and the gate signals of IGBT. Figure 2.6a shows an IGBT half bridge inverter with an inductive load,

Figure 2.6: Switching characteristics of an IGBT  $(T_1)$  in half-bridge inverter with inductive load [11].

and Figure 2.6b illustrates the switching characteristics (turn-on and turn-off) wave-forms of one transistor  $T_1$  with an inductive load without using snubbers. Suppose that the  $\frac{L}{R}$  time constant of the load is greater than used IGBT switching frequency. Therefore, the load current  $I_L$  can be considered constant.

When a positive gate voltage is applied to the gate IGBT, the input capacitance between the gate and emitter  $C_{GE}$  charges during the turn-on delay time  $t_{d(on)}$  to a voltage  $V_{GE}$ greater than the threshold voltage  $V_{th}$ , then the IGBT begins to turn on. The current and voltage waves as a function of time are shown in Figure 2.6. When  $V_{GE} > V_{th}$  the load current is transferred from the diode into the device and it increases to the steady on-state value during the rise time  $t_{ri}$ , where the current rise time  $t_{ri}$  is the time interval for the current to increase from  $0.1 I_L$  to  $0.9 I_L$ .

As soon as the gate voltage  $V_{GE}$  reaches the value  $V_{GE(on)}$ , the collector-emitter voltage begins to fall until reaches the value  $V_{CE(sat)}$  during the time  $t_{fv}$ , where the voltage fall time  $t_{fv}$  is the time needed for the voltage  $V_{CE}$  to decrease from  $0.9 V_s$  to  $0.1 V_s$ .

#### 2.1.3 IGBT Switching Losses

The loss of energy  $E_{on}$  during the turn-on of the IGBT can be written as the following:

$$E_{on} = \int_{0}^{t_{on}} V_{CE} \cdot i_{CE} \cdot dt \tag{2.1}$$

where  $t_{on}$  is the IGBT turn-on time. If the delay time is ignored, then the turn-on time equals  $t_{ri} + t_{fv}$ , and the loss of energy during the turn-on can be stated in the following equation form

$$E_{on} = \frac{V_s \cdot I_{CE}}{2} \cdot (t_{ri} + t_{fv}) = \frac{V_s \cdot I_{CE}}{2} \cdot t_{on}.$$

(2.2)

The average power dissipation  $P_{loss(on)}$  is given by

$$P_{loss(on)} = E_{on} \cdot f_{sw} = \frac{V_s \cdot I_{CE}}{2} \cdot t_{on} \cdot f_{sw}$$

(2.3)

where  $f_{sw}$  is the switching frequency of the IGBT.

As shown in Figure 2.6b, the IGBT turn-off begins by removing the gate-emitter voltage, where the gate-emitter capacitance  $C_{GE}$  begins to discharge, the time interval needed for the capacitance to discharge to the value  $V_{GE(on)}$  is called a turn-off delay time  $t_{d(off)}$ . When the  $V_{GE}$  reaches the value  $V_{GE(on)}$ , then the collector-emitter voltage  $V_{CE}$  begins to rise, whereas the collector-emitter current  $I_{CE}$  remains constant. The voltage  $V_{CE}$  increases during the time  $t_{rv}$  until the value equals  $V_s$ , and the collector-emitter current  $I_{CE}$  begins to decrease during the time  $t_{fi}$ . The voltage  $V_{GE}$  continues to decrease until it reaches the value less than the  $V_{th}$ , at this value of the  $V_{GE}$  the MOS channel in IGBT is turned off but the collector current is slowly decreasing because of the high minority carrier concentration stored in the  $n^-$  drift region. Since the voltage  $V_{CE}$  has reached the bus voltage  $V_S$ , with this current tail the loss of energy will be high and the power loss will increase with the frequency increasing.

The loss of energy  $E_{off}$  during the IGBT turn-off time can be written as follows

$$E_{off} = \int_{0}^{t_{off}} V_{CE} \cdot I_{CE} \cdot dt \tag{2.4}$$

suppose  $t_{off} \cong t_{rv} + t_{fi}$ , then Equation 2.4 can be written as the following

$$E_{off} = \frac{V_s \cdot I_{CE}}{2} \cdot (t_{rv} + t_{fi}) = \frac{V_s \cdot I_{CE}}{2} \cdot t_{off}. \tag{2.5}$$

The average power dissipation  $P_{loss(off)}$  is given by

$$P_{loss(off)} = E_{off} \cdot f_{sw} = \frac{V_s \cdot I_{CE}}{2} \cdot t_{off} \cdot f_{sw}. \tag{2.6}$$

The total losses of energy  $E_{SWlosses}$  during the IGBT turn on and turn off is the sum of Equation 2.2 and Equation 2.5

$$E_{SWlosses} = E_{on} + E_{off} (2.7)$$

$$= \frac{V_s \cdot I_{CE}}{2} \cdot (t_{on} + t_{off}). \tag{2.8}$$

The total power dissipation  $P_{SWlosses}$  during the switching is the sum of Equation 2.3 and Equation 2.6:

$$P_{SWlosses} = P_{loss(on)} + P_{loss(off)}$$

(2.9)

$$= \frac{V_s \cdot I_{CE} \cdot f_{sw}}{2} \cdot (t_{on} + t_{off}). \tag{2.10}$$

#### 2.1.4 IGBT Conduction Losses

Figure 2.6b illustrates the conduction losses during the on-state of IGBT, where these losses occur between the end of the turn-on time and the beginning of the turn-off time of the IGBT. The conduction energy losses  $E_{loss(con)}$  can be deduced using Equation 2.11

$$E_{loss(con)} = \int_{t_{con}} V_{CE(sat)} \cdot I_C \cdot dt$$

(2.11)

where  $t_{con}$  is the interval between the end of the turn-on time and the beginning of the turn-off time,  $V_{CE(sat)}$  is the voltage drop across the IGBT during the conduction, and  $I_C$  is the collector current that is equal the load current  $I_L$ . The losses during the off-state is negligible.

The total energy loss for IGBT  $E_{IGBT}$  is the sum of energy losses  $E_{on}$ ,  $E_{off}$  and  $E_{loss(con)}$

$$E_{IGBT} = E_{on} + E_{off} + E_{loss(con)}. (2.12)$$

And the total power loss  $P_{IGBT}$  is the product of total energy loss  $E_{IGBT}$  and the switching frequency  $f_{sw}$

$$P_{IGBT} = \{E_{on} + E_{off} + E_{loss(con)}\} \cdot f_{sw} = E_{IGBT} \cdot f_{sw}. \tag{2.13}$$

#### 2.1.5 Free Wheeling Diode (FWD)

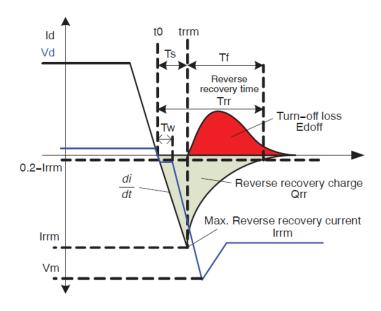

IGBT modules are sometimes composed of multiple IGBTs and freewheeling diodes which connect in anti-parallel with the IGBT, as shown in Figure 2.6a. The function of this diode is to handle the current of the inductive loads such as inductive motors or transformers. Therefore, the reverse recovery process of the diode will produce undesired stress on the IGBT during the operation. Therefore, the reverse recovery losses of the diode must be taken into account, because they will be rated to the switching losses of the IGBT. The switching and conduction waveforms of the diode (FWD) can be seen in Figure 2.7.

Figure 2.7: Switching waveforms of freewheeling diode in IGBT module [87].

When the diode conducts the current  $I_d$ , a voltage drop  $V_d$  will be across the diode. This condition will lead to turn-on and turn-off losses in the complementary switching. The conduction loss  $P_{conduction}(t)$  can be calculated as follows

$$P_{conduction}(t) = i_d(t) \cdot v_d(t). \tag{2.14}$$

The peak reverse recovery current  $I_{rrm}$  and recovered charge  $Q_{rr}$ , as shown in Figure 2.7, depend on the initial forward current  $I_0$  and the rate di/dt at which this current decreases. The turn-on loss  $E_{don}$  can be neglected, because the turn-on time is short and fast. Whereas the turn-off loss  $E_{doff}$  is determined by the reverse recovery charge of the diode [95]. The loss of energy  $E_{doff}$  can be calculated from Equation 2.15.

$$E_{doff} = \int_{t_w}^{t_f} V_m \cdot I_{rrm} \cdot dt. \tag{2.15}$$

Then the diode losses can be calculated as follows

$$P_{Dtotal} = (E_{conduction} + E_{doff}) \cdot f_{sw}. \tag{2.16}$$

#### 2.1.6 Thermal Characteristics of IGBT Modules

The IGBT temperature must be maintained below the critical level to avoid the device destruction during its operation. Generally, a significant amount of power is produced and it must be dissipated to the surroundings to prevent the temperature from rising to a level at which the device performance is unsatisfactory. A heat is generally removed to the surroundings by connecting the IGBT to a cooling surface or a heat-sink.

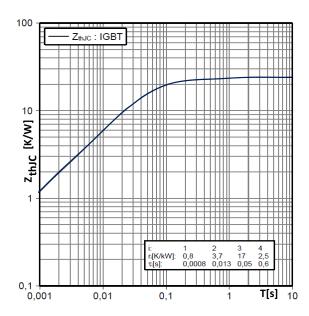

When a thermal design is achieved for an IGBT module, temperatures must be taken into consideration. The temperatures include the storage temperature  $T_{stg}$ , the virtual junction temperature  $T_{vj}$ , the junction-case temperature  $T_{JC}$  and the case heat-sink temperature  $T_{CH}$ . The thermal behavior of an IGBT module at the steady state is specified by the thermal resistance, whereas the thermal impedance  $Z_{thJC}$  characterizes the IGBT thermal behavior at transient conditions. The thermal resistance of junction to case  $R_{thJC}$  and case to heat-sink  $R_{thCH}$  are specified by manufacturers in a datasheet, whereas the transient thermal impedance  $Z_{thJC}$  is specified as a function of the time [1]. Figure 2.8

Figure 2.8: The transient thermal impedance  $Z_{thJC}$  as a function of the time  $Z_{thJC} = f(t)$  [95].

depicts the transient thermal impedance  $Z_{thJC}$  as a function of the time t, and it includes the partial fraction coefficient used for calculating the values of the capacitances as the

Figure 2.9: R/C Foster thermal model description [80].

following

$$C_i = \frac{\tau_i}{r_i} \tag{2.17}$$

where  $\tau_i$  is the time constant, and  $r_i$  is the thermal component resistance.

Knowing the thermal parameters  $R_{th}$  and  $Z_{thJC}$  of the device and the dissipated losses during the operation allow calculating the junction temperature. When the junction temperature is calculated, it must stay between the minimum and maximum specified values of the operating junction temperature  $T_{vj(op)}$  even in the case of hard conditions (overload, short circuit). There are various possibilities for measuring the device temperatures such as infrared cameras or using temperature sensors [13].

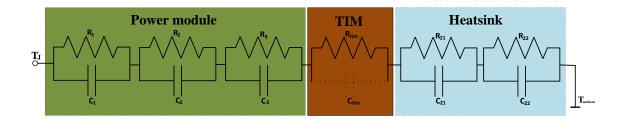

Every IGBT module has a thermal equivalent circuit which describes its thermal behavior during the switching operation. Figure 2.9 shows the thermal equivalent network using foster model, where the IGBT module is connected in series with the water cooled heat-sink via thermal interface material (TIM) [80].

The temperature changes can lead to mechanical stress which can result in a failure. Therefore, the thermal behavior analysis of IGBT modules mounted on heat-sinks was the issue of numerous articles. An RC component model (RCCM) is proposed in [117] for analysis the static and dynamic thermal behavior of the IGBT module mounted on water cooled heat-sink. It is important to have accurate thermal models for high power IGBT modules in order to predict its thermal behavior and calculate the junction temperature in the real time application [50].

#### 2.1.7 IGBT Gate Drive Circuit

As previously mentioned, the IGBT turn-on and turn-off are controlled by the gate voltage, and the speed of switching is determined by the gate current. The gate drive circuit feeds the IGBT gate signals. Therefore, it is considered as an interface between the logic signals generated from the controller and the signals of the IGBT gate.

Recently, the gate drive circuits have grown rapidly [74], to adapt with the development of switching devices which have special advantages, such as high currents, high voltages, high switching frequencies, and simple control [77] [8]. There are two types of gate drive

circuits, namely, voltage drive and current drive. The main function of the gate drive circuit is to convert the logic signals to power signals which control the IGBT switching. The gate drive circuit generates a positive voltage  $+V_{GE}$  during the turn-on, and a negative voltage  $-V_{GE}$  during the turn-off. Moreover, the gate drive circuit should control the time change rate di/dt of the IGBT collector current to avoid excessive Electro-Magnetic Interference (EMI), and it should control the time change rate  $dV_{CE}/dt$  of the IGBT collector-emitter voltage to avoid the IGBT latch up [53] [55].

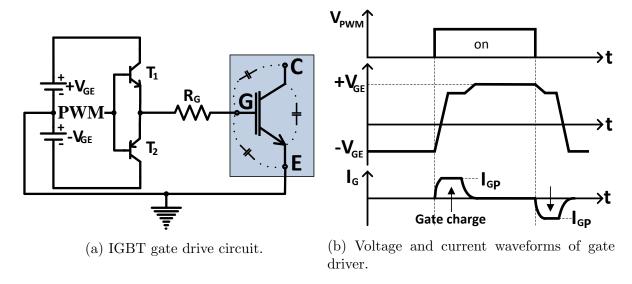

A simple gate drive circuit for IGBT module is shown in Figure 2.10a. The NPN and

Figure 2.10: IGBT gate drive circuit diagram and waveforms of current and voltage [29].

PNP transistors are used to convert the logic signal to the power signal. When the logic signal is high, the  $T_1$  is turned on and  $T_2$  is turned off. Accordingly, the IGBT gate is pulled up to  $+V_{GE}$ , and the IGBT module is turned on. When the logic signal is low, the switch  $T_1$  is turned off, and the switch  $T_2$  is turned on. As a consequence, the IGBT gate is pulled down to  $-V_{GE}$ , and the IGBT is turned off. A reverse bias must be used to ensure that the IGBT stays in its off-state when dv/dt noise is present in the collector-emitter voltage. The low reverse bias voltage does not only reduce the drive circuit power, but also improve the switching off time. In addition, the low reverse bias voltage can speed up the switching on time and the delay switching off time. A series gate resistor is used to limit the current flow through the gate. Equation 2.18 is used to calculate the peak value of the current flowed to charge and discharge the gate during the IGBT switching.

$$I_{GP} = \frac{+V_{GE} + \left| -V_{GE} \right|}{R_G + R_g} \tag{2.18}$$

where  $R_G$  is the external gate resistor and  $R_g$  is the internal gate resistor.

A small gate resistor reduces the switching times and switching losses, but this may cause a high surge voltage. The value of the gate resistor has a significant impact on the turn-on speed of IGBTs, while it barely affects the turn off speed.

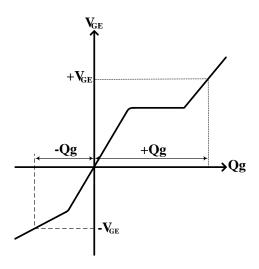

The average value of the drive current  $I_G$  can be calculated by Equation 2.19, using the gate charge characteristics shown in Figure 2.11

Figure 2.11: Waveform of IGBT gate charge characteristics [29].

$$+I_G = -I_G = f_{sw} \times (|+Q_g|+|-Q_g|)$$

(2.19)

where  $+Q_g$  is the gate charge from 0 V to  $+V_{GE}$  and  $-Q_g$  is the gate charge from  $-V_{GE}$  to 0 V. The gate drive power  $P_{d(on)}$  required to turn on the IGBT is given by

$$P_{d(on)} = f_{sw} \times \left[ \frac{1}{2} \times \left( \left| +Q_g \right| + \left| -Q_g \right| \right) \times \left( \left| +V_{GE} \right| + \left| -V_{GE} \right| \right) \right]$$

(2.20)

supposing that the gate drive power  $P_{d(off)}$  required to turn off the IGBT is equal to the power  $P_{d(on)}$ , then the gate drive power  $P_d$  required to drive the IGBT switching is written as follows

$$P_d = P_{d(on)} + P_{d(off)} = f_{sw} \times \left[ \left( \left| +Q_g \right| + \left| -Q_g \right| \right) \times \left( \left| +V_{GE} \right| + \left| -V_{GE} \right| \right) \right]. \tag{2.21}$$

Power circuit and gate drive circuit must be located as close as possible to the gate emitter control terminals of the IGBT module to minimize the stray inductance  $L_G$  in the gate path, which increases the switching losses. For high power applications, opto-couplers are used to avoid coupling of noise between the power circuits and the control circuits.

### 2.2 Present State in Inverter Diagnosis

The components of a drive system depend on their function and the place of use. Therefore, the faults and their causes may differ from system to another. The two components most prone to failure in the drive system are electrolytic filtering capacitors [51] [15] and power

devices, but 38% of faults in the drive systems occur due to the failure of power devices during the switching operation [57] [58].

This section deals with the IGBT fault diagnosis in power inverter, where the IGBT is taken as a working part or a failed part.

The IGBT transistor is a controlled device, where the gate drive circuit controls the IGBT switching. The literature includes a number of articles describing the fault diagnosis for IGBT transistor. The IGBT failure during the switching operation can lead to the failure of entire drive system. Therefore, it is important to protect the IGBT devices against the faults. The IGBT faults can occur due to external or internal causes. The external causes are environmental influences such as humidity, dust, electromagnetic radiation, and high temperature. The internal causes can be classified into open circuit faults and short circuit faults. In addition, IGBT gate driver faults can lead to the IGBT device failure.

The causes of failure in the drive system have been briefly discussed in [2]. This paper presented the fault causes in the variable frequency drives. Based on the results of failure analysis, the causes of the failure were electrical and non-electrical causes, but the most causes are non-electrical.

The IGBT open circuit faults, which are defined as electrical causes, may be caused by the lifting of bonding wires [4] [60], or by the gate driver failure [82] [75]. The open circuit fault is not considered a fatal fault, but it can lead to another fault in healthy parts. Therefore, it is necessary to get rid of these faults to protect the system from the complete failure. Several detection methods for open circuit faults have been developed. An open circuit fault diagnostic technique in IGBTs for the AC to DC converters has been achieved in [40]. Since the current value in the faulty leg will change during the open switch fault in the PWM rectifier, the absolute normalized DC current method is proposed. This fault detection method improved the reliability of the drive system, where any false alarm will be avoided. The fault detection is achieved during one cycle of the current waveform. The open circuit fault diagnostic technique presented in [66] is based on the line to line voltage measurement in voltage source inverters (VSI) which uses IGBT switches. This measured voltage value is combined with the gate driver signals using a simple circuit. This circuit is composed of some resistors, comparators, and logic gates "AND". However, this study is uncompleted, because it does not take into consideration the possibility of freewheeling diode fault and it supposes that this diode is always healthy during the IGBT open circuit fault. The same problematic is discussed in [97], where the proposed open circuit faults diagnosis method is achieved for multiple IGBTs faults in VSI fed an induction motor. This technique uses the slope method which was modified based on the proposed slope method in [76]. The algorithm of this modified method is achieved by the analysis of the current space vector trajectory diameter to detect and locate the fault occurrence in two IGBTs simultaneously. This method has some defects such as long detection times. In addition, this technique faces problems under the light loads.

The IGBT fault diagnosis based on the Park's vector method was achieved in [62]. A new diagnostic method is suggested in [28]. This technique can detect and locate a multiple open circuit fault in the VSI. The algorithm of this method is achieved using the combination of the current Park's vector phase and the currents polarity. Nevertheless, all

the methods, which use the Park's vector transformation in their algorithms, are complex and they require more efforts to achieve.

The short-circuit (SC) is considered the usual fault mode of semiconductors, because the short-circuit faults are very destructive. Therefore, the protection and diagnosis system requires special measures to turn off the drive system immediately.

The short circuit faults are based on a variety of conditions which differ from drive system to another. The IGBT SC fault can happen, if two transistors in the same inverter leg are turned on simultaneously. The driver circuit malfunction can lead to this fault [58].

The SC fault diagnosis is difficult to achieve because this event has a short time. During the SC fault, the current increases quickly, and it results in the destruction of the IGBT. Therefore, it is important to understand the IGBT behavior during the SC faults to design the suitable protection circuits that turn off the IGBT safely. Since the SC event is very fast, few mathematical algorithms are capable to record it. Therefore, the SC detection and protection are achieved by hardware circuits. Thus, most SC detection and protection for IGBTs are based on the gate driver design mechanism. The IGBTs SC withstand time, which can be in the range of 6  $\mu$ s to 10  $\mu$ s, is dependent on their type and structure. If the protection circuit failed to turn off the IGBT during the withstand time, the IGBT will be destroyed. The IGBT SC destruction modes may happen during the following periods:

- 1. Destruction during the IGBT turn-on due to a current spike.

- 2. Destruction during the IGBT turn-off due to a voltage spike.

- 3. Destruction after the IGBT conduction due to an abnormal current.

- 4. Destruction after the IGBT turn-off due to a thermal runaway.

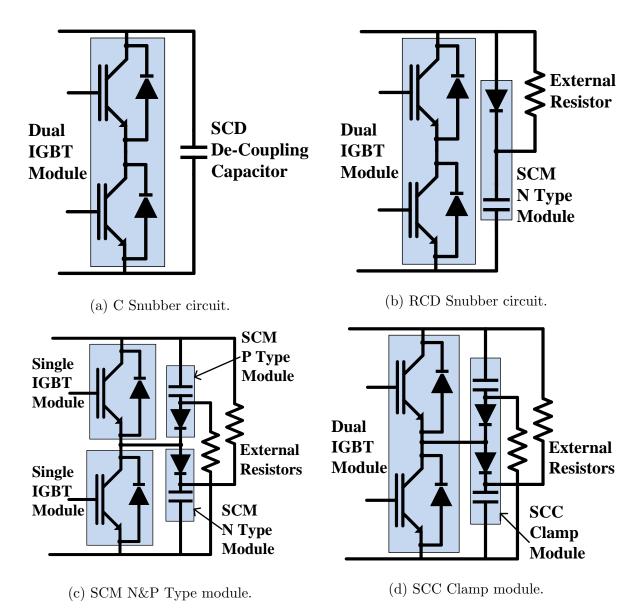

The voltage and current spikes on the IGBT can be reduced using a resistor capacitor (RC) damping network and a resistor-capacitor-diode (RCD) turn-off snubber. In addition, these circuits reduce the EMI by damping the voltage and current ringing. They also improve the reliability and the robustness against the SC conditions, but they increase the cost, size and losses in the drive system [10]. However, the efficiency does not increase. Moreover, the snubber circuits increase the commutation time. Accordingly, the dead time between the switching devices in the inverter has to be increased. The snubbers circuits used in IGBT applications depend on the power level, switching frequency, and circuit layout [89]. The snubber voltage will be at least equal to the maximum DC-bus voltage.

Figure 2.12 illustrates the snubbers circuits and their connections to the half bridge inverter. The C snubber circuit, shown in Figure 2.12a, is the simplest circuit used in medium current applications where it provides a low inductance path during the switching operation. Therefore, it reduces the transients. In high current applications, the C snubber produces a ripple current that can result in a capacitor failure. The RCD snubber, shown in Figure 2.12b, is used in medium and high current applications. In the higher current applications, the P type and N type SCM snubbers, illustrated in Figure 2.12c, may be used to protect the IGBT module against the over-voltage. This type of snubbers is suitable for

Figure 2.12: Types of snubber circuits used in IGBT applications [89].

high switching frequencies. It causes a small power dissipation loss. The power dissipation loss caused by the resistance of the snubber is calculated by Equation 2.22

$$P_{snub} = \frac{L.I_0^2.f_{sw}}{2} (2.22)$$

where L is the wiring inductance of the main circuit,  $I_0$  is the collector current at the IGBT turn-off, and  $f_{sw}$  is the switching frequency.

The dual IGBT module can be protected by the SCC snubber circuit, as shown in Figure 2.12d. This circuit reduces a reverse recovery voltage transient.

As mentioned before, the effective protection design requires understanding the IGBT behavior under the short circuit conditions, where the short circuit current may be 10 times the normal current. Based on the fact that the withstand time of most IGBT modules for SC is 10  $\mu$ s, the SC duration from the beginning to its turn-off must not last beyond 10  $\mu$ s. Nevertheless, the SC time is affected by various circuits parameters and fault conditions. The maximum SC duration  $t_{sc,MAX}$  greatly depends on the junction temperature  $T_{vj,op}$  and the DC-bus voltage  $U_{DC}$ , where the higher  $T_{vj,op}$  or  $U_{DC}$  will result in a shorter maximum permissible short circuit duration.

$$t_{sc} = f(T_{vj,op} \uparrow \downarrow, U_{DC} \uparrow \downarrow)$$

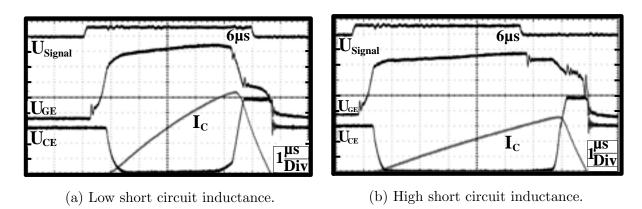

Moreover, the SC current and power dissipation are based on the inductance of the SC path. If the inductance is low, the di/dt at turn-on will be high, and the IGBT will be pushed into the desaturation state, as shown in Figure 2.13a, where The IGBT module enters the desaturation phase during a pulse time of  $6 \mu s$ . This fast change can lead to excessive power dissipation which generates a high temperature. Accordingly, the IGBT is destroyed, if the short circuit is sustained. If the inductance is high, the di/dt at turn-on

Figure 2.13: Effect of short circuit inductance on IGBT module behavior [100].

is low and the IGBT module doesn't enter the desaturation region quickly, as depicted in Figure 2.13b, where the IGBT doesn't go to the desaturation within the pulse of  $6 \mu s$ .

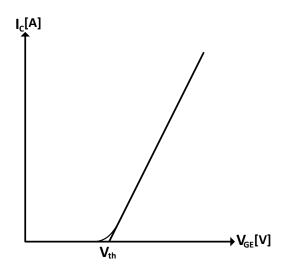

Generally, when the short circuit is turned off rapidly, the IGBT goes from the saturation mode to the desaturation mode but if the short circuit occurs before the IGBT reaches the saturated operation and when the SC is turned off due to the protection, a high du/dt occurs. This problem may happen, if the turn on process is slow. Therefore, the driver stage must turn on the IGBT as much as possible in a short time to attenuate the negative effects of such critical situation [100]. The short circuit inductance also plays a key role in the short circuit during the turn on, where a very low inductance increases du/dt and charges the gate beyond the nominal gate voltage via Miller capacitor. As a result, the IGBT can be destructed in spit of the protection devices. Another parameter called the forward transconductance  $G_{FE}$  influences the short circuit current. The  $G_{FE}$

is defined as a transfer characteristic which depicts how the gate voltage  $V_{GE}$  affects the collector current  $I_C$  with a constant collector-emitter voltage  $V_{CE}$ , where the rise of  $V_{GE}$  will result in the rise of  $I_C$ , as shown in Figure 2.14. Equation 2.23 defines the relationship between  $I_C$ ,  $V_{GE}$ , and  $G_{FE}$  as

Figure 2.14: Gate voltage effects on the collector current [14].

$$I_C = G_{FE}(V_{GE} - V_{th}) (2.23)$$

where  $V_{th}$  is the threshold voltage of the IGBT module.

The IGBT  $G_{FE}$  has a negative temperature coefficient. Therefore, it can protect the IGBT under the short circuit conditions [10].

The short circuit protection for the IGBTs and other power switch devices is an essential topic in the industrial applications, because the short circuit faults are destructive, and they can immediately destroy the switching devices and result in the entire drive system failure. Several approaches to the SC protection of IGBTs have been proposed and studied. Since the rise of the gate voltage  $V_{GE}$  is followed by the increase of the collector current due to the IGBT forward transconductance  $G_{FE}$ , several proposed SC protection methods were based on this function, where the short circuit current can be limited by the limitation of the maximum IGBT  $V_{GE}$ . The use of an external capacitor between the gate and the emitter can reduce the gate voltage after the fault. In addition, this capacitor reduces the Miller effect. But this technique affects the IGBT turn on time and it will delay the IGBT to reach its saturation mode. Another proposed method to reduce the  $V_{GE}$  during the SC fault is the use of a low gate resistor [18], where the fast change from the saturation to the desaturation causes a voltage swing which generates a negative current  $I_{GC}$ . This current causes the charge of the IGBT gate to values which are higher than nominal values provided by the gate driver. Therefore, due to  $I_{GC}$ , a low voltage will be created across the gate resistor which keeps the gate voltage within the nominal values. The increase of the gate resistor value will result in the increase of the turn on time  $t_{on}$  and switching losses  $(E_{on}, E_{off})$ . Moreover, the use of a very small gate resistor causes EMI noises, and it can lead to higher di/dt or dv/dt values. Therefore, the care must be taken when the gate resistor is chosen.

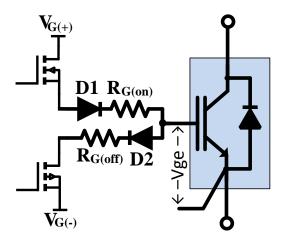

Generally, all the output stages of the proposed gate drive circuits have a gate resistor that is split into two resistors  $R_{G(on)}$  for switching turn-on, and  $R_{G(off)}$  for switching turn-off. This allows controlling and optimizing the switching turn-on and switching turn-off separately [18] [17] [83]. Sometimes, series diodes are placed to the gate resistors, as shown in Figure 2.15. However, the disadvantages of this method are the increase of the voltage

Figure 2.15: Gate resistors with series diodes.

drop at the output stage of the gate driver due to the diode forward bias, switching losses rise, increase of turn-on and off time, and increase of the PCB size.

As previously explained, when the IGBT transistor is turned on into a short circuit condition, a high current rises very quickly through it. After the occurrence of the short circuit detection, the IGBT is forced to turn off until it desaturates. In other words, due to the short circuit detection, the IGBT device goes from saturated operation to desaturated operation rapidly causing a high du/dt. Based on these conditions, several SC detection and protection circuits were suggested. The goal of these protection devices is to minimize the short circuit current and to decrease the high changes  $du_{ce}/dt$ . Therefore, the power dissipation is reduced and the system reliability increases. The fault current limiting circuit presented in [16] has the function of sensing the fault and lowering the gate voltage. The voltage  $V_{CE}$  is used to detect the short circuit fault. The advantage of this circuit is the reduction of the fault current and power dissipation during the short circuit. As a result, the short circuit withstand time increases. This circuit has several disadvantages: The first is that it cannot reduce the initial peak current because of its delay time during the normal turn-off transient conditions. The second is the disability of turning off the IGBT during the short circuit fault, and if the fault continues, the IGBT device will be destroyed. The last problem is that this circuit cannot detect the faults of light loads. Therefore, it is necessary to use additional means to this protection circuit to build a complete protection system, but this will lead to a more complex design and more cost. A new active protection method is proposed in [39]. This technique can limit the fault currents to acceptable level and safely shut down the IGBT. This method includes the desaturation technique. The protection circuit is able to suppress the initial peak current value. However, since it uses a resistors and diodes to sense the fault occurrence, the response time delay prevents its usage in high speed switching devices.

The desaturation technique is a common method for detection of the fault occurrence in the IGBT device [16] [39] [32]. The detection of SC fault is achieved, if the collector emitter voltage  $V_{CE}$  rises above 5-8 V during the on-state operation. The SC condition indicates that the collector current  $I_C$  has exceeded the normal value. This method is simple because it uses only a diode for sensing the fault.

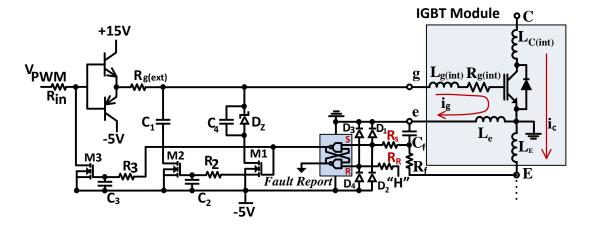

A new IGBT protection circuits are proposed in [33] [98] [102] to accelerate the fault detection time. The method technique is dependent on di/dt feedback control. The induced voltage across the stray inductance between Kelvin emitter and the power emitter is measured for the fault sensing. The induced voltage measured is investigated to extract the magnitude and the duration of di/dt signal which is used to control the IGBT shutdown during the SC fault. The advantage of this technique is its speed which allows it to be used with the high performance devices.

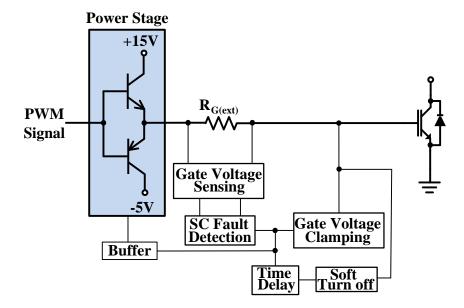

Figure 2.16: IGBT SC Protection circuit based on di/dt feedback control [102].

Figure 2.16 shows a SC protection scheme based on the voltage induced in the stray inductance between Kelvin emitter and the power emitter of the IGBT device. The induced voltage is given by Equation 2.24.

$$V_{Ee} = -L_{Ee} \cdot (di_c/dt) + L_{e(int)} \cdot (di_g/dt)$$

(2.24)

where  $V_{Ee}$  is the voltage drop between Kelvin and power emitter terminals in mV,  $L_{Ee}$  is the stray inductance between the power and Kelvin emitter terminals in nH. The  $di_q/dt$

is very small and it can be neglected. Then the  $L_{Ee}$  is expressed as

$$L_{Ee} \approx -V_{Ee}/(di_c/dt). \tag{2.25}$$

The SC fault is detected by the RS NAND Latch circuit, while the gate voltage clamping is achieved by the zener diode  $D_Z$  and capacitor  $C_4$ . After the clamping of gate voltage, the IGBT is softly turned off by adding the  $M_2$  and  $C_2$  to the operation.

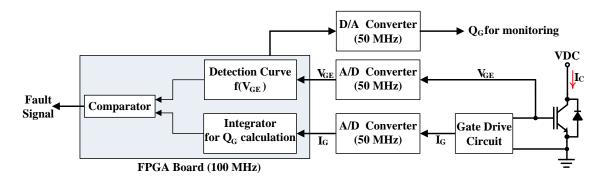

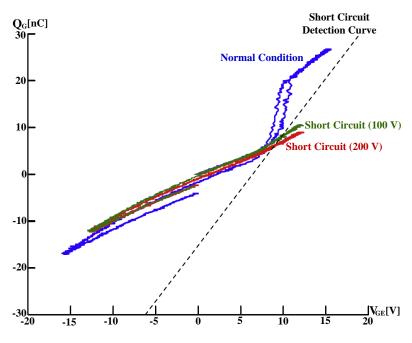

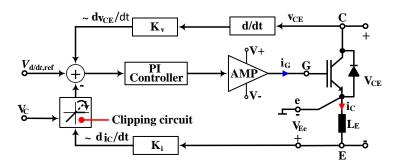

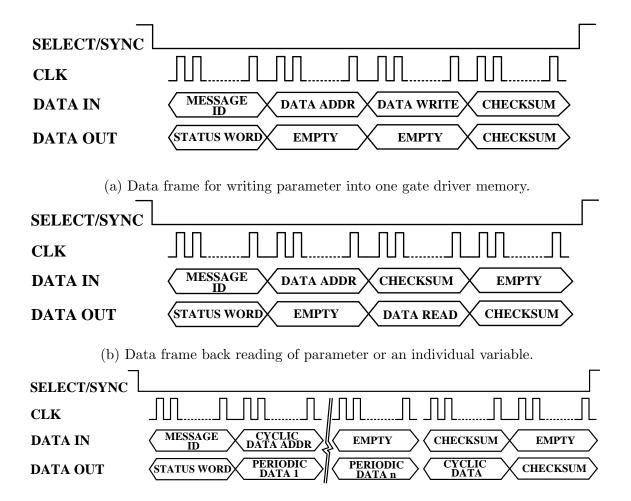

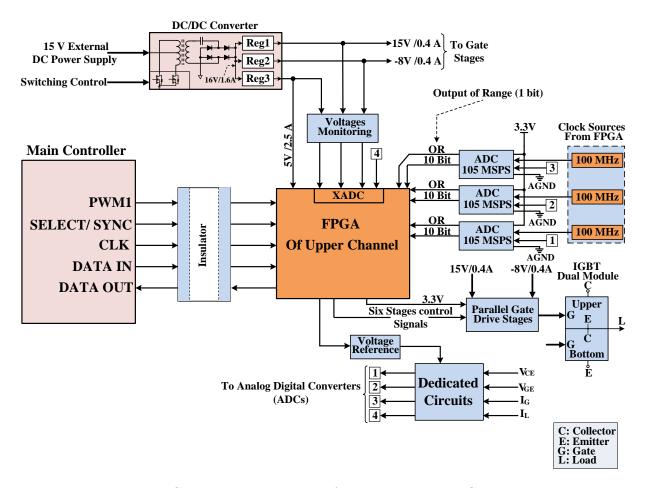

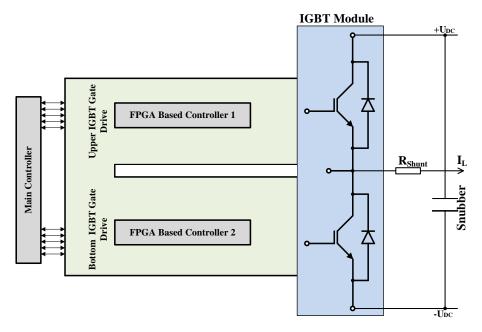

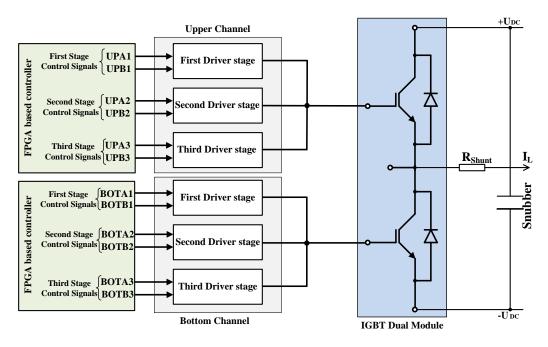

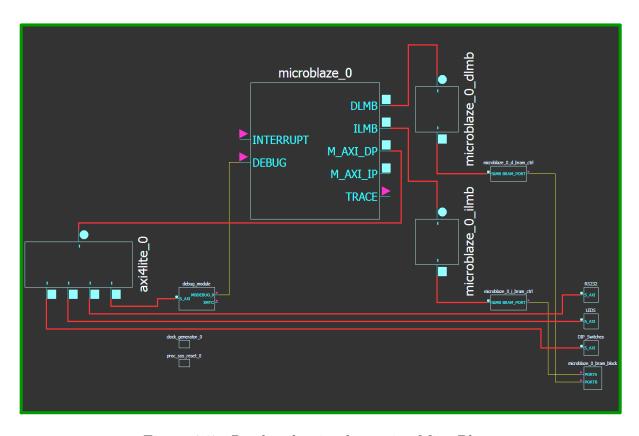

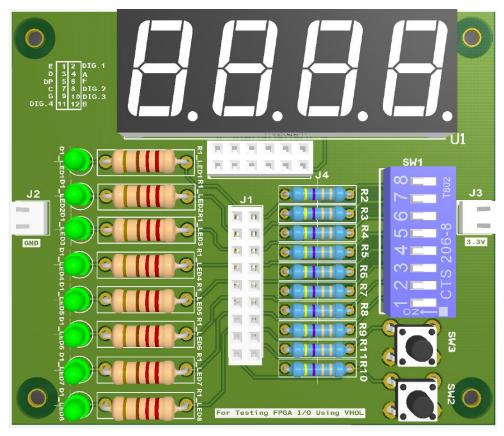

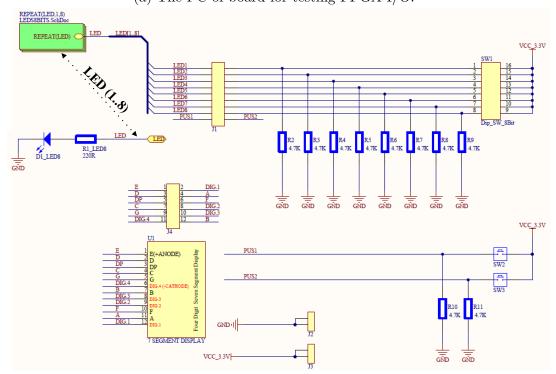

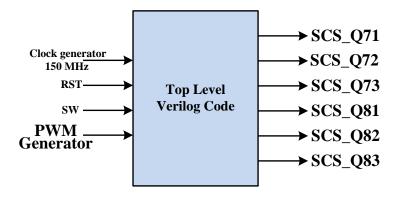

The similar approach has been discussed in [54], but in this proposed technique, the required measurements are achieved by a digital method. The digital method is an FPGA algorithm which can detect the SC occurrence.