### **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

**DEPARTMENT OF COMPUTER SYSTEMS**ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

# FAULT TOLERANT FIELD PROGRAMMABLE NEURAL NETWORKS

FIELD PROGRAMMABLE NEURAL NETWORKS ODOLNÁ PROTI PORUCHÁM

**PHD THESIS**

**DISERTAČNÍ PRÁCE**

**AUTHOR**AUTOR PRÁCE

Ing. MARTIN KRČMA

**SUPERVISOR**

doc. Ing. VLADIMÍR DRÁBEK, CSc.

ŠKOLITEL

**BRNO 2022**

### Abstract

This thesis focuses on the Field Programmable Neural Networks concept intended to make implementation of neural networks in FPGAs less resource demanding. The thesis introduces and discusses several types of Field Programmable Neural Networks which provide different trad-offs between the resource consumption and the accuracy of the implemented neural network approximation. This thesis also introduces and discusses methods of hardening the Field Programmable Neural Networks against faults with and without redundancy.

### Abstrakt

Tato práce se zaměřuje na koncept Field Programmable Neural Networks jehož cílem je učinit implementaci umělých neuronových sítí v hradlových polích méně náročnou jejich prostředky. Za tímto účelem práce konept rozvíjí a představuje několik jeho různých typů jež se vyznačují různými poměry mezi spotřebou zdrojů hradlových polí a přesností s jakou aproximují původní neuronovou síť jíž implementují. Teze díle rozšiřuje koncept o metody zabezpečení proti poruchám s využitím redundance a také bez ní.

### **Keywords**

Field Programmable Neural Networks, fault tolerance, neural networks, FPGAs

### Klíčová slova

Field Programmable Neural Networks, odolnost proti poruchám, neuronové sítě, FPGA

### Reference

KRČMA, Martin. Fault tolerant Field Programmable Neural Networks. Brno, 2022. PhD thesis. Brno University of Technology, Faculty of Information Technology. Supervisor doc. Ing. Vladimír Drábek, CSc.

# Fault tolerant Field Programmable Neural Networks

### **Declaration**

I hereby declare that this Ph.D. thesis was prepared as an original work by the author under the supervision of Mr. doc. Ing. Zdeněk Kotásek CSc. and Mr. doc. Ing. Vladimír Drábek CSc. I have listed all the literary sources, publications and other sources, which were used during the preparation of this thesis.

Martin Krčma August 31, 2022

### Acknowledgements

I would like to thank Mr. doc. Ing. Zdeněk Kotásek CSc. for his leadership and many years of professional support. Moreover, I would like to thank him for the wisdom and the life experiences he shared with me. I would also like to thank Mr. doc. Ing. Vladimír Drábek CSc. for his kind willingness to step in and take the role of my supervisor during a difficult time and to provide me the support I needed to finish this thesis.

# Contents

| 1        | 1 Introcution        |        |                                                               |                 |  |  |

|----------|----------------------|--------|---------------------------------------------------------------|-----------------|--|--|

| <b>2</b> | Neural networks      |        |                                                               |                 |  |  |

|          | 2.1                  | Neuro  | ns                                                            | 4               |  |  |

|          | 2.2                  | Activa | tion functions                                                | 4               |  |  |

|          | 2.3                  |        | hold                                                          | 5               |  |  |

|          | 2.4                  |        | topology                                                      | 6               |  |  |

|          | 2.5                  |        | ing of neural networks                                        | 7               |  |  |

|          |                      | 2.5.1  | Supervised learning                                           | 8               |  |  |

|          |                      | 2.5.2  | Unsupervised learning                                         | 8               |  |  |

|          |                      | 2.5.3  | Backpropagation                                               | 8               |  |  |

|          |                      |        |                                                               |                 |  |  |

| 3        | Fau                  |        | rance of neural networks                                      | 11              |  |  |

|          | 3.1                  |        | ele faults in neural networks                                 | 11              |  |  |

|          | 3.2                  |        | ning neural networks using learning                           | 14              |  |  |

|          |                      | 3.2.1  | Methods based on faults injection                             | 14              |  |  |

|          |                      | 3.2.2  | Methods based on restricting the weights                      | 16              |  |  |

|          |                      | 3.2.3  | Methods based on activation and basis functions modifications | 17              |  |  |

|          |                      | 3.2.4  | Methods using relearning                                      | 18              |  |  |

|          |                      | 3.2.5  | Other learning-based methods                                  | 19              |  |  |

|          | 3.3                  | Metho  | ods based on redundancy                                       | 19              |  |  |

|          |                      | 3.3.1  | Triple modular redundancy                                     | 19              |  |  |

|          |                      | 3.3.2  | Inserting new neurons                                         | 21              |  |  |

|          |                      | 3.3.3  | Temporal redundancy                                           | 21              |  |  |

| 4        | Trial                | d Duce | managa bla Naural Amaya                                       | 23              |  |  |

| 4        | 4.1                  | Tield  | grammable Neural Arrays Programmable Neural Network           | 24              |  |  |

|          | 4.1                  |        | The computation                                               | $\frac{25}{25}$ |  |  |

|          |                      | 4.1.1  | The computation                                               | ∠.              |  |  |

| 5        | $\operatorname{Res}$ | earch  | progress                                                      | 31              |  |  |

|          | 5.1                  | Appro  | eximation capabilities                                        | 32              |  |  |

|          |                      | 5.1.1  | FPNNs with a single operator per link                         | 33              |  |  |

|          |                      | 5.1.2  | Reduced and Full FPNNs                                        | 35              |  |  |

|          | 5.2                  | Fault  | tolerance                                                     | 36              |  |  |

|          |                      | 5.2.1  | Identity operators and mapping                                | 36              |  |  |

|          |                      | 5.2.2  | Triple modular redundancy                                     | 38              |  |  |

|          |                      | 5.2.3  | Detecting hard synapses fault                                 | 39              |  |  |

|          |                      | 5.2.4  | The FPNNs robustness                                          | 40              |  |  |

|    |                                                                        | 5.2.5 Recovery using partial dynamic reconfiguration               | 42        |  |  |  |  |

|----|------------------------------------------------------------------------|--------------------------------------------------------------------|-----------|--|--|--|--|

|    | 5.3                                                                    | List of Publications Related to the Thesis                         | 43        |  |  |  |  |

|    |                                                                        | 5.3.1 Author's contributions to papers related to The Thesis       | 45        |  |  |  |  |

|    | 5.4                                                                    | List of Other Publications, unrelated to the Thesis                | 45        |  |  |  |  |

|    | 5.5                                                                    | Research Projects and Grants                                       | 47        |  |  |  |  |

|    |                                                                        |                                                                    |           |  |  |  |  |

| 6  |                                                                        | Conclusions 4                                                      |           |  |  |  |  |

|    | 6.1                                                                    | Contributions                                                      | 51        |  |  |  |  |

|    | 6.2                                                                    | Possibilities of Future Research                                   | 52        |  |  |  |  |

| Bi | Sibliography 53                                                        |                                                                    |           |  |  |  |  |

|    |                                                                        |                                                                    |           |  |  |  |  |

| A  | Map                                                                    | oping trained neural networks to FPNNs                             | <b>62</b> |  |  |  |  |

| B  | 3 Comparison of FPNNs models approximation capabilities and FPGA re-   |                                                                    |           |  |  |  |  |

|    |                                                                        | ces utilization                                                    | 67        |  |  |  |  |

| С  | Con                                                                    | nparison of FPNNs Approximation Capabilities                       | <b>76</b> |  |  |  |  |

| D  | Detecting hard synapses faults in artificial neural networks           |                                                                    |           |  |  |  |  |

| E  | Fault tolerant Field Programmable Neural Networks                      |                                                                    |           |  |  |  |  |

| F  | Triple modular redundancy used in field programmable neural networks 9 |                                                                    |           |  |  |  |  |

| G  | Fau                                                                    | lt tolerant Field Programmable Neural Networks                     | 98        |  |  |  |  |

| Н  | Imp                                                                    | elementation of fault tolerant techniques into FPNNs               | L05       |  |  |  |  |

| I  | Fau                                                                    | It tolerance of different Field Programmable Neural Networks types | 109       |  |  |  |  |

### Chapter 1

### Introcution

It was the year 1943 when Warren McCulloch and Walter Pitts introduced the first mathematical description of a neuron in their A Logical Calculus of Ideas Immanent in Nervous Activity [40] paper. Their neuron was behaving as a logic switch, and they proved that an interconnected network composed of such neurons is able to calculate any operation of propositional logic. Donald Hebb followed their ideas and introduced the first learning algorithms for such neural networks in his book The Organization of Behavior [24] in 1949. Eight years later, Frank Rosenblat introduced perceptron [64], a generalized model of a neuron that worked with real numbers. He developed a learning algorithm for neural networks based on his model. The algorithm was able to calculate the desired configuration of the network in finite time and independently from the initial state of the network. With this algorithm in hand, Rosenblat constructed the very first neuro-computer, which he named Mark Perceptron I. The computer was able to recognize characters and its successful presentation attracted first serious attention and interest in neural networks.

The beginning of the seventies came with the first model of a binary associative neural network developed by Karl Steinbuch [70]. At the end of that decade, Marvin Minsky and Seymour Papert pointed out in their Perceptrons [43] book that the logical exclusive disjunction operation is impossible with only a single perceptron. The authors admitted that it was possible to realize the said operation with a network of three perceptrons organized into two layers. Unfortunately, no known algorithm could guide such a network to learn the operation at that time. From that, they incorrectly concluded that no such algorithm could exist. This unfortunate conclusion, together with a lack of new fresh ideas, led to a significant drop in interest in neural networks and caused cuts in funding for the research. Despite that, the research quietly continued and got the attention back when John Hopfield presented a new model of an associative neural network that worked as a memory in 1982 [25]. The same year brought another important model of neural networks - the Kohonen's networks [32].

David Rumelhart, Geo Rey Hinton, and James McClelland published one of the most used and essential learning algorithms - the backpropagation algorithm [65]. The algorithm was based on the iterative improvement of the network based on propagating the value of the network output error back through the network while modifying its weights. The first significant conference focused solely on neural networks, the IEEE International Conference on Neural Networks, was held in San Diego in 1987 and the neural networks have remained in the academic, research and software engineering communities' interest ever since.

### Chapter 2

### Neural networks

Neural networks generally are abstract mathematical structures inspired by the human brain even though artificial neural networks are massively simplified and more specifically focused compared to their original archetype. Just like the brain, artificial neural networks are composed of neurons. Similar to their biological counterparts, artificial neurons are interconnected by synaptic interconnections or for short, synapses. Synapses represent channels through which information flows between neurons while being modified by the synapses' parameters. Those parameters are generally called weights, and they represent the strength of the connection between neurons. It is the values of these weights that hold the knowledge that the particular neural network gained during its learning process.

#### 2.1Neurons

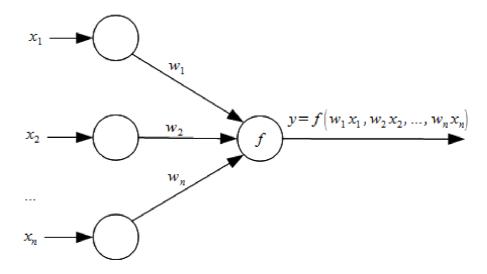

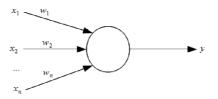

If we refer to Equation 2.1 representing a general model of an artificial neuron we can see that the neuron n has  $x_1, ..., x_n$  inputs representing all the incoming synaptic interconnections equipped with weights  $w_1, ..., w_n$  accordingly. The data modified by the weights then enter the function f which computes the output value y of the neuron that would be send through outgoing synapses to connected neurons (2.2). This function is called an activation function. The input of the activation function is generated by a function called basis function which transforms the set of input data  $x_1, ..., x_n$  and corresponding weights  $w_1, ..., w_n$ into a value called the neuron's potential or net. This value then serves as the input to the activation function. One of the most common basis functions is a weighted sum (2.1).

$$potential = net = \sum_{i=1}^{n} x_i w_i$$

$$y = f(net)$$

(2.1)

$$y = f(net) (2.2)$$

#### 2.2 Activation functions

In Section 2.1 we said it is the activation function of a neuron that generates its output which then serves as an input to other neurons or as the output data of the neural network itself. The activation function is, therefore, a core element of a neuron. Different types

Figure 2.1: General inside structure of a neuron

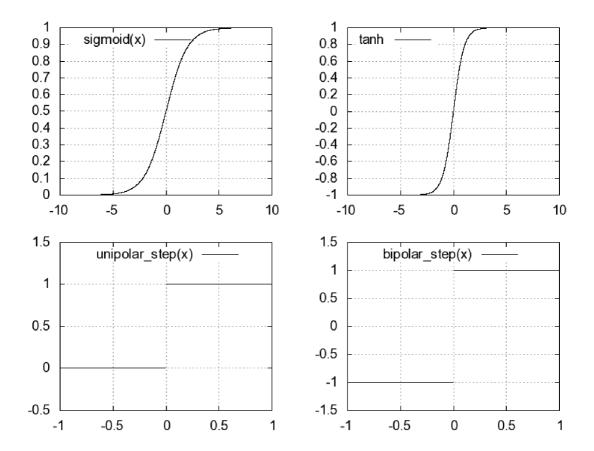

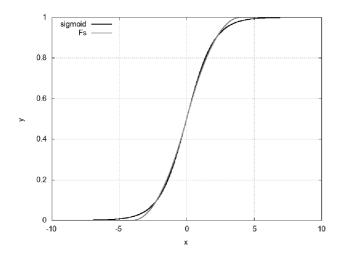

and models of neural networks utilize different activation functions or even combinations of different functions. An activation function is often an increasing continuous and differentiable function. Discontinuous functions can also be used, but their downside is that neural networks utilizing such a function cannot be learned with a learning algorithm based on differentials such as the Backpropagation algorithm described in section 2.5.3. The the most frequently used activation functions are for instance the sigmoid function (2.3), the uni-polar step function (2.5), bi-polar step function (2.6), hyperbolic tangent (2.4) which are defined as follows:

$$f(x) = \operatorname{sigmoid}(x) = \frac{1}{1 + e^{-\theta x}}$$

$$f(x) = \tanh(x) = \frac{2}{1 + e^{-2x}} - 1$$

(2.3)

$$f(x) = \tanh(x) = \frac{2}{1 + e^{-2x}} - 1$$

(2.4)

$$f(x) = \text{unipolar\_step}(x) = \begin{cases} 0 & \text{for } x \le 0 \\ 1 & \text{for } x > 0 \end{cases}$$

(2.5)

$$f(x) = \text{unipolar\_step}(x) = \begin{cases} 0 & \text{for } x \le 0 \\ 1 & \text{for } x > 0 \end{cases}$$

$$f(x) = \text{bipolar\_step}(x) = \begin{cases} -1 & \text{for } x \le 0 \\ 1 & \text{for } x > 0 \end{cases}$$

$$(2.5)$$

Fig. 2.2 illustrates the graphs of the said functions.

#### 2.3 Threshold

The threshold is a way to improve neural network capabilities by affecting a particular neuron's activation function independently. Originally the term threshold referred to an actual threshold that guarded the neuron output. It was a minimum limit that the neuron potential had to reach for the neuron to "fire," i.e., to produce an output. The neuron output would remain null if the potential did not cross this threshold. Even though this specific behavior can be achieved with a threshold as it is used in artificial neural networks, it is another variable that enters the computation of the neuron's potential rather than a limit imposed on it.

Figure 2.2: Activation functions

$$y = f(net + \theta) \tag{2.7}$$

Mathematically, a threshold  $\theta$  is a value that is added to the neuron's potential as shown in equation (2.7). It is figuratively a hidden weight with a constant input data of the value of one. The value of this virtual weight then enters the weighted sum of the potential as another element. By adding the threshold to the potential, every input of the activation function is shifted on the x axis by the same offset. The activation function of the particular neuron itself then appears to be shifted permanently on x axis. Furthermore, since the threshold is effectively just another weight, it can be determined together with the rest of the weights during the learning process.

### 2.4 Basic topology

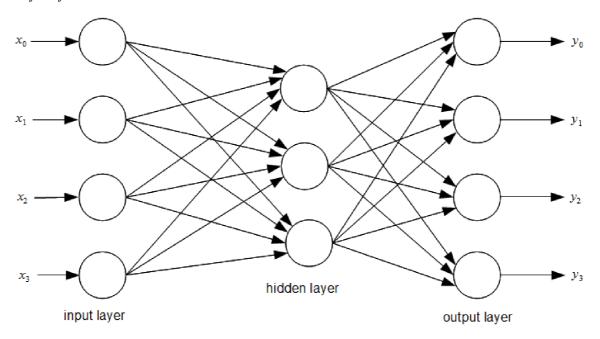

When Marvin Minsky and Seymour Papert derived that the logical function of exclusive disjunction can be realized by a network of three perceptrons, they also implied the most prominent building blocks of neural network architectures. That is, layers. Just like their three perceptrons network was composed of two successive layers, the following research also worked with neural networks like structures organized into layers. A neural network can be composed of a single layer, but usually, it is more. When a neural network has more

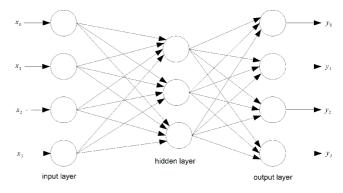

than one layer, then we call the first layer the *input layer* and the last layer the *output layer*. If the network has more layers than these two, then we speak of *hidden layers*. The number of neurons in each layer can differ from one another. The layers can have only one dimension in the form of a row of neurons, but any higher number of dimensions is possible. The neural networks working with image data usually have two-dimensional layers of neurons, for instance. A basic illustration of a one-dimensional neural network with one hidden layer can be seen in Fig. 2.3.

Another topological property of neural networks is the direction of the information flow. In other words, whether a feedback loop exists somewhere in the network. Usually, neural networks are feed-forward networks with information flowing from the input layer through hidden layers to the output layer and the outside world. It is also possible, however, to take a part of the output data vector and feed it back to the input layer. The Hopfield networks are an example of this topology. Similar feedback loops can exist between hidden layers as well. We can call the network with this property recurrent networks as opposed to feed forward networks.

Figure 2.3: Backpropagation model

### 2.5 Learning of neural networks

At the core of learning, algorithms lay the basic principle of how neural networks store their knowledge. It is the set of the particular network weights that stores that knowledge. Similar to the human brain, the weights represent the strength of connections between particular neurons and, therefore, the way how the information flow through different parts of the network. Just like the human brain "wires" itself to create neural paths that realize all our memories and skills, the artificial neural networks also basically realize their capabilities using the fact that the weights implement the way how the particular network is effectively wired.

Therefore, when we speak about a network learning to perform a specific task, we practically speak about setting the network's weights. The learning process sets the weights to make the information flow from the network's input through the neurons, transforming the input data to produce the desired results.

Bearing this principle in mind, we can say that the learning process creates a function or a map that connects desired output vectors to the inputs. This map is not a strict one, however. The relations between inputs and outputs that neural networks gains during their learning phase are not necessarily one-to-one. The relations are soft and indirect. Furthermore, in that fact lies the true strength of artificial neural networks. They are able to discover and generalize the relations between data vectors during learning and then apply this generalized knowledge to new and previously unseen input data vectors.

Moreover, if the network's knowledge is robust and general enough, it will be able to infer the correct relation and present a correct output data vector. To put this into a practical example, a neural network that has learned to recognize images of cars using a set of pre-prepared images. If the learning is sufficient, then the network will correctly recognize even an image of a car it has never seen before.

The learning process is then a process of determining the values of weights. The network usually starts with a randomized set of weights. This set is continuously modified in the learning process to bring the network to the desired operation step by step. Many algorithms can take the network through this process, and we generally recognize basic types - supervised learning and unsupervised learning.

### 2.5.1 Supervised learning

Supervised learning is based on an idea of a supervisor - a figurative entity that has knowledge of the task it wants the neural network to learn to do. Practically that means that the input data set intended to be used in the learning process has its desired-output data set counterpart. There is a known desired output data vector for every pre-prepared input data vector. The supervisor can then judge the output the network produces in response to the input data vectors and use this judgment in the consequent modifications to the network weights set to lead to the desired behavior. The backpropagation described in subsection 2.5.3 algorithm is a typical example of this type of learning method.

#### 2.5.2 Unsupervised learning

Unsupervised learning is, as the name suggests, a type of learning process that does not use a supervisor. That means it does not rely on pre-determined knowledge of how the network should ideally operate. Instead, it relies on the network to learn in a way that makes it discover the correct output by itself. In other words, unsupervised learning leads the network to discover patterns and features in the presented data and generalize the discovered relations. Deep learning is a typical example of unsupervised learning.

#### 2.5.3 Backpropagation

The backpropagation algorithm was published by David Rumelhart, Geo Rey Hinton, and James McClelland [65] in 1986. It is a gradient descent-based learning algorithm for a feed-forward neural network with multiple layers with all neurons in a layer, except the input layer, connected to all neurons in the previous layer. The layers are fully interconnected. It is a supervised learning algorithm based on presenting pre-prepared input data vectors

to the network, comparing the produced output vectors to corresponding correct output vectors, and calculating the difference. This difference is what drives the modification of the weights in the subsequent phase when the difference is propagated back to the network, from the output layer through the hidden layers back to the input layer. This is where the algorithm got its name. Because many methods discussed in the further parts of this work reference this algorithm, it is worth exploring it a little deeper.

### The algorithm

In this method, the supervisor feeds j number of input vectors  $x_1, ..., x_j$ . For every vector  $x_n$  the network calculates the output vector  $y_n$ . The supervisor calculates the difference between both vectors from the calculated vector and the expected and desired value  $t_n$ . When all the input vectors are presented to the network and all the differences collected, the supervisor calculates the sum of all the differences squared to determine the value of the error function E, as described by Equation (2.8):

$$E = \frac{1}{2} \sum_{j} (t_j - y_j)^2 \tag{2.8}$$

The algorithm's goal is to gradually reduce the error function's value and evolve the network closer to the desired configuration. Because it is the non-optimal value of the weights that cause the network to calculate differently than desired, we can clearly say that the error function is the function of the weights. In order to bring the network where the supervisor wants it to be, it is necessary to find the minimum of the error function. That can be done using simulated annealing or, more commonly, using gradient descent methods. Using gradient descend [45] we can derive the equation (2.9) for calculating the necessary weights modification in hidden layers and in the output layer:

$$w_{ij}^{(n+1)} = w_{ij}^{(n)} + \Delta w_{ij}^{(n)}$$

(2.9)

Where:

$$\Delta w_{ij}^{(n)} = \eta \delta_j o_i + \alpha \Delta w_{ij}^{(n-1)} \tag{2.10}$$

Equation (2.9) describes modification of the wights by adding a difference value calculated using equation (2.10). The  $\eta$  and  $\alpha$  values in the equation are positive real numbers that can be set at will as there is no preset way to calculate them. These values influence the algorithm's performance, and it is possible to modify them on the run to achieve better and quicker convergence.

If the activation function is the sigmoid function (2.3) and the network utilizes thresholds, using the function differential [45] we can define the  $\delta_i$  for the output layer:

$$\delta_j = (t_j - o_j) \, o_j \, (1 - o_j) \tag{2.11}$$

Where  $o_j$  is the output value of the neuron j and  $t_j$  is its desired value - the particular element in the desired output data vector. Similarly, we can calculate the  $\delta_j$  for the hidden layers:

$$\delta_j = o_j (1 - o_j) \sum_k \delta_k w_{jk} \tag{2.12}$$

Where k refers to the particular neuron in the output layer which back-propagated its  $\delta_k$  value calculated using the equation (2.11) to the neuron j in the hidden layer.

$\sum_{k}$  is a sum of all the differences sent back from the output layer and multiplied by the corresponding weights.

These deltas then propagate back to the preceding hidden layer, which calculates their on deltas using the same equation (2.12).

### Chapter 3

### Fault tolerance of neural networks

The fact that neural networks are distributed, redundant, and relatively homogeneous computational models had the researcher think about their fault tolerance. By nature, neural networks seem to have the potential to be inherently robust. A system composed of many interconnected components that are similar to each other and compute simultaneously might be able to tolerate a fault in one or even several of them. However, the layered structure of neural networks makes neurons dependent on the computation of all the neurons that proceed them in the previous layers. Should any of them produce erroneous results, the error might propagate and escalate in the following layers. The question of how robust the neural network can really be and whether this robustness can be improved has attracted research efforts throughout the years.

### 3.1 Possible faults in neural networks

When we want to evaluate possible faults in neural networks, we must consider different ways of viewing them because different faults can occur on different levels of abstraction and can be recovered using different methods. The natural way is to approach a neural network as a whole entity, a computation component. On this general point of view, there are two basic types of errors that can occur in a network's operation:

- Computation error the network generates erroneous outputs

- Communication error the network does not communicate properly with the rest of the system

A problem or a fault within the network would most probably cause the first type of error. The second type may be caused either by a fault inside the network or by an incorrect design of the network, its implementation, communication protocol, or implementation incompatibility with the rest of the system. A synchronization discordance and incompatibility of communication interfaces or protocols would be the most obvious suspects.

When we look closer at the composition of a neural network, we see that several types of faults can occur in the computation components that make the network. From the general point of view, a neural network is composed of neurons interconnected with synapses. Both can be seen as individual components, and both can suffer from different kinds of faults:

• The component's output is permanently stuck on a constant value. This type of fault can also represent a missing component, considering its output is stuck at zero.

• The component's output is erroneous. The output is affected by a value  $\Delta$ . The error can be additive (the  $\Delta$  is added to the output value) or multiplicative (the output value is multiplied by  $\Delta$ ).

Based on these possibilities, we can distinguish a set of possible faults regarding particular components:

Loss of a neuron By a loss of a neuron, we distinguish a situation when a neuron is permanently removed from the network or its output value is stuck at zero. The neuron does not participate in the following neurons' computation in both cases.

Loss of a synapse By losing a synapse, we distinguish a situation when a synapse is permanently removed from the network or its output value is stuck at zero. This can also be caused by an error in the corresponding weight that is stuck at a zero value. Another cause might be a problem with the corresponding neuron input.

**Saturated neuron** By a saturated neuron, we distinguish a situation when a neuron output is permanently stuck on one of the extrema values of the activation function codomain, the range of all its possible values. In the case of bipolar sigmoid activation function, the saturated neuron would have the output value 1 or -1.

**Saturated synapse** By a saturated synapse, we distinguish a situation when a synapse output is permanently stuck on one of the extrema values of the particular data type.

**Stuck neuron** By a stuck neuron, we distinguish a situation when a neuron output is permanently stuck on a constant value c. This problem can also be caused by an error in the neuron arithmetic unit, the following registers or memory cells, or the output bus.

**Stuck synapse** By a stuck synapse, we distinguish a situation when a synapse output is permanently stuck on a constant value d. This can also be caused by an error in the corresponding weight that is stuck at the value d. Another cause might be a problem with the corresponding neuron input.

**Transparent synapse** By transparent synapse, we distinguish a situation when a synapse becomes transparent to the data passing through it. It does not perform the computation it is supposed to but its output is not stuck, it let the data coming to its input to pass to its output. Effectively, this means that the data are not multiplied by the particular weight as they are supposed to. This can be caused by bypassing the computation components. The reason to bypass them might be to recover the network from a fault detected in the computation components.

**Noisy neuron** By a noisy neuron, we distinguish a situation when a neuron output is affected by a value  $\Delta$ . This situation can be caused by a transient error in the memory that participates in the neuron computation.

Noisy synapse By a noisy synapse, we distinguish a situation when a synapse output is affected by a value  $\Delta$ . This situation can be caused by a transient error in the memory that holds the corresponding weight. Another cause might be a noise in the corresponding neuron input.

Restricted neuron and synapse By a restricted neuron or synapse, we distinguish a situation when the output value of the neuron or the synapse is artificially limited in a particular range that is smaller than the activation function codomain (the range of all its possible values) or the used datatype. This situation can be caused by a permanent error in one of the memory cells that hold a particular weight or a result of the neuron computation.

For several reasons, it can be helpful to distinguish these fault types on the level of the components that make the neural network. The first reason is that we can select a particular type of fault, or a group of types, and harden the affected component against them while disregarding others to save resources or simplify the implementation. Moreover, we can also choose to harden only a particular selected set of components that we consider essential. We can also use an enhanced learning algorithm to harden the selected components to harden the network during the learning process. In this context, we can refer to two groups of components:

Critical neuron or synapse By a critical neuron or a synapse, we understand a component in which erroneous computation would have a significant impact on the quality of the results of the entire neural network. A fault in a critical component could cause the inability of the network to provide correct results.

**Non-critical neuron or synapse** By a non-critical neuron or a synapse, we understand a component in which erroneous computation would not have a significant impact on the quality of the results of the entire neural network. Even with the fault in the non-critical component, the network would still primarily provide correct or close to correct results.

We can also take a more detailed look beyond the abstract component and focus on the structure and building blocks of neurons. Like other computation component, those that build up into neurons and neural networks are prone to possible low-level faults like Single Event Upset (SEU) and others. Given the functionality of neurons, we can expect the design to utilize some of the following components:

- Adders that are collecting potential.

- Multipliers for multiplying by weights.

- Adders, multipliers, and other arithmetic units for computing the activation function.

- Registers and memory cells involved with the computation components and transferring data.

When we take a look at these components, we can predict a possible impact of faults occurring in them:

• Fault in the components computing the activation function would generally lead to the activation function changing its shape and therefore into an erroneous computation and output results.

- A fault in the adder responsible for computing the neuron potential would cause erroneous data to enter the activation function making all the following computations incorrect. This component's permanent fault would shift the activation function on the x axis.

- A fault in the multiplier responsible for multiplying the input data with corresponding weights would also cause erroneous data to enter the activation function. It could potentially lead to saturation or generate noise.

We can consider several approaches based on different principles to counter the possible faults on different levels of neural network design or enhance the neural networks' inherent robustness granted by their naturally redundant structure. We can increase network redundancy by adding more neurons, duplicating them, creating backup neurons, duplicating entire layers, or deploying techniques based on the majority principle like the Triple Modular Redundancy technique. We can introduce redundancy into the underlying components or even communication buses.

Different methods can be based on utilizing the learning process to harden the network naturally. If we set up a goal to learn the network to be more fault-tolerant, we can do so by modifying the learning algorithm or the condition in which they operate. In this approach, we can also focus on particular types of faults and errors.

### 3.2 Hardening neural networks using learning

Methods of hardening neural networks using learning are based on one of the known learning algorithms that were modified and expanded in a way that during the learning process, the neural network would not only learn to operate in the desired way but also learn to be fault-tolerant. These methods take into account different scenarios of possible fault occurrence and are designed to mitigate the impact of those scenarios using learning.

### 3.2.1 Methods based on faults injection

The methods based on fault injections utilize the fact that in the learning process, the neural network would gradually converge to the desired state regardless of its initial state or whether its state is externally changed. Given that the learning algorithm and the data used for learning are robust enough, the neural network would converge even when faults are introduced into its configuration. These faults would influence the quality of the network's output vector, increasing the error function. The faults would then become other variables in the error function, and their impact would be gradually reduced in the consequent learning. The learning phase would then naturally harden the network.

Methods based on this principle would use different types of faults to inject. They can remove neurons or synapses from the network in order to simulate their failure. They can also inject errors into network data, usually to the weights. It was shown that *injecting faults* into neural network weights during the learning phase would not only harden the network against faults causing errors in the weights but it would also *improve the network generalization capabilities* [15]. The injected faults would figuratively disrupt the network's convergence to the desired state the learning algorithm leads it to. The learning would be slower and harder so it would naturally force the network to discover deeper patterns in the input data. Therefore it would force the network to learn better potentially.

The first possible method based on this principle is a random faults injection into neurons weights in the hidden layers, one neuron at a time [7, 68]. In every iteration of the learning algorithm, a single random faults would be injected into a different neuron. The network would therefore learn to tolerate a single fault occurring in one of its neurons. We can also inject faults into more than one neuron or more than one weight in each iteration in order to harden the neural network against faults in multiple neurons. The fault injection, however, negatively impacts the error function, and it is possible to prevent the network from converging to the desired state at all by injecting too many faults during the learning process and therefore making it to fail.

Another method utilizing fault injection can be based on accounting for all the possible faults in a selected neuron [6, 7]. This method also uses fault injection during each iteration of the backpropagation learning algorithm. Suppose we have pre-prepared P input data vectors, and the hidden layer (suppose a single hidden layer in this description) is composed of N neurons. Then during each iteration of the learning algorithm, every input data vector is introduced to the network N times, with a fault being injected into a different neuron every time. The errors the fault injection caused in the output data are measured and a set of N errors are determined for every input vector, one for every neuron. The errors are then summarized into a single error value and propagated back through the network in the learning step of the backpropagation algorithm. Errors caused by faults in every particular neuron are part of the backpropagation algorithm's error function. By getting the error values for all neurons and including them in the backpropagation learning step, the network naturally learns to tolerate faults in all neurons in the hidden layer.

This method can be modified to teach the network to tolerate faults in more than one neuron. We can present each of the input data vectors  $N^m$  times and inject  $N^m$  combinations of faults when m is the number of faulty neurons we want the network to be able to tolerate. However, the number of injected faults can increase rapidly with rising m. As we mentioned earlier, it is possible to slow down the network convergence by injecting too many faults or events to prevent it from being able to learn at all.

These methods can be expanded to work with a neural network with more than one hidden layer. The methods must be applied to all the hidden layers in the described way.. It is also possible to select a subset of layers or neurons to be hardened while leaving the network vulnerable to faults in the others.

Another method of injecting multiple faults into a hidden layer is based on injecting an entire vector of faults. [28] In every iteration of the learning algorithm, a vector composed of n faults with n being equal to or lower than the number of neurons in the particular layer. The number of fault vectors is also n, and the x-th element of the x-th fault vector has a fixed value. Every vector, therefore, has one fixed value on the position corresponding to the vector index in the dataset. The rest of the element values are chosen randomly. By having a fixed value in each vector on the different indexes, the method assures that every neuron in the layer (or in the selected subset) is injected with a fault while also injecting random faults into the rest of the layer. While iterating over the set of the fault vectors, the method always injects at least one fault and a random number of random additional faults. The random generation of the additional faults is supposed to give the network a better chance to converge with its learning process because the authors presume that the injection of a fixed set of pre-selected have a chance to disrupt the network convergence.

Another approach to include hardening into the backpropagation learning algorithm is to construct a set of faults we want the network to harden against specifically and then use a modified backpropagation algorithm [80] utilizing a modified error function E. The

modified algorithm would evaluate the impact of all the faults in the set on the overall value of the error function ahead of learning. Then it would incorporate the error value caused by the faults into the error function during the learning process.

It is also possible to go beyond just a fault injection. Method published in [10] is based on fault injection and modification of the network structure. In each iteration of this algorithm, a random set of a fixed number of neurons is selected. Half of the selected neurons are then figuratively removed from the network by setting their outputs to zero, while the rest have their outputs artificially saturated. After that, a small set of synapses is randomly selected, and their weights are injected with random faults by adding a random number from a  $\langle -1, 1 \rangle$  interval to the weight value. The network then learns to tolerate multiple types of faults - lost neurons, saturated neurons, and lost or noisy synapses.

In order to harden a network against faulty synapses, the authors suggested proceeding to modifications of the network structure. After the network learned its task, each neuron's impact on the network performance was measured by removing it from the network, followed by testing the network. The testing data vectors were introduced to the network's input, and the difference between the new output data vectors and the initial data vectors was measured. Suppose removal of the neuron proves to cause a less significant difference in the output data (the authors accepted differences up to ten percent). In that case, the neuron is removed from the network. After the removal, the network goes through the learning process again. This process repeats until neurons can no longer be removed.

After the previous phase is finished and no more neurons can be removed from the network, the network is further hardened by successive replicating of the most critical neurons. The method determines the neurons whose removal had the most considerable impact on the output data quality. Then the neuron is replicated. The weights of the replicated neuron's input synapses are kept the same, and the weights of the output synapses of both the original neuron and its replica are halved. By halving the weights, the method assures the network returns to its original state even with the additional neuron. The reason is that the combined value both neurons provide to the neurons in the successive layer will sum up to the same potential. Halving the weights of both neurons also reduces their influence on the network performance, making a loss of either of them less critical. This process is repeated with other critical neurons until the replication no longer improves the network robustness.

### 3.2.2 Methods based on restricting the weights

These methods are based on the realization that the most fault-tolerant neural networks are those that have the most uniform set of weights, that have weights whose value do not significantly vary from one another. The more uniform the values of weights are, the more the possibility that some of them may be critical to a neural network's operation is reduced. However, most networks do not have this property because the learning process usually produces networks with a nonuniform set of weights. The network often has some weights that are critical to its function, usually with high values. A fault injected into these weights could significantly impact the network performance. Many of the other weights are less critical to the network operation. If the weights of the network could be made uniform, then a fault in any of them would have a more negligible impact on the network performance. This can be achieved by artificially restricting the values of the weights.

One of the methods how for reducing the number of critical weights is based on continuous evaluation of their impact on the output data. Those weights that prove to have a

large impact are then reduced in value, so their influence would also reduce. If the values of the weights are continuously restricted, the learning algorithm is forced to produce a network with more uniform weights. However, limiting the time interval during which this method is applied might be necessary because it might slow the learning process down or event prevent the network from converging to the desired state at all. On the other hand, this method can produce a network with higher generalization capabilities [20].

Another option to prevent the learning algorithm from generating weight with high values is to force it to minimize them during learning [10, 78, 79]. For the algorithm to do that, the error function (2.8) needs to be modified. The summarized value of the output errors is expanded with a sum of all the weights values squared as illustrated in equation (3.1), where W are the set of all weights.

$$E = \left(\frac{1}{2}\sum_{j}(t_{j} - y_{j})^{2}\right) + \sum_{w \in W} w^{2}$$

(3.1)

This modification means that the error function rises with the values of the network weights. The learning algorithm is then forced to minimize the network's weights as well together with the output error in order to minimize the error function. This method can be modified to only consider the weights of synapses connecting the hidden layer to the output layer, which might prove to be a more efficient approach to hardening the network [22, 23].

Besides modifying learning algorithms to make them harden the network, it is possible to approach the problem as a direct optimization problem. The need for the network to learn and the desire to harden it against fault can be seen as an optimization problem solvable with the Minimax method [12]. The algorithm's objective function that is supposed to be minimized represents the optimization problem. In this case, the objective function is the error function. The constraints set to the method are designed to make the algorithm as uniform a set of weights as possible and thus preventing the occurrence of critical weights. The Minimax algorithm is not the only optimization algorithm that can be used for hardening a neural network. The usage of quadratic programming [14], an optimization method, was also successfully demonstrated.

It was also shown that Hopfield neural networks [46] can be hardened by restricting the weights as well [29]. Hopfield networks are recursive networks containing a feedback loop that serves as an associative memory.

#### 3.2.3 Methods based on activation and basis functions modifications

These methods are based on the idea that it is possible to harden the network using neurons functions manipulation - the basis function that calculates the neuron potential and the activation function that calculates the neuron output from its potential.

The first method is a method modifying the basis function. This method changes the way of calculating the potential by replacing the original summation in the basis function with calculating a median value instead. The neuron's inputs are still being multiplied by the respective weights, but the median value is computed instead of the weighted data being summarized. By applying the median, the method filters out the input data influenced by weights with very high or very low values. Faults might cause these extreme values, and their influence would be mitigated by filtering them from the potential computation. However, because the median is not a continuous function and therefore is not a fully differentiable

function, the backpropagation algorithm needs to be modified. The experiments in the original paper show that a neural network composed of neurons with a median basis function showed a 10% better classification results than the original network with a weighted sum basis function. The results also show that the method performs the best when only the neurons in the output layer have their basis function replaced by the median [67].

Another possible approach is based on manipulating the activation function [30, 81]. This method is based on modifying the slope of a sigmoid activation function of the neurons to make it steeper. The neural network does through the learning phase with activation functions of its neurons having a modest slope. The slope is gradually made steeper and steeper. At the end of the learning process, the slope is so steep that the activation functions effectively turn into step functions. With the activation function like that, an output of a neuron mainly falls into one of the extrema. Should some fault influence the input data of the neuron and, therefore, its potential, there would be a significant chance that it would not affect the neuron's output at all as the output would still fall into the same extrema. This method is, however, suitable only for classification tasks.

### 3.2.4 Methods using relearning

These methods are based on the idea that if some permanent fault should occur in a neural network, it can be mitigated by letting the network relearn. The advantage of this approach is that there is no need to modify the learning algorithm or the network structure. It is the rest of the network that is unaffected by the fault and is still functioning that is used to mitigate the fault by relearning how to perform the given task in the presence of the fault. However, the network learns and later operates with fewer resources because some were lost due to the fault. Therefore, the network might not be able to recover fully. Also, the fact that the network relies on relearning is another disadvantage because the learning process can be time-consuming, and the original data the network learned from must be accessible. Both temporal and spatial complexity of this method is high.

The most simple but the least practical approach to recovering the network using learning is just to start the process of learning after the fault is detected. However, inserting a new neuron into the network to take the role of the faulty neuron and then take the network through relearning might be more effective [68]. This approach can recover the network into its fully operational state; however free resources to insert the additional neuron into the network must be available.

In the case of neural networks implemented in hardware, more than errors in data might occur but also errors in timing and synchronization. These can be troubling because they might not be easily detectable. A method based on the backpropagation algorithm was proposed to solve this problem [11]. This method aims to determine and verify the working frequency of the device that makes the device work the most reliably. This method is based on simulating the computation of the particular neural network with different deviations from the estimated ideal working frequency. The results of the simulations are applied to the backpropagation algorithm that lets the network learn to work on different frequencies. The overall error values the algorithm achieved are monitored. For each iteration of the method, the set of weights and the corresponding frequency are saved, and the final setting of the network's weights and working frequency is based on which frequency achieved the smallest overall error. The selected frequency should be the optimal working frequency for the particular network and the device it is running on.

### 3.2.5 Other learning-based methods

The backpropagation algorithm is not the only gradient descend-based learning algorithm that can also be used to harden the network. A learning algorithm based on the gradient descent and the Kullback-Leibler divergence was suggested [73]. During each iteration, this algorithm includes vectors of Gaussian noise to inject faults into the network weights. During learning, the noise is incorporated into the weights and the networks become more resilient against faults with Gauss noise characteristic affecting the weights.

In the case of Hopfield neural networks implemented in software, a method hardening the network against errors in data of the learning algorithm due to a corrupted memory is in [39]. All-access to data arrays in the memory access was protected by modulo operation to ensure that the correct region of the memory was accessed [82]. The iteration counter in the core of the learning algorithm, which serves for convergence evaluation, was hardened against data corruption by calculating a logical disjunction of its value with the value of an additional auxiliary variable. The variable was initialized with a non-zero value that is not a multiple of two. The iteration counter was initialized with the same value. This ensures that one erroneous bit in the iteration counter would not change its value to zero, thus stopping the learning algorithm prematurely. Using the logical dis-junction with another variable ensured that the iteration counter value was overwritten each iteration with a correct value.

Another measure of hardening the network learning was based on connecting an identical neural network to the hardened network. The second network serves as a golden model producing a correct value in case a fault occurs in the original network. The key idea is that even if the first network is not able to converge, the second one still is. If the second network were faulty, then it would not affect the first one.

### 3.3 Methods based on redundancy

The neural networks are, by principle, massively parallel and redundant structures. This redundancy provides them with inherent fault tolerance. A neural network can withstand a fault of a neuron or a synapse, especially if hardening techniques were applied during the learning process or modifications of the network's properties were used to improve its robustness, as described in the previous sections. However, their robustness can potentially be improved by techniques based on adding more redundancies to the network.

#### 3.3.1 Triple modular redundancy

The triple modular redundancy (TNR) is a classic method of hardening a system. This technique is based on triplicating the system or its subsystems and adding a voter that would evaluate the outputs of all three instances and vote for the correct one by the principle of majority. Even if one of the three instances were faulty, the system would still operate correctly.

This technique can be applied to neural networks as well. It can be applied to the entire network or its components on different levels. Of course, triplicating the whole network is an easy way to harden it without needing to modify the network's structure or doing any significant interference. However, it also triplicates the network spacial complexity, which can be already high in the case of most neural networks. The number of neurons and especially the number of weights grow quickly with the complexity of the implemented

task, and it might not be possible to expand it much more, let alone multiply it. Depending on the network implementation, triplicating may also increase the temporal complexity.

The TMR method can be applied to the level of individual neurons and synapses. The advantage is that we can individually choose what to harden and how. We can choose only a subset of neurons and synapses we deem critical. The method can also be used on the level of computing blocks themselves. We can triplicate the adders, multipliers, and other low-level blocks. We can even go as far as using this technique on the bits themselves. A method has been proposed for hardening a neural network using TMR while keeping the overhead as low as possible. The method is called Relaxed Triple Modular Redundancy (RTMR) [37] based on hardening the computational blocks and the interconnecting buses on the bit level but only on the level of the selected subset of high bits. In this approach, only the more minor part of the bits is hardened, and the rest of the design is still vulnerable. However, it is the least significant bits that are left unhardened. Naturally, the low bits have a lower influence on the overall values entering the computation. Its influence may be less critical if an error occurs in the lower bits. The advantage is that the spacial overhead consumed by replicated resources is significantly lower than in the case of the full TMR. It is at the expense of a trade-off between hardening and resource consumption, but it can be accommodated to the situation with the proper choice of hardened bits.

In the case of triplicating entire neural networks, voters with weighted inputs can also be used as demonstrated in [5, 35, 63]. The principle of this modification is that the voter at the output of the hardened system considers its inputs to have different priorities, and it uses those priorities given by their weights in the voting process. The input with a higher weight gets priority. For example, the weights can be determined using a backlog of faults that occurred in all three replicas. The weights can also be learned [84]. In this approach, the system is composed of three neural networks. However, the networks are not identical. Each network learns individually and independently from others in three different steps. In the first step, the networks learn to perform the desired task. In the second step, they learn again, but their input data were individually injected with faults. In the third step, they learn one more time and face simulated loss of some of their neurons. The weights for the voter are then determined by how well each network operated during the first steps. The more reliable and quality each network proved to be, the higher its weight gets.

In [54] the authors experimented with different replication orders. The root of the experiment was to create a set of different neural networks with different numbers in the hidden layers and let them learn to perform a classification task called Sonar [19]. In the next step, the networks were replicated in different orders. After that, their tolerance to loss of one of the neurons or synapses was evaluated. The authors came to two interesting conclusions. The first conclusion was that when the resulting neural network had the same size, it was the network that was created by a lower number of replications while using a larger starting network that proved more reliable. On the contrary, when the network was created by more extensive replication but from smaller original networks, it was less reliable. So, for example, a neural network composed of eight neurons in the hidden layer created by duplicating a network composed of four neurons was more reliable than a network created by four replications of a network with two neurons.

The second conclusion was that neural networks created by replicating smaller networks were more reliable than a network of that same size that was not created by replication. For example, a neural network composed of eight neurons in the hidden layer created by replicating the original four-neuron network was more reliable than a neural network constructed and learned with eight neurons without any replications.

Another successful use of TMR was demonstrated in [66]. The authors determined how critical each neuron was for the considered network computation and ordered them by the measured criticality. They selected a number of the most critical neurons and hardened them using TMR. They removed the same number of the least critical neurons to compensate for increased computation complexity. Their method managed successfully to harden the selected network against lost and noisy neurons.

### 3.3.2 Inserting new neurons

Neural networks can also be hardened by inserting new neurons into hidden layers. This approach comes with less overhead than replicating an entire network or its significant part. Naturally, the hardening effect is lower. As such, they are a middle ground between complete replication methods and replication-free methods based on relearning and modification of neural network configurations. These methods are always trade-offs between reliability and spatial complexity. It is also important to point out that these methods only apply to hidden layers because the respective data vector sizes give the input and output layers sizes.

The most basic technique is based on adding a single neuron into a hidden layer [3]. This technique not only hardens the network but also allows us to detect a fault in any of the neurons of the hardened layer. The technique works as follows. Suppose the neurons in the hardened layer are equipped with enough memory storage for two vectors of weights. One vector is for storing the operational weights, and the other is the testing vector for storing weights used for fault detection. The neurons are then tested in pairs. The weights of the first neuron in the pair are set to the values of the testing vector belonging to the second neuron in the pair. After that, both neurons receive the same input vector, and their output values are compared. If the values are different, then the network is possibly affected by a fault in one of the neurons in the pair. The second neuron then becomes the first in its own pair, and its subsequent neighbor in the layer becomes the second neuron in the pair. Then the test is repeated. Therefore, every neuron is tested twice (the last neuron in the layer will be paired with the newly inserted neuron). If a neuron suffers from a fault, it likely fails both tests and therefore is detected as faulty. The newly inserted neuron can take the faulty neuron role by setting its operation weights vector accordingly. Using this approach, we can build a neural network that is able to detect a single faulty neuron and recover from the fault. Naturally, every hidden layer can be hardened using this method.

Another approach [52, 53, 85] is based on multiple replications of all neurons. The neurons are replicated h times, then the thresholds of the neurons in the following layer are multiplied by the same value. This ensures the network computes the same way despite the replicated neurons while also being hardened against the faults in the replicated layer. If changing the thresholds does not suit the design for some reason, the same effect can also be achieved by dividing the weights of the synapses between the layers by the number h [16]. Both methods have the same result. The potentials of the neurons in the following layer will have the same values as before replication; therefore, the layer will compute the same way.

#### 3.3.3 Temporal redundancy

All the techniques discussed before were based on redundancy and utilized spatial redundancy to harden neural networks. However, it is also possible to achieve the effects of redundancy by performing additional computations. The most trivial method is just to

compute the result several times in a row and then compare the results to detect an error or select the correct result based on the majority principle. This approach can also be utilized together with spatial redundancy. Suppose the network is hardened in a way that uses replication and majority principle, but the fault detection fails. In that case, it is possible to recompute the results and then retry the fault detection.

An approach utilizing both spatial and temporal redundancy was introduced in [26]. The arithmetic unit used for computing the weighted sum was divided into three smaller units. Its operands were also divided into three parts based on the significance of the bits. The computation was divided into three phases. In the first phase, the data part with the least significant bits was introduced into all three arithmetic units, and three semi-results were computed. The second and third parts of the original operands were introduced to the arithmetic units in the two consequent parts. Their results were combined according to the significance of the particular parts. Eventually, three independent full-operand results were produced using three independent arithmetic units. The results were compared, and the final result was selected using the majority principle.

### Chapter 4

## Field Programmable Neural Arrays

The concept of Field Programmable Neural Arrays (FPNAs) [17] is designed to enable a resource-efficient implementation of artificial neural networks in Field Programmable Gate Arrays by adjusting the network's properties and especially its structure in order to make them more efficiently implementable into the gate arrays. For instance, FPNAs were used for implementing large scale spiking networks [21]. The efficiency comes from the FPNA's main feature - a highly customizable structure that enables the designer to build it in a way that allows sharing the FPGA's resources by merging sets of synapses into several dedicated components. This concept also simplifies the interconnection structure compared to the original neural network. The number of neurons remains the same.

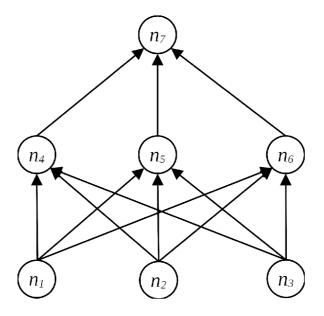

By the original definition by B. Girau [17], an FPNA is directed graph (N, E) where N is a set of nodes and E is a set of directed edges that connect the nodes:

**Definition 4.0.1** (FPNA [17]). We say that structure (N, E) is an FPNA if the following statements hold true:

- 1. N is a set of nodes called Activators. Activators represent the original neural network neurons.

- 2. E is a set of directed edges called *Links*. Link connect activators.

- 3. Each activator n has a set of predecessors:  $Pred(n) = \{p \in N, (p, n) \in E\}$

- 4. Each activator n has a set of successors:  $Succ(n) = \{s \in N, (n, s) \in E\}$

- 5. There is a set of input nodes:  $N_i = \{n \in N, Pred(n) = \emptyset\}; N_i \subset N$

- 6. Each link  $(p,n) \in E$  has an affine operator:  $\alpha_{(p,n)} = W_n(p)x + T_n(p)$

- 7. Each non-input activator  $n \in N$  has an *iteration operator*:  $i_n : \mathbb{R} \to \mathbb{R}$  to calculate its potential.

- 8. Each non-input activator  $n \in N$  has an function operator:  $f_n : \mathbb{R} \to \mathbb{R}$  to calculate the activation function.

Definition 4.0.1 states that the original neurons are represented by the nodes in the graph, the *activators*. The activators use their iteration operators  $i_n$  to calculate their potentials and then apply their function operators  $f_n$  to calculate the activation functions over the potentials and thus generate their outputs. Therefore, the activators principally closely mimic the function of neurons.

The activators are interconnected by edges, by links. The links calculate an affine transformation of their inputs using their affine operators  $\alpha$ . By doing this, they approximate multiplying the data by the corresponding weights. Therefore they participate in calculating the weighted sum by taking this part of the computation out of activators. Moreover, each link can approximate multiple synapses for multiple activators. Therefore, the weighted data are calculated for each activator in parallel by a set of links that connect them to the preceding activators. The definition allows the activators to be connected by more than a single link. It is possible to create chains of links between activators or layers and, therefore, to split each synapse and the corresponding weight into a set of successive affine operators. Because this possibility exists, it is helpful to introduce a unifying term for both activators and links - neural resources.

FPNAs resemble restructured original neural networks they implement; however, they still miss some necessary properties and parameters to achieve their main goal - to convert the neural networks into structures suitable for implementation in an FPGA. The additional details must be defined using *Field Programmable Neural Network* to reach this goal.

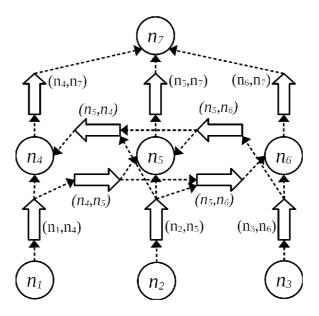

### 4.1 Field Programmable Neural Network

FPNN (Field Programmable Neural Network) [17] is one of the possible configurations of an FPNA. It defines the interconnections between neural resources and, therefore the FPNN's actual structure, and it defines concrete settings of the parameters and operators:

**Definition 4.1.1** (FPNN [17]). We say that structure (N, E) is an FPNN if the (N, E) is an FPNA and each non-input activator  $n \in N$  and each link  $(p, n) \in E$  have the following defined:

- 1.  $\Theta_n \in \mathbb{R}$  initial value of the variable used by the iteration operator  $i_n$ . This value represents a threshold.

- 2.  $a_n \in \mathbb{N}$  the number of iterations to performed by the  $i_n$  operator.

- 3.  $W_n(p), T_n(p) \in \mathbb{R}$  the setting of the affine operator.

- 4.  $\forall p, p \in Pred(n) : r_n(p)$  a binary flag indicating whether the link (p, n) and the activator n are connected.

- 5.  $\forall s, s \in Succ(n) : S_n(s)$  a binary flag indicating whether the activator n and the link (n, s) are connected.

- 6.  $\forall p, s; p, s \in Pred(n), s \in Succ(n) : R_n(p, s)$  a binary flag indicating whether the link (p, n) and the link (n, s) are connected.

Moreover, every input activator  $n \in N_i$  has the following defined:

- 1.  $c \in \mathbb{N}$  the number of inputs

- 2.  $\forall s, s \in Succ(n) : S_n(s)$  a binary flag indicating whether the input activator n and the link (n, s) are connected.

Definition 4.1.1 declares several binary flags that indicate local connections between activators and links and between links and other links. These flags, as well as the order of

neural resources defined by their Pred and Succ sets, describe the actual structure of the particular FPNN. It also defines concrete values of other parameters.

The FPNNs do not have the same structures as neural networks, although they can be constructed that way. They are based on a different model that can be structurally different from the original neural network. This also means that the FPNA can differ in its capabilities. In principle, the FPNNs are not a straightforward implementation of neural networks but rather their approximation designed in an FPGA-friendly way. Since the FPNNs can be constructed in various ways and types, the approximation accuracy can be different.

### 4.1.1 The computation

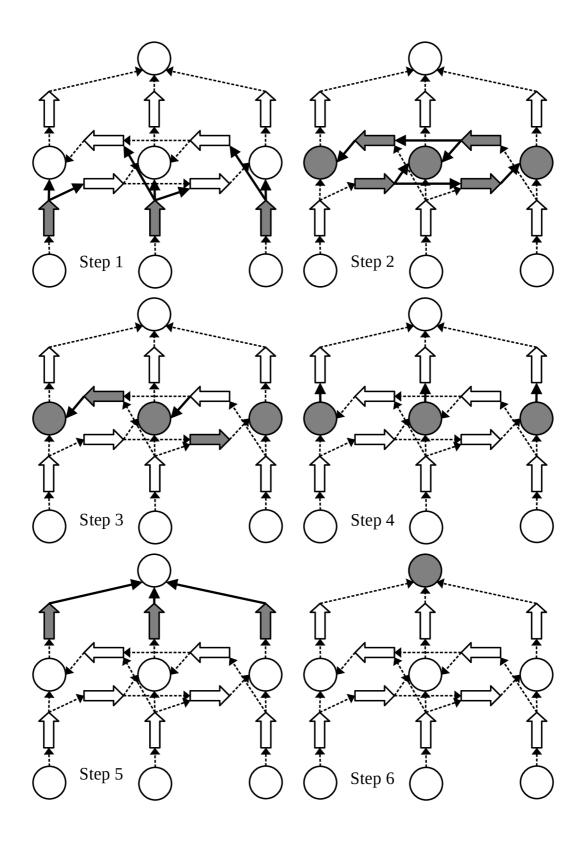

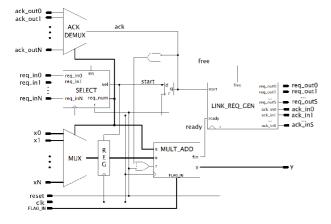

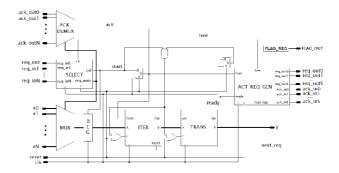

The neural resources are autonomous components that work with others in parallel, processing the data received from their predecessors (or the FPNN's input) and propagating their results to their successors. The communication between them is based on the request-acknowledgment model. When a neural resource finishes its current computation, it propagates the results to its output and generates a request for each of its successive connected resources (defined by its  $S_n$  and R-N flags). These requests notify each successor individually. However, the resources may already be busy processing other requests. Therefore, the original resource waits until all successors accept their requests and send back the corresponding acknowledgment. It only resumes the operation only after all acknowledgments are received. Then, it selects a request from its own input to process or wait until a new request comes.

The operation of a neural resource can be summarized in the following successive steps:

- 1. The neural resource selects one of the requests waiting on its input. If there are no pending requests, the neural resource waits for a new one to come.

- 2. The neural resource acknowledges the acceptance of the selected request to the request origin.

- 3. The neural resource processes the request:

- Link applies the affine operator  $\alpha$ .

- Activator applies an iteration operator  $i_n$ . Suppose the iteration counter equals  $a_n$ , indicating that this is the last supposed iteration, and all the necessary data from all the predecessors have been collected. In that case, the cumulative result of the iteration operator is presented to the function operator  $f_n$ , which computes the activation function. The iteration counter is reset. If this is not the last iteration yet, the computation returns to step 1.

- 4. The result of the computation is propagated to the neural resource's output, and requests for all successors are generated.

- 5. The neural resource waits until it receives acknowledgments for all generated requests.

- 6. Return to step 1.

The way a request is selected for processing in step 1 is essential. It is necessary the requests were selected in a way that ensures that all of them will be processed eventually and that the predecessors waiting for the acknowledgments will not be left waiting longer

than necessary. It is also necessary for activators to keep track of the number of iterations they have been through with the current data set to ensure that they work with the correct set and not with the data belonging to a successive set. Failing to do so would cause the entire FPNN result to be wrong, and it could also block the FPNN from processing the following data by breaking the synchronization. The recommended method of selection is Round&Robin.

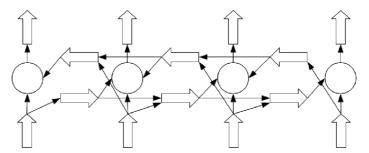

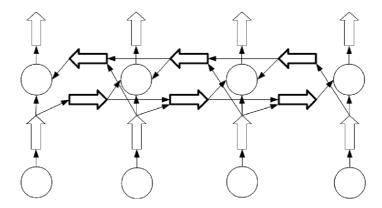

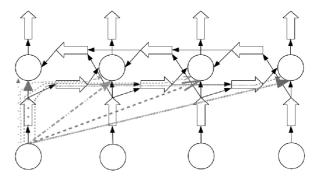

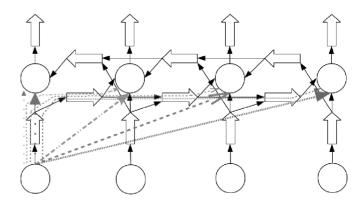

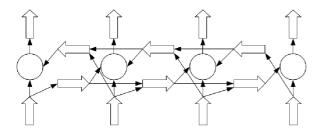

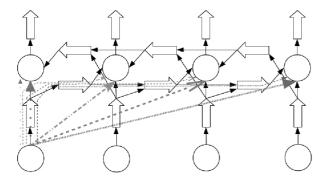

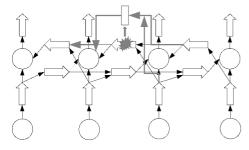

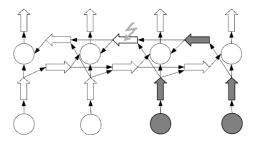

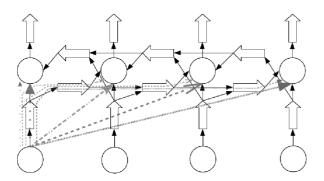

#### The grid structure

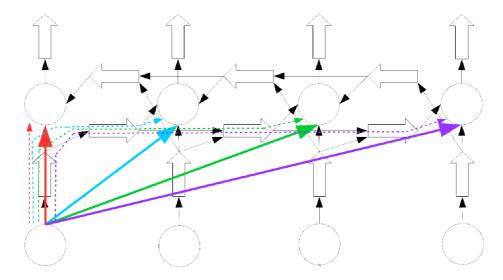

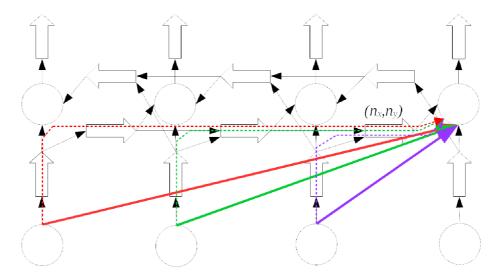

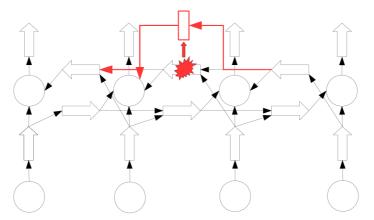

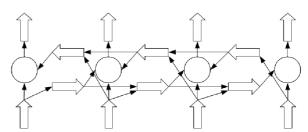

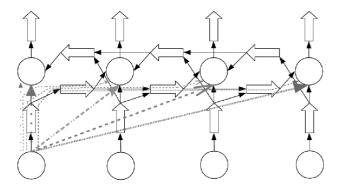

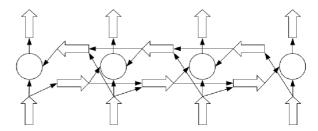

As we mentioned above, the purpose of FPNNs is to implement neural networks in gate arrays less resource-consuming way by sharing resources between synapses and by simplifying the interconnections. The primary tool to reach this goal is to shape the FPNN into a grid-like structure, illustrated in Fig. 4.2. In the figure, the wide arrows represent links. The thin arrows show the connections between neural resources. It can be seen that the connections are only local between close neural resources. This is to mitigate the need for long buses and complicated routing that would consume a lot of FPGA resources. The intended locality of connections is also why the synapses are broken in chains of several links - so that the entire FPNN would make the intended grid-like structure that would inherently keep the connections local and short.

Figure 4.1: A grid FPNN. Circles represent activators, wide arrows illustrate links and thin arrows show the way how the neural resources are connected to each other.