# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF MECHANICAL ENGINEERING

FAKULTA STROJNÍHO INŽENÝRSTVÍ

# INSTITUTE OF SOLID MECHANICS, MECHATRONICS AND BIOMECHANICS

ÚSTAV MECHANIKY TĚLES, MECHATRONIKY A BIOMECHANIKY

# **CONFIGURABLE SPI DEVICE**

KONFIGUROVATELNÉ SPI ZAŘÍZENÍ

MASTER'S THESIS DIPLOMOVÁ PRÁCE

AUTHOR AUTOR PRÁCE Bc. Pavol Ženčár

SUPERVISOR VEDOUCÍ PRÁCE doc. Ing. Jiří Krejsa, Ph.D.

**BRNO 2021**

# **Assignment Master's Thesis**

| Institut:        | Institute of Solid Mechanics, Mechatronics and Biomechanics |  |  |  |  |  |

|------------------|-------------------------------------------------------------|--|--|--|--|--|

| Student:         | Bc. Pavol Ženčár                                            |  |  |  |  |  |

| Degree programm: | Applied Sciences in Engineering                             |  |  |  |  |  |

| Branch:          | Mechatronics                                                |  |  |  |  |  |

| Supervisor:      | doc. Ing. Jiří Krejsa, Ph.D.                                |  |  |  |  |  |

| Academic year:   | 2020/21                                                     |  |  |  |  |  |

As provided for by the Act No. 111/98 Coll. on higher education institutions and the BUT Study and Examination Regulations, the director of the Institute hereby assigns the following topic of Master's Thesis:

### **Configurable SPI device**

#### **Brief Description:**

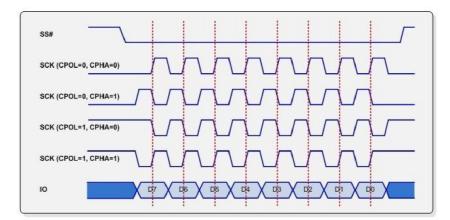

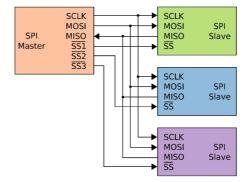

Serial peripheral interface (SPI) is a synchronous serial communication interface specification used for short–distance communication, primarily in embedded systems. For the purposes of development and testing of system containing SPI slave elements it is useful to have the possibility to simulate the behavior of real devices – for example the memory – and therefore invoke the behaviour of the whole system, which would be difficult to reach otherwise. The connection with PC and data presentation in appropriate software are inseparable parts of the thesis goal.

#### Master's Thesis goals:

- 1. Get acquainted with the properties of SPI and its variants.

- 2. Design the device that can simulate the behavior of SPI slave device that can be controlled and configured via USB.

- 3. Design proper method of real device behavior simulation.

- 4. Select existing device that supports SPI communication and prepare its virtual replacement.

- 5. Evaluate usability of proposed solution for different types of tasks, describe the device in question with respect to achievable data transfer speed.

#### Recommended bibliography:

AXELSON J., USB Complete: Everything You Need to Develop Custom USB Peripherals, Lakeview Research; 3rd Edition, 2005.

Deadline for submission Master's Thesis is given by the Schedule of the Academic year 2020/21

In Brno,

L. S.

prof. Ing. Jindřich Petruška, CSc. Director of the Institute doc. Ing. Jaroslav Katolický, Ph.D. FME dean

# Abstrakt

Táto práca sa zaoberá vývojom a testovaním konfigurovateľného SPI slave zariadenia, ktorého hlavným účelom je testovanie reálnych SPI master zariadení. Zariadenie je implementované pomocou STM32 mikrokontroléra na vývojovej doske NUCLEO. Medzi základné funkcionality zariadenia patrí meranie frekvencie SPI prenosu, stream mód, ktorý umožní presne sledovať, čo pripojené master zariadenie posiela po SPI zbernici a LUT mód, ktorý umožňuje nakonfigurovať zariadenie tak, aby odpovedalo prednastavenými odpoveďami na aktuálnu príchodziu správu. Rozšírená funkcionalita sa skladá z EEPROM emulátor módu. V tomto móde sa zariadenia správa ako virtuálna náhrada reálneho EEPROM zariadenia. Zariadenie je pripojené k počítaču pomocou sériového portu a je možné toto zariadenie konfigurovať pomocou python programáterského rozhrania. Zariadenie taktiež hlási každú aktivitu na SPI zbernici tomuto python programátorskému rozhraniu.

# Summary

This thesis deals with the development and testing of a configurable SPI slave device, the main purpose of which is to test real SPI master devices. The device is implemented using STM32 microcontroller on NUCLEO development board. The basic functionalities of the device include measuring frequency of the SPI transmission, stream mode, which allows the user to accurately monitor what the connected master device is transmitting over the SPI interface, and LUT mode, which allows the user to configure the device to respond with preset responses according to the current incoming message. More advanced functionality consists of an EEPROM emulator mode. In this mode, the device behaves as a virtual replacement of a real EEPROM device. The device is connected to a personal computer using a serial port and it is possible to configure the device using a python programming interface.

# Klíčová slova

SPI, mikrokontrolér, EEPROM pamäť, DMA

# Keywords

SPI, microcontroler, EEPROM memory, DMA

# **Bibliographic citation**

ŽENČÁR, P. *Configurable SPI device*. Brno: Brno University of Technology, Faculty of Mechanical Engineering, 2021. 122 pages, Master's thesis supervisor: doc. Ing. Jiří Krejsa, PhD..

# Rozšírený abstrakt

# Motivácia

SPI slave zariadenia sú vo väčšine prípadov rôzne typy senzorov. Preto počas vývinu ľubovoĺného produktu, ktorý používa senzory, je dosť pravdepodobné, že vývojár bude musieť vyvinúť SPI master zariadenie, ktoré je spojené s týmito SPI slave senzormi. Jediný reálny spôsob ako otestovať tieto SPI master zariadenia je použiť logický analyzér, pretože vývojár nemá prístup do SPI slave zariadení a nemôže sa "pozrieť dovnútra" pomocou debugging softvéru alebo niečoho podobného. Testovanie logickým analyzérom má svoje limitácie. Pomocou logického analyzéra je možné presne sledovať, čo sa deje na SPI signálových zberniciach, ale hociaká logika zariadenia nemôže byť otestovaná. Aby bolo možné otestovať logiku SPI master zariadenia, je potrebné použiť iné SPI slave zariadenie. Cieľom tejto práce je vyvinúť toto SPI slave zariadenie, s ktorým je možné testovať SPI master zariadenia. Bolo by užitočné, aby toto zariadenie bolo možné jednoducho nakonfigurovať tak, aby základná logika a funkcionalita SPI master zariadení mohla byť otestovaná.

Na detailné testovanie SPI master zariadenia, ktoré slúži na ovládanie jedného konkrétneho SPI slave zariadenia je potrebné simulovať chovanie reálneho SPI slave zariadenia podrobnejšie a ideálne je potreba vytvoriť jeho model, ktorý ma podobné až identické chovanie ako reálne zariadenie. Tento model nie je možné vytvoriť univerzálnym spôsobom aby zahŕňal všetky SPI slave zariadenia, preto bolo vybrané jedno reálne SPI slave zariadenie a bol vytvorený model tohto zariadenia. Účel tohto modelu je taký, aby tento model mohol byť považovaný za virtuálnu náhradu reálneho SPI slave zariadenia, ktorá má rovnaké správanie ako reálne zariadenie, môže byť konfigurovateľná a je možné sledovať, čo sa aktuálne deje vo vnútri tohto zariadenia. Tento model môže byť použitý na vývoj SPI master zariadenia, keď reálne SPI slave zariadenie je ťažko dostupné.

# Ciele

Cieľom tejto práce je vytvoriť zariadenie, ktoré sa bude chovať ako generické SPI slave zariadenie. Je potrebné vyvinúť metódy, s ktorými bude možné nasimulovať najzákladnejšie SPI slave funkcionality s jednoduchou konfiguráciou. Ďalší cieľ je vybrať jedno reálne SPI slave zariadenie a rozšíriť vytvorené SPI slave zariadenie o funkcionalitu, ktorá bude simulovať vybrané reálne SPI slave zariadenie. Vytvorené SPI slave zariadenie by malo byť konfigurovatelné pomocou programovacieho rozhrania v preferovanom programovacom jazyku.

# Zhrnutie a popis riešenia

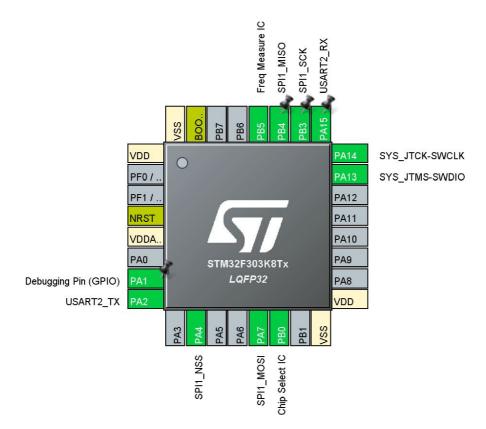

Hlavný cieľ tejto práce je vyvinúť testovacie zariadenie pre SPI master zariadenia. Toto testovacie zariadenie by malo mať univerzálne testovacie schopnosti a taktiež schopnosti emulovať jedno konkrétne reálne SPI slave zariadenie. STM32F303K8 mikrokontrolér bol vybraný ako platforma zariadenia. Bola použitá NUCLEO vývojová doska s vybraným mikrokontrolérom. Hlavná charakteristika tohto zariadenia je, že toto zariadenie

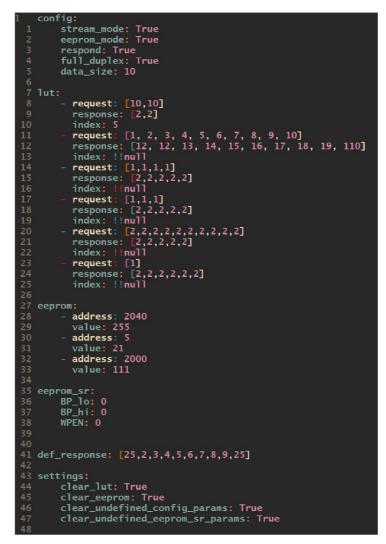

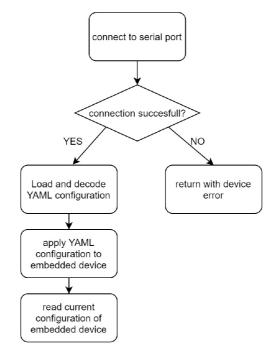

musí byť konfigurovatelné pomocou počítača. Tým pádom je toto zariadenie pripojené k počítačovému sériovému portu pomocou UART rozhrania. ST-LINK, ktorý obsahuje NU-CLEO vývojová doska je použitý ako USB-UART adaptér. Bolo vytvorené python API a toto API vie komunikovať s embedded zariadením. Hlavná úloha API je aplikovať konfiguráciu na zariadenie a taktiež príjmať informačné a potvrdzovacie správy z embedded zariadenia. Potvrdzovacie správy musia byť príjmuté za každým príkazom a musia obsahovať informácie o danom príkaze, inak príkaz nie je validný. Prenosy medzi embedded zariadením a počítačom obsahujú CRC číslo, ktoré je použité na zistenie chýb prenosu. YAML súbor je podporovaný z dôvodu jednoduchého formátu konfigurácie. Tento YAML súbor je vytvorený uživaťelom a presne špecifikuje zvolenú konfiguráciu. Konfigurácia z YAML súboru je aplikovaná na zariadenie v momente úspešného pripojenia zariadenia k python API.

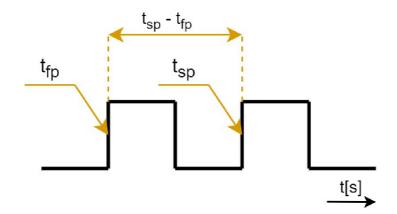

Predtým ako boli vyvinuté metódy, ktoré testujú logiku SPI master zariadenia, bola vyvinutá funkcionalita, ktorá dokáže merať frekvenciu SPI hodinového signálu. Frekvencia sa meria pomocou časovača, ktorý zachytáva momenty stúpajúcich hrán hodinového signálu. Ak sú známe momenty stúpajúcich hrán signálu, je možné spočítať periódu tohto signálu a tým pádom aj frekvenciu. Frekvencia sa vypočíta viackrát a výsledná frekvencia je určená ako módus týchto meraní. Frekvenciu SPI hodinového signálu je možné merať s dostačujúcim rozlíšením.

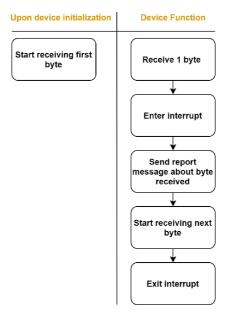

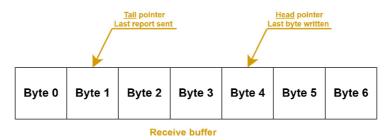

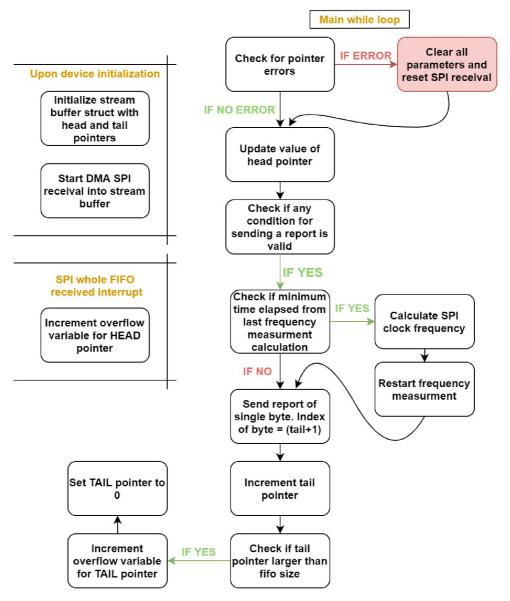

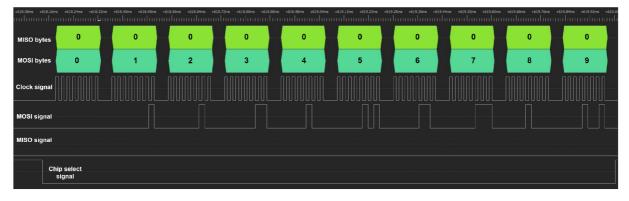

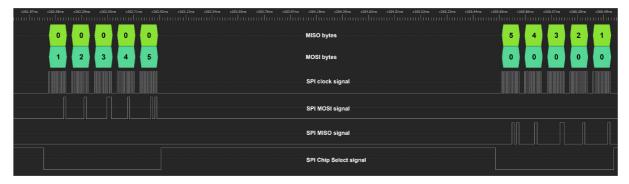

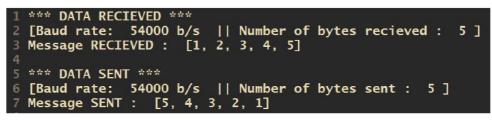

Prvým módom, ktorý testuje logiku SPI master zariadenia je tzv. stream mód. V stream móde sa žiadne dáta neposielajú zo slave zariadenia, ale dáta sú len príjmané. Hlavným účelom stream módu je preposielať každý prijatý byte SPI rozhraním priamo do python API. Nejaké problémy vznikli z dôvodu rozdielu rýchlostí SPI a UART rozhraní, ale väčšina problémov bola vyriešená pomocou kruhového buffru s "head" a "tail" pointermi. Použitím tohto buffru sa zaručilo, že preposielanie prijatých bytov sa uskutočnuje asynchrónne od momentu prijatia daného bytu SPI rozhraním a taktiež, že všetky byty sú poslané a žiadny byte nie je stratený.

Dalšia metóda testovania základnej logiky SPI mastra je LUT (Look Up Table) mód. Tento mód dovoluje uživatelovi definovat LUT páry. Jeden LUT pár obsahuje žiadosť, ktorá bude prijatá SPI rozhraním od SPI mastra a odpoveď, ktorá bude poslaná z SPI slave zariadenia podľa toho, aká žiadosť bola prijatá. Tento mód vie fungovať buď v obojsmernom alebo jednosmernom móde.

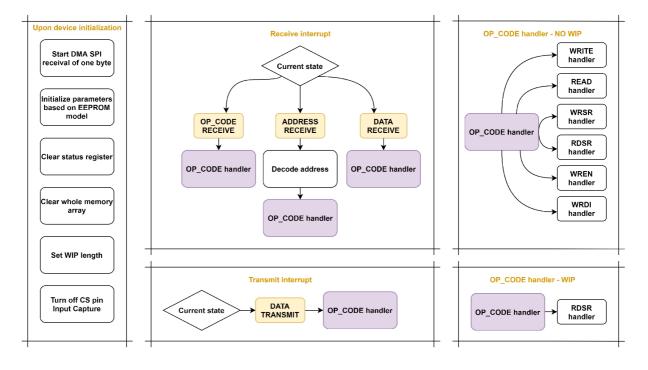

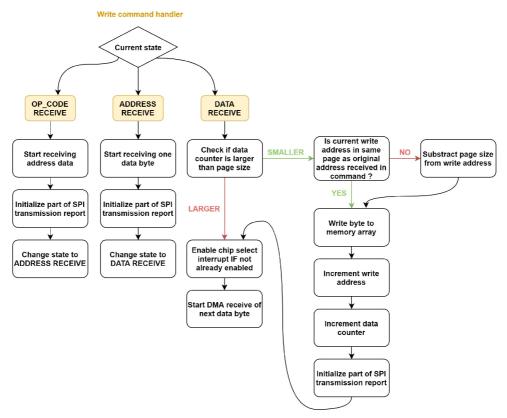

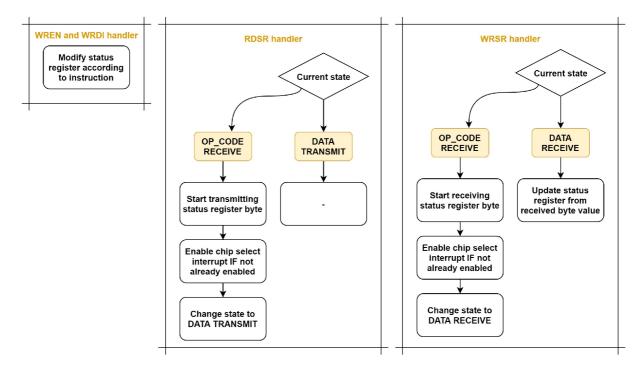

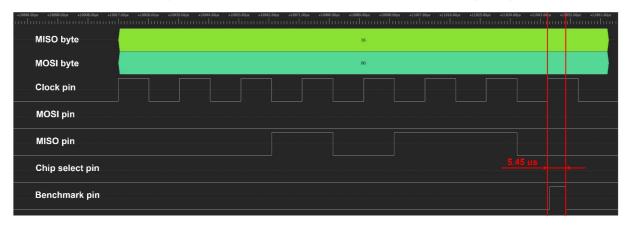

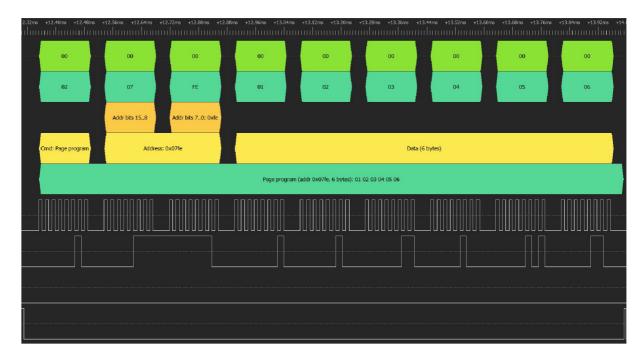

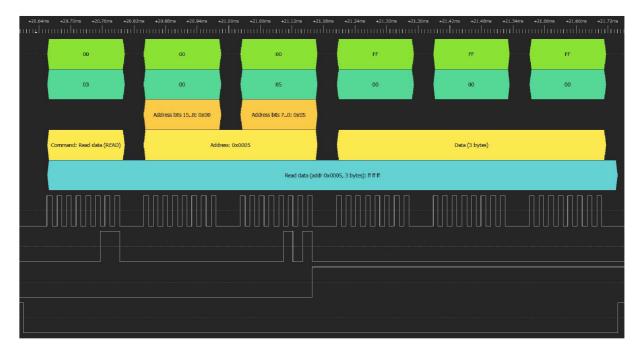

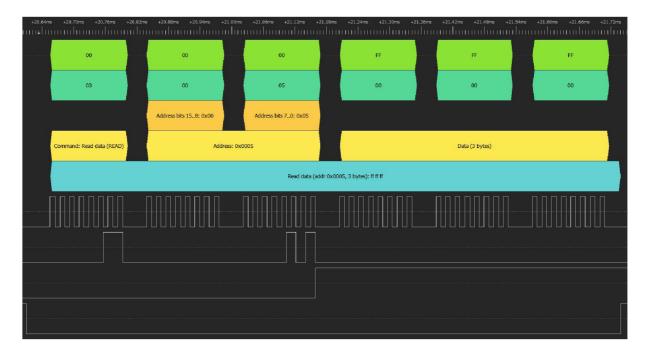

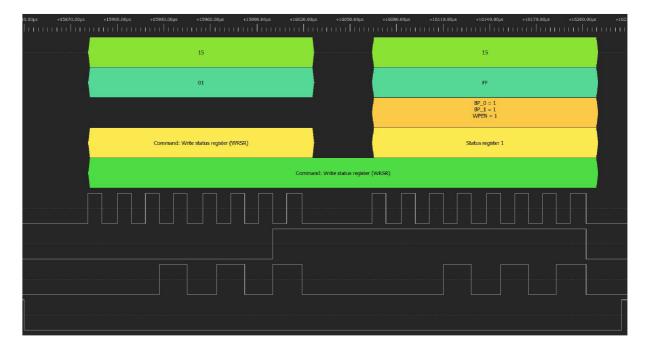

Na detailnejšie testovanie špecifického SPI mastra bolo vybrané jedno reálne SPI slave zariadenie a bol vyvinutý jeho emulátor. SPI EEPROM pamäť bola vybraná ako preferované reálne zariadenie. Emulátor bol vyvinutý a ten presne emuluje logické správanie daného reálneho SPI slave zariadenia. Jedna významná limitácia tohto emulátor zariadenia je, že maximálna frekvencia SPI rozhrania emulátora je výrazne menšia ako maximálna frekvencia SPI rozhrania reálneho zariadenia. Táto limitácia je spôsobená tým, že všetka vnútorná logika emulátora je riešená vo vnútri interruptov. Táto limitácia nie je braná ako závažný problém, pretože vyvinuté zariadenie je považované za prototyp. V budúcom vývoji bude použitý oveľa rýchlejší mikrokontrolér, čo výrazne zlepší problémovú situáciu. Taktiež pri meraní tejto limitácie bol predpokladaný nepretržitý "bit stream", čo znamená rovnaké časy medzi bytami ako medzi bitmi. Nepretržitý bit stream je v realite nepravdepodobný a preto skutočná maximálna frekvencia SPI rozhrania je výrazne vyššia.

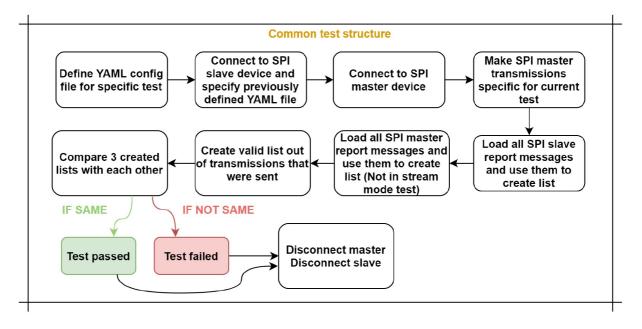

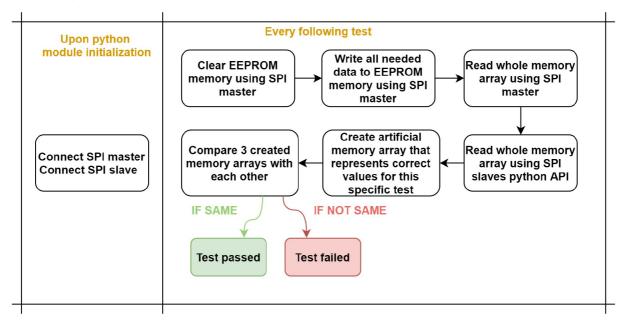

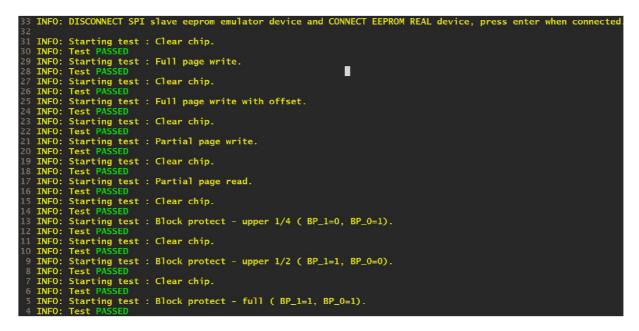

Následne boli vyvinuté verifikačné testy a každá funkcionalita bola overená týmito testami. Výsledky testov boli úspešné a všetky funkcionality fungujú tak ako majú.

## Zhodnotenie výsledkov

Všetky dané ciele boli dosiahnuté a v niektorých prípadoch prekročené. Výsledok tejto práce je zariadenie, ktoré môže byť použité na testovanie existujúcich SPI master zariadení. Je možné otestovať univerzálne SPI master zariadenia pomocou stream a LUT módu a taktiež je možné otestovať špecifické SPI EEPROM master zariadenie EEPROM emulátor módom. Zariadenie je možné konfigurovať pomocou python API.

V budúcom vývoji je možné uplatniť pár vylepšení. Jedno výrazné vylepšenie pre stream mód by bolo modifikovať proces posielania informačných správ. Momentálne jedna správa obsahuje len jeden prijatý byte. Efektívnejšie riešenie by bolo, keby jedna správa obsahovala všetky byty, ktoré neboli doposiaľ poslané. Plán pre EEPROM emulátor mód je pridať podporu pre viac EEPROM zariadení, ideálne vyvinúť nejakú metódu ako jednoducho definovať univerzálne EEPROM zariadenie.

I hereby declare that except where specific reference is made to the work of others, the contents of this thesis are original and that this master's thesis is my own work and contains nothing which is the outcome of work done in collaboration with others.

### Pavol Ženčár

Brno . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

First of all, I would like to thank my supervisor doc. Ing. Jiří Krejsa, PhD. for the great support, motivation and insightful comments. I also would like to thank Jakub Lešinský for all his help, motivation, knowledge and patience while answering all my questions. Last but not the least, I would like to thank my family for support.

Pavol Ženčár

# Contents

| 1        | Intr              | oductio        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------|-------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | 1.1               | Motiva         | tion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $13$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|          | 1.2               | Goals .        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| <b>2</b> | Res               | earch          | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| -        | 2.1               |                | ng solutions $\ldots \ldots 14$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|          | 2.2               |                | $controllers \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

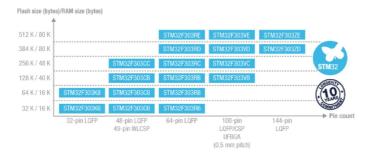

|          |                   | 2.2.1          | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|          |                   | 2.2.2          | $Main usage \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|          |                   | 2.2.3          | Common types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|          |                   | 2.2.0<br>2.2.4 | $Interrupts \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|          |                   | 2.2.1<br>2.2.5 | $Timer  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|          |                   | 2.2.6          | DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|          | 2.3               |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          | $\frac{2.0}{2.4}$ |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          | $2.4 \\ 2.5$      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          | 2.6               |                | OM memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|          | 2.0               |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 3        | Det               | ailed g        | oals description 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| <b>4</b> | Har               | dware          | selection and setup 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|          | 4.1               |                | controller selection $\ldots \ldots 27$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|          | 4.2               | PC con         | nnection $\ldots \ldots 29$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

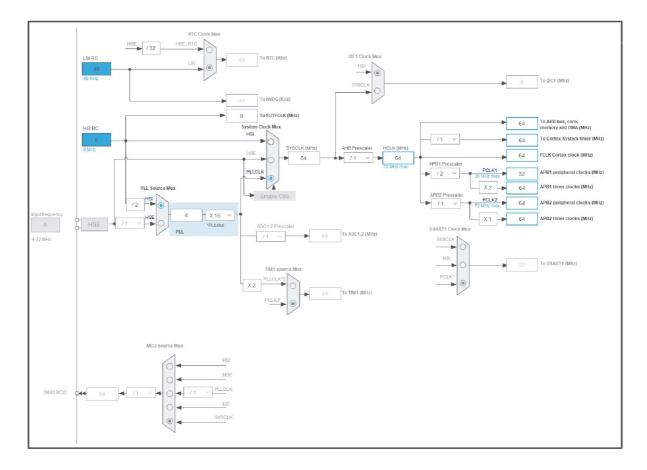

|          | 4.3               | MCU s          | setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| _        | Б                 |                | ce functionality 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| <b>5</b> |                   |                | ice functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|          | 5.1               |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          | 5.2               |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          | 5.3               | -              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          |                   | 5.3.1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          |                   | 5.3.2          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          |                   | 5.3.3          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

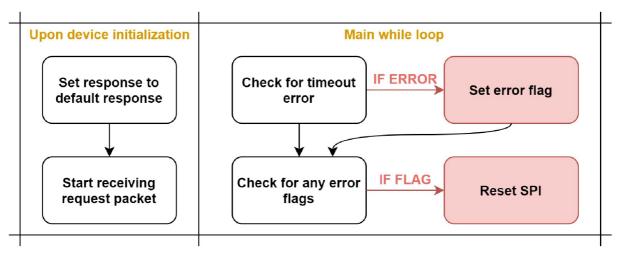

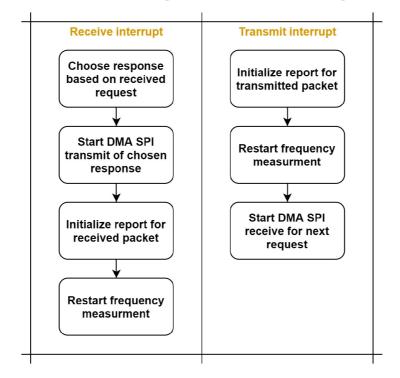

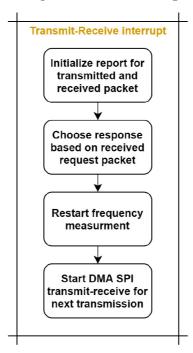

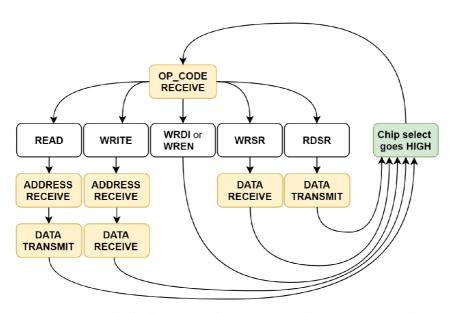

|          |                   | 5.3.4          | Receive interrupt indicated a set of the test of t |  |