# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

### DEPARTMENT OF RADIO ELECTRONICS

ÚSTAV RADIOELEKTRONIKY

# PARALLELISM IN DIGITAL SIGNAL PROCESSING

PARALELISMUS V ČÍSLICOVÉM ZPRACOVÁNÍ SIGNÁLŮ

#### **DOCTORAL THESIS**

DIZERTAČNÍ PRÁCE

AUTHOR Ing. Roman Mego AUTOR PRÁCE

SUPERVISOR doc. Ing. Tomáš Frýza, Ph.D. ŠKOLITEL

**BRNO 2020**

#### **Abstract**

The doctoral thesis is focused on the systems for digital signal processing, its architecture and possibilities of software development. The text discussed the basic classification of computer systems from the view of parallel processing. It also demonstrates the behavior of the low-level and high-level programming languages on the multicore digital signal processors based on VLIW architecture. The aim of the dissertation thesis is to develop a tool that can be used to implement any DSP algorithm on the any VLIW processor with efficiency of the low-level programming languages, but with the advantages of the high-level programming languages. Result is the software that uses a signal-flow graph approach to describe an algorithm, and generates the low-level assembly code.

#### **Keywords**

digital signal processing, VLIW architecture, software development, signal-flow graph

#### **Abstrakt**

Dizertační práce je zaměřena na systémy pro číslicové zpracování signálů, jejich architekturu a možnosti vývoje softwaru. Text pojednává o základním rozdělení počítačových systémů z hlediska paralelního zpracování dat. Rovněž demonstruje chování nízkoúrovňových a vysokoúrovňových programovacích jazyků na vícejadrovém signálovém procesoru založeném na architektuře VLIW. Cílem dizertační práce je vytvořit nástroj, který může být použitý při implementaci DSP algoritmů na VLIW procesory s efektivností nízkoúrovňových programovacích jazyků, s výhodami ale vysokoúrovňových programovacích jazyků. Výsledkem je software, který využívá pro popis algoritmů graf signálových toků a generuje kód v jazyce symbolických adres.

#### Klíčová slova

digitální zpracování signálů, VLIW architektura, vývoj softwaru, graf signálových toků

Mego, Roman. Parallelism in digital signal processing: doctoral thesis. Brno: Brno University of Technology, Faculty of Electrical Engineering and Communication, Department of Radio Electronics. 2020. Supervised by doc. Ing. Tomáš Frýza, Ph.D.

### **Declaration**

I declare that I have written my doctoral thesis on the theme of Parallelism in digital signal processing independently, under the guidance of the doctoral thesis supervisor and using the technical literature and other sources of information which are all quoted in the thesis and detailed in the list of literature at the end of the thesis.

As the author of the doctoral thesis I furthermore declare that, as regards the creation of this doctoral thesis, I have not infringed any copyright. In particular, I have not unlawfully encroached on anyone's personal and/or ownership rights and I am fully aware of the consequences in the case of breaking Regulation § 11 and the following of the Copyright Act No. 121/2000 Sb., and of the rights related to intellectual property right and changes in some Acts (Intellectual Property Act) and formulated in later regulations, inclusive of the possible consequences resulting from the provisions of Criminal Act No. 40/2009 Sb., Section 2, Head VI, Part 4.

| Brno, 19. August 2020 |                    |

|-----------------------|--------------------|

|                       | Author's signature |

# **Contents**

|         | Introduction                                                              | 1  |

|---------|---------------------------------------------------------------------------|----|

| 1       | State of the art                                                          | 2  |

| 1.1     | System classification                                                     | 2  |

| 1.1.1   | Single instruction, single data (SISD)                                    | 2  |

| 1.1.2   | Single instruction, multiple data (SIMD)                                  | 3  |

| 1.1.3   | Multiple instructions, single data (MISD)                                 | 3  |

| 1.1.4   | Multiple instructions, multiple data (MIMD)                               | 4  |

| 1.2     | Individual cases of processor architectures                               | 4  |

| 1.2.1   | Scalar central processing units (CPU) and digital signal processors (DSP) | 4  |

| 1.2.2   | Graphics processing units (GPU)                                           | 6  |

| 1.2.3   | Very long instruction word (VLIW)                                         | 6  |

| 1.2.4   | Multicore systems with shared memory                                      | 7  |

| 1.2.5   | Multicore systems with distributed memory                                 | 8  |

| 1.2.6   | Multicore systems with hybrid distributed-shared memory                   | 8  |

| 1.3     | Programming methods                                                       | 9  |

| 1.3.1   | Low-level languages                                                       | 9  |

| 1.3.2   | High-level languages                                                      | 10 |

| 1.3.2.1 | Difference between compiled and interpreted languages                     | 11 |

| 1.4     | Standard optimization methods                                             | 11 |

| 1.4.1   | Redundancy elimination                                                    | 12 |

| 1.4.2   | Constant propagation optimization                                         | 12 |

| 1.4.3   | Useless code elimination                                                  | 13 |

| 1.4.4   | Inline expansion                                                          | 13 |

| 2       | The objectives of the dissertation thesis                                 | 15 |

| 3       | Effectiveness of software development tools                               | 16 |

| 3.1     | Multicore DSP TMS320C6678                                                 | 16 |

| 3.1.1   | TMDSEVM6678LE Development Board                                           | 17 |

| 3.2     | Test cases                                                                | 18 |

| 3.2.1   | Data and thread parallelism using OpenMP                                  | 18 |

| 3.2.1.1 | Section work-sharing                                                      | 18 |

| 3.2.1.2 | Loop work-sharing                                                         | 19 |

| 3.2.2   | Algorithm parallelization in OpenMP                                       |    |

| 3.2.2.1 | FIR filter                                                                |    |

| 3.2.2.2 | Discrete Fourier transform                                                | 20 |

| 3.2.2.3 | Fast Fourier transform                                                    | 20 |

| 323     | Measured performance of OpenMP                                            | 21 |

| 3.2.4   | Low-level optimizations of the algorithms on the VLIW architecture | 24 |

|---------|--------------------------------------------------------------------|----|

| 3.2.5   | High-level and low-level comparison                                | 25 |

| 3.2.5.1 | Low-level assembly                                                 | 25 |

| 3.2.5.2 | Linear assembly                                                    | 26 |

| 3.2.5.3 | High-level language                                                | 27 |

| 3.2.6   | Comparison of the libraries with different structure               | 28 |

| 3.3     | Chapter summary                                                    | 29 |

| 4       | Impact of the software efficiency to the power consumption         | 30 |

| 4.1     | Theoretical power consumption increase on multi-unit systems       | 30 |

| 4.2     | Practical test cases                                               | 31 |

| 4.2.1   | Case 1: Empty loop                                                 | 31 |

| 4.2.2   | Case 2: Load/Store operations                                      | 32 |

| 4.2.3   | Case 3: Fixed-point operations                                     | 32 |

| 4.2.4   | Case 4: Floating-point operations                                  | 33 |

| 4.2.5   | Case 5: FFT routines                                               | 33 |

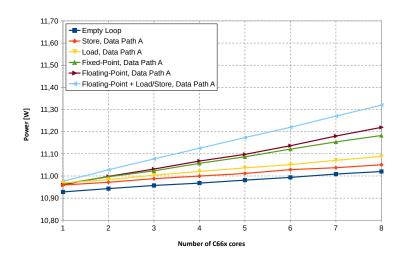

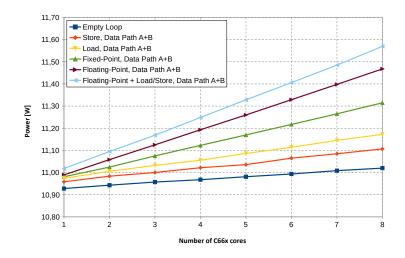

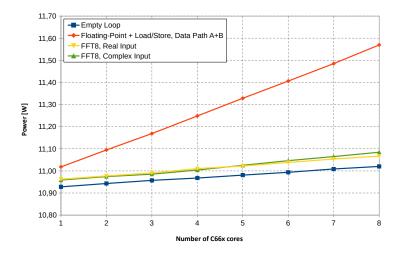

| 4.3     | Experimental Results                                               | 34 |

| 4.4     | Chapter summary                                                    | 37 |

| 5       | Instruction mapping tool for DSPs                                  | 38 |

| 5.1     | The idea of signal-flow graph approach                             | 38 |

| 5.2     | Input files                                                        | 39 |

| 5.2.1   | Architecture definition                                            | 39 |

| 5.2.1.1 | Hardware resources                                                 | 40 |

| 5.2.1.2 | Instruction set                                                    | 44 |

| 5.2.2   | Algorithm description                                              | 47 |

| 5.3     | Algorithm mapping                                                  | 48 |

| 5.3.1   | Input files parsing                                                | 49 |

| 5.3.1.1 | Parsing signals                                                    | 49 |

| 5.3.1.2 | Parsing nodes.                                                     | 50 |

| 5.3.1.3 | Multi-operation nodes                                              | 52 |

| 5.3.2   | Finding relations and validation                                   | 53 |

| 5.3.2.1 | Extending nodes and signals information                            | 53 |

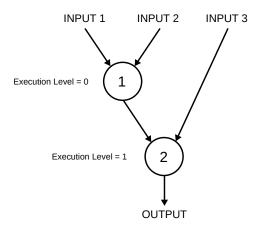

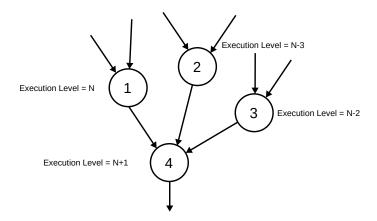

| 5.3.2.2 | Determining execution order                                        | 53 |

| 5.3.3   | Node sorting                                                       | 55 |

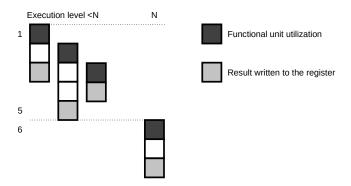

| 5.3.3.1 | Sorting according to execution level                               | 56 |

| 5.3.3.2 | Sorting according to the total CPU cycles of the operation         | 56 |

| 5.3.3.3 | Sorting according to number of supported functional units          | 56 |

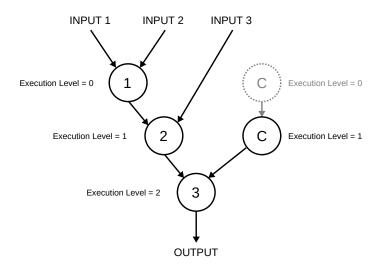

| 5.3.3.4 | Handling constant loading                                          | 57 |

| 5.3.4   | Functional unit allocation                                         | 57 |

| 5.3.4.1 | Finding start cycle of the execution                               |    |

| 5.3.4.2 | Allocation                                                         | 58 |

| 5.3.5   | Signal allocation                   | 59 |

|---------|-------------------------------------|----|

| 5.4     | Implementation                      | 60 |

| 5.4.1   | Build environment                   | 62 |

| 5.5     | Chapter summary                     | 62 |

| 6       | Experimental results                | 64 |

| 6.1     | Basic behavior of algorithm mapping | 64 |

| 6.1.1   | Values prepared in registers        | 64 |

| 6.1.1.1 | Fast Fourier Transform              | 64 |

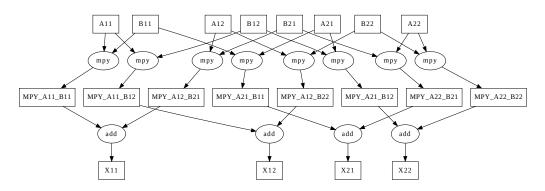

| 6.1.1.2 | Matrix multiplication               | 71 |

| 6.1.2   | Values stored in memory             | 74 |

| 6.1.2.1 | Fast Fourier Transform              | 74 |

| 6.1.2.2 | Matrix multiplication               | 77 |

| 6.2     | Optimization impact                 | 79 |

| 6.2.1   | Node priority                       | 79 |

| 6.2.2   | Functional unit priority            | 80 |

| 6.3     | Comparison to other methods         | 82 |

| 6.4     | Chapter summary                     |    |

| 7       | Conclusion                          | 84 |

# **List of figures**

| Figure 1.1: SISD arrangement                                                        | 2  |

|-------------------------------------------------------------------------------------|----|

| Figure 1.2: SIMD arrangement                                                        | 3  |

| Figure 1.3: MISD arrangement                                                        | 3  |

| Figure 1.4: MIMD arrangement                                                        | 4  |

| Figure 1.5: CPU (left) and GPU (right) difference                                   | 6  |

| Figure 1.6: Superscalar (top) and VLIW (bottom) difference                          | 7  |

| Figure 1.7: Shared memory system                                                    | 8  |

| Figure 1.8: Distributed memory system                                               | 8  |

| Figure 1.9: Hybrid distributed-shared memory system                                 | 9  |

| Figure 1.10: Levels of the programming languages                                    | 9  |

| Figure 1.11: Example of common subexpression elimination                            | 12 |

| Figure 1.12: Example of copy propagation transform                                  | 12 |

| Figure 1.13: Example of constant folding                                            | 13 |

| Figure 1.14: Example of useless code elimination                                    | 13 |

| Figure 1.15: Example of dead code elimination                                       | 13 |

| Figure 1.16: Example of inline expansion                                            | 14 |

| Figure 1.17: Example of loop unrolling                                              | 14 |

| Figure 3.1: Example of section work sharing                                         | 19 |

| Figure 3.2: For-loop parallel execution                                             | 19 |

| Figure 3.3: FFT radix-2 with highlighted loop iterations                            | 21 |

| Figure 3.4: Relative speedup of FIR filter                                          | 22 |

| Figure 3.5: Relative speedup of DFT                                                 | 22 |

| Figure 3.6: Relative speedup of FFT                                                 | 23 |

| Figure 3.7: Hand-written assembly code                                              | 26 |

| Figure 3.8: Example of linear assembly code                                         | 26 |

| Figure 3.9: Disassembly of the algorithm written in linear assembly                 | 27 |

| Figure 3.10: Disassembly of the FFT algorithm written in C                          | 27 |

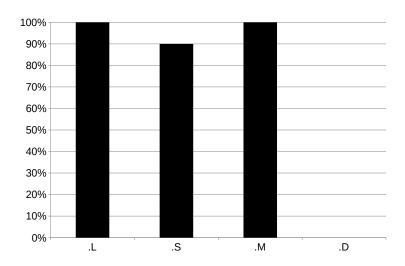

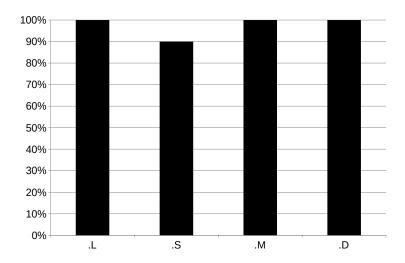

| Figure 4.1: Functional unit utilization for the case 1                              | 31 |

| Figure 4.2: Functional unit utilization for the case 2                              | 32 |

| Figure 4.3: Functional unit utilization for the case 3                              | 32 |

| Figure 4.4: Functional unit utilization for the case 4 without data loading/storing | 33 |

| Figure 4.5: Functional unit utilization for the case 4 with data loading/storing    | 33 |

| Figure 4.6: Functional unit utilization for the case 5                              | 34 |

| Figure 4.7: Workplace for the measuring the power consumption                       | 35 |

| Figure 4.8: Power consumption of theoretical test cases at data path A              | 35 |

| Figure 4.9: Power consumption of theoretical test cases at data paths A and B       | 36 |

| Figure 4.10: Power consumption of FFT routines at data paths A and B                | 36 |

| Figure 5.1: Structure of the TMS320C6678                                            | 39 |

| Figure 5.2: Basic structure of the JSON architecture file                               | 40 |

|-----------------------------------------------------------------------------------------|----|

| Figure 5.3: Structure of data path in JSON file                                         | 41 |

| Figure 5.4: Structure of cross-path in JSON file                                        | 42 |

| Figure 5.5: Example of the cross-path connection to the functional units                | 43 |

| Figure 5.6: Creating register groups from the physical registers                        | 44 |

| Figure 5.7: Structure of instruction in JSON file                                       | 45 |

| Figure 5.8: Execution progress of ADDDP instruction                                     | 45 |

| Figure 5.9: Signal-flow diagram from example algorithm                                  | 48 |

| Figure 5.10: Mapping process                                                            | 49 |

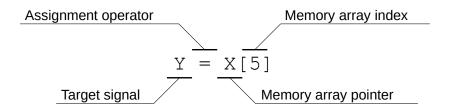

| Figure 5.11: Signal definition format                                                   | 49 |

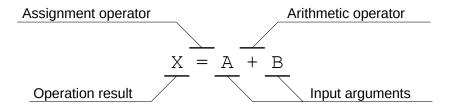

| Figure 5.12: Arithmetic operation format                                                | 51 |

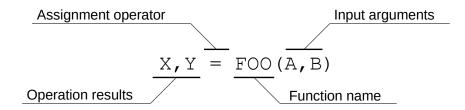

| Figure 5.13: Function definition format                                                 | 51 |

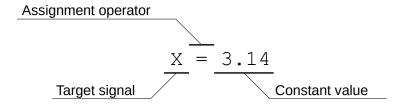

| Figure 5.14: Constant definition format                                                 | 52 |

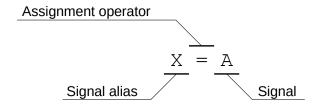

| Figure 5.15: Signal alias definition format                                             | 52 |

| Figure 5.16: Memory operation format                                                    | 52 |

| Figure 5.17: Determining execution level using input signals                            | 54 |

| Figure 5.18: Determining execution level using previous nodes                           | 55 |

| Figure 5.19: Determining execution level of constant loading                            | 55 |

| Figure 5.20: Instruction execution order based on CPU cycles                            | 56 |

| Figure 5.21: Instruction execution order based on number of supported functional units. | 57 |

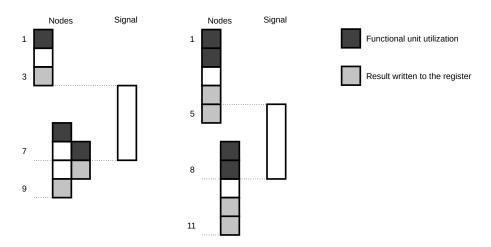

| Figure 5.22: Determining first possible CPU cycle for execution                         | 58 |

| Figure 5.23: Determining signal lifetime                                                | 59 |

| Figure 5.24: Mapping tool structure.                                                    | 60 |

| Figure 5.25: Architecture editor running under Linux and Windows system                 | 62 |

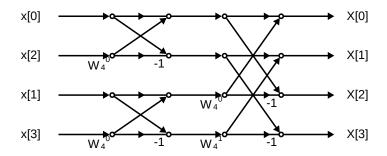

| Figure 6.1: 4-point FFT algorithm                                                       | 65 |

| Figure 6.2: Part of signal definition in the 4-point FFT implementation                 | 65 |

| Figure 6.3: Source code of the 4-point FFT (without signal definition)                  |    |

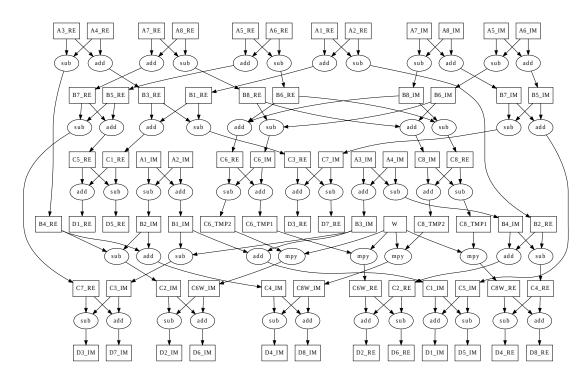

| Figure 6.4: Graphical representation of the 4-point FFT                                 | 66 |

| Figure 6.5: Generated source code for the 4-point FFT with fixed-point representation   | 66 |

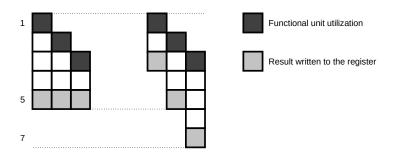

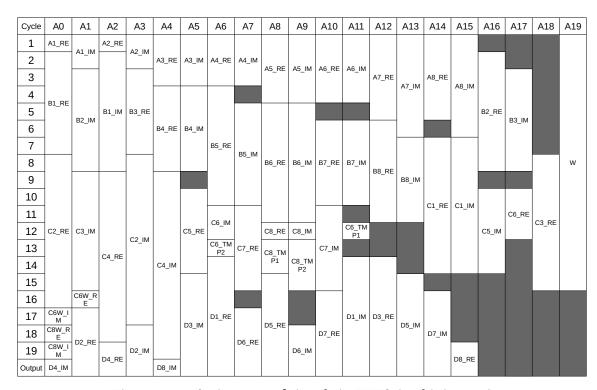

| Figure 6.6: Functional unit usage in FFT4 (32-bit integer)                              | 67 |

| Figure 6.7: Assignment of signals in FFT4 (32-bit integer)                              | 67 |

| Figure 6.8: Functional unit usage in FFT4 (single precision floating-point)             | 68 |

| Figure 6.9: Assignment of signals in FFT4 (single precision floating-point)             | 68 |

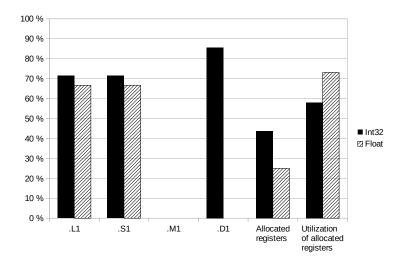

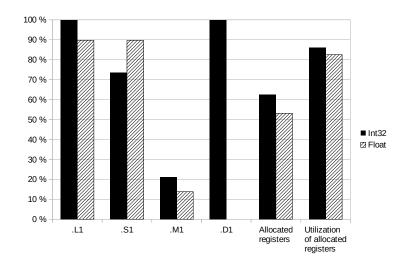

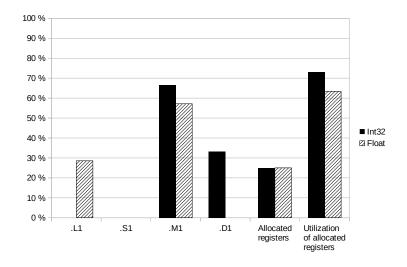

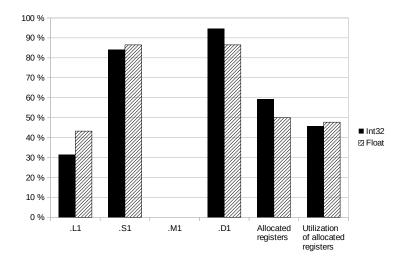

| Figure 6.10: Resource utilization of the 4-point FFT                                    |    |

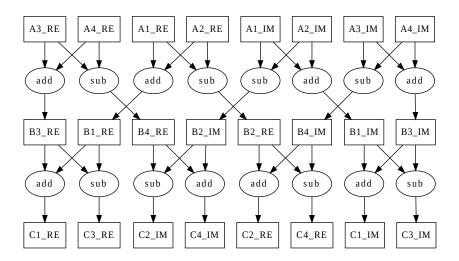

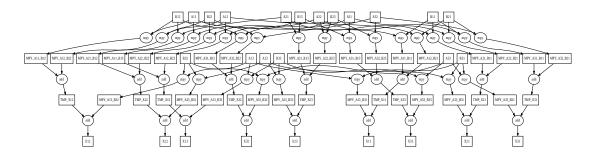

| Figure 6.11: Graphical representation of 8-point FFT                                    |    |

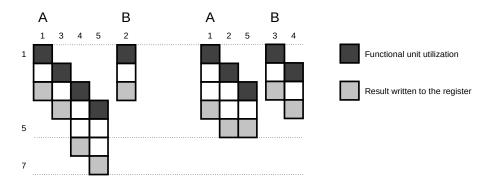

| Figure 6.12: Usage of functional units in FFT8 (32-bit integer)                         |    |

| Figure 6.13: Assignment of signals in FFT8 (32-bit integer)                             |    |

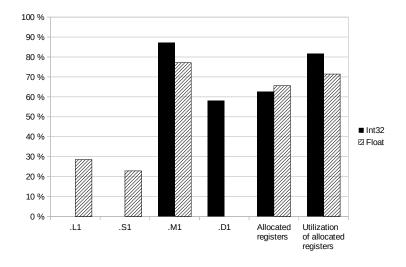

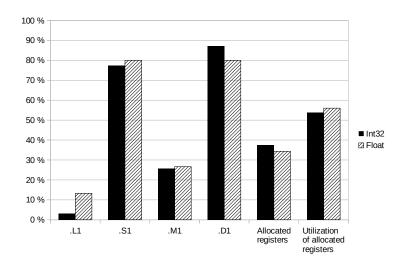

| Figure 6.14: Resource utilization of the 8-point FFT                                    |    |

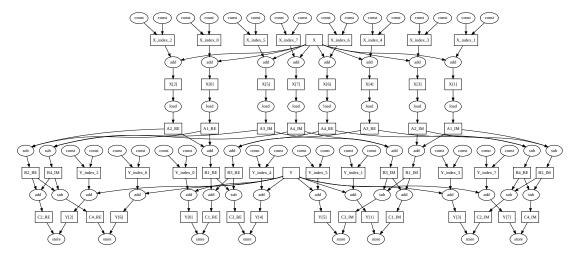

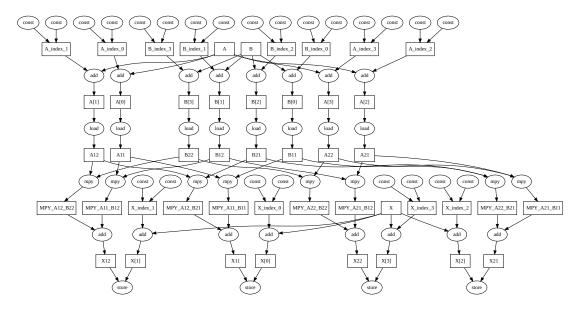

| Figure 6.15: Graphical representation of matrix multiplication 2x2                      | 72 |

| Figure 6.16: Resource utilization for the matrix 2x2 multiplication                     | 72 |

| Figure 6.17: Graphical representation of matrix multiplication 3x3                    | 73      |

|---------------------------------------------------------------------------------------|---------|

| Figure 6.18: Resource utilization for the matrix 3x3 multiplication                   | 73      |

| Figure 6.19: Difference of the input/output definition                                | 75      |

| Figure 6.20: Graphical representation of the 4-point FFT with memory operations       | 75      |

| Figure 6.21: Functional unit usage in FFT4 (32-bit integer, data in memory)           | 76      |

| Figure 6.22: Resource utilization of the 4-point FFT with memory operations           | 77      |

| Figure 6.23: Graphical representation of the 2x2 matrix multiplication (data in memo  | ry). 77 |

| Figure 6.24: Resource utilization for the matrix 2x2 multiplication (data in memory). | 79      |

# **List of tables**

| Table 3.1: Basic parameters of the TMS320C6678                                     | 17     |

|------------------------------------------------------------------------------------|--------|

| Table 3.2: Measured reference time                                                 | 21     |

| Table 3.3: Time needed to create parallel region                                   | 23     |

| Table 3.4: C implementation FFT performance                                        | 24     |

| Table 3.5: Low-level implementation FFT performance                                | 24     |

| Table 3.6: Relative speedup of the low-level FFT implementation                    | 25     |

| Table 3.7: Performance comparison of the different approach of the C libraries for | FFT28  |

| Table 5.1: Arithmetic instruction supported operations                             | 46     |

| Table 5.2: Arithmetic instruction supported data types                             | 46     |

| Table 5.3: Memory instruction supported operations                                 | 47     |

| Table 5.4: Signal definition roles                                                 | 50     |

| Table 5.5: Signal definition data types                                            | 50     |

| Table 5.6: Operators for arithmetic operations                                     | 51     |

| Table 6.1: Average hardware resources usage on selected algorithms                 | 74     |

| Table 6.2: Average hardware resources usage on selected algorithms (data in mem    | ory)78 |

| Table 6.3: Node priority mapping improvements (data in memory)                     | 80     |

| Table 6.4: Functional unit priority mapping improvements (data in memory)          | 81     |

| Table 6.5: Comparison of tool results with the standard methods                    | 82     |

# Introduction

The signal processing is the field of electrical engineering which is used for acquiring, modifying and evaluating signals using mathematics operations. In these days, it is used practically in every type of applications around us, such as multimedia, communication, medicine or industrial control. In the beginnings of the electronics, the signal processing was performed only with analogue circuits such as active or passive filters, additive mixers, integrators, derivators, voltage-controlled oscillators, phase-locked loops and so on. These circuits were able to provide enough resources to implement such complex systems like radars and television broadcasting.

Later in 1960s, the digital signal processing became the next field of electrical engineering and computer science. It was caused by availability of required hardware components. But this did not lead to the massive deployment of the applications, because the price of computers was quite limiting. The digital signal processing was used mainly in military, medical and research applications. In the 2000s, the hardware became inexpensive, so the digital signal processing replaced analogue circuits in the applications of everyday life.

Digital signal processing is the application of mathematics operations on discrete quantized signal. The algorithms can be implemented in general computer, digital signal processors or on specialized hardware based on field-programmable gate arrays (FPGA) and application-specific integrated circuits (ASIC). The system parameters are highly dependent on application purpose. The main advantages of the digital signal processing on programmable circuits over its analog equivalent are high accuracy, cheaper implementation of complex algorithms, wide offer of interfaces for data recording and its easy modification without touching the electrical connection. The last advantage leads to the software which is one of the key aspects of the final performance.

This dissertation thesis is focused on software part of the digital signal processing applications, especially on parallel architectures. The result will be a tool, that help to optimize the software with generated parts in the assembly language. The first part of thesis shows the overview of the architectures that can be used on data processing and methods of the programming. The second part demonstrates the behavior of various methods of creating software, especially on multicore very long instruction word (VLIW) processor, and its impact on the application performance. The last part introduces the tool for instruction mapping suitable for creating cores of digital signal processing algorithm cores.

# 1 State of the art

There are many options how to realize digital processing in these days. Every realization is made of the hardware part and the software part. This chapter is dealing with the hardware resources for digital processing and the possibilities of creating the software.

# 1.1 System classification

One of the most known classifications of the computer architectures is the Flynn's taxonomy [1]. This classification is based on the number of concurrent instructions and data streams. The processors can be divided according to Flynn's taxonomy into the following groups:

- Single instruction, single data (SISD)

- Single instruction, multiple data (SIMD)

- Multiple instructions, single data (MISD)

- Multiple instructions, multiple data (MIMD)

#### 1.1.1 Single instruction, single data (SISD)

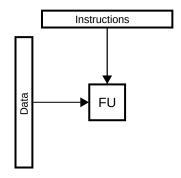

The first group of the Flynn's taxonomy is SISD. Systems belonging to this group are the simplest. They can process only one instruction in one instruction cycle. They also are not able to process multiple data at once, so there is no parallelism (Figure 1.1) [2]. This group might include classic scalar architectures such as complex instruction set computers (CISC) [3] or reduced instruction set computers (RISC) [4]. The advantage is the simplicity of implementation, which requires only one functional unit (FU), and low requirements in software design.

Figure 1.1: SISD arrangement

#### 1.1.2 Single instruction, multiple data (SIMD)

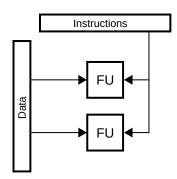

The next group of the Flynn's taxonomy is SIMD. These systems are able to handle larger amount of data with a single instruction (Figure 1.2) [2]. Vector and matrix operations are typical for this group, so the processors are sometimes called the vector processors. The example could be a processor based on the x86 architecture, which is SISD, but extended with the MMX instruction set [5]. The special subset if formed by graphics processing units (GPU). They are used in the homogeneous processing of large amount of data. The disadvantage is that the classic high-level programming languages, such as ANSI C, are not able to utilize the full potential. For this reason, the optimized libraries, special macros or the unusual programming languages are used.

Figure 1.2: SIMD arrangement

#### 1.1.3 Multiple instructions, single data (MISD)

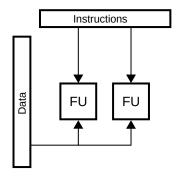

The systems from the MISD group are quite unusual. They are commonly used in special fault-tolerant applications. Data are processed on independent functional units and the results are compared. Data and instruction streams are shown in Figure 1.3 [2]. It reduces the chance of the errors. Except this feature, it provides no benefit like the increase of the computing power. Specific example from MISD group is IBM System/88 [6].

Figure 1.3: MISD arrangement

#### 1.1.4 Multiple instructions, multiple data (MIMD)

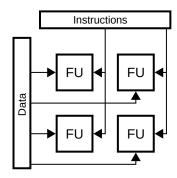

MIMD systems use several mutually independent functional units, which can handle different data (Figure 1.4) [2]. In practice, the majority of systems are made of multicore processors with shared or distributed memory. In this case, every processing unit has its own thread, which is not dependent on the others. It offers flexibility in the parallel processing of the data. This category also includes processors based on very long instruction word (VLIW). Core of the VLIW architecture consist of the multiple functional units, so it can execute multiple instructions in one instruction cycle.

Figure 1.4: MIMD arrangement

# 1.2 Individual cases of processor architectures

Some specific processor and computer architectures were mentioned in the description of Flynn's taxonomy, which can be used for the digital processing. The next text deals with these architectures.

# 1.2.1 Scalar central processing units (CPU) and digital signal processors (DSP)

Scalar processors have been used since the birth of the first computers until now. The program is executed sequentially in the order of instructions in the memory. The only options how to change its execution order are the branch instructions or the instructions for calling the subroutines. Over the time, there were made various requirements during its development. This has to led to expanding of the instruction set and thus to the increasing of the arithmetic logic unit (ALU). After some time, it was found that most of the applications can be created with use of only a small number of instructions with comparable performance relative to the original solution. This gave the opportunity to create the RISC. Thanks to the reduced instruction set, the ALU could be smaller, the execution of instructions was faster, and the compilers could be better optimized [7].

RISC [4] is characterized by the following properties:

a large register file,

- emphasis on operations that use registers,

- instructions are executed in one instruction cycle,

- · simple instructions for memory access,

- simplified addressing modes,

- · uniform length of the instruction word

- and others.

For comparison CISC [3] characterized with:

- a small register file,

- a large number of instructions,

- instructions oriented for memory access,

- a non-uniform length of instruction word,

- a different time of instruction execution.

Classic processors CISC and RISC are adjusted mainly for control applications. Average application of this type performs branch operation on every 7<sup>th</sup> instruction [8]. In addition, branches are often unpredictable. Digital signal processing algorithms are different. They are characterized mainly by regular running in loops and periodic memory access. Digital signal processing applications also includes many algebraic operations. Typical operation is a multiply and accumulate (MAC), fused multiply-add (FMA), vector operations or saturated arithmetic [9][10][11]. For this reason, digital signal processors (DSP) were created. Their architecture is similar to the RISC processors in some ways. The first step was to implement the previously mentioned MAC function. Then the idea of separate buses was taken from Harvard architecture. In this case, the memory has not been divided into program and data parts, but the buses are used to read instruction and all operands in one instruction cycle, what increases throughput [12].

Nowadays the typical representative of the CISC architectures are IA-32 (known as Intel x86) and AMD64 (IA-64, x86-64) [13][14][15], which are currently used on most of the personal computers. There are also processors derived from the 8-bit Intel MCS-51 core, which are used in embedded devices. The example of the derivate is 8051 [16]. The RISC processors are more common in embedded devices. They are contained in wide spectrum of the variants from the 8-bit microcontrollers such as PIC [17] or AVR [18], through the 16-bit mixed signal microcontrollers like MSP430 [19] or PIC24, to the 32 and 64-bit processors with the ARM core [20]. The DSPs are also available from the lower performance variants like dsPIC [21] or C2000 [22] to the high-performance processor cores like C6000 [23] or StarCore [24].

#### 1.2.2 Graphics processing units (GPU)

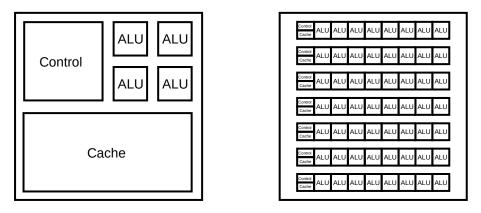

Classic CPUs are oriented to the complex controlling of application and data processing in one thread, sometimes with use of cache memory. GPUs are oriented to parallel data processing with high throughput. It is achieved with the high number of computing cores [25]. One GPU can contain hundreds of them. This number is achieved at the cost of their simplicity, so they are not suitable for control applications. GPUs are therefore used in combination with CPUs as the coprocessor [26]. The difference between CPU and GPU is shown in Figure 1.5 [27].

Figure 1.5: CPU (left) and GPU (right) difference

From the graphical comparison of the CPU and GPU can be seen, that the big part of the classic CPU is made of the memory, which can be used for data and instructions. Also due to its complexity, the control logic and ALUs needs more logic elements. On the other side is the GPU with the minimal cache memory or control logic. The biggest part is created by the ALUs, so it makes GPUs suitable for data processing with high throughput as it was mentioned, not for control application.

First video cards stared with the IBM Monochrome Display Adapter in 1981 with only text support. Later, the video cards supported 2D and 3D graphic acceleration [28]. In 1999 Nvidia introduced the first GPU for the personal computer (PC) industry with the definition that a GPU is "a single chip processor with integrated transform, lighting, triangle setup/clipping, and rendering engines that is capable of processing a minimum of 10 million polygons per second" [29]. ATi introduced Radeon R100 as Nvidias rival and later with R300, ATi used term Visual Processing Unit (VPU) [30]. Nowadays, the GPUs are not used only for graphic processing, but there are also models dedicated for high performance computing (HPS), such as Nvidia Tesla [31]. These cards are also known as general-purpose graphics processing units (GPGPU).

# 1.2.3 Very long instruction word (VLIW)

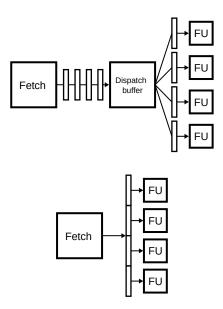

Core of the processor based on VLIW [32][33] architecture contains multiple functional units with ability to execute multiple instructions at once. It is the instruction-level

parallelism like in the superscalar processors, but with one difference. Superscalar processor maps the instruction dynamically from the stream of the single instructions (Figure 1.6) [34]. Software for VLIW is made of instruction packets, which are created statically during the software compilation. Thanks to this, the VLIW core structure can be simplified. This makes the space for the additional functional units, its functionality or the increase of the clock frequency. The VLIW processors usually find its place in signal processing or multimedia applications. The instruction-level parallelism is used mainly in the implementation of DSP algorithm cores.

Figure 1.6: Superscalar (top) and VLIW (bottom) difference

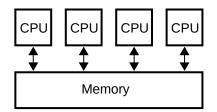

## 1.2.4 Multicore systems with shared memory

Multicore systems with shared memory contain several independent CPUs with direct access to the local memory, which is usually RAM (Figure 1.7). This model could be applied to various architectures such as CISC, RISC, DSP or their combination, so the system could be homogeneous or heterogeneous. The most known systems from this group are multicore PCs, but they are also used in embedded systems for medical systems, radar systems etc. The parallelism is created through threads. During the processing, the input signal is divided into several parts, which are processed separately. The iterations must be independent on each other, so not all algorithms can be parallelized in this way.

Figure 1.7: Shared memory system

The advantage of these systems is the fast data sharing between the tasks. Also, the single address space provides simple perspective on memory during the software developing. The main disadvantage is the scalability of the systems. With the increase of the number of processors also increases the traffic on the memory to CPUs bus. The next disadvantage is connected with the previous one. The software developer should be aware about the correct access to the memory [35].

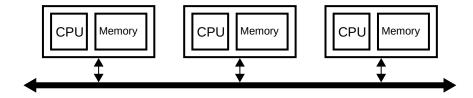

#### 1.2.5 Multicore systems with distributed memory

Multicore systems with distributed memory are similar to the systems with shared memory from the parallelism principle point of view. The difference is that every processor has its own address space. When access to the different memory space is needed, data are transmitted in the message through the communication network (Figure 1.8). These systems are used in the HPC typically for simulation of the physical effects such as fluid flow or electromagnetic fields with very detailed models.

Figure 1.8: Distributed memory system

The advantage of this systems is the scalability. With the increasing the number of processors the memory also expands. In addition, each processor can access to its own memory without interference of the other CPUs. The disadvantage is the non-uniform data access, because the data can be placed in different node. This also makes difficult to work with the global data, because the software needs to process the data exchange between the nodes [35].

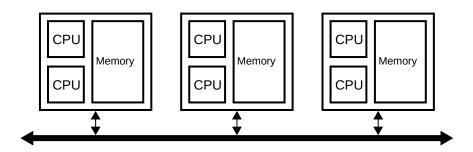

## 1.2.6 Multicore systems with hybrid distributed-shared memory

These systems combine previously mentioned systems. The shared memory systems with multiple CPUs or GPUs with its own memory space are interconnected with

network like system with distributed memory (Figure 1.9). These systems can be scaled to the desired application respecting the advantages and disadvantages of the combined systems.

Figure 1.9: Hybrid distributed-shared memory system

# 1.3 Programming methods

The performance of the final application is not only dependent on the device, but also on the software. It is really important part of the application, because the well optimized code could make better performance on the low-cost hardware than the bad written code running on the high-priced device. There are several methods of creating the final code which has its pros and cons (Figure 1.10). This subsection will introduce some methods of creating software.

Figure 1.10: Levels of the programming languages

# 1.3.1 Low-level languages

The low-level programming languages provide only little abstraction from processor instruction set. Low-level code could be converted directly to the machine code without using a compiler. The software written in low-level language could be really fast and the result binary code could be small. This kind of programming was common in the past because of lack of high-level language compilers, but nowadays is used only for:

embedded systems with small resources

- optimizing of the critical part of the software

- creating hardware drivers and system code

The next reason, why it is not used, is the economical aspect. The software development takes a long time and the code is highly dependent on the processor architecture and instruction set, so it is not easy portable between different devices [36] [37].

There are several ways how to write a low-level code:

- machine code

- low-level assembly

- linear assembly

Writing an application in machine code is unusual and in common practice is not used at all, because it is requires lot of concentration, the code is not human readable, so there could be easy to make mistake that is really hard to find. Instead of this, the assembly language is used. It is the text interpretation of the processor instructions. The difference between low-level assembly and linear assembly is that the code in linear assembly does not include the information about the used registers and functional units. The compiler maps the required resources itself automatically [38].

### 1.3.2 High-level languages

The high-level languages provide strong abstraction from the hardware. Instead of dealing with the instructions, registers and memory addressing, the high-level languages deal with the variables and arithmetic expressions. The code is better readable than the assembly code. Thanks to the strong abstraction, it is also easy portable. High-level languages include for example the FORTRAN [39], BASIC [40][41], C [42], C++ [43], C# [44] or Java [45]. After the compilation, some of them could be executed directly on the machine, but some of them needs interpreter. The price for possibility to easy write complex code, which is also portable, is a smaller efficiency and the larger size of the final binary program. This is caused by the inability of the direct translation of the elements into the machine code. Even if the compilers are still being developed to generate more optimized code [46], they are not able to handle some special cases. The following examples refer to the standard C/C++ expressions:

- inability to express special DSP operation such as addition, subtraction and multiplication with saturation

- inability to express vector operations

- inability to mark the independent part of programs which can be run in parallel due to sequential character of notation

inability to process data on parallel functional units/cores (split iterations of loops)

These deficiencies are removed using the special optimized libraries provided by processor manufacturers [47][48][49] or by the third party [50], compiler extensions, such OpenMP [51] for program execution on shared memory system or MPI [52] for distributed memory system or with special programming languages like CUDA [53] for general-purpose processing on GPU. There are also some projects such as [54] that are able to handle the instruction level parallelism more effective.

#### 1.3.2.1 Difference between compiled and interpreted languages

The typical approach of the translating source code of the program written in high-level languages such C/C++ is compiling it to the machine code. This result can be decoded directly by the compatible hardware and the CPU can execute the instructions. In some cases, it is not necessary to translate source code directly to the machine code [55]. These languages can be divided into:

- pure interpretation,

- hybrid implementation systems.

The pure interpreted languages are also called scripting languages. These languages need the interpreter, i.e. a software for fetching the high-level language statements and parsing it into the operations at runtime. The main disadvantage of this system is the slowness of the execution.

This disadvantage is reduced with the hybrid implementation system, where the source code is compiled into the intermediate code, sometimes called byte code. This code contains only instruction for the virtual machine, which only translate the byte code into the machine code [56].

# 1.4 Standard optimization methods

Optimizations are set of analyze and transform operations performed on source code achieving to run it faster or consume less hardware resources. These operations finds and replaces parts of code with more efficient alternatives. The compilers use two main techniques to determine the code parts to optimize [57]:

- control flow analysis

- data flow analysis

Control flow analysis is based on the examination of the control statements which can cause branch in the program such as loops, conditions and function calls. In this case, the optimizations are applied on the possible paths of program execution.

Data flow analysis is another type of optimization, which analyzes the usage of data in the program. This can be used for reducing number of variables, optimize loading of constants and data transfer.

Several optimization techniques are described in [46] and [57]. Following text will shortly introduce some of these common methods.

#### 1.4.1 Redundancy elimination

The code can be marked as redundant when the same expression has been previously evaluated without modification of its variables [46]. The redundancy elimination includes common subexpression elimination and copy propagation transformation [57].

The common subexpression elimination reduces number of executed instructions by removing expressions which were already computed. The result value is used instead of the evaluate expression again (Figure 1.11).

Figure 1.11: Example of common subexpression elimination

The copy propagation transform reduces cases when variables are copied from one to another. Instead of copying variables and accessing to target and source location, the source variable is used in next expressions (Figure 1.12).

Figure 1.12: Example of copy propagation transform

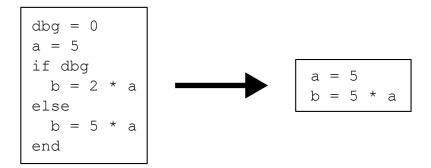

## 1.4.2 Constant propagation optimization

Constant propagation optimization [46] also known as constant folding [57] tracks the known variable values propagation in the call graph. In cases where the value of the expression can be determined at compile time, this expression is substituted with the evaluated constant (Figure 1.13).

Figure 1.13: Example of constant folding

#### 1.4.3 Useless code elimination

Some parts of code can have no effect to the program results. These parts of code can be formed by assignment operations to unused variables (Figure 1.14) and unrealizable conditions (Figure 1.15). These operations and parts of code can be removed without program functionality affection. Special case of this optimization type is also known as dead code elimination [46][57].

Figure 1.14: Example of useless code elimination

Figure 1.15: Example of dead code elimination

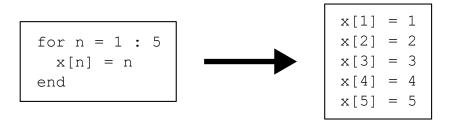

#### 1.4.4 Inline expansion

Inline expansion, or inlining, is used to increase the code performance [46][57]. It replaces complex parts of code with its inline representation. Typical optimization is the function inlining where function call is replaced directly by function content (Figure 1.16). Inlining also includes loop unrolling, where the loop content is replaced by the series of operations from loop (Figure 1.17).

```

function abs(x)

if x < 0

return -x

else

return x

end

end

a = -5

b = a < 0 ? -a : a

```

Figure 1.16: Example of inline expansion

Figure 1.17: Example of loop unrolling

# 2 The objectives of the dissertation thesis

The previous chapter described possible realization options of digital signal processing applications. It does not matter if the signal processing is performed on the scalar processor or the multicore system, the software is still the most critical part that specifies the final efficiency. The modern compilers could produce quite effective code, usually on scalar architectures, because these compilers were developed for a long time and they are frequently used. But there are other architectures which are not commonly used in applications and they are using some enhanced type of parallelism, not only pipelining, so the compilers could be less effective. The VLIW architecture meets this condition, because its instruction parallelism must be specified at compile time.

For this reason, the dissertation thesis will be focused on the software part of the signal processing systems, mainly the parallelism. The objectives are as follows:

- Prove that the software development tools for instruction-level parallelism are less effective than the tool for data parallelism or task parallelism.

- Create the effective tool for the software developing of digital signal processing application suitable for architectures using instruction-level parallelism, especially VLIW processors.

The second objective consists of the followed points:

- Create the general model of VLIW processor or any general-purpose processor which will be used by the tool to final assembly code.

- Create an algorithm for DSP algorithm assignment to the available hardware resources.

- Implement an optimization method to effective mapping of the functional units and registers.

# 3 Effectiveness of software development tools

The software plays the key role in the whole signal processing system based on DSP. This chapter will show the effectiveness of the widely used programming approaches focused on parallelism. The dissertation thesis is aimed on the instruction parallelism when the software execution is determined at compilation time. Also, the instruction level parallelism should be compared with the data parallelism. For that reason, the multicore VLIW based DSP will be used in the next benchmarks.

This chapter will demonstrate the programming methods of signal processing applications from higher-level to low-level. The high-level approach will include data processing in multiple threads to show the suitability on computations in different areas. The next high-level approach will be pure single threaded execution of the algorithms to be compared with the low-level approach when VLIW architecture is used. This high-level case will be compared with the low-level assembly language and linear assembly language, which is not available for all architectures.

There are not so many silicon manufacturers producing VLIW DSPs which meets the requirements and are also easily available. Texas Instruments (TI) offers DSPs from C6000 family, which are based on VLIW architecture and they are also made in multicore variants. There ale also multiple development kits based on these DSPs. The most of them are with the C64x [58] cores, which is older series supporting only fixed-point arithmetic, and with the C66x [59] cores with floating-point support. The choose will be decided from the newer C66x, because it will show also the handling of the floating-point arithmetic. From the availability of the evaluation boards, the TMS320C6678 [60] was chosen. This DSP fits perfectly, because it is multicore fixed-point VLIW based DSP allowing wide demonstration cases in fields of instruction-level and threading parallelism. The processor and the development board will be described in detail later in this chapter.

The first part of chapter describes the structure of used processor, its features and properties, and the used development board as well. The second part is evaluating the DSP algorithms created with the high-level and low-level languages in instruction-level parallelism point of view. The high-level language also demonstrates the thread level parallelism using OpenMP.

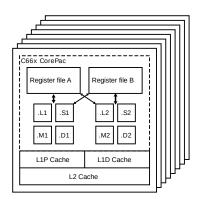

#### 3.1 Multicore DSP TMS320C6678

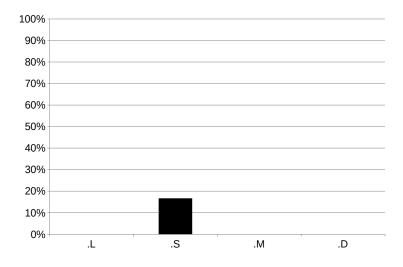

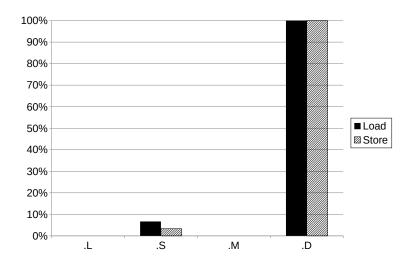

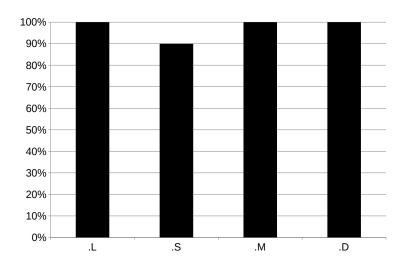

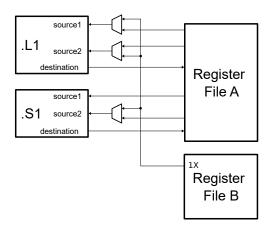

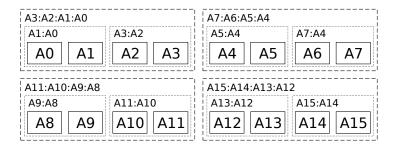

The TMS320C6678 is a multicore fixed/floating-point digital signal processor and it is containing of eight C66x DSP cores [59]. Each core consists of two data paths (titled A and B), two sets of thirty-two 32-bit registers (A0, ..., A31 in data path A and B0, ...,

B31 in data path B, respectively), and two sets of four functional units (.L1, .S1, .M1, .D1 in data path A and .L2, .S2, .M2, .D2 in data path B). Each functional unit is primary used for a different type of operations. The .Dx units are used for loading/storing data between a general-purpose register file and a memory space. The .Lx and .Sx functional units perform general fixed and floating-point arithmetic operations, next the logic operations, and finally the branch functions. The .Mx units perform all multiply operations with the single/double precision floating-point numbers as well as with the fixed-point values. In addition, the DSP is capable to execute SIMD instructions for fixed-point and floating-point instructions, where 8 and 16-bit operands are packed into the single 32-bit word, or single precision floating-point values are packed into the register pairs. These SIMD instructions are especially for additions and multiplications (DADD2, MPY2, DADDSP, DMPYSP, QMPYSP, etc.) [23]. This is useful for the signal processing algorithms such as Fast Fourier Transform, Discrete Cosine Transform, etc. The DSP can also perform complex multiplication or multiplication of complex vectors by the complex matrices. Detailed description of the DSP functionality can be found in [60]. The basic parameters of TMS320C6678 DSP are shown in Table 3.1.

*Table 3.1: Basic parameters of the TMS320C6678*

| Parameter                 | Value       |

|---------------------------|-------------|

| Clock speed               | 1.4 GHz     |

| L1P memory                | 32 kB/Core  |

| L1D memory                | 32 kB/Core  |

| L2 memory                 | 512 kB/Core |

| Shared L2 memory          | 4 MB        |

| External memory interface | 64-bit DDR3 |

| GFLOPS                    | 128         |

| Thermal design power      | 17 W        |

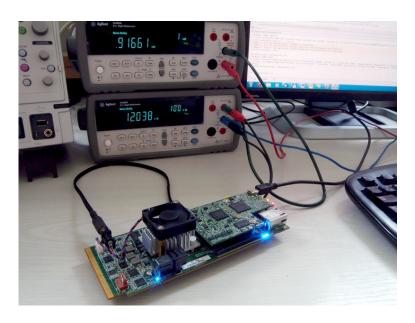

## 3.1.1 TMDSEVM6678LE Development Board

The 8-core DSP is assembled on a development board TMDSEVM6678LE [61]. It is a stand-alone development board with 512 MB of DDR3 memory, 64 MB of NAND Flash, 16 MB SPI NOR Flash, Gigabit Ethernet, PCIe, and other typical peripherals. Some of them are routed to the AMC B+ edge connector. It makes the board ideal for developing of media gateways, and/or video servers of video recognition applications. The board also contains an embedded JTAG emulator, so it can be connected with TI's software development tool: Code Composer Studio without need of any external emulator. Nevertheless, it is possible to connect a different emulator through a 60-pin TI

JTAG connector. In this case, the XDS560v2 is providing the real-time debugging. The disadvantage of the board is the lack of accessible testing points, so the power consumption can be measured for the whole board and not for the components separately.

#### 3.2 Test cases

Testing of the software behavior is divided into 2 groups. The first group explores the performance of the code from the data and thread parallelism, the second examines the performance from the instruction level parallelism. All of the evaluations were performed on the real hardware which was previously described.

#### 3.2.1 Data and thread parallelism using OpenMP

The data parallelism is achieved when the multiple functional units (or the cores) perform the same operation on different data. It could be realized on the SIMD or multiprocessor system. For comparison, the thread parallelism can be achieved only on the multiprocessor system. One of the solutions how to make code to run on multicore processor is to use OpenMP [51].

OpenMP is an application program interface (API), which provides a portable, scalable model for shared-memory programming. First specification of OpenMP was defined in 1997 for FORTRAN by major hardware and software vendors. One year later OpenMP was defined for C/C++.

OpenMP uses thread based parallelism with fork-join model. This means, that application start in one thread and if it come to parallel section, it creates another thread. When this team of threads completes their work, they synchronize and terminate except master thread. These threads can be section work-sharing and loop work-sharing [62].

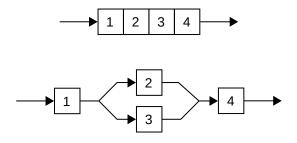

#### 3.2.1.1 Section work-sharing

This type of work-sharing can be used for independent pieces of code which can run in parallel. Parallelism of this type is similar to creating threads through standard libraries provided by operating system. It can be used to pipeline the processing.

Figure 3.1 shows the example of section work-sharing. The original algorithm consists of 4 steps and is performed sequentially. Steps 2 and 3 are independent and can be performed in different order or in parallel.

Figure 3.1: Example of section work sharing

#### 3.2.1.2 Loop work-sharing

The loop work-sharing is the common way how to increase the performance of the application. For-loops are primary targets in parallelization. They can be used if iterations have no dependencies between each other.

Figure 3.2 shows a for-loop parallel execution, which is processing an array with length of 16. It is divided into 4 threads, where each of them processes 4 values. Parts of array which are processed are marked in gray color.

Figure 3.2: For-loop parallel execution

In this case the processed data are shared among all cores. If the algorithm uses some auxiliary variables and they are used by all threads, the code will possibly return wrong result. These variables must be defined as private, which means that there is created local copy in memory for every core.

# 3.2.2 Algorithm parallelization in OpenMP

This part is dealing with a parallelization of selected signal processing algorithms. It is especially finite impulse response (FIR) filter, discrete Fourier transform (DFT) and Fast Fourier transform (FFT). These algorithms allow easy parallelization on the loop. Each of them has different character comparing the others. The FIR filter process relatively small part of input signal to generate one output sample. The DFT needs the whole input signal for each output sample. These two algorithms process the output signal directly sample by sample, but the FFT needs to compute intermediate data from all input samples and then the final signal. Parallelization of code is realized with OpenMP directives. During this process, it is important to take care of which variable is shared between threads and which must be created as private for each thread.

#### 3.2.2.1 FIR filter

FIR filter is implemented according to

$$y_n = \sum_{k=0}^{N-1} x_{n-k} h_k \tag{3.1}$$

from [63], where *x* is input signal, *y* is the output signal and *h* is impulse response if the filter with the length of *N*.

This type of filter was selected, because it does not require feedback, which could not be simply parallelized. Final code contains 2 nested for-loops, but only outer loop is parallel. However, OpenMP support nested parallelism, inner loop is performed sequentially. It is because the number of physical cores is less than number of signal samples and there is no space where to execute other threads.

#### 3.2.2.2 Discrete Fourier transform

Structure of the DFT implementation (3.2) is similar to the FIR filtration (3.1). The output sample is given by the sum of products of input signal and another variable. It consists of 2 nested for-loops. The difference is that there are complex calculations and the inner loop goes through full length of the signal. This means, that the amount of processed data is much higher in compared to the FIR filter. According to [63], DFT is given by

$$X_{k} = \sum_{n=0}^{N-1} x_{n} e^{\frac{-i2\pi kn}{N}}$$

(3.2)

where x is input signal with length of N in time domain. The X is output signal in frequency domain also with the length of N.

#### 3.2.2.3 Fast Fourier transform

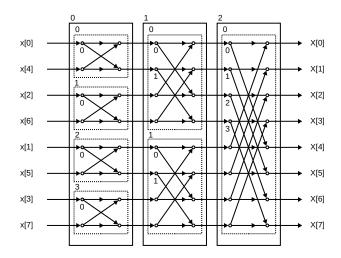

For the demonstration of FFT, the Cooley-Tukey algorithm [64] was chosen. This algorithm is one of the most used in the practical implementations of the signal processing algorithms. The structure is different from the previous implementations. Figure 3.3 schematically shows progress of used loops in algorithm. The outer loop iterations, which represent the stage in FFT, obviously depend on each other, so it cannot be executed in parallel. The middle, representing group of butterflies, and the inner loop, representing butterfly processing, are independent in each of its iteration. For simplicity, only middle loop was chosen for parallelism even if last stages will not benefit from this. The final implemented FFT algorithm is the radix-2 decimated in time (DIT).

Figure 3.3: FFT radix-2 with highlighted loop iterations

Final parallel code cannot run without operating system, which controls threads. TI provides real-time kernel called SYS/BIOS [65] or DSP/BIOS [66]. It is designed to use in embedded applications which requires real-time scheduling.

#### 3.2.3 Measured performance of OpenMP

The execution time of whole function call represents the performance of implemented algorithms. Dependence of execution time on number of created threads and length of input signal was measured. For determining how the performance of algorithms was influenced with changing of these parameters and by the OpenMP runtime, the execution time of sequential versions (without OpenMP pragmas) of algorithms was chosen as reference (Table 3.2).

Table 3.2: Measured reference time

| Length of the signal | FIR     | DFT       | FFT      |

|----------------------|---------|-----------|----------|

| 16                   | 2 µs    | 157 μs    | 16 µs    |

| 32                   | 4 µs    | 605 µs    | 39 µs    |

| 64                   | 8 µs    | 2457 μs   | 93 µs    |

| 128                  | 16 µs   | 9911 µs   | 215 µs   |

| 256                  | 32 µs   | 39832 μs  | 491 μs   |

| 512                  | 63 µs   | 159782 μs | 1105 μs  |

| 1024                 | 126 µs  | 640102 μs | 2456 μs  |

| 2048                 | 252 μs  | -         | 5405 μs  |

| 4096                 | 507 μs  | -         | 11810 μs |

| 8192                 | 1025 μs | -         | 25791 μs |

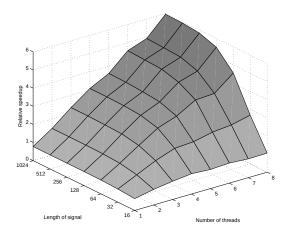

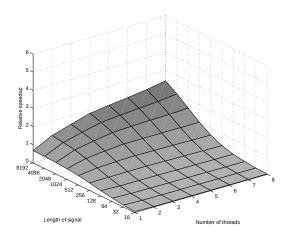

Figures 3.4 to 3.6 show the relative increase of performance. The X axis represents number of cores processing the signal, the Y axis carries the length of the processed signal and the Z axis shows the speedup relative to the reference time from Table 3.2. From graphs can be seen, that performance of all algorithms with OpenMP directives are slower when there is only master thread. It is because the process of thread creating is still active, even if the maximum number of threads is set to 1. It is the same reason why the relative speedup is not the same as the number of created threads. In addition, threads are communicating with each other and accessing to the same memory, because inputs and outputs are defined as shared variables.

Figure 3.4: Relative speedup of FIR filter

Figure 3.5: Relative speedup of DFT

*Figure 3.6: Relative speedup of FFT*

Table 3.3 shows the measured times that are needed to create the new threads. On FIR filter and DFT algorithm, it is created only once. When program compute FFT, the parallel region is created regularly depended on length of input array.

Table 3.3: Time needed to create parallel region

| Number of threads | Time  |

|-------------------|-------|

| 1                 | 17 μs |

| 2                 | 34 µs |

| 3                 | 36 µs |

| 4                 | 39 µs |

| 5                 | 42 μs |

| 6                 | 45 μs |

| 7                 | 48 µs |

| 8                 | 52 μs |

If the processing is made of the small number of instructions or the length of processed data is short, it does not worth it to parallelize the loops. It is because the time required for creating threads and time while these threads communicate with each other can be approximately the same or bigger than the execution time of the actual time of calculation. In addition, the behavior of the hyper-thread enabled processor could be found in [67]. This makes threading parallelism suitable to apply on processed data with the same algorithm core, not for its creation. The algorithm core creation should be performed by optimization on the low-level, which will be shown in next part of this chapter.

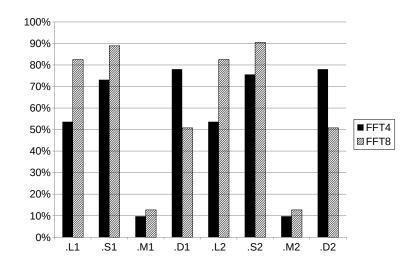

# 3.2.4 Low-level optimizations of the algorithms on the VLIW architecture

The low-level programming approach allows the programmer to utilize the functional units of the VLIW processor as much as possible. For the next examination, the FFT was chosen again. Now, the algorithm is not written to work in loops with variable-length input signal, but it is written to process fixed vectors with 4, 8 and 16 samples. The function's computing performance was measured in CPU cycles. All measurements were evaluated for a single-core DSP version only.

Table 3.4: C implementation FFT performance

| Function | Input            | Data path | CPU cycles |

|----------|------------------|-----------|------------|

| FFT4R    | 4-point real     | A+B       | 46         |

| FFT4C    | 4-point complex  | A+B       | 80         |

| FFT8R    | 8-point real     | A+B       | 123        |

| FFT8C    | 8-point complex  | A+B       | 205        |

| FFT16R   | 16-point real    | A+B       | 425        |

| FFT16C   | 16-point complex | A+B       | 642        |

Table 3.4 summarizes the computing demands of functions written in C language, where notation FFT4R represents a function for real FFT with N = 4, FFT16C is the function for complex FFT with N = 16, etc. The code was compiled by commercially available compiler for C6000 Optimizing Compiler v7.3.1 from TI. By exploring the disassembly code, the usage of both DSP data path A and B was affirmed. It can be seen, for a single FFT calculation between 46 CPU cycles (for N = 4 real values) and 642 CPU cycles (for N = 16 complex values) is needed. The computing performance of functions written in low-level source code is shown in Table 3.5.

*Table 3.5: Low-level implementation FFT performance*

| Function | Input            | Data path | CPU cycles |

|----------|------------------|-----------|------------|

| FFT4R    | 4-point real     | A         | 19         |

| FFT4C    | 4-point complex  | A         | 24         |

| FFT8R    | 8-point real     | A         | 34         |

| FFT8C    | 8-point complex  | A         | 42         |

| FFT16R   | 16-point real    | A         | 88         |

| FFT16C   | 16-point complex | A         | 100        |

Low-level implementation of the previous functions takes from 19 (for N = 4 real values) to 100 CPU cycles (for N = 16 complex values). The relative speedup (Table 3.6) is from 2.4 (for N = 4 real values) up to 6.4 (for N = 16 complex values). The next improvement is the utilization of only one data path. It means that if there is need to compute multiple transforms in row, the speedup can be twice as it is now achieved only with copying the code into the data path B.

*Table 3.6: Relative speedup of the low-level FFT implementation*

| Function | Input            | Relative speedup |

|----------|------------------|------------------|

| FFT4R    | 4-point real     | 2.42             |

| FFT4C    | 4-point complex  | 3.33             |

| FFT8R    | 8-point real     | 3.62             |

| FFT8C    | 8-point complex  | 4.88             |

| FFT16R   | 16-point real    | 4.83             |

| FFT16C   | 16-point complex | 6.42             |

### 3.2.5 High-level and low-level comparison

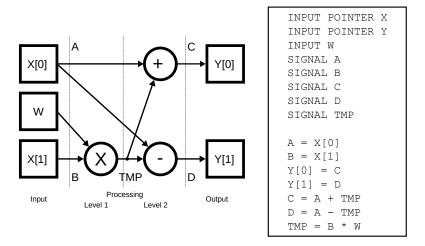

Previous parts are exploring the speed of execution of low-level and high-level implementation. Now, the text will show the difference in the structure of the compiled code. It will be shown on the 4-point FFT with complex inputs. The code is based on the FFT4C function from previous demonstration. The low-level code was rewritten into the linear assembly and C language respecting the same order of the operations. The optimizations were disabled for better recognition of the disassembled parts.

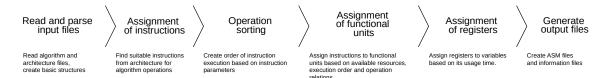

#### 3.2.5.1 Low-level assembly

The low-level language offers the most accurate way to optimize the code. The software developer has full control over the processor functionality and timing. It makes this method suitable for creating time critical parts of software, such as the DSP cores. Developing software in the low-level assembly requires more time and the final code can be used only on the specific architecture. For these reasons, the low-level assembly is not used for creating the complex software or the libraries. For example, the FFTW library [50] is fully implemented in C, but some parts have multiple implementations, which include assembly routines as well.

```

.D1 *A4++[2], A17:A16

LDDW

.D1 *A4--[1], A19:A18

LDDW

ADDSP .L1 A6, A8, A6

SUBSP .S1 A6, A8, A8

.D1 *A4++[2], A21:A20

LDDW

ADDSP

.L1 A7, A9, A7

SUBSP .S1 A7, A9, A9

.D1 *A4++[1], A23:A22

LDDW

```

Figure 3.7: Hand-written assembly code

The part of low-level implementation of the FFT is shown in Figure 3.7. The first ADDSP (single precision floating-point addition, see [23]) operation is the equivalent of the first addition operation of the C code from Figure 3.10. This part of the code is preceded by the other 4 LDDW (load double word from memory) instructions for loading data into the registers and the loading process continues during the processing of previously loaded data. In this case, the whole computation of the 4-point FFT with complex input takes only 24 instruction cycles for TMS320C6678. The code uses only data path A, but the level of parallelism is much higher than the result of the C compiler.

#### 3.2.5.2 Linear assembly

Linear assembly language is very similar as the classic assembly language, where the developer uses specific instructions, but does not care about timing and usage of functional units and registers. This method is alternative for the TMS320C6000 architecture family DSPs [68]. This feature should help to reduce developing time [69].

The FFT algorithm from the previous case in the linear assembly language contains instructions in the same order as in the low-level assembly code, but the register names were replaced by the symbolic titles. The functional units were removed as well. The part of the linear assembly code is shown in Figure 3.8.

| ldw   | *pX[6], in6  |

|-------|--------------|

| ldw   | *pX[7], in7  |

| addsp | in0, in4, m0 |

| addsp | in1, in5, m1 |

| subsp | in0, in4, m2 |

Figure 3.8: Example of linear assembly code

In the disassembly form of the example code (Figure 3.9) can be seen one data path A is used, similar tot the low-level assembly, but the instructions are executed sequential, even if there is a possibility to combine them into one instruction packets. The example is the instructions ADDSP and SUBSP, which use already loaded independent data, but SUBSP waits for the completion of the ADDSP instruction. The

addition and subtraction of two floating-point numbers can be performed by the functional units .L and .S [23]. The arguments of the operations are also different. In addition, the compiler waits for the result with NOP (no operation) instruction before executing the following operation.

```

LDW.D1T1 *+A4[6],A19

LDW.D1T1 *+A4[7],A18

ADDSP.L1 A7,A9,A17

.fphead p, l, W, BU, nobr, nosat, 0000011b

NOP 3

ADDSP.L1 A6,A8,A16

NOP 3

SUBSP.L1 A7,A9,A9

NOP 3

```

Figure 3.9: Disassembly of the algorithm written in linear assembly

## 3.2.5.3 High-level language

The high-level programming languages are useful for creating complex software, because it reduces developing time. They are also suitable for creating the libraries for the multiple platforms, because the source code is portable to different architectures.

Tested algorithm is made as separate function in the C language, with one input pointer to signal samples vector. The temporary results are stored into the local variables. The code contains only 16 arithmetic operations and the part of final disassembled code from TIs C6000 compiler v7.3.1 with the default optimization level is shown in Figure 3.10. The disassembled code shows the first operation of the algorithm.

| fft4 dit c: |                 |            |            |

|-------------|-----------------|------------|------------|

| 00008340:   | 07FFEC52        | ADDK.S2    | -40,B15    |

| 00008344:   | AC45            | STW.D2T1   | A4,*B15[1] |

| 18          | A6 = pX[0] + pX | [4];       |            |

| 00008346:   | 6246            | MV.L1      | A4,A3      |

| 00008348:   | 9247            | MV.L2X     | A4,B4      |

| 0000834a:   | 904D            | LDW.D2T2   | *B4[4],B4  |

| 0000834c:   | 018C0264        | LDW.D1T1   | *+A3[0],A3 |

| 00008350:   | 020C979A        | FADDSP.L2X | B4,A3,B4   |

| 00008354:   | 2C6E            | NOP        | 2          |

| 00008356:   | DC45            | STW.D2T2   | B4,*B15[2] |

Figure 3.10: Disassembly of the FFT algorithm written in C

The execution of the function takes 195 instruction cycles, including function call and return. There can be seen, that the compiler is using both data paths A and B. It could be a good idea to use all possible resources, but in this cases with similar range it

is not effective because the data transfer between data paths must be realized through the cross-path, which is limited on single value per cycle. The next think to notice is the instruction parallelism. The <code>||</code> sign means, that the instruction is executed at the same time with the instruction above. Here, the code is executed mostly sequentially, one instruction after the other.

The other issue is the frequent access to the memory. The function also does not use access to values through the pointer, but it uses separate variables where the values were copied. In this example the result was similar, because the variables were allocated on the stack.

The function was also rewritten to not using access to values through the pointer, but it uses separate variables where the values were copied. The result was similar, because the variables were allocated on the stack. Other information about usage of the functional units can be found in [70].

## 3.2.6 Comparison of the libraries with different structure

The method for implementing DSP algorithm should be considered for the application. It is typically compromise between the effort and code portability on one side and the code performance on the other.

| T 11 27 D (              | •               | C 1 1 1 CC 1     | 1 (             | ( ( ) ( )        | c ppp    |

|--------------------------|-----------------|------------------|-----------------|------------------|----------|

| Table 3.7: Performand    | re comnarison a | nt the aitterent | annroach of fi  | re C. IInraries  | tor ee i |

| Table 5.7 . I ci joi man | e comparison c  | of the different | approach of the | ic C iioi ai ico | 10, 111  |

| Size | Cycles        |        |           |  |  |

|------|---------------|--------|-----------|--|--|

| Size | Non-optimized | FFTW   | TI-DspLib |  |  |

| 8    | 5 909         | 893    | 145       |  |  |

| 16   | 10 520        | 2 080  | 171       |  |  |

| 32   | 35 628        | 4 862  | 244       |  |  |

| 64   | 60 804        | 15 400 | 373       |  |  |

| 128  | 193 058       | 33 990 | 818       |  |  |

| 256  | 321 088       | 77 314 | 1 483     |  |  |

Table 3.7 shows the performance, given in CPU cycles, of three FFT libraries on the TMS320C6678. The first non-optimized library was implemented only for the testing purposes. Everything is computed during the runtime, including the twiddle factors. The second is the FFTW [50], which was configured for the general C compiler, because it does not have any support of the special instructions for the target DSP processor. The twiddle factors and other parameters are precomputed before the FFT execution. The last one is the TI's DSP library for C6000 [47]. The FFT parameters are also precomputed, but it is optimize using the low-level assembly parts. The disadvantage is

that this code cannot be used on different architectures. The difference of the libraries performance is significant. The optimized FFTW library is about 6.5 times faster than unoptimized library for small vectors and about 4 times faster for larger vectors. The low-level library (TI-DspLib) is about 6.5 times faster than optimized C library for small vector and about 53 times faster for larger vector.

# 3.3 Chapter summary

This chapter showed the difference between low-level and high-level programming languages. The demonstration was performed on the multicore DSP TMS320C6678. The results are described below.

The high-level programming languages is the fast and easy way how to write DSP algorithms offering the possibility of compile the code on the other platform. But on the VLIW architectures, it is not very effective. The compiled code contains no or little parallelism on instruction level. This could be caused by the processes of optimization where compiler tries to find similar parts of the code end reuse them. This works on scalar processors, but on VLIW architectures, where the detected code could contain different parallel operations which cannot be changed at run-time, it makes the target processor behaves as it has only one functional unit.

The thread parallelism can be helpful for processing a large amount of data. On smaller inputs, the cost of creating parallel regions by the operating system could be much bigger than the data process itself. This makes thread parallelism inappropriate for creating the cores of the DSP algorithms. For this purpose, the low-level programming languages can produce highly optimized code, especially on VLIW architectures. The disadvantages of the low-level languages are the longer development time and the fact, that the produced code could be used only on the specific platform. The results were published in [67], [70] and [71].

# 4 Impact of the software efficiency to the power consumption

The previous chapter showed how the different approaches of software creation affect the final performance of the application. This has an influence on the final time of data processing. But there is also another aspect which is affected. It is the amount of energy which is consumed while the application is running. This chapter will show the behavior of the real systems from the view of the power consumption when the program is executed on different number functional units and cores.

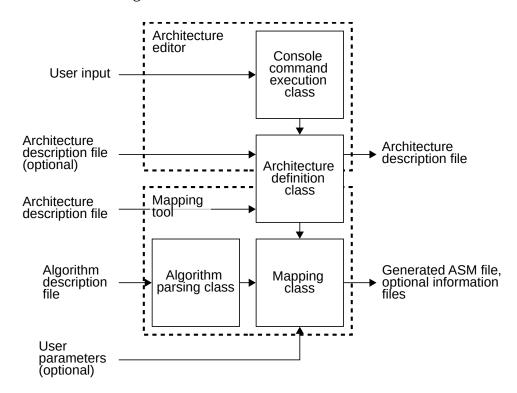

# 4.1 Theoretical power consumption increase on multiunit systems