# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# **FACULTY OF INFORMATION TECHNOLOGY**

FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

### **DEPARTMENT OF COMPUTER GRAPHICS AND MULTIMEDIA**

ÚSTAV POČÍTAČOVÉ GRAFIKY A MULTIMÉDIÍ

# **GHOST-FREE HDR VIDEO USING FPGA**

**GHOST-FREE HDR VIDEO S VYUŽITÍM FPGA**

**PHD THESIS**

DISERTAČNÍ PRÁCE

**AUTHOR**

Ing. MARTIN MUSIL

**AUTOR PRÁCE**

**SUPERVISOR**

Prof. Dr. Ing. PAVEL ZEMČÍK

ŠKOLITEL

**BRNO 2020**

#### Abstract

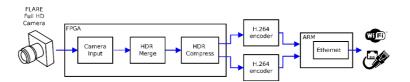

This thesis proposes an algorithm for multi-exposure ghost-free HDR video acquisition for embedded devices. The Ghost-free HDR acquisition was evaluated on the state-of-the-art FPGA architecture and achieved more than real-time performance of 96FPS on FullHD resolution. The proposed Ghost-free algorithm produces output visually comparable to the state-of-the-art algorithms which are considerably more demanding or not implementable on embedded devices at all.

#### Abstrakt

Tato práce navrhuje algoritmus pro pořizování ghost-free HDR videa ze sekvence expozic, který je určený pro implementaci ve vestavěných zařízeních. Vlastnosti algoritmu byly ověřeny implementací ve state-of-the-art architektuře HDR kamery, kde je schopen zpracovávat HDR video s potlačením tzv. ghosting efektu rychlostí až 96 snímků za sekundu na FullHD rozlišení, což více než dostačuje pro zpracování v reálném čase. Navrhovaný ghost-free algoritmus produkuje výstup vizuálně srovnatelný s nejmodernějšími algoritmy, které jsou výpočetně řádově složitější a často je nelze na embedded zařízeních ani implementovat.

# Keywords

HDR, HDR Acquisition, HDR Deghosting, Embedded Systems, FPGA, Real-time HDR processing

#### Klíčová slova

HDR, pořizování HDR, HDR Deghosting, vestavěné systémy, FPGA, zpracování HDR v reálném čase

#### Reference

MUSIL, Martin. Ghost-free HDR video using FPGA. Brno, 2020. PhD thesis. Brno University of Technology, Faculty of Information Technology. Supervisor Prof. Dr. Ing. Pavel Zemčík

# Ghost-free HDR video using FPGA

#### Declaration

Prohlašuji, že jsem tuto bakalářskou práci vypracoval samostatně pod vedením pana prof. Dr. Ing Pavla Zemčíka. Uvedl jsem všechny literární prameny, publikace a další zdroje, ze kterých jsem čerpal.

Martin Musil

August 31, 2020

# Acknowledgements

Tímto bych chtěl poděkovat svému vedoucímu prof. Dr. Ing. Pavlu Zemčíkovi za odborné vedení, konzultace a připomínky, které mi pomohly při řešení diplomové práce. Dále bych chtěl poděkovat kolegovi Ing. Svetozáru Noskovi za spolupráci na tvorbě HDR kamery, jejíž architektura byla několikrát publikována v odborných časopisech a na níž byl demonstrován vědecký přínos této práce.

# Contents

| 1                | Introduction                                     | 2          |

|------------------|--------------------------------------------------|------------|

| <b>2</b>         | HDR acquisition and deghosting                   | 4          |

|                  | 2.1 HDR acquisition                              | 4          |

|                  | 2.2 HDR tone mapping                             | 8          |

|                  | 2.3 HDR deghosting                               | 11         |

|                  | 2.4 Motion object selection methods              | 12         |

|                  | 2.5 Motion object registration methods           | 17         |

| 3                | Embedded HDR acquisition and deghosting          | <b>2</b> 1 |

|                  | 3.1 Embedded platforms and accelerators          | 21         |

|                  | 3.2 System-on-chip platforms                     | 28         |

|                  | 3.3 State-of-the-art hardware solutions overview | 31         |

|                  | 3.4 Ghost avoiding/removing solutions            | 41         |

| 4                | Proposal of ghost-free HDR algorithm             | 47         |

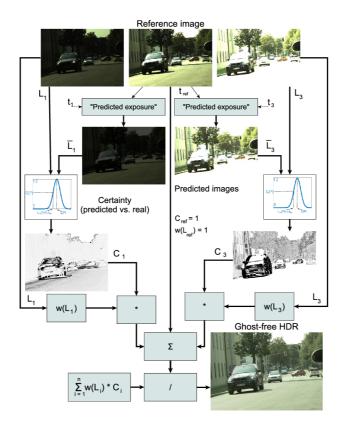

|                  | 4.1 Ghost-free merging algorithm                 | 48         |

|                  | 4.2 Implementation in HDR pipeline               | 50         |

|                  | 4.3 State-of-the-art ghost removal evaluation    | 53         |

|                  | 4.4 Performance summary                          | 58         |

|                  | 4.5 Validation and scientific contribution       | 63         |

|                  | 4.6 Applications and future work                 | 64         |

| 5                | Conclusion                                       | 71         |

| $\mathbf{B}^{:}$ | Bibliography                                     | 72         |

# Chapter 1

# Introduction

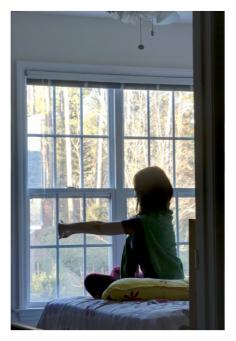

In the real world, our human vision is capable of seeing and recognising objects in various light conditions, even when they mix in one scene, such as a view from dark room outside to the sunny street. In the contemporary digital world, we are also trying to get this real-looking images into digital form as photography, video etc. One of the current problem in digital image acquisition is very limited dynamic contrast that can be captured from the scene, because the current camera sensors have only limited and linear response to the light, unlike the human eye. This often leads to photos with some white (overexposed) and black (underexposed) sections.

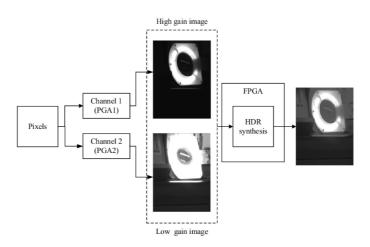

An effort still exists to remove this bottleneck and capture a high dynamic range image (HDR). The first possible way is to assemble a chip with a non-linear response to lightning. They are currently available, but they are still in the early age of development and suffers from some bugs, they have small resolutions, etc. Currently, most spread way how to obtain an HDR image is by merging a sequence of low dynamic range images (LDR) captured by the ordinary camera into one HDR.

The algorithms that merge LDRs into HDR image are known for a quite long time, but they produce a good visual result only with static scenes. In case of any motion, either in the scene or by the camera itself, the ghosting artefacts occur in resulting HDR image. Quite many papers about deghosting techniques were proposed; however, it is still a challenge and a quite open problem, no universal method with reference "deghosted" result exists.

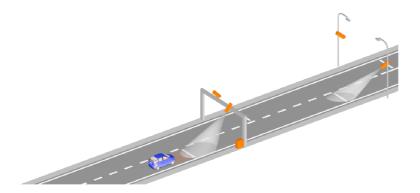

This dissertation is motivated by a need of many surveillance, security, traffic monitoring systems, and industrial applications that can benefit from HDR video capture. These applications are typically cost-sensitive and so multi-exposure HDR acquisition is often the only feasible option. In these use-cases, the motion in the scene is inevitable and "ghosting" in such systems, caused by the nature of image acquisition, troubles the applications. Therefore, I decided to develop a method of fast de-ghosting for such applications.

Applications in surveillance, security and industry require high performance in general – we cannot afford slow and demanding offline processing that the best state-of-the-art algorithms require. The essential goal is to capture HDR image fast, to be able to react to a certain situation very fast and or in a given time frame.

Image acquisition systems of this type are still being built on PC based systems; however, this approach is on the decline, since the PCs are expensive, they have large dimensions, and they consume a lot of power. Nowadays, the interest is turning towards compact embedded systems, which are breaking such limits. They often contain low power CPUs accompa-

nied by powerful, task tailored accelerators which require a fraction of power consumption comparing to CPU based systems, while they can deliver even much more performance.

The most efficient circuits are generally considered to be ASICs, which means Application-Specific Integrated Circuits. It is a collective name for single-purpose circuits/accelerators, tailored to provide specific functionality only. However, the manufacturing cost of such circuits is enormous; its manufacturing pays off only with high volumes of chips. The development processes of ASICs are taking place on large FPGAs (Field-programmable Gate Array), which are a completely customisable array of logic gates and registers, which can be interconnected in any desired way; therefore, they offer quite the same flexibility in design as ASICs, but with diametrically lower cost. Nowadays, FPGAs are very popular even in consumer electronics for their computing power, reliability, reprogrammability, low cost, and also low power consumption. These benefits are outweighed by designing time, which is still quite high. Also, not every task is implementable or convenient to accelerate on FPGA.

Some class of image processing algorithms are quite suitable for FPGA acceleration, at least when they uniformly process the image by pixels or blocks. For example, the HDR acquisition, as it was proposed by Debevec and Malik[5] is a typical example of a suitable algorithm. Unfortunately, this algorithm requires static images to produce a good-looking visual output. In case of motion in the scene, the ghost effects appear. As it is summarised later in this dissertation work, deghosting algorithms producing good visual output are very computationally demanding and quite often not even implementable on FPGA. The simpler algorithms are, on the other way, not very successful in deghosting and therefore, they are not suitable for applications in security, traffic monitoring, or industrial applications.

These circumstances led me to set the scientific contribution of this thesis to prove that a multi-exposure ghost-free HDR acquisition algorithm comparable to the state-of-the-art algorithms in quality can be designed for an embedded hardware device and achieves a real-time performance at high resolution.

The dissertation thesis begins with Chapter 2, which contains an overview of state-of-the-art algorithms related to the HDR acquisition and tonemapping. Chapter 2 further contains an overview of state-of-the-art deghosting algorithms, followed by selected deghosting algorithms feasible to be implemented in embedded devices. The thesis continues with Chapter 3 that contains an overview of hardware platforms suitable for implementation of deghosting algorithms, including an overview of embedded system-on-chip solutions. Chapter 3 is further focused on embedded platforms of for HDR acquisition, followed by an overview of existing embedded HDR deghosting solutions.

The proposal of ghost-free merging algorithm, which I developed to fulfil the goal stated in this thesis, is located in Chapter 4, which also contains algorithm evaluation, comparison to related algorithms, and also to the state-of-the-art. The chapter contains an evaluation of performance and power consumption, which demonstrates the engineering contributions of the proposed solution. The chapter ends with an evaluation of scientific contribution and by a summary of possible applications of the proposed algorithm.

# Chapter 2

# HDR acquisition and deghosting

This chapter contains an overview of state-of-the-art algorithms related to HDR acquisition and tonemapping. The chapter further contains an overview of state-of-the-art deghosting algorithms and also an overview of selected deghosting algorithms feasible to be implemented in embedded devices.

## 2.1 HDR acquisition

Standard video cameras are unable to capture the dynamic range of visual information the human eye is capable of. The dynamic range is the variation of luminance within a given scene and the obvious goal of image and video acquisition is to capture the whole luminance range of the scene into the captured image. The contemporary sensors are very limited and capable of capturing variations within two or three orders of luminance magnitude, while some scenes contain variations over the five orders. The video cameras are able to select which part of dynamic range is captured and which is lost as under/overexposed, e.g. by a selection of the aperture and shutter speed.

Two main approaches to HDR (High Dynamic Range) image capture exist. First of them is to build special cameras with HDR sensor. Some commercial products start to be available, such as SpheroCam HDR<sup>1</sup>, or Panoscan MK3<sup>2</sup> In the academic world, Sakakibara et al. [49] introduced a High-Sensitivity CMOS sensor with gain adaptive column amplifiers and 14 bit analogue-digital converters. Zhao et al. [73] capture HDR using the modulo camera. All the above approaches require the availability of special HDR sensors or generally expensive and technologically demanding equipment. Regarding the HDR sensors, it is questionable whether some physical limit in a dynamic range will eventually be reached and what it will be.

The second and more frequently used approach is based on standard sensors/cameras which captures the high luminance range in the scene sequentially, by the acquisition of multiple images typically with varying exposure times [5, 37, 48, 34]; such sequence is then merged into one HDR image. The individual images can be captured simultaneously, e.g. using a beam splitter with several CCD/CMOS sensors [58], or, more often are gathered sequentially using a single image sensor which causes ghost effects by a motion of objects during the sequence acquisition. This approach is technologically less demanding and results in cheaper systems.

<sup>1</sup>https://www.spheron.com/

<sup>&</sup>lt;sup>2</sup>http://www.panoscan.com/

#### HDR acquisition algorithms

Two main approaches how to merge differently exposed standard images into an HDR image exist, the first and more efficient approach involves a combination of pixels in the image domain (direct merging of pixels). As an example, a method presented by Mertens et al. [34] combines multiple exposures directly without any knowledge of the camera response function(CRF). In this approach, only the best parts of frames from each exposure are exploited. A resulting HDR image is obtained as a weighted average of pixel values across the exposures:

$$I_C = \sum_{k=1}^{N} w(Z_k) Z_k \tag{2.1}$$

where  $I_C$  is a composite image,  $Z_k$  is a pixel value and  $w(Z_k)$  is a weight of a pixel. This approach produces the HDR images which can be directly displayed on LDR (Low Dynamic Range) monitors.

The second approach is based on merging in the radiance domain, in the meaning of real illumination in the given scene. Algorithms using this approach are attempting to calculate the exact value of luminance in the scene. These methods require knowledge of the camera response function [5, 48, 37], which is the response function of the camera sensor to the incident light (see Section 2.1). The inverse function of CRF is then applied to obtain an image with approximately linear response to light. The CCD and CMOS technology generally do have a linear response function, but the image results are often affected by postprocessing algorithms, for example, by gamma-correction or by white balance. In general, RAW images are preferable for HDR composition because they contain data obtained directly from CCD/CMOS sensors without any postprocessing, and therefore it can be assumed that they have a linear response function. Unlike the merging in the image domain, this class of algorithms produces an image with higher bit-depth, which is not directly displayable on standard LDR devices. The HDR images have to be post-processed by algorithms commonly called tone mapping operators. The operators reduce the bit-depth of the HDR image while they preserve all important image details.

The first and most straightforward approach is to select the pixels from the longest but still unsaturated exposure. The resulting pixel value in the HDR image is calculated according to equation:

$$L_p = \frac{Z_{longest_p}}{t_{longest}} \tag{2.2}$$

where Lp is the resulting pixel value p from HDR image, the pixel value  $Z_{longest_p}$  is the value of the pixel from image with longest exposure time where pixel is not saturated and  $t_{longest}$  is the exposition time of this image.

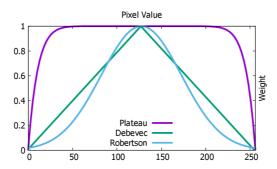

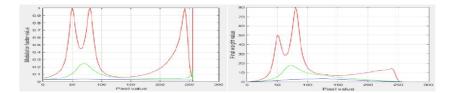

Debevec and Malik [5] proposed an algorithm which can fuse multiple photographs into a high dynamic range radiance map whose pixel values are proportional to the true radiance values in the scene. The contribution of each pixel is determined from the weight function shown in Figure 2.1. Resulting pixel value p in HDR image is calculated as a weighted average of each pixel exposures:

$$L_p = \frac{\sum_{i=0}^{N} w(Z_{ip}) \frac{Z_{ip}}{t_i}}{\sum_{i=0}^{N} w(Z_{ip})}$$

(2.3)

where  $L_p$  is the resulting pixel value p in HDR image, N is the number of input images,  $Z_{ip}$  is the value of a pixel p in image number i,  $t_i$  is the exposure time of image i.

Figure 2.1: Pixel weighting functions proposed by Debevec [5], Robertson [48] and plateau weighting function (from Luminance HDR software<sup>3</sup>).

This algorithm can use various weighting functions. The weight function by Robertson (shown in Figure 2.1) is a Gaussian-like weight function. In the HDR processing applications (e.g. Luminance HDR<sup>3</sup>) the "plateau" function is often used (Figure 2.1) which it is defined as follows:

$$w_z = 1 - (2z - 1)^{12} (2.4)$$

where z is a pixel value. In case of image captured with linear sensor, there is no need of assigning variable weights to pixels in the linear range, except the extreme pixel values, where the pixel value could be distorted.

#### Obtaining camera response function

The camera response curve important information for HDR image creation. CRF is a curve which indicates the conversion relationship between the brightness of the scene and the resulting values of the recorded image. This response is most influenced by the image post-processing in the camera. It's important to work around this process since composing of HDR images require the values with a linear transfer characteristic between the light in the scene and the values in the image.

Analog data from the CCD/CMOS sensor are converted to digital using A/D converters and then further processed in the camera. Range of adjustments varies by camera and its settings. Common modifications include remapping of pixel values (change of contrast and brightness, gamma mapping curve, etc.), colour correction (e.g. increased colour saturation), noise reduction, sharpening, and more. Some of the newer consumer cameras, for example, also carry out the reduction of the optical lens distortion. It is possible to get around these corrections by using the RAW format, supported by some cameras, where the data from the sensor are stored unchanged. RAW output is almost linear, only with a few exceptions:

- The level of black Because of the chip design, charge amplifiers, A/D converters and their noise, the level of black can be shifted from zero upwards. This means that black has a higher value than zero. To eliminate this effect, we have to determine this value and subtract it from the image data.

- Quantization Error in quantization arises during the conversion from analogue to digital values. The converter with a higher number of bits (10, 12, ...) can reduce the absolute error value. Quantization also causes higher inaccuracies in the dark

<sup>3</sup>http://qtpfsgui.sourceforge.net/

values of the image (during the short exposures, the higher range is mapped into a few values near to zero).

• Saturation - Photodiodes on camera sensor have only limited charge capacity, which determines the level of saturation. Above the level of saturation, the camera gives the same numerical response for all values of the input luminance. These values are not applicable for HDR image composing and therefore have to be suppressed, e.g. by using a weighting function.

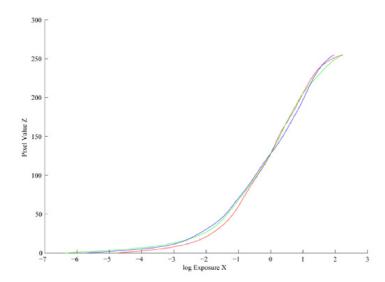

Figure 2.2: Response curve of the Canon EOS 350D (retrieved from http://cybertron.cg.tu-berlin.de/eitz/hdr/).

Several algorithms for calculation/estimation of response function exist if we don't have an opportunity to obtain the picture with a linear response to incident light. The basic method is using a standardized table composed of several fields in grayscale which are photographed and then compared with the camera output. The response function is created from the differences. However, the measurement is complicated because the table must be uniformly illuminated and shall not shine.

#### Algorithm by Debevec

This algorithm is described in the paper Recovering High Dynamic Range Radiance Maps from Photographs [5]. The initial assumption is that the scene is static and the shots are taken so quickly that we can ignore changes in scene illumination. Under these circumstances, we can assume that the intensity of illumination  $E_i$  is constant for each pixel. The values of each pixel will be marked  $Z_{ij}$  where i = 1, ..., N is a one-dimensional index specifying the position of the pixel in the image and j = 1, ..., P is the index across the different exposure times  $\Delta t_j$ . The relationship that exists between the  $E_i$  and  $Z_{ij}$  is defined as:

$$Z_{ij} = f(Ei * \Delta t_j) \tag{2.5}$$

where f is an unknown camera response function which we assume to be monotonous.

Lets define a function g as the natural logarithm inverse to the function:  $g = \ln f^{-1}$ . We get an equation in the form:

$$g(Z_{ij}) = lnE_i + \Delta t_j \tag{2.6}$$

The values of  $Z_{ij}$  and  $\Delta t_j$  are known, lighting  $E_i$  and function g are unknown. The advantage is that searching the function g implies the searching of finite number of values of g(z), where  $z = \langle z_{min}; z_{max} \rangle$  is a finite set of values that pixels can take. The problem is then reduced to a search of finite number of values of g(z) and N values of  $lnE_i$ , which are minimizing the value of the following quadratic optimization function:

$$\mathcal{O} = \sum_{i=1}^{N} \sum_{j=1}^{P} \left[ g(Z_{ij}) - \ln E_i - \ln \Delta t_j

ight]^2 + \lambda \sum_{z=Z_{min}+1}^{Z_{max}-1} g''(z)^2$$

#### Other algorithms

The method presented by Robertson [48] does not put any restrictions on the shape of the resulting response function. This method assumes a Gaussian weight function. Using the Gauss-Siedel iteration, the authors seek the solutions of the objective function which they defined. The method presented by Mitsunaga [37] approximates the camera response function by a polynomial of N-th degree. The authors are looking for coefficients of the polynomial by minimizing the error function, which they defined. The advantages of the method include the ability to determine the exact ratios of exposures. Also, many other methods exist, such as the histogram-based method or a method attempting to derive the response from a single image.

## 2.2 HDR tone mapping

HDR acquisition algorithms produce images which are not directly displayable by current display technologies. The dynamic range of the HDR image has to be compressed to be able to display such an image. Such a process is commonly called tone-mapping. Application of tone-mapping should compress only the range of values; however, the visual information should be preserved – this ability strongly depends on individual algorithms and their properties. This dissertation addresses tone-mapping only marginally; still, a short overview is convenient for the coherence of the topic.

Displaying the HDR content is still a challenging topic, as standard displaying devices are able to represent only a limited dynamic range, typically 8 or 10 bits per channel. To display an image with higher bit-depth, the HDR images have to be post-processed by algorithms commonly called Tone Mapping Operator (TMO) which reduce the bit-depth of HDR image so it can be displayed using standard devices while preserving all important details.

In general, two main approaches to displaying HDR content exist. The first approach is to use specialized HDR monitors that directly render the HDR content; such displays still have some limitations, they are expensive, and they often should be used in a very controlled environment. Thew second approach is based on the application of dynamic range scaling with an effort to reduce the dynamic range but to preserve local contrast in the scene details. This process, as mentioned above, is called Tonemapping (or applying

Tonemapping operators). Many operators exist [9, 47, 11, 6, 31, 7] and they are divided into two main categories - global and local operators.

Global operators use the same mapping function for all pixels of the image. Parametrization of the function depends on global image characteristics, such as average, minimum, and maximum values of luminance.

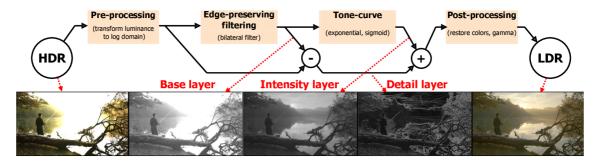

Figure 2.3: Illustration and principled scheme of local tone mapping algorithms (Image retrieved from dataset by Froehlich et al. [13]).

Local operators generally preserve more details than the global ones as they use information from neighbouring pixels to estimate local illumination and thus adapt compression to local luminance conditions. The most frequently used approach is separation of HDR image into base and detail layers (see Figure 2.3). The base layer contains large scale variations of luminance and the detail layer contains local differences, which holds the details of the scene. The base layer can be obtained from luminance in the logarithmic domain by using low-pass edge-aware filtering, e.g. by Bilateral filter (BF), as proposed by Durand [9], Edge-avoiding wavelets [10], or by estimation from gradient domain (Gaussian pyramids [11]). The base layer, which is responsible for high dynamic range, can be compressed because fine details are preserved in detail layer.

#### 2.2.1 HDR compression

High Dynamic Range (HDR) imaging technologies can provide high levels of immersion through a dynamic range that meets and even exceeds the instantaneous range of the Human Visual System (HVS). This increase in the level of immersion comes at the cost of significantly higher bit-rate requirements compared to those associated with conventional imaging technologies. As a result, efficient HDR-relevant coding solutions have to be developed.

Backwards-compatible HDR compression methods are designed so that legacy decoders, which can manage only Low Dynamic Range (LDR) images, are still able to decode and display a tone-mapped version of the HDR image/video. HDR-capable decoders, if available, would be able to decode the full stream and deliver the HDR image experience.

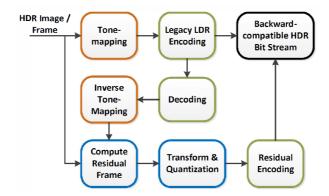

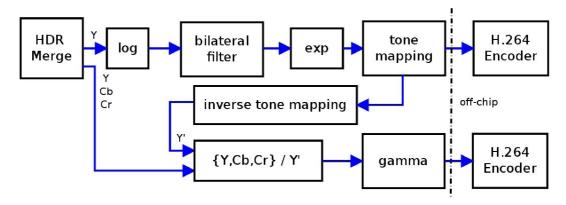

Figure 2.4 shows a block diagram of backward-compatible HDR image and video encoders. The base layer encodes a tone-mapped 8-bit LDR representation of the HDR input using a fully compatible legacy encoder and decoder. The enhancement layer contains the difference (residual) between the inverse tone-mapped base layer and the original HDR input, which is used for reconstructing of HDR content in the HDR devices.

Figure 2.4: General structure of backward-compatible HDR image and video encoders (retrieved from [72]).

#### Backward compatible image compression

At the first place, several methods for encoding HDR images were proposed. In 2004,

Ward and Simmons[65] proposed a backwards-compatible HDR extension for JPEG, whereby the HDR image is tonemapped to an 8-bit LDR image which is then encoded by a legacy JPEG encoder. The ratio image between the original HDR image and the tone-mapped version is down-sampled and stored as a tag in the header file. This ratio image can be used by HDR-capable decoders to reconstruct the HDR content, while all other legacy devices would simply ignore the tag and directly display the tone-mapped LDR image.

Spaulding et al. [53] proposed layered coding for JPEG gamut extension. In the base layer, an image with a clipped colour gamut is encoded. In the enhancement layer, a residual image is formed in a sub-band. This residual image is defined as the arithmetic difference between an input ERIMM RGB colour space image and the encoded sRGB foreground image (limited to 8 bits). The main advantage of the approach proposed in [53] is that the format is backwards-compatible with existing JPEG image codecs.

#### Backward compatible video compression

Mantiuk et al. [32] were the first to propose layered coding for backwards-compatible HDR video compression. Their method was designed as an extension to the MPEG-4 compression standard. The authors introduce a colour space transformation that facilitates comparisons between LDR and HDR pixels. A reconstruction function is then proposed which predicts the value of an HDR pixel based on the value of the corresponding LDR pixel. A non-linear function is used for encoding the HDR residual information. This is then added as side information to the bitstream and can be used by HDR-capable decoders to obtain the full range of visible luminance values. In order to facilitate a smooth transition from LDR to HDR in the decoder, tone-mapping and residual video stream calculation are performed as a preprocessing step before encoding. The novelty of this method is that it employs an advanced Human Visual System (HVS) model to achieve better compression performance. The HVS model selectively pre-filters the residual stream in order to remove imperceptible high spatial frequency information, thus reducing its bit-rate requirements after MPEG-encoding.

Mai et al. [74] proposed a backwards-compatible method that aims to find an optimal tone-curve for mapping the input HDR image/video to a backwards-compatible 8-bit LDR image/video, which can then be compressed by a conventional video codec such as H.264. The reconstructed image/video can then be displayed on a conventional LDR display or can be inverse-tone mapped and augmented by an optional enhancement layer containing an HDR residual signal (also compressed by the codec) for display on an HDR display. The tone-curve optimization aims to minimize the quality loss due to tone-mapping, encoding, decoding and inverse tone-mapping of the original image/video.

## 2.3 HDR deghosting

The HDR merging algorithms [5, 37, 48, 34] summarized in Section 2.1 are suitable for static scenes only. Motion of objects during the image sequence capture causes adverse effects called *ghosting*. To reduce such effects, various methods to detect and remove ghosting from HDR images have been developed.

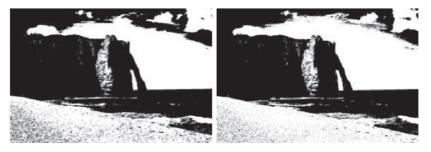

Figure 2.5: Image on the left includes ghosting artifacts, that has to be removed or reconstructed (right). Retrieved from http://www.flickr.com/photos/nuwomb/.

The problem of removing motion artefacts for sequential HDR imaging has been the subject of extensive research and has led to two major type of approaches. The first type assumes that the images are mostly static and that only a small part of the scene contains motion. These de-ghosting algorithms use the input frames to determine whether a given pixel is static or has motion and then apply different merging algorithms in each case. For static pixels, the traditional HDR merge can be used. For motion pixels, many algorithms use only a subset of exposures (in many cases only one) to produce a deghosted HDR. The fundamental problem with these techniques is that they cannot handle scenes with large motion if the moving parts of the scene contain HDR content.

The second type of approaches attempts to align the input sources to a reference exposure before merging them into an HDR image. The most successful algorithms use optical flow to register the images, but even these methods are still brittle in cases of large motion or complex occlusion/dis-occlusion. Since the aligned images produced by these algorithms often do not align to the reference very well, the resulting HDR still contain the ghosting artefacts. For this purpose, the alignment algorithms for HDR often introduce special merging functions that reject the information from aligned exposures in locations where they do not match the reference. In such a case, the HDR content in these regions are not fully reconstructed.

According to the goal of this dissertation, I focused on algorithms feasible of capturing ghost-free HDR images in real-time. Thus I further reviewed mostly simple, computationally unpretentious methods, that could claim the real-time performance. I reviewed mostly the methods categorised by Tursun [59], Srikantha [54] and other authors as "motion object selection" methods. Anyway, a short introduction into the demanding optical flow and patch-based algorithms is presented.

## 2.4 Motion object selection methods

This dissertation work focuses on embedded systems and real-time processing; therefore, only simple, computationally unpretentious methods, categorised by Tursun [59], Srikantha [54] and other authors as "motion object selection" methods are reviewed in this subsection. The optical flow-based and patch-based algorithms are, due to their high computational demands, reviewed only for the coherence of the topic. Also, the global image registration is not addressed, as we assume only static cameras.

In the work of Sidibe et al. [51], the ghosting regions are detected based on the observation that the order relation is given by Equation 2.7 is satisfied for pixels which remain static between two images, and can be broke down for motion pixels. Therefore, they detect possible ghosting regions by checking the order relation between k consecutive images, and by marking pixels for which the relation breaks down at least once.

$$if\Delta t_i > \Delta t_j, \text{ then } L_i > L_j.$$

(2.7)

Where  $\Delta ti$  and  $\Delta tj$  are exposure time of images  $L_i$  and  $L_j$ . This method does not verify the real increment of a pixel value which causes the ghost detection to fail relatively often. The order relation only works if the pixel is not under- or over-exposed. For instance, a white pixel in a shorter exposure will remain white in a longer exposure, and a black pixel in a longer exposure remains black in a shorter one. Therefore, the authors discard under and over-exposed pixels when checking the order relation between consecutive images. Concretely, they exclude pixels which are outside the range [20,..., 240] (for 8-bit pixel values). [51]

Once ghost regions are detected, artefacts-free HDR can be created. For all pixels outside a ghosting region, HDR generation proceeds in a conventional manner, i.e. the pixel value in the HDR is a weighted average of the corresponding pixels in the differently exposed images, as proposed Debevec and Malik [5]. For a pixel inside a detected ghosting region, a common approach is to substitute the pixel value by the corresponding value in the best exposure image for that region. For each region, the best exposure is chosen as the one with the lowest number of under-or over-exposed pixels. Sidibe's method gives

goods results in some cases, it, unfortunately, reduces the dynamic range of the HDR by considering only one exposure. [51]

Sidibe et al [51] claimed that according to experiments on various sequences, the order relation-based method and the predicted colour method give more precise results than the variance-based method. However, the measure of variance works well only if the colour of the moving object is clearly distinguishable from the background.

Kao et al.[22] processes two images with  $\pm 1EV$  difference in exposition times. Since they know exposition time, the following relation between pixel values is expected:

$$L_2(p)/L_1(p) = 2, \Delta t_2 = 2 * \Delta t_1$$

(2.8)

If this relation is not fulfilled, the pixel is marked as a ghost and is omitted from the merging algorithm. The saturated pixels, which are under or over a fixed threshold, are omitted from the ghost detection process too. Kao et al. uses the motion estimation for aligning the source images, which works over macroblocks of  $16 \times 16$  pixels.

Gallo et al. [14] assumes a linear dependency between couples of pixels when they "see" the same radiance levels, based on knowledge of exposure times. The following relation between the images is expected:

$$L_i = L_j \cdot \frac{t_i}{t_j} \tag{2.9}$$

Any image spot violating this linear relation is considered as containing a motion. All images are registered to the reference image  $L_{ref}$ ; to suggest a good reference frame, they find the saturated pixels in each image of the stack, then they remove small saturated regions with morphological operators (erosion followed by dilation) because such area's neighbourhood usually contains enough information to avoid artefacts. Finally, they pick the exposure with the fewest remaining saturated pixels. [14]

The reciprocity assumption states that if the radiance of the scene does not change, the exposure time and the irradiance are linearly related through the exposure time  $\Delta t$ :

$$X = E \cdot \Delta t \tag{2.10}$$

Aside from over and under-saturated pixels, Equation 2.10 should only be violated when the scene changes. Therefore, the equation could be used to decide if the irradiance at a given pixel in the reference frame can be combined with the corresponding pixel in another image in the stack. In practice, however, a small misalignment or imprecise estimation of the camera response function can produce large deviations from this behaviour. [14] To increase a robustness and prevent rising of such artifacts, the algorithm operates on relatively large rectangular patches (e.g. 40x40 pixels) rather than individual pixels. Patches with a large number of not corresponding pixels are omitted from merging, causing visible artefacts to occur at their boundaries; Gallo et al. [14] suggest their suppression by Poisson blending.

Raman et al. [46] extended the work of Gallo et al. [14] so that it does not require any knowledge of the CRF or exposure settings. They introduced an intensity mapping function (IMF) obtained from the static part of the scene – they assume that upper 5-10 image lines are usually static. The authors assume the motion is mostly confined to the ground plane of the scene. This assumption may be very limiting, and it can work only for certain scene compositions.

Grosch [15] proposed a simple method based on the estimation of pixel value from the known exposure time and CRF. In opposite to the most of the algorithms that require a static scene and direct correspondence of pixels to obtain a CRF, Grosch uses the algorithm presented by Grossberg and Nayar [16] to recover a CRF from a non-aligned sequence with object motion. This algorithm calculates the response function based on cumulative histograms and is mostly unaffected by camera or object motion. [15]

With a known camera response function, they can predict the pixel colour from one image to another. For each pair of consecutive images, they test if the real colour in the second image is well approximated with the predicted colour from the first one. If the pixels at the certain position do not fit the estimation, the corresponding region is marked as ghosted into the error map. [15] To increase the robustness and eliminate the influence of the noise in the source images, the author uses a user-defined threshold for the pixel colour comparison.

Wu et al. [66] algorithm estimate the CRF from regions where RGB vectors remain fixed with respect to the changes of exposure. The algorithm refines motion detection by a combination of pixel order relation from Sidibe et al. [51] and pixel value estimation from Grosch [15].

Wang et al. [63] proposed the motion region detection method, that is motivated by the inter-frame difference method for video sequence that does subtraction to compute the difference between adjacent frames on the intensity domain. To enable it, the algorithm normalises all images  $L_i$  according to the reference image  $L_{ref}$ . For each pixel, if the corresponding difference value is bigger than a certain threshold, then the pixel is considered to be in a motion region. This method is commonly used on motion detection of video stream. [63]

The threshold value is determined from median pixel value in each image and is adaptive to avoid certain artefacts – the threshold for the under and over-exposed areas is increasing, because the brightness changes only little in spite of adjusting the exposure levels because it has reached saturation. The bitmaps with detected motion are further strongly refined using morphological operations. The tolerance ratio should also be adjusted by the user to provide the best visual result. [63]

The algorithm of Jacobs et al. [18] is calculating pixel variance over the exposures to detect the presence of motion. The *Variance Image* is created, storing pixel's variance over the exposures in a matrix with the same resolution as input images. Further, they ignore under and over-saturated pixels in *Variance Image*. The *Variance Image* is transformed into binary map (equivalent of *ghostmap*, see on Figure 2.6)), with movement clusters, which are formed by comparing the *Variance Image* with fixed threshold. The *Variance Image* is supplied by *Uncertainty Image*, which is calculated using the local variance, obtained from a histogram of a small 2D window; 5x5 pixels in size [18].

For each movement cluster, they substitute the irradiance values with the irradiance values from only one image. Substituting an entire region with irradiance values from one image introduces artefacts at that region's borders. To reduce these artefacts, they substitute pixel values with *Variance* and *Uncertainty Image* entry above a certain threshold (higher than the threshold used at the movement clusters) with a weighted average of the reference image and the irradiance value from in the selected image. [18]

Pece et al. [44] algorithm extracts median threshold bitmap (MTB [64], see Figure 2.7) from each of the input images. Any difference between the threshold maps of input images and the reference image, presented typically by the mid-exposure one, is marked as a motion-region. To remove the effects of the noise, the motion map is refined using mor-

Figure 2.6: The Figure shows the results of variance based deghosting method by Jacobs et al. [18]. The variance map (bottom left) is obtained from the image sequence (upper row) and used to generate the HDR image (bottom right). Figure obtained from [18].

phological operations such as erosion and dilation. The pixels in the motion-regions are assigned smaller weights during the HDR construction. This method is strongly dependent on scene composition since its reliability is strongly dependent on the median image value. Additionally, the pixels with a value close to the threshold may be falsely detected as ghosts.

Min et al. [35] improved method of Pece et al. [44] and introduced multi-level threshold map, where thresholds are selected to divide the image into multiple regions according to the pixel intensity, each region having the same number of pixels (see Figure 2.8). Any difference between the threshold maps of input images and the reference image, presented typically by the mid-exposure one, is marked as a motion-region. Introduction of multiple histogram regions, in opposite to Pece et al. [44], allows for the incorporation of a tolerance in which shifts of pixels within neighbouring regions are not evaluated as motion. The algorithm suffers from dependence on scene composition and image histogram layout. Min et al. [35] further improved the algorithm in a follow-up article [36] by employing a noise reduction phase, which incorporates an additional set of rules for spatially neighbouring pixels. Unfortunately, the algorithm needs to use a large, performance and memory demanding, spatio-temporal smoothing filter. The above methods by Pece et al. [44] and Min et al. [35, 36] are using coarse morphological operators, such as erosion and dilatation, to suppress false detection rising on edges or by noise.

An et al. [1] proposed a method for multi-exposure fusion without the ghosting effect. The method evaluates the photometric relation of images from sequence to the reference image, producing binary ghostmaps. This ghostmaps are refined using the ZNCC (Zero Mean Normalized Cross-Correlation), which evaluates the similarity of the ghostmap patterns. By default, they use an  $11 \times 11$  patch for photo-metric relation test and a  $33 \times 33$  patch for ZNCC calculation.

Moon et al. [38] published a short article where they proposed HDR fusion method with ghost-free effect. The author claims that the method is intended for embedded devices and

(a) Original Exposures: +2 and -2 stops respectively.

(b) Bitmaps generated by MTB.

Figure 2.7: The Figure shows the two images and corresponding Median Threshold Bitmaps (MTB), proposed by Pece et al. [44]. Figure obtained from [44].

Figure 2.8: The figure presents the intermediate step of deghosting algorithm by Min et al. [35]. The source sequence is on the top, the bottom images shows the multi-level threshold maps for corresponding images on the top. Figure obtained from [35].

fast processing, since it does not require the demanding morphological operations, required by many other algorithms [44, 35, 1] for ghostmaps refinement. They introduced a simpler non-ghostness probability, which is combined with a conventional fusion weight [34] to yield a ghost-free fusion weight. All of the images are photometrically calibrated toward the reference image by an image transform from the result of histogram matching between

the reference image and their individual exposure images. Unlike in their previous work [1], they use "soft" assigned weights instead of binary ghostmaps.

Srikantha et al. [54] propose a method which works on input images with linear CRF. Their work is based on the assumption that if the pixels from different exposures capture a static region of the scene, they must be linearly dependent since they are equal to the multiplication of sensor irradiance and exposure time. The pixels which do not follow the linearity and potentially cause ghosting are found using singular value decomposition (SVD) of a matrix containing pixel intensities from all exposures. This matrix is reconstructed using only the largest singular values, forcing the linearity between the corresponding pixel intensities of different exposures. The reconstructed pixel intensities are used to produce a ghost-free HDR image. [59]

Bouderbane et al. [3] implemented simple ghost removing algorithm on FPGA based platform. They were inspired by the work of Sidibe et al. [51] and presented the algorithm based on the modification of Debevec [5] weighting function. The idea of the methods is to adjust pixel weights based on the deviation from the reference image [51]. The function gives a higher weight for pixels whose value are closed to the reference value and low weight for pixels whose value diverges considerably from a reference value. Consequently, they achieved the same performance as the Debevec and Malik [5] standard algorithm with a ghost removing in a radiance domain, right before HDR data generation. [3]

## 2.5 Motion object registration methods

The following algorithms are not suitable for real-time processing; however, I reviewed them for the coherence of the HDR deghosting topic and also because they are part of the state-of-the-art in terms of deghosting quality. Achieving good visual results comparing to such algorithms is also one of my side-goals.

#### Patch-based algorithms

These approaches attempt to align the different LDR exposures before merging them into the final HDR image. Although the alignment of images has long been studied in image processing and vision communities (e.g. Zitová and Flusser [76]), its application to HDR imaging has special considerations. Here, the input images are not of equal exposure, so the colour constancy assumption of many algorithms is violated. Even if we map images to the same radiance space using the camera response curve (Debevec [5], Mitsunaga [37]), they will have regions that are too dark/light and therefore invalid during the alignment. This makes standard image registration techniques unsuitable for this application. [50]

The quality of the HDR images produced by these techniques is fundamentally limited by the accuracy of the alignment. Even the state-of-the-art optical flow algorithms are brittle in cases with complex motion and occlusions, which is why many use special HDR merging steps to reject misaligned images (as in deghosting) and cannot use standard merging techniques. Furthermore, optical flow cannot typically synthesise new content and thus cannot handle disoccluded content that could be made visible when aligning one image to another. [50]

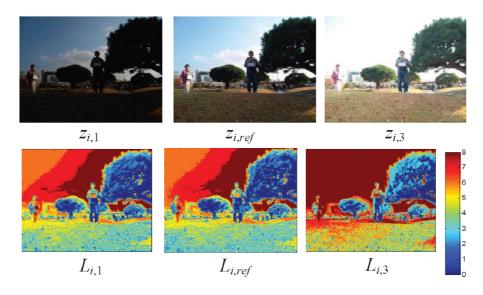

The algorithm proposed by Sen et al. [50] is a patch-based energy minimisation formula. The algorithm produces an HDR image from a set of LDR images captured with different exposures which is aligned to the reference image  $L_{ref}$  and which is also an LDR image that

contains the best-exposed pixels. The resulting HDR image contains as much information as possible from the well-exposed pixels from the  $L_{ref}$  image (see Figure 2.9). In places where  $L_{ref}$  is not well exposed, every patch in the image H at a given exposure should have a similar patch in one of the LDR images after exposure adjustment (coherence). Also, every exposure adjusted patch in all  $L_k$  images should be contained in H at exposure k (completeness). The iterative approach performs joint optimisation of image alignment and HDR merge process until all the exposures are correctly aligned to the reference exposure, and a good quality HDR result is produced.

Figure 2.9: The figure shows the source sequence, images reconstructed by patch-based algorithm by Sen et al. [50] and the resulting HDR image. Image obtained from [50].

Orozco et al. [43] presents a method which consists of both ghost detection and image registration steps. In the ghost detection step, the detection algorithms of Pece [44], Jacobs et al. [18], Sidibe et al. [51] and Grossberg et al. [16] are compared, and it was found that the IMF based ghost detection of Grossberg et al. is the most accurate. In the image registration phase, an intensity-based method without feature detection is employed. The image with the best exposure is selected as the reference image. A bounding box is fitted around the previously detected motion regions. Next, the region in each bounding box is registered by translation and rotation to the reference image. The Sum of Squared Distances (SSD), Normalized CrossCorrelation (NCC), Mutual Information (MI) and MedianBitmap Difference (MBD) are compared as a similarity measure for the registration. The authors state that NCC has the best computational cost and performance. In order to speed up the process, the registration is performed using the pyramid structure of the images, from coarse to fine resolution. However, since the registration applies only translational and rotational transformations, more complex motions caused by objects with deformable bodies are not handled. [59]

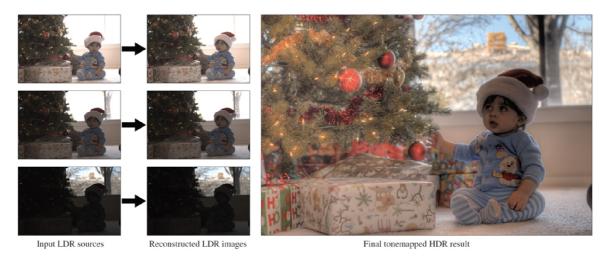

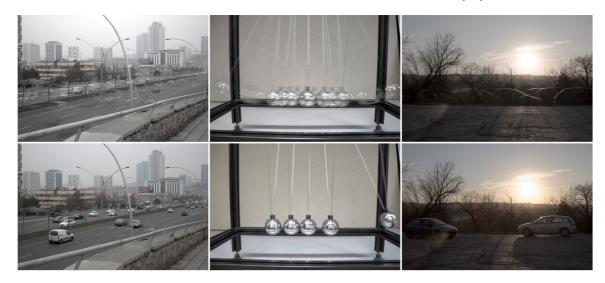

Hu et al.'s more recent work [17] proposes a PatchMatch[2] based HDR reconstruction algorithm with energy minimization (see Figure 2.10). Among the input LDR images, the one with the largest number of well-exposed pixels is selected as  $L_{ref}$ . In the next step, for each input LDR image  $L_i$  a latent image  $T_i$  is synthesised. Latent images are similar to  $L_{ref}$  where it is well-exposed. In under- or over-exposed regions, a matching patch is found using the PatchMatch algorithm in other input images. Using the matching patches and the intensity mapping function obtained with the histogram-based method of Grossberg

Figure 2.10: The figure shows the source sequence (left column), images reconstructed by algorithm by Hu et al. [17] (middle column) and the resulting HDR image (right). Image obtained from [17].

and Nayar[16], the latent images are obtained by minimising the following energy function:

$$\varepsilon(T, \tau, u) = C_r(T, L_{ref}, \tau) + C_t(L, T, u) \tag{2.11}$$

where L, T and u are the sets of input images, latent images and coordinate mappings to matching patches, respectively. The  $C_r$  and  $C_t$  terms measure the radiometric and the texture consistencies between the reference image and the input images, respectively. As opposed to Sen et al. [50], Hu et al. [17] does not require the CRFs of the input images to be linear. In certain comparison studies, it is observed that Hu et al. [17] was more successful at producing noise-free outputs whereas Sen et al. [50] was better at preserving texture details. [59]

#### Optical flow-based algorithms

The approaches in this group are mostly based on optical-flow estimation, which is a well-studied problem, especially in stereo vision applications. In the HDR domain, optical-flow estimation must also take the exposure differences between the input images into account. The accuracy of the estimation is very critical for the quality of the outputs since any mismatch results in undesirable artefacts. In addition, the use of optical-flow presents other challenges such as handling the occlusion, noise, or large displacements in the scene. [59]

Zimmer et al. [75] use state-of-the-art optical flow approach to register LDR exposures before the merging process. They minimise their proposed energy function that uses a data term and smoothness term to reconstruct saturated and occluded areas. After alignment, the displacement fields obtained with subpixel precision are used to produce a super-resolved HDR image. The main advantage of the proposed strategy is that the resulting dense displacement fields can describe arbitrary complex motion patterns, which

is indispensable when dealing with complex camera motions or motion objects in the scene. Another attractive aspect is that they do not require knowledge of the camera response curve or the exposure times. Concerning efficiency, they were able to achieve reasonable run times on sequential CPU architectures, whereas parallel GPU implementations reduce the computation times to a few seconds.

Ferradans et al. [12] find dense correspondence of input images in the radiance domain with respect to the reference image. In order to detect the mismatches in the estimated flow fields, the input images are warped using the estimated fields, and the absolute difference map of each pixel is calculated. Instead of applying a fixed threshold to the difference map, its histogram is modelled as a mixture of Gaussians. The pixel intensities corresponding to the flow vectors causing the mismatch are assigned zero weight in HDR reconstruction. The information from the remaining pixels in each input image is fused in the gradient domain. Jinno and Okuda [19] use a novel weighting function which has significantly smaller overlap between the contribution of input LDR images to the radiance domain. The proposed method assumes that the global alignment is already performed. Displacement, occlusion, and saturation regions are modelled as Markov Random Fields. The optimal parameters are found by minimising the energy function (see [19]). [59]

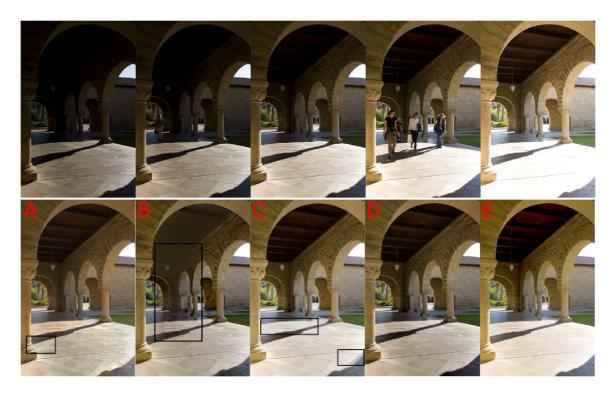

#### CNN based algorithms

The latest published algorithms are based on popular Convolution Neural Networks (CNN). Kalantari et al. [20] based their approach on optical flow from Liu et al. [28] and merges images into HDR using CNN. At first step, the source images are normalised to the same level of luminance as the reference (middle) image – similarly to Wang et al. [63] and many others. Then, the optical flow algorithm of Liu et al. [28] is used to align the images. Such aligned set is merged using CNN network trained on their dataset containing ground truth sequences. The CNN is responsible for removing the ghosting artefacts appearing on the edges of motion regions. Yan et al. [69] proposed a similar approach; however, their proposed CNN uses not only surrounding information of a pixel as Kalantari et al. [20], but also considers the information from other frames.

Figure 2.11: The figure presents the results achieved by Kalantari et al. [20]. From the left – the source sequence, images aligned by optical flow by Liu et al [28], resulting tonemapped images and the details of marked region merged by "simple" merging (probably by Debevec and Malik [5]) and by proposed CNN based method by Kalantari et al. [20].

# Chapter 3

# Embedded HDR acquisition and deghosting

This chapter contains an overview of the state-of-the-art embedded HDR acquisition solutions. The chapter begins with an overview of existing hardware platforms, which are commonly used for the implementation of HDR acquisition, deghosting and tonemapping tasks, further followed with an overview of specialized hardware accelerators and embedded systems, aimed for high-performance processing. The chapter's last section is devoted to the description of state-of-the-art implementations of HDR acquisition and deghosting on embedded devices and description of theirs, mostly custom based embedded platforms.

## 3.1 Embedded platforms and accelerators

This section describes selected hardware platforms that are currently available and are related to the algorithms described in the Chapter 2. The HDR processing algorithms can be implemented and even hardware-accelerated on these platforms. Individual platforms are presented and their benefits and disadvantages for such tasks are summarized. The section begins with a definition of metrics used to enumerate the computing power of individual platforms. Subsequently, the platforms based on CPU, GPU and DSP processors are presented, followed by a description of FPGA circuits. To date, very popular are SoC platforms (System on Chip), where the CPU is located on one chip with the accelerator in the form of GPU (nVidia Tegra), FPGA (Xilinx Zynq) or DSP unit (Google PVC).

#### Performance metrics

Typical performance metrics of computing systems include:

- Computing power

- Memory capacity

- Memory access time

- Power consumption

- Peripheral device support

- Cost

Very important parameters also include development time and overall cost. They are related to the selected platform and its available development, debugging or simulation

tools, the possibility of running an operating system and finally, availability of function libraries.

Large memory and computing requirements are typical for image processing and computer vision tasks. The algorithms are often performing several operations over each pixel. This could be an issue for real-time video processing.

Mainly used metrics are MIPS and MFLOPS, both representing millions of executed instruction per seconds, MIPS is for fixed-point and MFLOPS for floating-point arithmetic instructions.

Algorithms of image processing are often using only simple mathematical operations, such as addition or multiplication. They often do not need a high precision number representation. An 8-bit fixed point or 32-bit floating-point numbers are frequently used for pixel representation. Image processing algorithms are quite well parallelizable in general because the same operations are applied for each pixel/block of the image. This feature allows easy and efficient utilization of parallel computing platforms. It leads to easy computing performance scaling and also to the reduction of cost and power consumption. Then one of the performance metrics could be a number of processor cores or number of parallel operations executed per clock cycle.

Amount of available memory space is often not critical. In most of the cases, one version of the currently processing image have to be held in memory. Some algorithms are requiring more memory space for partition structures and tables storing. Memory capacity metric is a number of bits/bytes, that can be stored in memory. Some image processing algorithms can take advantage of block memory accesses, but on the other hand, some of them need random memory access (mostly algorithms using some partition structures). They have different demands on memory throughput and latency too. Memory throughput is measured on Gb/s. Memory latency shows the time between the start of a memory access request and its finishing. Latency is affected by memory cells speed and mostly by memory system hierarchy. Average memory latency is indicated in nanoseconds (ns).

From the perspective of real system deployment, the overall device cost is one of the most important parameters. This is given by component price, production complexity, development cost and appropriate licence fees. Price is normally expressed in dollars (\$). Price is often related to other parameters, such as computing performance (MIPS/\$, MFLOPS/\$) or memory capacity (Gb/\$) due to different platforms comparison.

To compare with different platforms often price applies to other parameters such as computational performance (MFLOPS per dollar) or memory capacity (GB per dollar).

Development price is affected by the available development, debugging and simulation tools and by existing function libraries. It also depends on targeted technology and on knowledge and experiences among developers.

Power consumption becomes an important metric today, specifying how long can device run on battery, the cost of annual traffic etc. Power consumption is primarily affected by integrated circuits parameters, such as manufacturing technology, the size on the chip, clock frequency and supply voltage. Many platforms have power-saving technology like a dynamic clock frequency/voltage scaling and clock-gating. Power consumption is measured in watts (W). Relative units are also used, such as computing power per watt (MIPS/W).

Another important parameter is the support of peripheral interfaces. Each image processing device requires at minimum an input interface, which is used for retrieving image for processing, and output interface for the representation of the results. Additional interfaces are needed, for example, for communication with other devices. Data throughput is the critical parameter for the input interface, especially in real-time systems. Currently, there

are several commonly used and well-supported interfaces as a PCI Express, Thunderbolt, USB, Firewire and custom high-speed serial link/busses.

A separate issue is a possibility of adapting the computing platform for a specific application. One of the possible options is to use external processing units (e.g. for video decompressing). Another option is to use a self-designed computer system. A typical example is application-specific integrated circuits (ASIC) or programmable gate arrays (PLD, FPGA). This technology allows creating an application-specific computing system to the specific application. Such systems have the best parameters relative to consumption, performance and chip dimensions. Their main disadvantage is the very high development cost. System metrics vary depending on the technology used. Unit of equivalent gates was applied for comparison purposes, indicating the amount of AND and OR gates that we can replace with a specific chip.

#### CPU based platforms

CPUs platforms are designed for general computing. The universal processor allows use in a wide range of applications. CPUs are used as computational units in PCs, servers or some embedded systems. Its main advantage is versatility but counterbalanced with resource requirements (time, power consumption, chip area) comparing to the specialized computing systems. The processor is a complex sequential engine executing algorithms expressed by machine code. The basic part of the processor is the arithmetic logic unit (ALU), cache memory, control unit and IO controller.

Architecture specifics ALU performs operations on the data such as addition, multiplication, division and some logical functions, logical AND, OR and many others. ALU is also driving the program execution, performing a conditional or branching code. ALU is designed to compute with fixed-point numbers only. Floating-point unit (FPU) have to be used for decimal number processing; it is located outside the ALU. Today, in order to reach maximum performance, processors have more ALU units and the FPU is designed for parallel data processing. Processor frequency is today clocked over 4GHz and they can reach the 300,000 MIPS with eight cores and 95W TDP (AMD Ryzen7 1800X). Special server processors have up to 32 cores.

The processor has a fast registry set, where the intermediate results are stored. They operate on ALU frequency and their quantity is limited. On the other side, main memory has huge capacity today, up to 512GB, but it operates on much lower frequencies and with thousand-times bigger latency. This problem is solved by a complex memory hierarchy, where cache memory is embedded to the processor in order to preload and store frequently used memory locations and thus improve memory access latency. The cache is divided to several levels, from L1, which is fastest (latency about 1-3 processor clock cycles) but has the smallest capacity, around 768kB, for L3 with capacity around 8MB (32MB in high-end processors), but with significantly slower access.

Processor's controller unit manages the interaction of individual parts of a processor. Nowadays, it's a very complex and circuit which includes sophisticated algorithms to accelerate processors computing performance by out of order instruction executions, branching code prediction and more.

Currently, there exist two main processor categories applicable to image processing. PC processor architecture is represented mostly by x86 standard compatible processors. Increasingly popular are the ARM-based processors located mostly in embedded systems,

such as mobile phones, tablets etc. The other architectures have a low computing power (embedded systems), minority presence in the market or are not advisable for image processing (server processors).

x86 architecture X86 processors are used primarily in personal computers, notebooks, special embedded systems and servers. They are called CISC processors since they have a lot of very complex instructions in its instruction set. They are based on Intel x86 instruction set, which was first used in the Intel 386 processor and they are fully backwards compatible with this model. The instruction set originally supports only 32-bit operations, but today's processors take advantage of extended AMD64 instruction set with the support of 64-bit operations.

Advantage of these processors is their backward compatibility as the basic instruction set is standardized. This brings an advantage for precompiled software, which is able to run on the newest hardware. On the other hand, backward compatibility is a great bottleneck not only for maximum performance but even to other parameters, like power consumption and even chip size. Overall, they are not quite effective. That's the main reason why there aren't suitable for small and efficiency embedded systems.

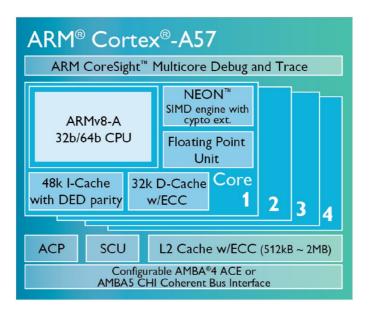

ARM architecture ARM processors (Figure 3.1) becomes popular in small embedded systems. Unlike the x86 compatible processors, their instruction set is RISC and without backward compatibility. RISC means that only basic instructions are supported, which leads to small processor complexity. The ARM instruction set is variable, so only certain instructions could be supported. This leads to a small, effective processor with much lower power requirements compared to x86 processors. That's why their popularity is rising, especially in the embedded and mobile segment. ARM processors are sold by ARM holding as a design file, not as a physical chip. It's quite similar to IP cores for FPGAs(described below). Hence the manufacturer can build his own chip with custom peripherals based on the ARM processor core.

Figure 3.1: Scheme of Quad-core ARM processor A57. Image retrieved from https://www.androidauthority.com/

**Development software** The CPU processors are long supported and widely used so that there exist a huge number of effective development tools in the form of operating systems and their APIs, compilers and libraries, development studios etc. CPU programming is then quite simple and fast, but this applies to one, not to multiple CPU programming. There can be a lot of work with CPU's synchronization. The Windows operating system is primarily designed for x86 processors. On the other hand, Unix based systems are adapted to run on both x86 and ARM architecture.

**Applications** CPUs are quite suitable for most sequential image processing algorithms. It can effectively handle random memory access, needed by tree or list search algorithms, as well as block memory access. Although the CPU is quite effective in this way, overall computing power should be insufficient. Nowadays, the CPUs are equipped by more than sixteen cores in order to reach high computing performance.

#### General purpose GPU

GPGPU, i.e. General-purpose Computing on Graphics Processing Unit is the way of using graphic cards GPU's for general-purpose computing instead of their original purpose, performing graphics operations. GPGPU is supported since 2006 by GPU manufacturers.

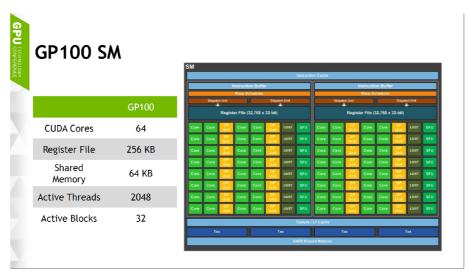

GPU's have a big computing potential. It is composed of several SMP (Streaming Multiprocessor), each containing a large number of CUDA cores, currently up to 64 per SMP, each running up to 1,5GHz (architecture Nvidia Pascal). Each core can provide basic FX arithmetics and memory access operations. Cores within SMP have access to shared memory, registry set and FP(Floating Point) computing units. Computing cores are simplest as possible, so they don't have their own controlling logic. Cores within SMP are divided into several warps, each with own program controller. Whole warp is then executing one source code, so SMP behaves like the multithreaded processor.

Figure 3.2: Schematics of SMP from nVidia Pascal GPU. Image retrieved from https://wccftech.com/nvidia-pascal-specs/.

The graphic card usually contains a large amount of memory on board, currently up to 11GB. To provide as most data bandwidth as possible, multiple cache levels and techniques are applied. All SMP processors share global memory and up to 4096kB L2 data

cache(Pascal). Every SMP have its L1 cache (up to 64kB) shared between all Cuda cores. They also contain a small texture cache that can be used for some special operations.

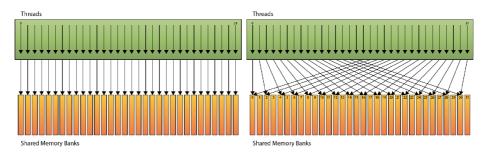

Architecture specifics In general, GPU has extreme computing power but extreme power consumption too. They can reach up to 10,6 TFLOP, currently with 300W TDP, but could be a serious problem to reach such a performance in a real application. Cores within SMP are further divided to warps which are driven by the common controller, so every core in warp is typically executing the same instruction. If a program contains some branching instructions, as "if-else" or "case" statements, the controller has to selectively enable or stop some threads to allow executing of the relevant part of code statement for each core. GPU is capable of running a lot of threads in parallel, so it can process a huge amount of data. The memory subsystem is designed for a high load, but the programmer has to take care of a proper global memory access attitude. Ideally, threads have to gather memory accesses, memory cells required by individual threads should be adjacent. Access with inappropriate stride can rapidly decrease memory throughput. For better performance, access to global memory should be aligned to 128B memory segment.

Shared memory is divided into multiple banks to increase throughput. The proper attitude is to access memory cells by stride 1 or by the stride of the prime number. This results in 1:1 assignment within banks and threads of the warp. Different stride leads to worse ratio and in the worst case to serialize memory requests. In case of reading one memory cell by all threads, exists a built-in memory broadcast mode.

Figure 3.3: Shared memory bank access. On the left is the example of Linear addressing, causing no bank conflict. Two-way conflict is on the right, leads to two memory accesses instead of one in linear addressing.

**Development software** Currently, there are two programming platforms for GPGPU, Nvidia CUDA and OpenCL. CUDA is developed and supported by Nvidia company, one of the graphic card manufacturers, therefore is available only for Nvidia Graphic cards. CUDA SDK contains large libraries for easier application development. OpenCL is a more general platform and supports GPU of any manufacturer. Moreover, OpenCL can utilize not only GPUs but even CPU for computation. Both platforms are based on C language with additional extensions.

**Applications** Types of algorithms suitable for running on GPUs are clear from its specific architecture. High performance can be reached on per pixel or local image operations, such as image filters. On the other hand, it can be a problem to write effectively a tree search algorithms, algorithms with random memory access, algorithms with if-else statements etc.

#### **DSP** processors

DSP is a shortcut for Digital Signal Processor. It is primarily designed for real-time signal processing. Currently, DSP processors are used for example, at mobile phones (GSM signal coding/decoding), DVD drives, cameras etc.

DSP is based on Harvard architecture and thus has a separated instruction and data memory. This leads to better throughput because every memory has its own bus. To maximize computing power, DSP has several parallel processing units, so in every clock cycle can be executed more than one instruction. Typically, there are more ALUs, MAC Multipliers and data load/store units. DSP also has two or more DAG (Data Address Generator) and a lot of DMA units. DAG unit is capable of advanced memory addressing, such as a round buffer addressing, reverse addressing, stride memory access etc. There are two basic types of DSP, divided by used arithmetics. DSP's are either calculating with fixed or a mix of fixed/floating-point arithmetics. Fixed points performance of one DSP core is currently up to 8 MACS(multiple and accumulate) per clock cycle. Floating-point DSPs have approximately half of this performance, up to 4 FLOPS/clock cycle. L2 cache memory is currently about 4MB per core. TDP of one core is highly dependent on desired performance, from less than 0.1W up to 7W. Nowadays DSP processors can have up to 4 cores and run above 1.2GHz frequency.

Architecture specifics Real-time signal processing is the main utilization of DSP processors, so their architecture is adapted to meet such criteria. One of the great advantages is the presence of multiple computation units capable of parallel processing, which allows easy hardware loop unrolling. DSP is using a long instruction word (VLIW). One instruction is composed of several instructions, each for one processing unit. If a source code contains data-independent instructions, they can be executed simultaneously. This is solved by the compiler, which has to take into account the number of processing units, length of instruction execution and possible data dependencies. This implies that a compiled code is not compatible with different DSP processors. Not all of the processing units can be busy at the time, so the DSP long instruction can contain some NOP instructions. This can have a bad impact on DSP's performance.

The bottleneck of DSP processors is conditional code executing, for example, if-else or case statement. It is solved by preliminary selection of branch code and incidental execution of recovery code. In this case, code cannot be effectively parallelized.

**Applications** Primary DSP orientation is on real-time signal processing, it's design is quite customized for this purpose. Applications based on FFT, signal coding/decoding, signal compression tasks are very effective on DSP. Algorithms effective on DSP are commonly based on block or stream processing, loops etc. There can be easily achieved parallel execution, loop unrolling and DAG unit utilization. On the other hand, significantly ineffective could be algorithms based on random memory access and if-else and case statements, for example, tree searching algorithms.

**Development tools** Typically, DSP BIOS is running on DSP chips. It is a kind of real-time operating system (RTOS), which cares about low-level system events, task priorities and provides a simple API for a custom application. C or C++ compilers are available for DSP programming.

## 3.2 System-on-chip platforms

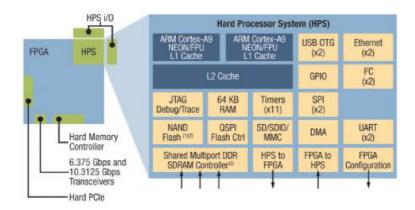

SoC architectures, sometimes also known as an application services platform (ASP), are a combination of existing architectures described above. Typical hybrid systems are composed of several interconnected chips. Nowaday the CPU + GPU, CPU + FPGA and DSP + FPGA cooperation for signal processing is quite common. A Brand new way is to embed more computing architectures into one chip. Xilinx Zynq SoC and Nvidia Tegra are a typical example of a useful combination of the multi-core ARM processor and FPGA, respectively GPU.

#### SoC FPGA - Xilinx Zynq

Architecture specifics Xilinx Zynq is a combination of dual-core ARM processor core (and other peripherals, such as memory controllers etc.) with a standard FPGA chip. Both parts can run on different frequencies, so ARM can run on 677MHz and is not decelerated by the slow FPGA clock frequency. Both parts are interconnected through standard AXI bus and share RAM memory. Moreover, the FPGA can be directly connected even to the ARM cache memory. The ARM processor has a 64kB L1 and 512kB L2 cache memory shared between cores. The standard way to communicate between ARM and FPGA is to make a memory-mapped device connected directly to the AXI bus. This device is then configured from the ARM processor and serves as a coprocessor or independent system with access to system memory, like a graphic card on PC. Zynq is an excellent combination of two totally different architectures. ARM CPU is quite suitable for any sequential algorithm. On the other hand, FPGA has a great parallel computing potential but executing of standard sequential code is almost impossible and have to be solved by IP cores processors.

**Development tools** A big advantage of the Zynq platform is the capability of running a Linux operating system. So there exists a lot of development studios, standalone code compilers and development libraries just like for Linux desktop operating system. Xilinx Company provides support for FPGA part, including IP cores for easy AXI bus connection. They also developed a basic Linux distribution with several examples of interconnecting both parts of a chip.