# BRNO UNIVERSITY OF TECHNOLOGY VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

DEPARTMENT OF RADIO ELECTRONICS

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ ÚSTAV RADIOELEKTRONIKY

### FAST BEAM CURRENT CHANGE MONITOR FOR THE LHC

MĚŘENÍ RYCHLÝCH PROUDOVÝCH ZMĚN ČÁSTICOVÉHO SVAZKU URYCHLOVAČE LHC

MASTER'S THESIS DIPLOMOVÁ PRÁCE

AUTHOR JAN KRÁL

AUTOR PRÁCE

SUPERVISOR Ing. DAVID BĚLOHRAD, Ph.D. VEDOUCÍ PRÁCE

### VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

Fakulta elektrotechniky a komunikačních technologií

Ústav radioelektroniky

## Diplomová práce

magisterský navazující studijní obor Elektronika a sdělovací technika

Student:

Bc. Jan Král

ID:

125500

Ročník:

2

Akademický rok:

2013/2014

#### **NÁZEV TÉMATU:**

Měření rychlých proudových změn částicového svazku urychlovače LHC

#### POKYNY PRO VYPRACOVÁNÍ:

Seznamte se se systémem ochrany urychlovače LHC proti rychlým ztrátám částicového svazku (FBCCM). Navrhněte FBCCM a vhodnou metodu pro jeho komunikaci s řídicím systémem urychlovače LHC. Při návrhu zohledněte dostupné hardwarové prostředky, jednoduchost řešení a zavedené komunikační protokoly.

Realizujte navržené zařízení a jeho komunikační protokol s řídicím systémem urychlovače LHC. Navrhněte metodiku automatického měření zařízení v laboratoři a toto zařízení v praxi navrženou metodou otestujte.

#### DOPORUČENÁ LITERATURA:

[1] Cyclone III Device Handbook [online]. Vydáno: 2012, [cit. 5.6.2013]. Dostupné z: <a href="http://www.altera.com/literature/hb/cyc3/cyclone3\_handbook.pdf">http://www.altera.com/literature/hb/cyc3/cyclone3\_handbook.pdf</a>

[2] Sitara AM335x ARM Cortex-A8 Microprocessors [online]. Vydáno: 2013, [cit. 5.6.2013]. Dostupné z: <a href="http://www.ti.com/lit/ds/sprs717f/sprs717f.pdf">http://www.ti.com/lit/ds/sprs717f/sprs717f.pdf</a>>

Termín zadání: 10.2.2014 Termín odevzdání: 23.5.2014

Vedoucí práce: Ing. Michal Kubíček, Ph.D.

Konzultanti diplomové práce:

doc. Ing. Tomáš Kratochvíl, Ph.D.

**UPOZORNĚNÍ:** Předseda oborové rady

Autor diplomové práce nesmí při vytváření diplomové práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

### **ABSTRACT**

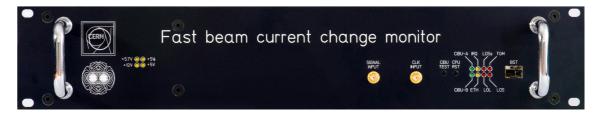

Stringent demands on the LHC safety and protection systems require improved methods of detecting fast beam losses. The Fast Beam Current Transformer (FBCT) is a measurement instrument, providing information about bunch-to-bunch intensity of the accelerated beam. This thesis describes the development of a new protection system based on the FBCT signal measurements. This system, the Fast Beam Current Change Monitor (FBCCM), measures the FBCT signal in a narrow frequency band and computes time derivation of the beam signal magnitude. This derivation is proportional to the beam losses. When the losses exceed a certain level, the FBCCM requests a beam dump in order to protect the LHC. The LHC protection will be ensured by four FBCCMs which will be installed into the LHC in July 2014. Six FBCCMs have been already constructed and their characteristics were measured with satisfactory results. The FBCCMs were tested by a laboratory simulation of the real LHC environment.

### Keywords

Fast Beam Losses, Beam Intensity Measurement, FPGA, BeagleBone, DMA, Ethernet

### **ABSTRAKT**

Striktní nároky na systémy ochrany a zabezpečení LHC vyžadují vylepšené metody detekce rychlých ztrát částicového svazku. Rychlý proudový transformátor (FBCT) je měřicí přístroj poskytující informaci o intenzitě shluků urychlovaných částic. Tato diplomová práce popisuje vývoj nového systému ochrany LHC založeného na měření signálu FBCT. Tento systém, monitor rychlých proudových změn částicového svazku (FBCCM), měří signál FBCT v úzkém frekvenčním pásmu a počítá časovou derivaci okamžité amplitudy tohoto signálu. Tato derivace je přímo úměrná ztrátám částicového svazku. Pokud ztráty svazku překročí určitou úroveň, FBCCM přikáže kontrolním systémům zničit svazek kvůli bezpečnosti LHC. Ochrana LHC bude zabezpečena čtyřmi FBCCM, které budou instalovány do LHC v červenci 2014. Bylo zkonstruováno a testováno šest FBCCM. Jejich měřené charakteristiky vyhovují stanoveným požadavkům. FBCCM bylo vyzkoušeno laboratorní simulací reálného prostření LHC.

### Klíčová slova

Rychlé ztráty částicového svazku, měření intensity částicového svazku, FPGA, BeagleBone, DMA, Ethernet

### **DECLARATION**

I declare that I have made my Master's Thesis, with the subject of *Fast Beam Current Change Monitor for the LHC*, independently, under supervision of my supervisor, using the technical literature and the other information sources which are all cited in the text and enumerated in the list of the references at the end of this thesis.

In Brno, 23 May 2014

Jan Kral

### **Bibliographic Citation**

KRAL, J. Fast Beam Current Change Monitor for the LHC. Master's Thesis. Brno: Brno University of Technology, Faculty of Electrical Engineering and Communication, 2014. 100 p. Supervisor David Belohrad

### ACKNOWLEDGEMENT

I would like to express my sincere gratitude to my supervisor David Bělohrad for his invaluable technical advice and excellent management abilities. I could not have succeeded without his encouragement. The most difficult challenge for me was the initiation into the use of Emacs and the Linux OS. Today, I am glad that he convinced me to use these better methods. However, I could not have used these systems effectively without his advice and guidance. Last but not least, David, thank you very much for being a great friend.

My gratitude also belongs to my university supervisor Michal Kubíček for his administrative work and helpful advice concerning the study issues.

I would like to thank all my colleagues at CERN for creating a good working environment and for provided help. Especially I thank Josef Kopal and Pavel Fiala for taking the photo documentation of our project.

I would like to also thank for the offered opportunity to measure in the laboratories aided by the SIX project, the registration number CZ.1.05/2.1.00/03.0072, the operational program Research and Development for Innovation,

## CONTENTS

| Introduction |               |                                                 |    |  |

|--------------|---------------|-------------------------------------------------|----|--|

| 1            | Lar           | ge Hadron Collider                              | 4  |  |

|              | 1.1           | Theory of Accelerator Operation                 | 4  |  |

|              | 1.2           | Fast Beam Current Transformer                   | 6  |  |

|              | 1.3           | Beam Synchronous Timing                         | 7  |  |

|              | 1.4           | General Machine Timing                          | 7  |  |

|              | 1.5           | Beam Interlock System                           | 7  |  |

|              |               | 1.5.1 User Interface of the BIS                 | 8  |  |

|              | 1.6           | Fast Beam Current Change Monitor                | 8  |  |

|              |               | 1.6.1 The First Prototype                       | 10 |  |

|              |               | 1.6.2 The Final Version of the FBCCM            | 11 |  |

| 2            | FBO           | CCM Hardware                                    | 14 |  |

|              | 2.1           |                                                 | 14 |  |

|              |               |                                                 | 15 |  |

|              |               |                                                 | 15 |  |

|              |               |                                                 | 21 |  |

|              |               | 2.1.4 Clock Low-Pass Filter                     | 21 |  |

|              |               |                                                 | 24 |  |

|              |               | 2.1.6 Clock Termination                         | 24 |  |

|              |               | 2.1.7 TTC Receiver                              | 27 |  |

|              |               | 2.1.8 Indicators and Controls                   | 28 |  |

|              |               | 2.1.9 Serial Number                             | 30 |  |

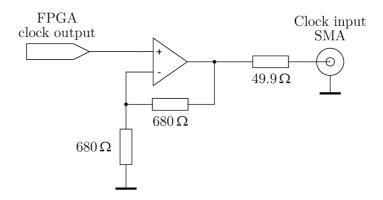

|              | 2.2           | CPU Subsystem                                   | 30 |  |

|              |               | 2.2.1 BeagleBone                                | 31 |  |

|              |               | 2.2.2 Client Interface for CIBU                 | 32 |  |

|              |               | 2.2.3 Clock Input and Output, Telegram Receiver | 33 |  |

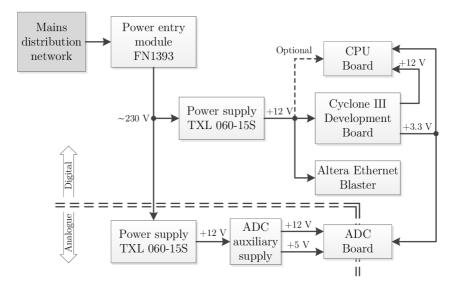

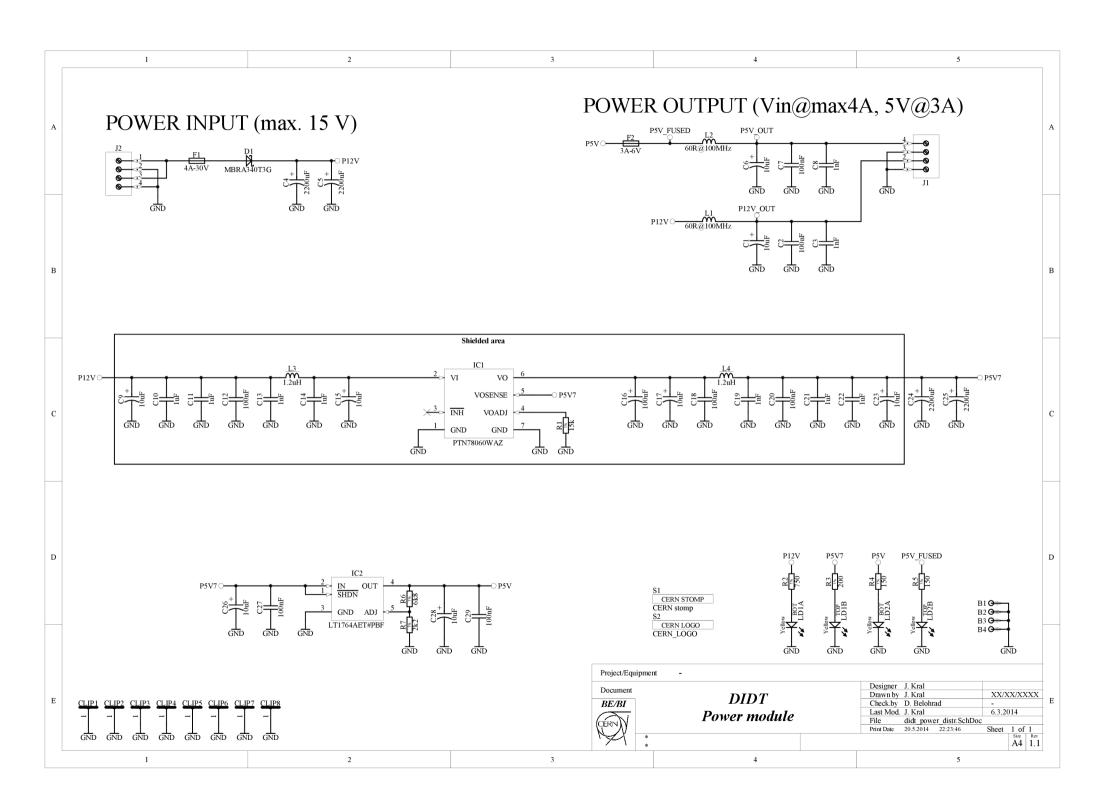

|              | 2.3           | FBCCM Electric Power Distribution System        | 35 |  |

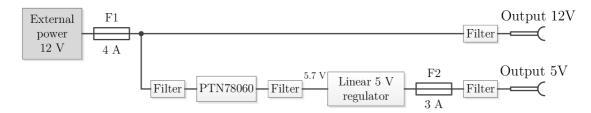

|              |               | 2.3.1 ADC Auxiliary Power Supply                | 36 |  |

|              |               | 2.3.2 Power Distribution of the ADC Subsystem   | 37 |  |

|              |               | 2.3.3 Power Distribution of the CPU Subsystem   | 38 |  |

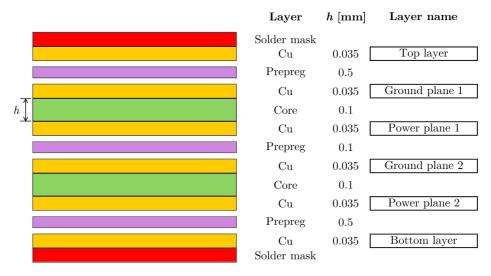

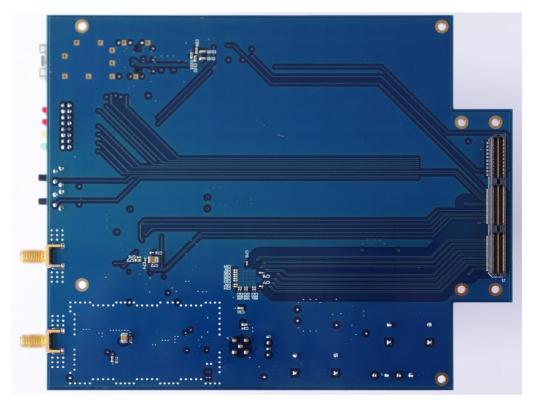

|              | 2.4           | PCB Design of the FBCCM Subsystems              | 40 |  |

|              |               | 2.4.1 PCB of the ADC Subsystem                  | 40 |  |

|              |               | 2.4.2 PCB of the CPU Subsystem                  | 41 |  |

|              | 2.5           | Mechanical Design                               | 41 |  |

| 3            | $\mathbf{FP}$ | GA Firmware                                     | 43 |  |

|              | 3.1           | Top Entity                                      | 43 |  |

|              | 3 9           | DIDT Master                                     | 44 |  |

|            |                                      | 3.2.1 FIFO Buffer                                                                                                                                                                                                                                                                                                                                                     | 45                                                 |

|------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|            |                                      |                                                                                                                                                                                                                                                                                                                                                                       | 46                                                 |

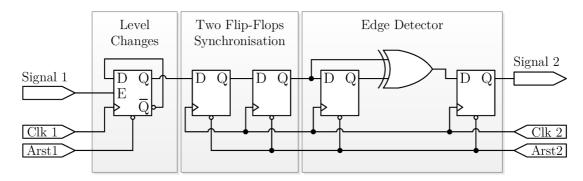

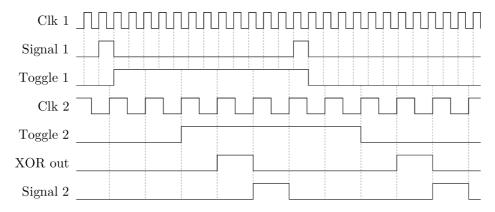

|            |                                      | 3.2.3 Turn Flag Synchronisation                                                                                                                                                                                                                                                                                                                                       | 54                                                 |

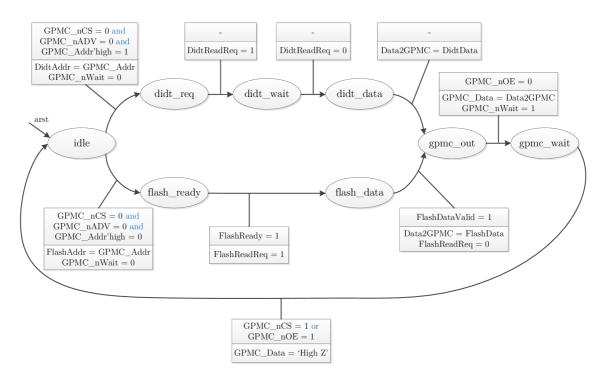

|            | 3.3                                  |                                                                                                                                                                                                                                                                                                                                                                       | 55                                                 |

|            |                                      |                                                                                                                                                                                                                                                                                                                                                                       | 55                                                 |

|            |                                      | 3.3.2 BeagleBone Entity                                                                                                                                                                                                                                                                                                                                               | 56                                                 |

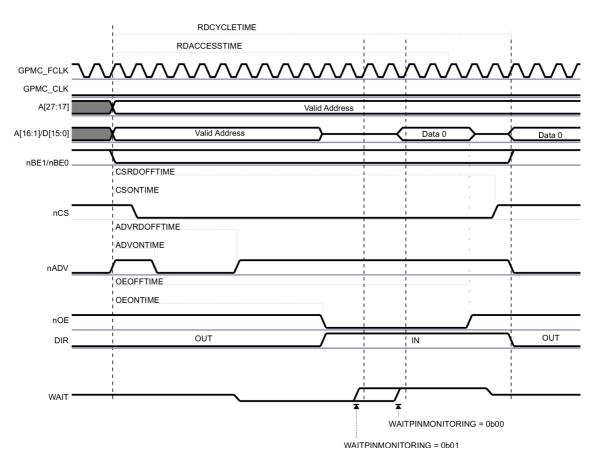

|            |                                      |                                                                                                                                                                                                                                                                                                                                                                       | 57                                                 |

|            | 3.4                                  | Flash Data Upgrade                                                                                                                                                                                                                                                                                                                                                    | 60                                                 |

| 4          | Bea                                  | gleBone Software                                                                                                                                                                                                                                                                                                                                                      | 61                                                 |

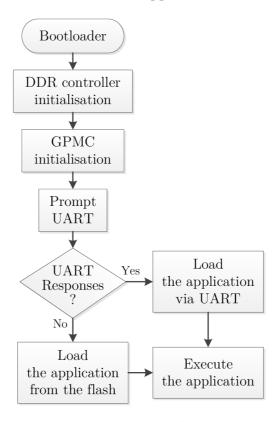

|            | 4.1                                  | BeagleBone Bootloader                                                                                                                                                                                                                                                                                                                                                 | 61                                                 |

|            | 4.2                                  | BeagleBone Main Application                                                                                                                                                                                                                                                                                                                                           | 62                                                 |

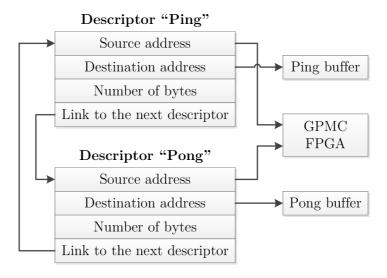

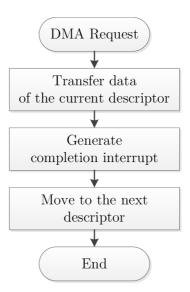

|            |                                      | 4.2.1 DMA Module                                                                                                                                                                                                                                                                                                                                                      | 63                                                 |

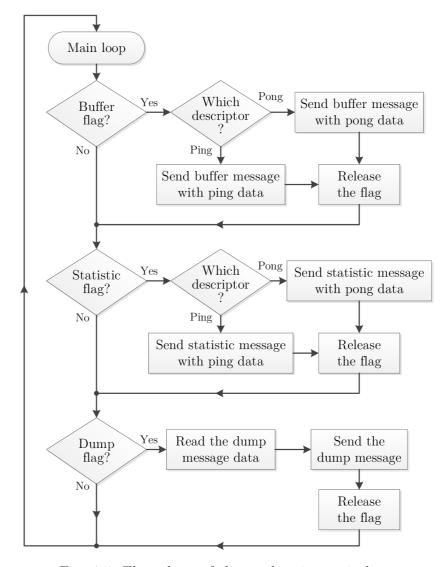

|            |                                      | 4.2.2 Main Loop                                                                                                                                                                                                                                                                                                                                                       | 65                                                 |

|            |                                      | 4.2.3 FBCCM Server                                                                                                                                                                                                                                                                                                                                                    | 66                                                 |

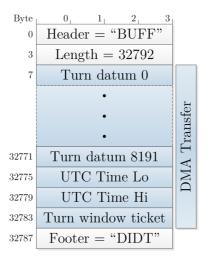

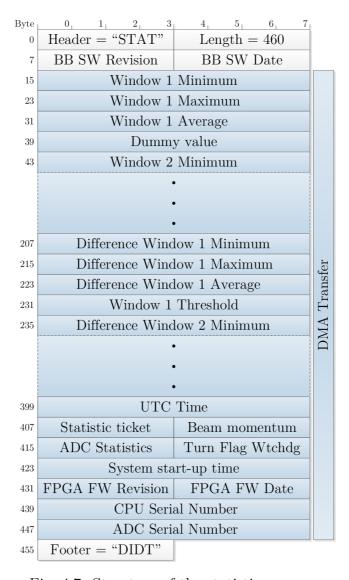

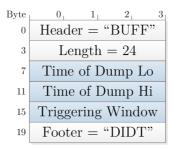

|            |                                      | 4.2.4 Structure of the FBCCM Messages Sent to Clients                                                                                                                                                                                                                                                                                                                 | 67                                                 |

| 5          | FBO                                  | CCM Measurements                                                                                                                                                                                                                                                                                                                                                      | 70                                                 |

|            | 5.1                                  | Measurements of the RF Front End Characteristics                                                                                                                                                                                                                                                                                                                      | 70                                                 |

|            | 5.2                                  | Laboratory Simulation of Losses                                                                                                                                                                                                                                                                                                                                       | 72                                                 |

| 6          | Con                                  | nclusion                                                                                                                                                                                                                                                                                                                                                              | 75                                                 |

| D,         | efere                                | neos                                                                                                                                                                                                                                                                                                                                                                  | 76                                                 |

| TIG        |                                      | nces                                                                                                                                                                                                                                                                                                                                                                  | , 0                                                |

|            |                                      |                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

| Li         | st of                                | Abbreviations                                                                                                                                                                                                                                                                                                                                                         | 78                                                 |

| Li         | st of                                | Abbreviations                                                                                                                                                                                                                                                                                                                                                         |                                                    |

| Li:<br>Li: | st of                                | Abbreviations Figures and Tables dixes                                                                                                                                                                                                                                                                                                                                | 78<br>80<br>83                                     |

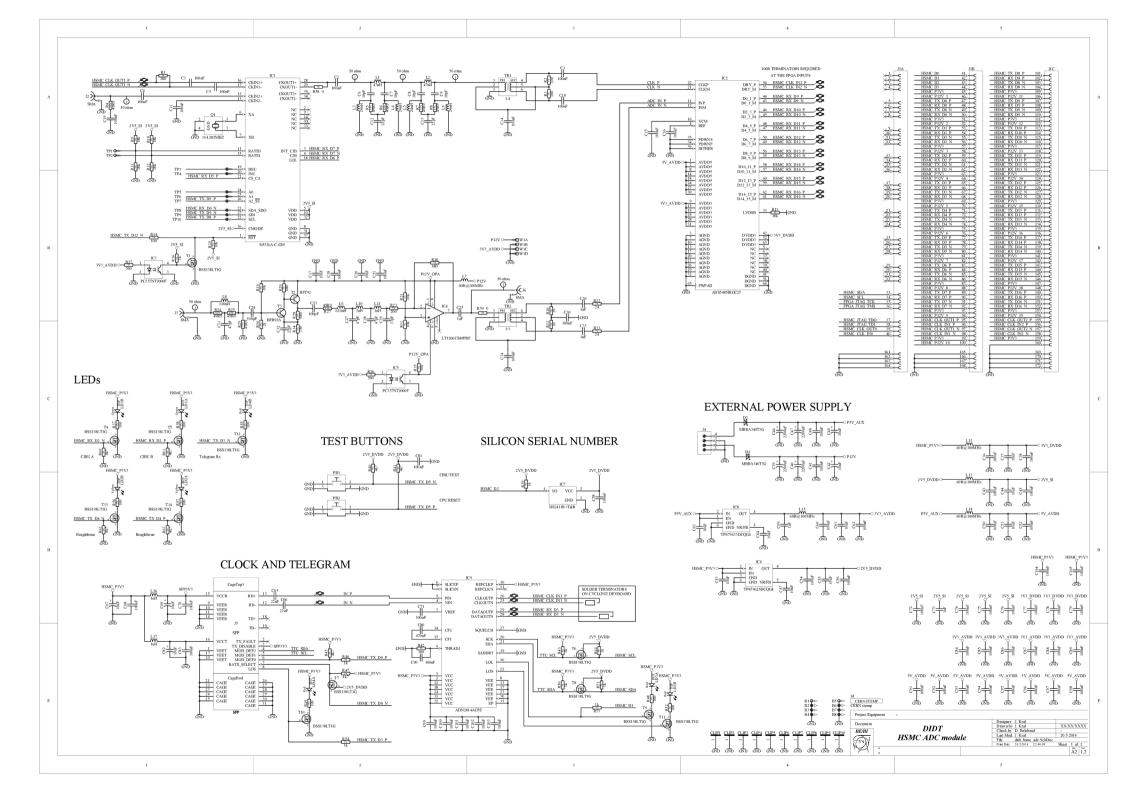

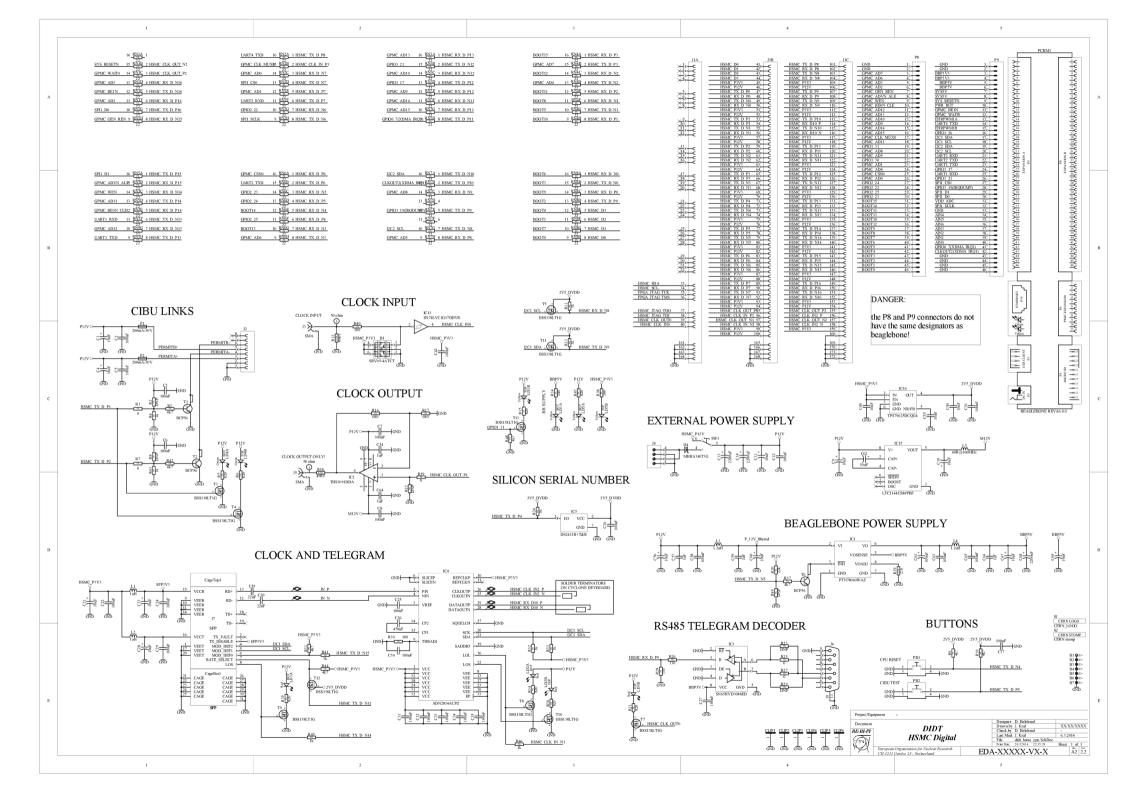

| Li:<br>Li: | st of<br>st of<br>ppen<br>A.1        | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems                                                                                                                                                                                                                                                                                      | 78<br>80<br>83                                     |

| Li:<br>Li: | st of<br>st of<br>ppen               | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems                                                                                                                                                                                                                                                                                      | <b>78</b><br><b>80</b><br><b>83</b><br>83          |

| Li:<br>Li: | st of<br>st of<br>ppen<br>A.1        | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems                                                                                                                                                                                                                                                                                      | <b>78</b><br><b>80</b><br>83<br>87<br>87           |

| Li:<br>Li: | st of<br>st of<br>ppen<br>A.1        | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems                                                                                                                                                                                                                                                                                      | <b>78 80 83</b> 87 87                              |

| Li:<br>Li: | st of<br>st of<br>ppen<br>A.1<br>A.2 | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems                                                                                                                                                                                                                                                                                      | <b>78 80 83</b> 87 87 89                           |

| Li:<br>Li: | st of<br>st of<br>ppen<br>A.1<br>A.2 | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems  Photographs of FBCCM Subsystems  A.2.1 Photographs of the ADC Subsystem  A.2.2 Photographs of the CPU Subsystem  A.2.3 Photographs of the ADC Auxiliary Power Supply  Pictures of the FBCCM Mechanical Model                                                                        | <b>78 80 83</b> 87 87 89 91                        |

| Li:<br>Li: | st of<br>st of<br>ppen<br>A.1<br>A.2 | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems  Photographs of FBCCM Subsystems  A.2.1 Photographs of the ADC Subsystem  A.2.2 Photographs of the CPU Subsystem  A.2.3 Photographs of the ADC Auxiliary Power Supply  Pictures of the FBCCM Mechanical Model  Photographs of the FBCCM Device                                       | <b>78 80 83</b> 87 87 89 91 93                     |

| Li:<br>Li: | st of<br>st of<br>ppen<br>A.1<br>A.2 | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems Photographs of FBCCM Subsystems A.2.1 Photographs of the ADC Subsystem A.2.2 Photographs of the CPU Subsystem A.2.3 Photographs of the ADC Auxiliary Power Supply Pictures of the FBCCM Mechanical Model Photographs of the FBCCM Device VHDL Codes                                  | 78<br>80<br>83<br>87<br>87<br>89<br>91<br>93<br>95 |

| Li:<br>Li: | st of<br>st of<br>ppen<br>A.1<br>A.2 | Abbreviations  Figures and Tables  dixes  Schematic Diagrams of FBCCM Subsystems  Photographs of FBCCM Subsystems  A.2.1 Photographs of the ADC Subsystem  A.2.2 Photographs of the CPU Subsystem  A.2.3 Photographs of the ADC Auxiliary Power Supply  Pictures of the FBCCM Mechanical Model  Photographs of the FBCCM Device  VHDL Codes  A.5.1 FIFO Buffer Entity | <b>78 80 83</b> 87 87 89 91 93                     |

### INTRODUCTION

The Large Hadron Collider (LHC) is the largest and the most powerful particle accelerator in the world. LHC safety and protection is taken very seriously, especially after the damage to the LHC caused by a magnet quench in September 2008. After four years of operation, the LHC is currently in the Long Shutdown 1 (LS1) and many of its systems are being extensively upgraded. The main goal of the upgrade is to reach the nominal beam energy of 7 TeV instead of 3.5 TeV currently used. With circulating beams at twice energy, the LHC will be more vulnerable to the beam losses. Therefore the machine protection systems need to be absolutely reliable. The fast intensity measurement provided by the Fast Beam Current Transformers (FBCT) is used to measure fast beam loss and to implement a second level of beam loss protection in addition to the primary machine protection system based the Beam Loss Monitors [1].

This thesis focuses on the design, implementation and testing of the Fast Beam Current Change Monitor (FBCCM), fast beam loss detection system. The thesis is structured into the chapters. The first chapter briefly introduces the LHC operation, the FBCT intensity measurements and the other systems which the FBCCM is dependent on. This chapter also discusses the principal FBCCM operation, the first prototype of the FBCCM and the final concept of the FBCCM.

The principal FBCCM algorithm requires the digital processing of the FBCT signal. This processing is implemented in the FPGA of the Cyclone III Development Board. The analogue FBCT signal is converted for the digital processing by a dedicated electronic subsystem. The results of the signal processing are sent to the CERN Control Systems using the Ethernet network. The Ethernet interface is implemented by the microprocessor module BeagleBone. The BeagleBone is a part of another subsystem developed and described in this thesis.

The hardware development of the electronic subsystems is described in the second chapter. The third chapter looks into the implementation of the selected parts of the FPGA firmware. The BeagleBone software providing the FBCCM with the communication interface is examined in the fourth chapter.

Four FBCCMs will be installed in the LHC in July 2014 and be fully operational before the end of the Long Shutdown 1. Before installation, all the FBCCMs must be extensively tested in the laboratory to verify their functionality. Automatic testing methods were proposed and the FBCCMs were tested using these methods. The measurements and the testing are subjects of the fifth chapter.

The last chapter summarises the achievements of this thesis and presents following plans for the FBCCM project.

### 1 LARGE HADRON COLLIDER

Particle accelerators are devices generating high speed particles which are required in many diverse disciplines including fundamental and applied research, but also in industrial fields. Low-energy machines are for example cathode ray tubes frequently used in old screens or X-ray scanners in medicine and industry. Nuclei accelerated at lower energies are also used in the medicine as particle therapy, for treatment of cancer. Contrarily the high-energy particles are mainly provided for high-energy physics where experiments with them help nuclear physicists to explore new relations between elementary particles and extend knowledge of fundamental constituents of matter.

The Large Hadron Collider (LHC) belongs to the second category. Currently it is the most powerful and the largest collider in the world. It was built by the European Organization for Nuclear Research (CERN) and it is situated on the border between Switzerland and France close to Geneva. Its main purpose is to allow the physicists to test predicted theories of particle physics and based on results from experiments to prove or disprove these predictions. The monumental achievement of the LHC till now is the confirmation of the Higgs boson existence [1].

### 1.1 Theory of Accelerator Operation

Nowadays the particles in accelerators are accelerated by the electric field, whereas the magnetic field adjust the trajectory of the accelerated particles. To interact with the electromagnetic field, the accelerated particles have to be electrically charged, e.g. protons, electrons, and ions. The particles are accelerated in the vacuum, because otherwise they would collide with atoms of air and their acceleration would not be possible.

The trajectory of particles in the accelerator can be either circular or linear. Each type of trajectory has its advantages and disadvantages. The circular accelerators can benefit from the circular trajectory of the particle to accelerate particles each revolution which reduces demands on intensity of the accelerating electric field. The complication is that the particle path has to be curved by a magnetic field which the particles move in. The higher the velocity and mass of particles is, the stronger the magnetic field has to be to keep the on the defined trajectory. The linear accelerator basically requires higher intensity of the electric field to accelerate particles in the short time due to its limited size.

The particles are accelerated to speeds very close to the speed of light where laws of classical mechanics are not longer valid. The total energy of the accelerated particle due to Einstein's theory of relativity is given

$$E = \sqrt{(m_0 c^2)^2 + (pc)^2} \tag{1.1}$$

where  $m_0$  is the invariant mass of the particle, c is the speed of light, and p is the momentum which is defined as

$$p = m_0 v. (1.2)$$

The LHC is a circular accelerator with the circumference of 26659 m. Particles in the LHC are accelerated in two opposite directions and collide in places which are called experiments. The LHC accelerates particles from starting energy of 450 GeV up to collision energy of 7 TeV. The particles are accelerated by the RF electromagnetic field (respectively by its electric component) which is created in superconducting cavity resonators. The superconducting cavity is a part of the low level RF system of the LHC that is responsible for particle accelerating.

#### Magnet Quench

The intensity of electric field in the cavities is 5 MV/m [2] and the magnetic induction of the bending magnets is up to 8 T [3]. This can be only achieved using superconducting cavities and magnets. Currently used materials become superconductive only at very low temperatures. The electromagnets in the LHC are cooled down to 1.8 K and temperature of cavities is about 4.5 K [3].

Their coils are made from superconducting wires that allow a current of 12 kA to flow to induce the nominal induction of the magnetic field. If the magnet temperature was increased by 1 K at nominal parameters, the magnet would stop being superconductive and become conductive with considerably higher resistance. The current of 12 kA flowing through the higher resistance would increase its temperature which would increase its resistance again resulting in the avalanche effect. The consequences would be very fast energy dissipation and very fast evaporation of the cooling liquid which could cause an explosion of the accelerator. This effect is known as a magnet quench.

#### Beam Pattern in the LHC

The beam of particles in the LHC is not a constant flow. The particles are gathered in bunches separated by spaces. The particles in the bunch have a normal longitudinal distribution with a Gaussian probability density function. The number of particles in one bunch is called the bunch intensity. By summing bunch intensities over the revolution period (the entire turn), the beam intensity is obtained. In the LHC, one turn contains 3564 bunch slots, but because of technical reasons only 2808 bunch slots is usable. The bunch space between two consecutive bunch slots is the bunch period. It is approximately 25 ns and it is slightly reduced when the beam is being accelerated.

The bunch slots in the LHC are occupied by bunches based on the technical possibilities of preceding accelerators which inject the beam into the LHC and on the injection system. The occupied and free bunch slots form the beam pattern. The 2808 irregularly occupied bunch slots are followed by 3 µs gap which allows the extraction kicker magnet to turn on and reach the nominal intensity of the magnetic field. The extraction kicker magnet is a fast pulse magnet which ejects the beam

from its standard circular trajectory into the beam dump area where the beam is dissipated into heat.

### 1.2 Fast Beam Current Transformer

The beam is a flow of charged particles. The flow of particles generates a beam current. With respect to Ampère's law the motion of charged particles induces a magnetic field around the beam. The flow of particles is not constant, thus the beam current and the magnetic field is time variant. To sense the magnetic field (subsequently the beam current) a transformer around the beam is used. The transformer providing bunch to bunch measurements in the LHC is called the Fast Beam Current Transformer (FBCT).

The signal provided by the FBCT is proportional to the beam current generated by the motion of charged particles in the accelerator. It is used to estimate number of charges in the bunch (the bunch intensity), since the given integral of the beam current i(t)

$$\int_{R} i(t)dt = Q \tag{1.3}$$

defines the charge Q of the bunch when the integration region R is limited to the bunch or the charge Q of the beam when the integration region R is limited to the revolution period. The number of charged particles in the bunch (respectively in the beam) can be estimated using the equation

$$Q = N \cdot e \tag{1.4}$$

where N is the number of charges and e is the charge of a proton.

The spectrum of the beam current is in the range from 0 Hz to  $\approx 10$  GHz. The bandwidth of the measured signal is limited by the FBCT and ranges from 300 Hz to 1.2 GHz. The spectrum of the signal corresponds with the beam pattern. The main component of the signal is at the frequency of 40 MHz which equals to the frequency of bunch slots  $(25 \text{ ns})^{-1}$ . In addition many adjacent spurs spaced by 11.5 kHz are present due to the LHC revolution frequency.

There are four FBCTs installed in the LHC Point 4. Two FBCTs are installed in the system A and two in the system B. The system A is the system which actively runs the LHC. The system B is a spare system being used for development and testing. The one FBCT in the system A observes the beam 1, the other one the beam 2. The other FBCTs in the system B are organised in the same way.

The detailed information about intensity measurements and the FBCTs can be found in [4] or in the condensed version in [5].

### 1.3 Beam Synchronous Timing

The Timing, Trigger and Control (TTC) system distributes the Beam Synchronous Timing (BST) signal with trigger and control information around the machine [6].

The BST originates in the low level RF systems of the machine where the BST is derived from the RF frequency driving the accelerating cavities. High power lasers transmit the signal from the RF systems to the CERN Control Centre (CCC). In the CCC a signal carrying additional messages is generated synchronously with the BST. The result is a composite signal which allows a receiver to recover the 40 MHz bunch clock, the orbit turn flag, and variant BST messages. This composite signal is transmitted over single-mode optical fibres to the LHC experiments and to all beam instrumentation placed around the LHC ring.

The TTC provides instruments with the beam synchronous timing and messages. There is a lot of types of messages which can be transmitted over the TTC network, for example the beam momentum and the UTC time.

Further details can be found in [7].

### 1.4 General Machine Timing

The General Machine Timing (GMT) is a complementary system to the BST. The GMT uses the RS-485 physical layer. The GMT signal is broadcast at rate of 500 kbps [8]. The received timing signal has a jitter of 14 ns that is caused by the signal distribution over the copper cables and by the capacitive loading of the receiver inputs.

Besides the timing signal, the GMT carries a lot of messages sent over the network, e.g. the beam energy (equivalent to the beam momentum) and the UTC time.

### 1.5 Beam Interlock System

The Beam Interlock System (BIS) [9] is a part of the machine protection system. Its main goal is to collect information from the other systems that are fundamental in machine safety and decide if it is safe to inject the beam into the machine. When the beam is already being accelerated and any connected system fails or stops the machine operation, the BIS has to dump the beam.

The beam dump is performed by instructing kicker magnets to extract the beam from its natural trajectory and guide it into the beam dump where it is transformed into the heat.

More information can be found in [10].

#### 1.5.1 User Interface of the BIS

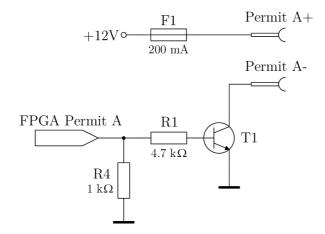

The BIS provides all client systems with a User Interface (CIBU) to ensure a reliable machine protection. Each client system has to declare a safety flag permitting to inject the beam. Control systems permit the beam injection or request the beam dump depending on the status of the flags published by the client systems.

The most important factor of the BIS is the reliability; therefore the CIBU is equipped with two separate channels. When the device sets the beam permit flag, it has to set both channels to their active states independently. This duplicity minimises a possibility of setting the permit flag by mistake due to a failure of output circuits.

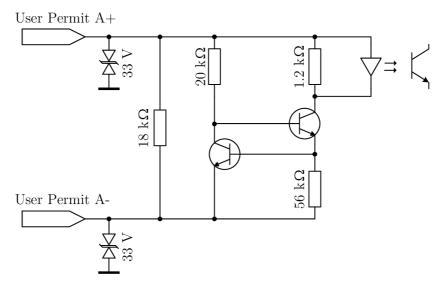

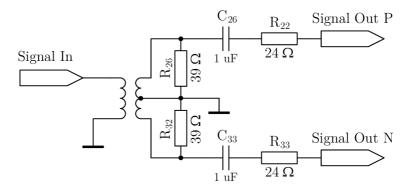

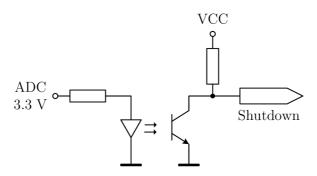

Fig. 1.1: CIBU input circuitry

Fig. 1.1 depicts the input circuitry of the one of the CIBU channels as it is defined in [11]. Referring to the document of the CIBU [11], the channel is considered in the active state when a current of more than 9 mA flows from the port A+ (respectively B+) to the port A- (respectively B-) of a connected system. The beam permit flag is set when both CIBU channels (A and B) are set to their active states.

Twisted pair cables with two Burndy 8-pin connectors are used to interconnect the CIBU and the client system [11].

### 1.6 Fast Beam Current Change Monitor

The Fast Beam Current Change Monitor (FBCCM also known as DIDT) is a beam diagnostic instrument for the LHC. The FBCCM is a redundant system of the machine protection to the LHC Beam Loss Monitors (BLM) [12]. The Beam Loss Monitors are devices which protect the LHC against damages caused by failures of the machine systems. They are inserted into the beam path and integrate the

current through the ionisation chamber to estimate the number of particles in the beam. When the BLM detects fast losses, it triggers the beam dump to protect the machine.

The FBCCM principle is different and independent of the operation of the Beam Loss Monitors. It evaluates the measurements of the beam intensity provided by the FBCT and calculates losses.

The motivation for the FBCCM is to increase the reliability of the machine protection provided by using a different principle of measurements. Additionally the FBCCM has a potential to achieve faster detection of the losses than the BLM.

The idea of the FBCCM is to acquire the signal from the FBCT and to evaluate the losses of beam intensity. In the accelerators no losses of intensity are ideally acceptable, but because of imperfections of the machine some losses are tolerated. When the FBCCM detects the fast losses exceeding a tolerated level, it has to trigger the beam dump.

Experimentally it was discovered that the beam intensity is proportional to the magnitude of the FBCT signal in the narrow band around the 40 MHz component. This property is used by the FBCCM to estimate the beam intensity. The magnitude of the 40 MHz component is integrated to calculate the total number of charges over different time (integration window). Ideally the result of the integration over the each window should never be less than the previous result of the same window. The negative differential of definite integral would signify losses of the charges. The condition for non-zero losses would be

$$\frac{\mathrm{d}}{\mathrm{d}\tau} \int_{W} |s(t)| \mathrm{d}t < 0 \tag{1.5}$$

where |s(t)| is the magnitude of the signal proportional to the beam intensity and window W is the region of the finite integral. However in the real system some losses are tolerated, then the FBCCM has to dump the beam when the following condition met.

$$\frac{\mathrm{d}}{\mathrm{d}\tau} \int_{w} |s(t)| \, \mathrm{d}t < \vartheta_{W} \tag{1.6}$$

where  $\vartheta_W$  is the tolerated loss threshold for the particular window and energy.

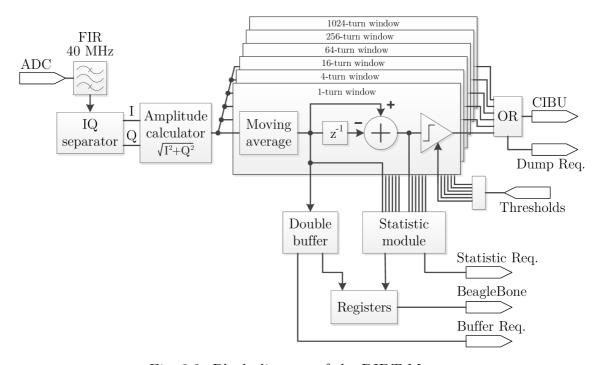

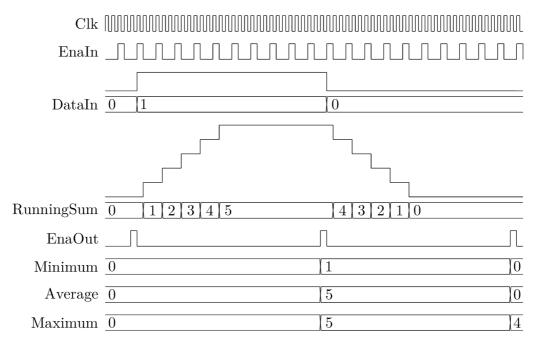

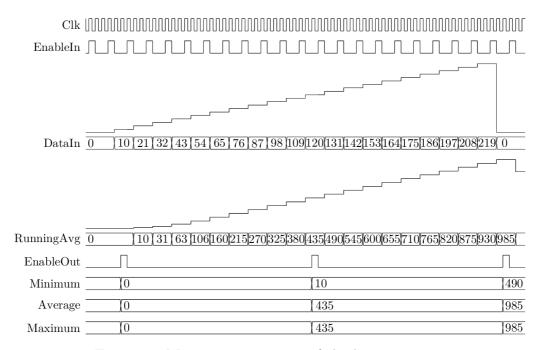

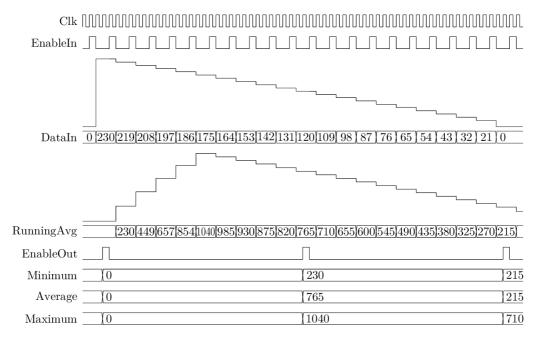

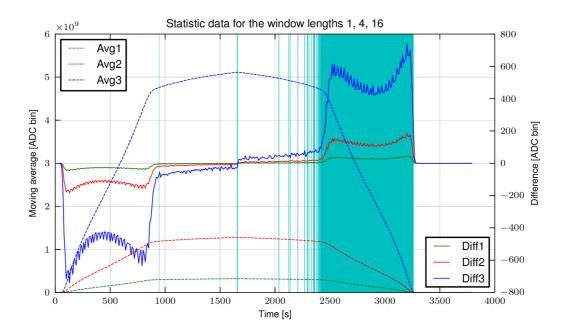

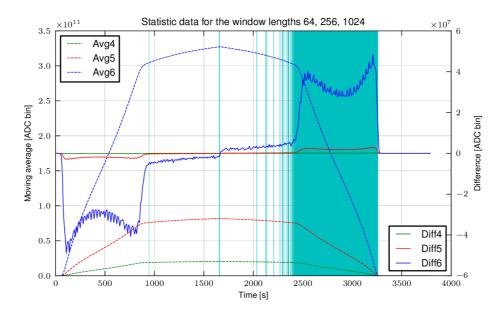

Based on the study of intensity measurements it was decided that the length of different integration windows for the FBCCM implementation should be 1, 4, 16, 64, 256, 1024 turns. To comply with all requirements of the narrow bandwidth and six different integration windows, the signal processing has to be performed digitally. Eq. 1.6 can be approximated into the discreet domain as

$$\sum_{y=N}^{y} |s_x| - \sum_{y=2N}^{y-N} |s_x| < \vartheta_N \tag{1.7}$$

where N is the length of the summation window in the number of input samples of the signal  $s_x$  and  $\vartheta_N$  is the threshold of tolerated losses for the particular length of the window and energy.

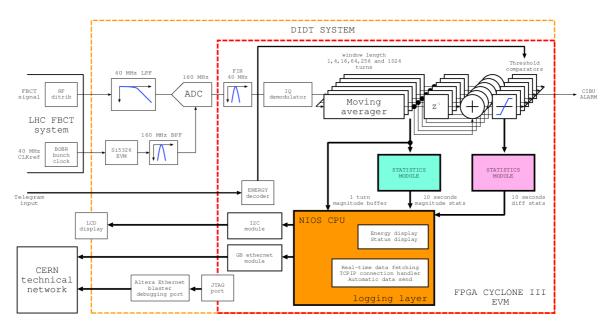

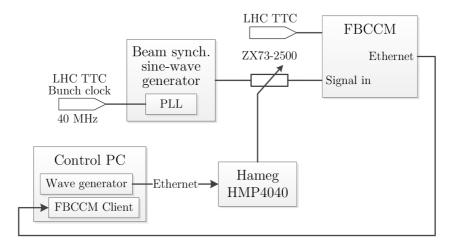

### 1.6.1 The First Prototype

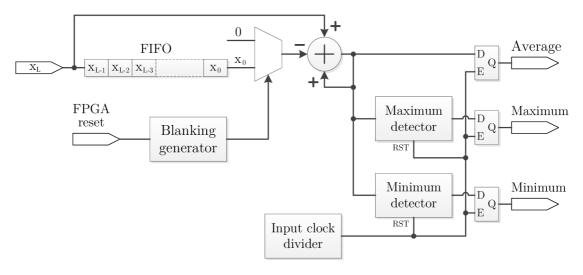

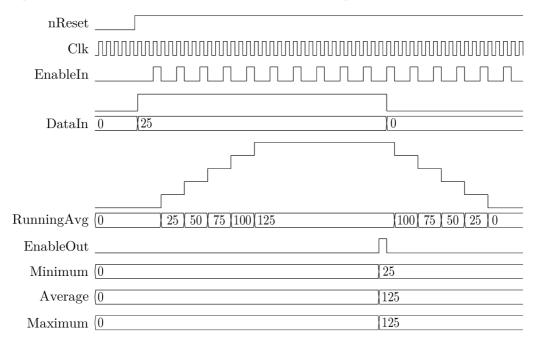

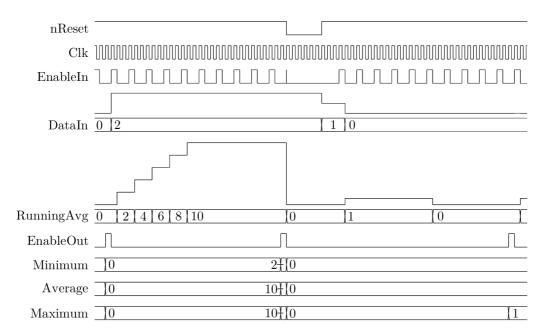

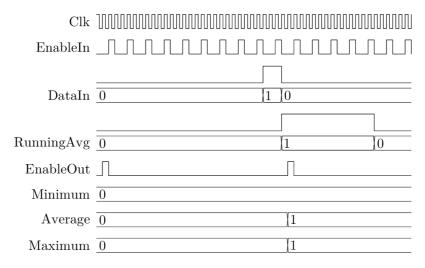

Belohrad presents the first prototype of the FBCCM in [13] and shows the system concept (Fig. 1.2). The analogue signal from the FBCT is filtered by the anti-aliasing low-pass filter (LPF) module to suppress the frequencies above the frequency of 40 MHz which the band of the interest is around. The filtered signal is converted into the digital domain by the ADC ADS5485 using the TI evaluation module [14]. The evaluation module is then connected through the High Speed Mezzanine Card (HSMC) connector to the Cyclone III Development Board. The digital processing is implemented in the FPGA.

Fig. 1.2: Diagram of the FBCCM system [13]

The digital signal is firstly filtered by the narrow-band FIR filter with the bandwidth of 2.5 MHz. Referring to Eq. 1.7 magnitude of the signal has to be calculated. The digitally filtered signal is firstly translated by the quadrature mixer to the baseband around frequency of 0 Hz. The magnitude of the signal is then calculated from its I and Q samples.

$$|s_x| = \sqrt{I^2 + Q^2} \tag{1.8}$$

The simplest quadrature mixer for the translation of the high-frequency digital signal to the baseband can be implemented when the sampling frequency of the signal is four times the signal frequency. The samples of the signal are then equal to the sequence of samples +I, +Q, -I, and -Q. This implementation is only possible if the sampling clock is locked to the beam and its frequency is four times higher than the bunch frequency. To comply with this condition the bunch clock from an adjacent system is provided to the first prototype. The PLL Si5326 is used to multiply the bunch frequency to obtain the 160 MHz sampling clock. The ADC achieves the better signal-to-noise ratio when the sampling clock waveform is the

sine wave instead of the square wave. The generated phase-locked square wave is therefore filtered to suppress higher harmonics before it is connected to the ADC.

The signal processing continues by summing the magnitude signal over windows with different lengths and computes the difference of two consecutive output samples for each window. When the difference exceeds the defined threshold, the FBCCM triggers the beam dump. The thresholds are selected with respect to the actual beam energy which is decoded from the messages in the received telegram from the GMT.

The outputs of the moving average and the differences are statistically evaluated. The results (maximum, average, minimum) are sent each ten seconds by the NIOS processor to the CERN technical network over Ethernet The NIOS processor is an Altera's soft processor implemented into the general FPGA logic. The data is sent through TCP sockets to ensure the reliability of their reception. Any general client can connect to the FBCCM to receive the data. Besides these statistical messages the NIOS periodically sends data of the one turn moving average and as well the beam dump messages anytime the beam dump occurs. At the same time it prints device status information in the front panel LCD display.

The management and updates of the device are performed via the Altera Ethernet Blaster which is a JTAG programmer with the Ethernet connection. This programmer is fully supported by Altera and it allows to execute remotely the same operations like an ordinary USB JTAG programmer. The Altera Ethernet Blaster provides a secured way to remotely update and debug the device.

Generally the first prototype is very modular which is great for a testing and an elaboration, because each module can be replaced with another having different characteristics or functionality. Unfortunately the most modules were not specifically designed for the FBCCM, thus in some cases the system is over-complicated. These characteristics are not convenient for the final solution.

#### 1.6.2 The Final Version of the FBCCM

The first prototype of the FBCCM was never intended to be a final solution. It was designed and constructed to prove the measurement methods. Some parts and features of the first prototype were known not to be ideal even before the first tests, another were discovered lately after the examination of the test results. The outcomes of the first prototype testing defined specifications for the final version of the FBCCM.

The first prototype was equiped with two measurement channels and measured intensity of both beams at the same time. This feature turned up as a disadvantage in the end, because a cross-talk between the two channels degraded the sensitivity of the instrument. Even though the cross-talk is a hardware issue and a proper design should minimise it to the sufficient level, it was decided to construct one device for each beam.

The soft processor NIOS of the previous system had to be replaced, because as

every soft processor, it consumes a lot of valuable high-speed FPGA logic which is needed for the signal processing. Moreover the TCP/IP stack implemented in its operating system  $\mu$ C/OS was not stable enough and the processor was too slow to handle the TCP communication with more than two connected clients. This performance limitation denies implementation of expert features in the future.

The first prototype acquires the beam synchronous timing and the telegram from two different interfaces. The final design combines the reception of both timing and the telegram into the common receiver of the TTC received from the optical fibre. This improves reliability of the FBCCM due to the less cabling and removes the FBCCM dependence on the adjacent system. Moreover it was discovered in the first prototype tests that settings performed on the adjacent system influenced the FBCCM functionality. Therefore the FBCCM requires a dedicated link for the timing reception.

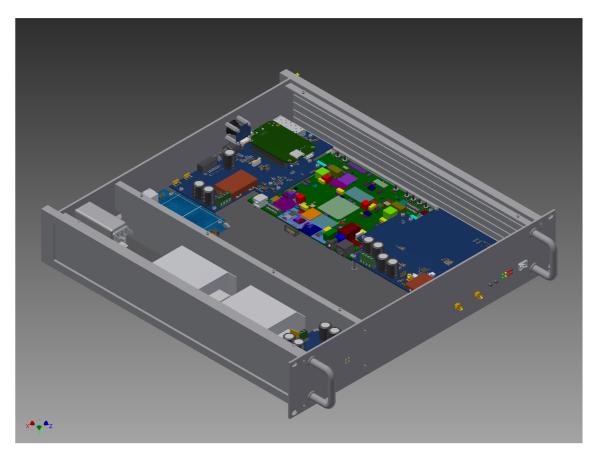

This thesis is aimed at the development of the new device implementing fixes of all the discovered issues of the first prototype. Six operational pieces of the new FBCCM had to be fabricated and subsequently tested in the laboratory. In the end of the testing phase, four devices will be installed in the LHC close to the measuring FBCTs in the LHC Point 4, while two devices will be kept in the laboratory for testing and development purposes. Two devices will supervise the beam 1 and 2 and will be in the system A and the others for the beam 1 and 2 in the system B. The organisation of the FBCCM in the LHC is similar to the organisation of the FBCTs.

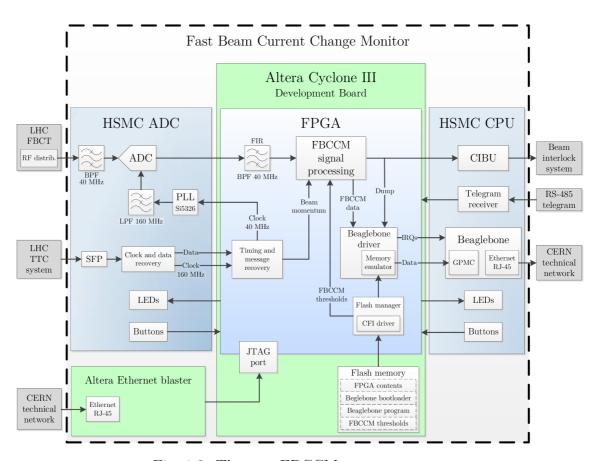

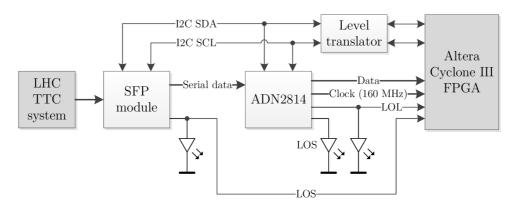

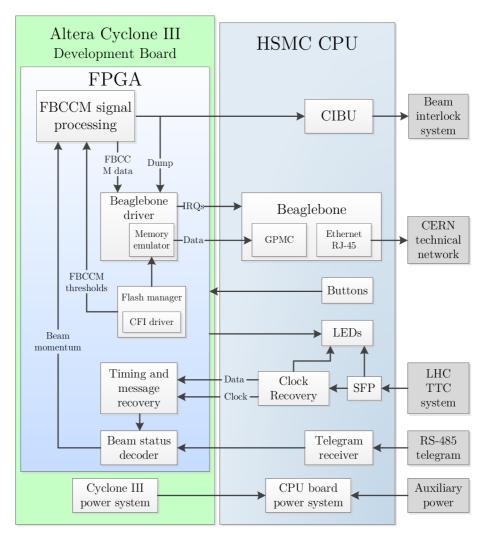

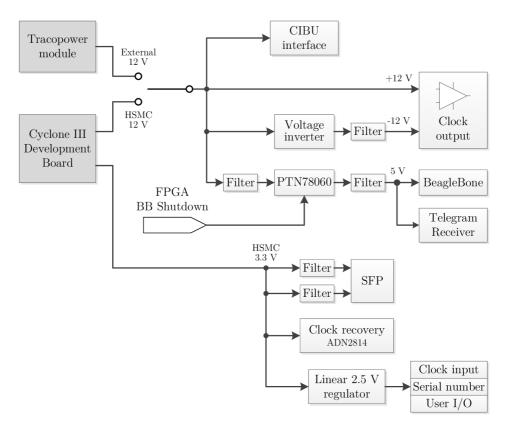

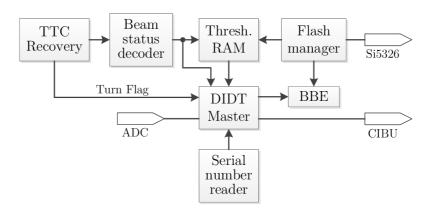

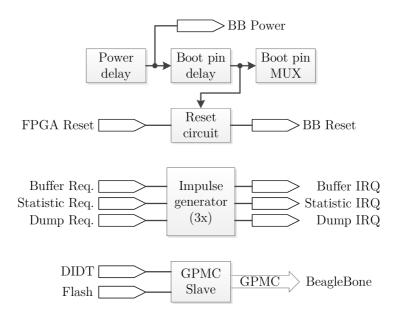

The desired concept of the new system is shown in Fig. 1.3. The measurement principles and algorithms are well tested in the first prototype; therefore they are adopted by the new FBCCM. Nevertheless their implementation is absolutely different. There was an intention to replace the NIOS processor with a system on chip in Cyclone V, but unfortunately a release of this FPGA was delayed and the development of the FBCCM had to meet the given schedule. Therefore the Cyclone III Development Board was kept in the design and a BeagleBone was chosen as a suitable replacement for the NIOS processor. The BeagleBone is a microprocessor system using the AM335x Sitara ARM Cortex-A8 processor. It is equipped with the Ethernet connection which is used to transport the measured data to the CERN Control System.

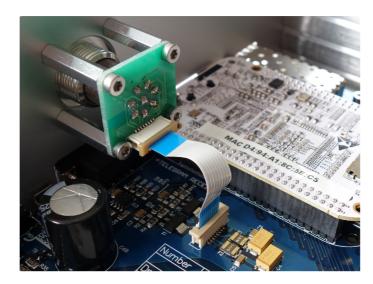

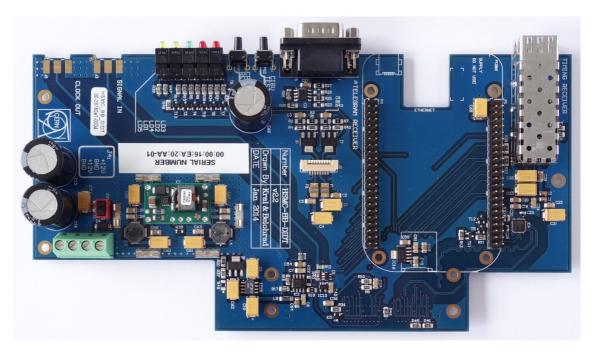

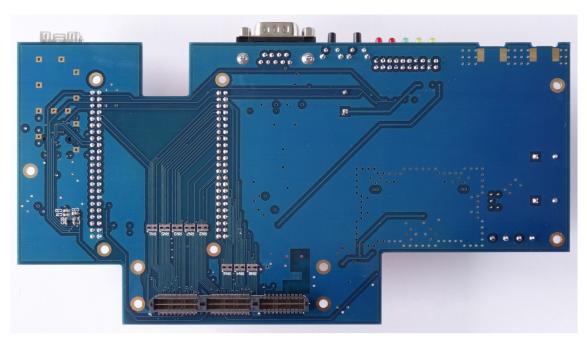

Two peripheral subsystems for the FBCCM had to be designed. The each subsystem is connected to the HSMC connector on the central FPGA board. The ADC Subsystem contains the analogue-to-digital converter, the main TTC receiver, indicators, and controls. The CPU Subsystem interconnects the BeagleBone with the FPGA board. Furthermore it carries the CIBU interface, the spare TTC receiver, the telegram receiver, indicators, and controls.

The power subsystem in the new FBCCM is completely different, because previously used evaluation and development boards required various voltages which are not more needed. This makes the power system simpler.

Fig. 1.3: The new FBCCM system concept

### 2 FBCCM HARDWARE

This chapter focuses on the design of the FBCCM hardware. The main designed electronics are the ADC Subsystem and the CPU Subsystem. The subsystem design is restricted by the possible signal connections to the central Cyclone III Development Board.

### 2.1 ADC Subsystem

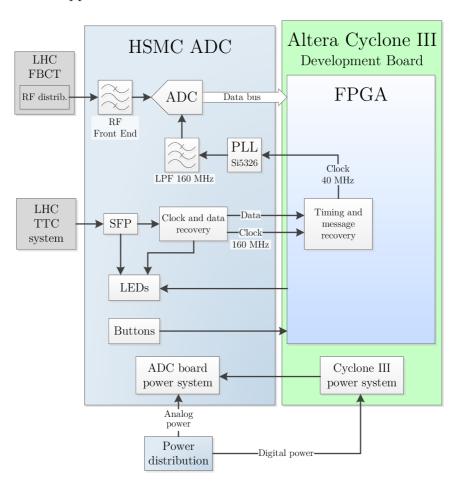

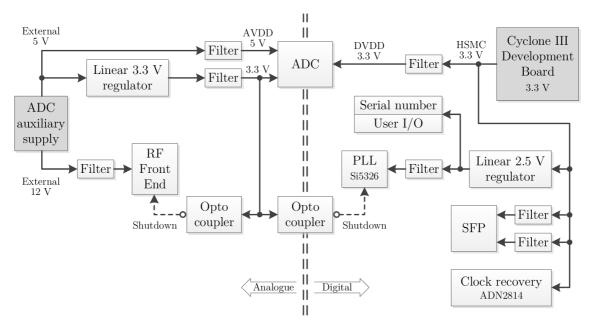

The ADC Subsystem is one of two designed peripheral boards connected by the HSMC connector to the FPGA module. It contains a mixture of digital and analogue electronics. Its block diagram is shown in Fig. 2.1. The complete schematic diagram can be found in Appendix A.1.

Fig. 2.1: Block diagram of the ADC Subsystem

The digital electronics include high speed data buses communicating with frequencies up to 160 MHz. These buses require a proper impedance matching to avoid signal reflections. The reflections would narrow the eye-diagram of the signal at the

destination and shorten the time window of the proper sampling. Furthermore the lengths of signal traces in common bus have to be matched to ensure equal propagation delays for all the signals in the bus. Different transport delays would shorten the sampling window for the whole bus. The narrow window of a proper sampling would put higher constraints on timing driven compilation of the FPGA.

The impedance matching is the issue of the analogue electronics design as well. The reflected signal would be superposed to desired signal and negatively influence its processing.

### 2.1.1 Analogue to Digital Conversion

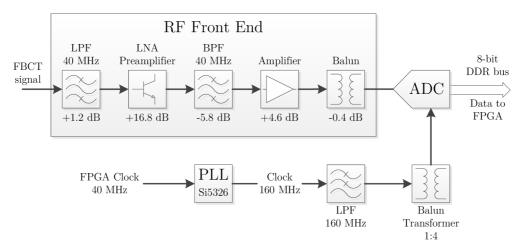

Fig. 2.2: Block diagram of the analogue to digital conversion of the ADC Subsystem

The main purpose of the ADC Subsystem is to convert the FBCT signal into the digital domain. The input signal level is too low to be converted directly. It has to be gained and filtered. The filtration suppresses strong frequency components out of the processed band. Otherwise these components would degrade the system signal-to-noise ratio (SNR), because the signal gain would be limited to the ADC full-scale range by these undesired components. The signal is gained and filtered by the RF Front End.

### 2.1.2 RF Front End of ADC Subsystem

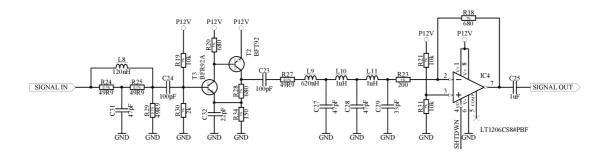

The design and development of the RF Front End is not part of this thesis. Its structure and values of its components have been adopted from the first FBCCM prototype. The implemented circuit of the RF Front End is depicted in Fig. 2.3. The particular stages of the front end are coupled by capacitors. The input low-pass filter and the low noise preamplifier are coupled by the capacitor C24. The capacitor C23 link the preamplifier output to the band-pass filter and the output amplifier. The C25 separates the output amplifier from the following RF balun. The output

amplifier works in inverting mode and is offset by the resistor divider (R21 and R31). The AC coupling allows to power all the blocks by an asymmetrical power supply.

Fig. 2.3: Schematic of the implemented RF Front End

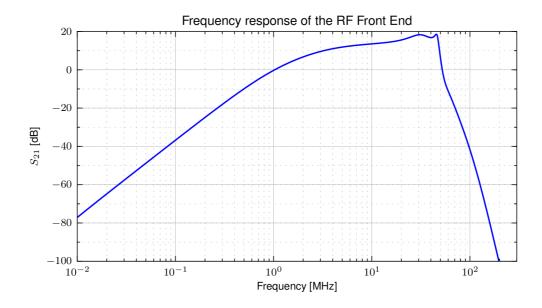

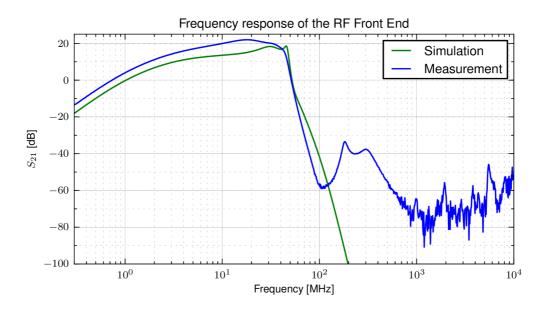

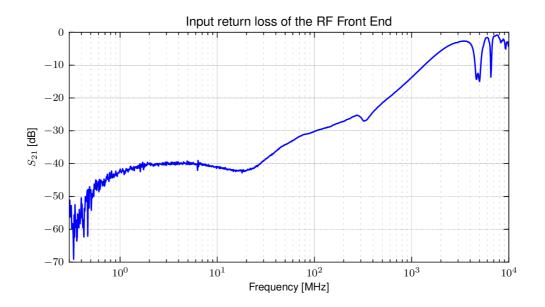

The simulated frequency response of the RF Front End is depicted in Fig. 2.4. Characteristic parameters of the band pass amplifier are the maximum gain of 18.6 dB, the gain at 40 MHz of 16.8 dB, the high-pass cut-off frequency of 19.9 MHz, and the low-pass cut-off frequency of 47.4 MHz.

Fig. 2.4: Simulation of the frequency response of the RF Front End

#### RF Front End Tolerance Analysis

The simulated frequency response will never be precisely equal to the real circuit characteristics. The real frequency response will deviate simultaneously with a change of component parameters from their nominal values. The possible deviations of circuit characteristics have to be determined by the tolerance analyses. The

observed parameters of the front end tolerance analysis are the gain at frequency of 40 MHz, the maximum gain, and the low cut-off and high cut-off frequencies. The 40 MHz gain defines actively used dynamic range of the ADC. If the used dynamic range was considerably less than maximum range, the digital signal SNR would be degraded. The maximum gain has to be close to the 40 MHz gain. Otherwise it would degrade the system SNR again, because the maximum signal amplitude has to be covered by the full-scale range.

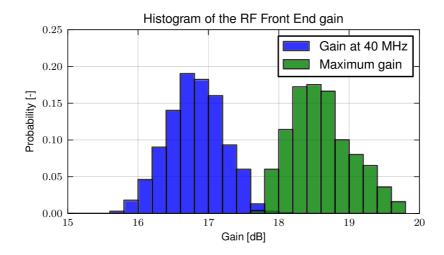

The results of the gain tolerance analysis are shown in Fig. 2.5. The dispersion of the maximum gain is 2 dB and of the 40 MHz gain is 1.5 dB. The variations of the both gains are sufficiently small. In addition the 40 MHz gain variation will be compensated by the system calibration.

Fig. 2.5: Tolerance analysis of gain of ADC Subsystem RF Front End

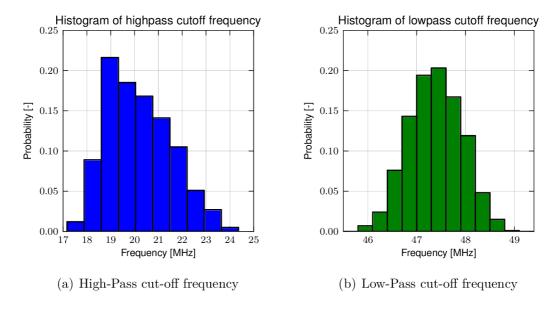

Fig. 2.6 presents the variations of the high-pass low-pass cut-off frequencies of the RF Front End. The high-pass cut-off frequency ranges from 18 MHz to 23 MHz. The range of the low-pass cut-off frequency is from 46 MHz to 48.5 MHz. The variation of the RF Front End pass-band meets the requirements of the undesired signal components filtration.

All the tolerance analyses of the RF Front End give acceptable results. The frequency response of the RF Front End has to be measured for all the finally fabricated ADC Subsystems to verify their functionality and record their exact parameters.

All the tolerance simulations were calculated in PSpice using one thousand runs. Tolerances of all the components were set according to their real parameters. Coils and capacitors have 5 %, resistors with 49.9  $\Omega$  have 0.1 %, and the others have 1 %.

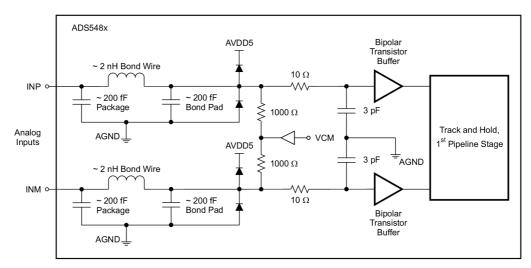

#### Matching of the ADC Signal Input

The RF Front End output is a single-ended signal, but the following ADC requires a differential signal. In addition the ADC signal input shown in Fig. 2.7 does not

Fig. 2.6: Tolerance analysis of the high-pass and the low-pass cut-off frequencies of the ADC front end

provide the required impedance. Therefore the matching circuit with a balun for single-ended to differential conversion had to be implemented.

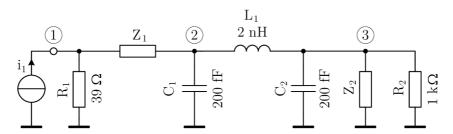

The matching circuit significantly influences the quality of the ADC conversion. Therefore it is recommended [15] to adopt the matching circuit from the ADC evaluation module. The matching circuit of the ADS5485 evaluation module [14] is depicted in Fig. 2.8. It is verified by calculation that this particular matching circuit is suitable for the 40 MHz signal matching.

Fig. 2.7: Schematic of the equivalent circuit of the ADS5485 signal input [16]

The used balun ADT1-1WT transforms a signal with the impedance ratio of 1:1. In the ideal situation the required impedance seen by the balun on its secondary

Fig. 2.8: Schematic of the implemented matching circuit for the ADS5485 signal input

side would be 50  $\Omega$  to reflect 50  $\Omega$  on its primary side. However the transformer is not ideal and it has a non-zero reverse gain. Therefore the compensation has to be calculated by following equations in [15]. The real characteristic impedance of the transformer is calculated using its reverse gain at the signal frequency [17].

$$s_{12} = 10^{\frac{-L_{R_{dB}}}{20}} = 10^{\frac{-15.85}{20}} = 0.1613$$

$$s_{12} = \frac{50 - Z_{0_1}}{50 + Z_{0_1}}$$

$$Z_{0_1} = 50 \Omega \cdot \frac{1 - s_{12}}{1 + s_{12}} = 50 \Omega \cdot \frac{1 - 0.1613}{1 + 0.1613} = 36.11 \Omega$$

$$(2.1)$$

The real impedance on the secondary side  $Z_{0_2sig}$  required to reflect the ideal impedance on the primary side is given

$$\frac{Z_{0_1}}{Z'_{0_2}} = \frac{Z'_{0_1}}{Z_{0_2}} Z_{0_2} = Z'_{0_2} \cdot \frac{Z'_{0_1}}{Z_{0_1}} = 50 \,\Omega \cdot \frac{50}{36.11} = 69.23 \,\Omega \tag{2.2}$$

where  $Z'_{0_2}$  is the ideal impedance on the secondary side, and  $Z'_{0_1}$  is the ideal impedance on the primary side.

Fig. 2.9: The aggregated circuit used for the input impedance calculation of the matching network and the ADC signal input

The matching circuit (Fig. 2.7) together with the ADC input (Fig. 2.7) has to provide the secondary side with the impedance of  $Z_{0_2} = 69.23 \,\Omega$ . This is verified by the input impedance calculation of the aggregated circuit shown in Fig. 2.9 with respect to ground. Due to the calculus complexity the matrix equation derived from Kirchhoff's laws is used.

$$\begin{pmatrix} G_1 + Y_1 & -Y_1 & 0 \\ -Y_1 & Y_1 + Y_{C_1} + Y_{L_1} & -Y_{L_1} \\ 0 & -Y_{L_1} & Y_{L_1} + Y_{C_2} + G_2 + Y_2 \end{pmatrix} \begin{pmatrix} u_1 \\ u_2 \\ u_3 \end{pmatrix} = \begin{pmatrix} i_1 \\ 0 \\ 0 \end{pmatrix}$$

(2.3)

where conductance  $G_x$  is the inverse of corresponding resistance  $R_x$ . The admittance  $\mathbf{Y}_x$  is the inverse of corresponding impedance  $\mathbf{Z}_x$ . The  $\mathbf{Y}_{C_x} = j \cdot 2\pi f C_x$  is admittance of the corresponding capacitor, and  $\mathbf{Y}_{L_1} = (j \cdot 2\pi f L_1)^{-1}$  is admittance of the inductor  $L_1$ .

The input impedance of the circuit (Fig. 2.9) can be calculated from Eq. 2.3 using Cramer's rule and Gaussian elimination.

$$Z_{in} = \frac{u_1}{i_1} = \frac{i_1 \frac{(-1)^{1+1} \Delta_{1,1}}{\Delta}}{i_1} = \frac{\Delta_{1,1}}{\Delta}$$

(2.4)

where  $\Delta_{1,1}$  is a determinant of the reduced admittance matrix from Eq. 2.3 without the first row and the first column, and  $\Delta$  is a determinant of the whole admittance matrix. The numerical solution of the input impedance at frequency of 40 MHz is

$$Y_{1} = Z_{1}^{-1} = \left(24 + \frac{1}{j \cdot 2\pi \cdot 40 \cdot 10^{6} \cdot 10^{-6}}\right)^{-1} = (41.67 + 6.908 \cdot 10^{-3}j) \text{ mS}$$

$$Y_{2} = Z_{2}^{-1} = \left(10 + \frac{1}{j \cdot 2\pi \cdot 40 \cdot 10^{6} \cdot 3 \cdot 10^{-12}}\right)^{-1} = (5.685 + 753.9j) \text{ µS}$$

$$Y_{C_{1}} = Y_{C_{2}} = j \cdot 2\pi \cdot 40 \cdot 10^{6} \cdot 200 \cdot 10^{-15} = 50.27j \text{ µS}$$

$$Y_{L_{1}} = \frac{1}{j \cdot 2\pi \cdot 40 \cdot 10^{6} \cdot 2 \cdot 10^{-9}} = -1.989j \text{ S}$$

$$\Delta_{1,1} = \begin{vmatrix} Y_{1} + Y_{C_{1}} + Y_{L_{1}} & -Y_{L_{1}} \\ -Y_{L_{1}} & Y_{L_{1}} + Y_{C_{2}} + G_{2} + Y_{2} \end{vmatrix}$$

$$\Delta = \begin{vmatrix} G_{1} + Y_{1} & -Y_{1} & 0 \\ -Y_{1} & Y_{1} + Y_{C_{1}} + Y_{L_{1}} & -Y_{L_{1}} \\ 0 & -Y_{L_{1}} & Y_{L_{1}} + Y_{C_{2}} + G_{2} + Y_{2} \end{vmatrix}$$

$$Z_{in} = \frac{\Delta_{1,1}}{\Delta} = \frac{(1.756 - 84.860j) \cdot 10^{-3}}{(0.1159 - 2.259j) \cdot 10^{-3}}$$

$$Z_{diff} = 2Z_{in} = (75.00 - 2.29j) \Omega$$

The differential input impedance  $Z_{diff} = (75.00 - 2.29j) \Omega$  of the matching circuit together with ADC inputs is very close to the calculated required impedance

$Z_{0_2} = 69.23 \,\Omega$  (Eq. 2.2). The difference can be caused by using the equivalent ADC input circuit, which does not have to equal the real ADC input in the whole range of frequencies, or by the balun leakage inductance, which has not been taken into consideration.

The verified matching circuit was implemented and measured in the ADC Subsystem. Its measurement shows the input reflection of -34.8 dB at 40 MHz which is sufficient for this application.

### 2.1.3 ADC Clock Generation

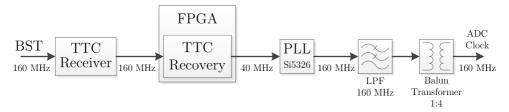

The signal provided by the RF Front End has to be sampled synchronously with the beam. This is ensured by the bunch clock reception and sampling clock generation. The generation of the sampling clock is depicted in Fig. 2.10.

Fig. 2.10: Block diagram of the sampling clock generation

The FPGA recovers the 40 MHz bunch clock from the TTC clock signal. The bunch clock is routed to drive the PLL. The PLL multiplies the bunch clock frequency four times to obtain sampling clock frequency of 160 MHz. The generated sampling clock signal is phase-locked to the LHC bunch clock, thus the ADC sampling and the beam are coherent. The phase-locked sampling clock could be generated by the PLL in the FPGA, but this solution does not achieve a required clock jitter of less than 1 ps. Therefore the PLL Si5326 is used to attenuate jitter of the sampling clock down to 300 fs.

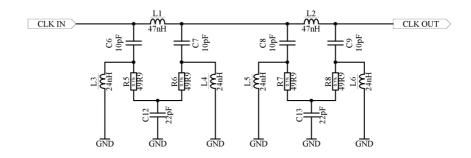

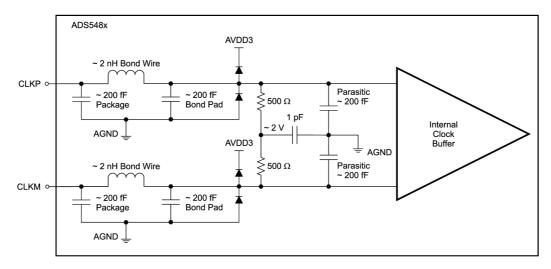

### 2.1.4 Clock Low-Pass Filter

The sampling clock generated by the PLL Si5326 is in the form of a square-wave. The ADC requires the sine-wave clock signal to achieve the best signal to noise ratio [16]. Therefore the sampling clock is filtered by a low-pass filter to remove all its higher harmonic components.

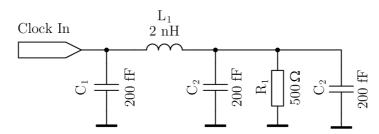

The clock low-pass filter design is not part of this thesis. It is examined to provide a complete view on the ADC Subsystem. The structure and component values of the filter have been adopted from the first FBCCM prototype. The filter structure is depicted in Fig. 2.11. The filter is a 12<sup>th</sup> order elliptic filter consisting of two equal filter stages in series.

Fig. 2.11: Schematic diagram of ADC clock filter

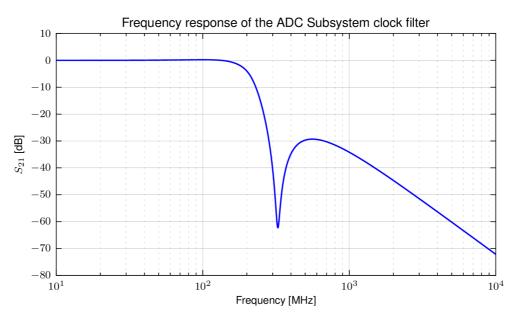

The simulated frequency response of the clock filter is shown in Fig. 2.12. The filter was loaded with its characteristic load of 50  $\Omega$ . It can be seen that the filter cut off frequency is 190 MHz and the first significant minimum of the insertion gain is at the frequency of 325 MHz. The filter frequency characteristic could be more suitable to filter the 160 MHz square wave clock signal, because the main unwanted component is the clock third harmonic at the frequency of 480 MHz. If it is discovered in the future tests that the purity of the clock signal is not sufficient, the new filter with a zero of the transmission at a frequency around the third harmonic will be designed.

Fig. 2.12: Simulated frequency response of the Clock Low-Pass Filter

#### Clock Low-Pass Filter Tolerance Analysis

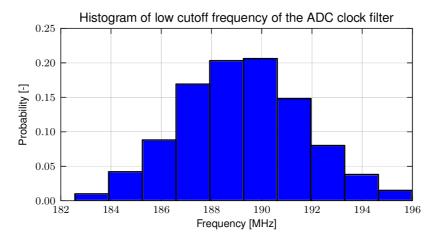

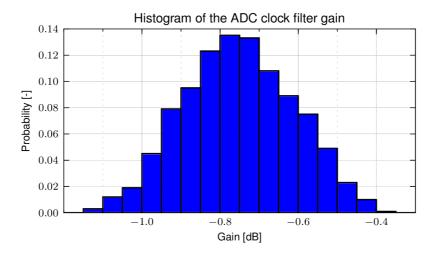

The frequency responses of simulated filter and the real filter will never be same. Deviation of the real filter frequency response is determined by the tolerance analysis. The filter tolerance analysis was performed in PSpice. Results of this analysis are the tolerance of the low cut-off frequency (Fig. 2.13) and the tolerance of filter gain at the clock frequency of 160 MHz (Fig. 2.14).

The tolerance analysis was performed with one thousand repetitions and the uniform distribution of the component value probability. The tolerances of the components from the schematic in Fig. 2.11 were set according to characteristics defined by their manufacturers. All the inductors have 2 % tolerances, all the capacitors have 5 %, and the resistors have 0.1 %.

Fig. 2.13: Simulation of the low cut-off frequency tolerance of the Clock Low-Pass Filter

Fig. 2.14: Simulation of the gain tolerance of the Clock Low-Pass Filter

The low cut-off frequency varies from 182 MHz to 196 MHz. This is sufficient interval, because the input clock signal has only the wanted spectral line at frequency of 160 MHz. The low cut-off frequency of the filter is not critical parameter unless it is close to the clock frequency. The filter gain at the frequency of 160 MHz is more important parameter, because the amplitude of the clock signal injected into the ADC should be in range from 6 dBV to 14 dBV. The tolerance analysis shows the most gains in the interval from -1 dB to -0.5 dB. The spread of the filter gain is sufficient for the final fabrication, because the range of the tolerated clock amplitude is wider.

### 2.1.5 Single-Ended to Differential Clock Conversion

The filtered clock generated by the Si5326 is a single-ended signal with maximum amplitude of 2.5  $V_{PP}$  [18]. The ADC requires a differential clock with amplitude in the range from 3  $V_{PP}$  to 5  $V_{PP}$  [16]. Therefore the clock for the ADC provided by a clock low-pass filter is gained and converted to differential signal by a balun transformer.

The required gain of the balun transformer had to be calculated. The recommended input voltage is in the range from  $V_{Imin_{dB}} = 6$  dBV to  $V_{Imax_{dB}} = 14$  dBV. The PLL clock output level is in the range from  $V_{Omin_{dB}} = 4$  dBV and  $V_{Omax_{dB}} = 8$  dBV. The insertion loss of the clock low-pass filter is  $L_{LPF} = 0.8$  dB. The desired voltage gain of the balun transformer is solved using an equation

$$G_B - L_B = V_{O_{dB}} - V_{I_{dB}} + L_{LPF} (2.6)$$

where  $G_B$  is the gain of the balun,  $L_B$  is the insertion loss of the balun,  $V_{O_{dB}}$  is the PLL output voltage, and  $V_{I_{dB}}$  is the ADC input voltage in decibels. The minimum voltage gain of the balun transformer is given

$$G_{B_{min}} - L_B = V_{Imin_{dB}} - V_{Omin_{dB}} + L_F = 2.8 \text{ dB}.$$

(2.7)

The maximum voltage gain is given

$$G_{B_{max}} - L_B = V_{Imax_{dB}} - V_{Omax_{dB}} + L_F = 6.8 \text{ dB}.$$

(2.8)

Due to the calculated range the balun transformer with  $G_B = 6$  dB can be used. The voltage ratio of such transformer is 1:2, thus the transformer impedance ratio is 1:4. The chosen transformer gain corresponds to gain of the transformer on the ADS5485 evaluation module [14]. The used balun transformer is ADT4-1WT with insertion loss  $L_B = 1$  dB at 160 MHz [19].

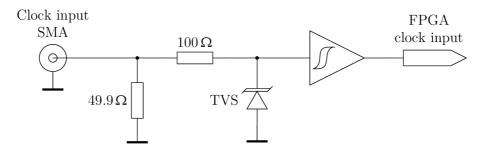

#### 2.1.6 Clock Termination

The characteristic impedance at the balun transformer input has to be 50  $\Omega$ , because the clock low-pass filter requires to be loaded with this nominal impedance. This is ensured by the matching network on the transformer secondary side. The matching

Fig. 2.15: Equivalent ADS5485 clock input circuit [16]

network has to be designed with respect to the impedance of the ADC clock input. The equivalent circuit of the ADC clock input is shown in Fig. 2.15.

The required impedance seen by the ideal RF balun transformer would be 200  $\Omega$  to reflect 50  $\Omega$  on the transformer input side. The calculation of the matching circuit for the real transformer has to reflect its non-zero reverse gain [19]. The procedure of the impedance matching calculation is similar like for the ADC signal input [15]. The real impedance  $Z_{0_1}$  on the primary side of the transformer is calculated.

$$s_{12} = 10^{\frac{-L_{R_{dB}}}{20}} = 10^{\frac{-20}{20}} = 0.1$$

$$s_{12} = \frac{50 - Z_{0_1}}{50 + Z_{0_1}}$$

$$Z_{0_1} = 50 \Omega \cdot \frac{1 - s_{12}}{1 + s_{12}} = 50 \Omega \cdot \frac{1 - 0.1}{1 + 0.1} = 40.91 \Omega$$

(2.9)

The impedance  $Z_{0_2}$  which the transformer has to see on the secondary side to reflect 50  $\Omega$  into the primary side is given by the equation.

$$\frac{Z_{0_1}}{Z'_{0_2}} = \frac{Z'_{0_1}}{Z_{0_2}}$$

$$Z_{0_2} = Z'_{0_2} \cdot \frac{Z'_{0_1}}{Z_{0_1}} = 200 \,\Omega \cdot \frac{50}{40.91} = 244.4 \,\Omega$$

(2.10)

The input differential impedance of the matching circuit and the ADC clock input has to be  $244.4~\Omega$ . The calculation of the matching circuit input impedance requires knowledge of the ADC clock input impedance. There are three basic ways how to solve the ADC clock input impedance (Fig. 2.15). The first way is analytic which means to calculate the impedance using any circuit solving method. Another way is to simulate the input circuit in circuit analyser program (e.g. PSpice). The

last way is to use the ADC scattering parameters declared by the manufacturer which should be the most precise definition of the real impedance. The scattering parameters are not available for the used ADC. Therefore the input impedance is calculated.

The input impedance calculation is limited to the high frequency signals. The equivalent clock input circuit (Fig. 2.15) is simplified to schematic diagram depicted in Fig. 2.16 for the calculation of input impedance with respect to ground (AGND). The complex impedance of the clock input with respect to ground can be calculated using the following equations.

$$Y_{1} = R_{1}^{-1} + j \cdot 2\pi f(C_{2} + C_{3}) = (2 + 0.402j) \text{ mS}$$

$$Y_{L_{1}} = (j \cdot 2\pi f L_{1})^{-1} = -0.497j \text{ S}$$

$$Y_{clk} = \frac{Y_{1}Y_{L}}{Y_{1} + Y_{L}} + j \cdot 2\pi f C_{1} = (2.003 + 0.5954j) \text{ mS}$$

$$Z_{clk} = Y_{clk}^{-1} = (458.67 - 136.34j) \Omega$$

(2.11)

where the  $Y_1$  is complex admittance of the parallel combination of C2, R1, and C3. The  $Y_{L_1}$  is complex admittance of L1. The  $Y_{clk}$  and the  $Z_{clk}$  are complex admittance and impedance of the clock input with respect to ground.

Fig. 2.16: Schematic of the equivalent simplified circuit of the ADS5485 clock input pin

The easiest way to provide an external matching is to connect external combination of resistive and reactive components parallel to the clock input. The parallel admittance of the clock input and the matching circuit have to comply with the following equation to produce the required impedance on the secondary side of the balun.

$$Y_{02} = \frac{\mathbf{Y}_{clk}}{2} + \mathbf{Y}_{cm}$$

$$\mathbf{Y}_{cm} = Z_{02}^{-1} - \frac{\mathbf{Y}_{clk}}{2}$$

$$\mathbf{Y}_{cm} = 244.4^{-1} - 0.5 \cdot (2.003 + 0.5954j) \cdot 10^{-3} = (3.090 - 0.2977j) \text{mS}$$

$$\mathbf{Z}_{cm} = \mathbf{Y}_{cm}^{-1} = (320.6 + 30.89j) \Omega$$

(2.12)

where  $Y_{0_2}$  is the required characteristic admittance on the secondary side derived from eq. 2.10 and  $Z_{cm}$  is impedance of the designed matching circuit for the clock lines. The clock input admittance in Eq. 2.11 is calculated with respect to ground, but in Eq. 2.12 admittances are differential. The clock input admittance is therefore divided by two to obtain the differential admittance of the clock inputs.

The parallel matching load has to be a serial combination of a resistor and an inductor, because the reactive part of the matching impedance is positive. The result is compliant with an expectation that an inductor has to compensate the capacitive character of the ADC clock input. The matching load could be a parallel combination of a resistor and an inductor as well, but the inductance of the parallel combination would be excessively high for the clock frequency. The resistance of the matching resistor  $R_{cm}$  equals the real part of the calculated impedance (Eq. 2.12) and the inductance of the serial inductor  $L_{cm}$  is derived from its imaginary part.

$$R_{cm} = \text{Re}(\mathbf{Z}_{cm}) = 442.8 \,\Omega$$

$$L_{cm} = \frac{\text{Im}(\mathbf{Z}_{cm})}{2\pi f} = \frac{30.89}{2\pi \cdot 160 \cdot 10^6} = 30.7 \,\text{nH}$$

(2.13)

The designed matching circuit with the RF balun transformer is depicted in Fig. 2.17. It was tested on the ADC evaluation module. The input reflection was measured to be -16 dB which is sufficient matching for the clock low-pass filter.

Fig. 2.17: Balun transformer and matching load of the ADC clock signal

#### 2.1.7 TTC Receiver

The bunch clock, which the PLL is provided with, is recovered in the FPGA from the TTC signal. The TTC signal is distributed as an optical signal through the optical fibre. The optical signal from the fibre is converted by an optical SFP module. The optical SFP module is a module commonly used in telecommunications. It integrates a reciever and transmitter. Only the receiver is used in the FBCCM as no uplink is required.

All the suitable SFP modules comply with the same standards, thus the TTC Receiver design can be independent of the particular SFP module. The currently used SFP module in the FBCCM is the AFCT-5701PZ. Advantageously it could be exchanged to another optical module in the future if the optical receiver parameters (e.g. wavelength or sensitivity) were redefined.

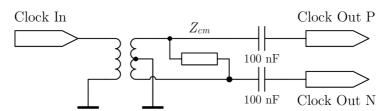

The electrical signal provided by the SFP module is an asynchronous serial data stream. It cannot be processed directly by the FPGA Cyclone III, because this particular FPGA is not equipped with any clock recovery circuit. A dedicated circuit ADN2814 is used for clock recovery from the serial data stream. This circuit contains a PLL which locks on to the input serial stream. The output of the PLL is used as clock signal for the FPGA. This method with PLL is necessary for clock recovery, because the TTC clock is used for the beam synchronous sampling. The recovered clock and the data are used for recovery of the 40 MHz bunch clock in the FPGA. The recovery is based on the decoding of the bi-phase mark code.

Fig. 2.18: Block diagram of the TTC reciever

The block diagram of the TTC receiver is depicted in Fig. 2.18. The TTC clock signal is connected to dedicated FPGA pins thus the signal can be connected to clock nets inside the FPGA effectively. This is required for high performance of the FPGA firmware. The HSMC connector pins are connected to the 2.5 V FPGA banks. The TTC receiver uses the 3.3 V CMOS standard. The TTC data and clock signals do not require any voltage level translation, because both signals are differential LVDS. The voltage level translation is implemented on the loss of lock (LOL) and the loss of signal (LOS), although it is not drawn in the picture. The SFP module and the clock recovery circuit share the management I<sup>2</sup>C bus. The signals of this bus require bidirectional voltage level translators.

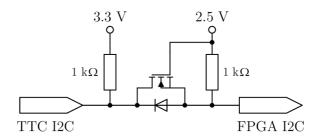

The bidirectional voltage level translation between 3.3 V and 2.5 V logic for I<sup>2</sup>C is performed by the circuit depicted in Fig. 2.19. The circuit contains a N-channel MOSFET and two pull-up resistors. A bipolar transistor cannot be used for this circuit. The internal MOSFET diode pulls down the FPGA side of the bus to ground when any circuit of the TTC side pulls down the bus. The chosen MOSFET has to be sensitive enough for gate-to-source voltage less than 2.5 V, otherwise the circuit would not work. The MOSFET transistor BSS138 is widely used for these purposes.

#### 2.1.8 Indicators and Controls

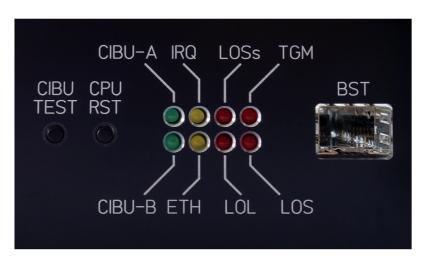

On the front panel (Fig. 2.20) all important indicators and controls have to be visible and accessible to clearly indicate the device status.

Fig. 2.19: Bidirectional voltage level translator for I<sup>2</sup>C

There are three LEDs showing the TTC receiver status (already depicted in Fig. 2.18). Two of them indicate the loss of signal. The loss of signal provided by the SFP module reflects the optical signal level. The loss of signal provided by the ADN2814 corresponds to the electrical signal level of the SFP module. The third LED is active when the PLL in the ADN2814 is not locked on to the input signal. These three LEDs are driven by the TTC receiver hardware, thus their functions cannot be modified.

The other LEDs are driven by the FPGA and in general indicate the status of the FBCCM device. Two LEDs show settings of beam permit flags for the CIBU. Other LEDs blink when the BeagleBone registers an IRQ or when a message is sent to the Ethernet network. The last one indicates an error of telegram reception.

Besides the indicators, two push buttons are placed on the front panel. Both of them are connected to the FPGA. The first button resets the the FPGA and the BeagleBone and the other starts the test of the Interface for CIBU.

Fig. 2.20: Picture of the front panel indicators and controls

#### 2.1.9 Serial Number

The silicon serial number chip DS2411 provides the subsystem with an unique serial number. It is connected by a one-wire data bus to the FPGA. The serial number allows to unambiguously identify each of fabricated boards, e.g. in measurement reports.

### 2.2 CPU Subsystem