# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

## **DEPARTMENT OF MICROELECTRONICS**

ÚSTAV MIKROELEKTRONIKY

# DESIGN OF AD CONVERTER WITH LOW SUPPLY VOLTAGE IN CMOS TECHNOLOGY

NÁVRH PŘEVODNÍKU AD S NÍZKÝM NAPÁJECÍM NAPĚTÍM V TECHNOLOGII CMOS

#### **MASTER'S THESIS**

DIPLOMOVÁ PRÁCE

AUTHOR Bc. Jiří Holas

SUPERVISOR Ing. Vilém Kledrowetz, Ph.D.

**VEDOUCÍ PRÁCE**

**AUTOR PRÁCE**

**BRNO 2016**

# **Diploma thesis**

Masters's study field Microelectronics

Student: Bc. Jiří HolasID: 134312Year of study: 2Academic year: 2015/16

**NÁZEV TÉMATU:**

#### Design of AD converter with low supply voltage in CMOS technology

#### **INSTRUCTION:**

Study different architectures of A/D converters and their performance. Focus on high speed (hundreds of kHz) and medium resolution architectures (>10 bits). Implement the ADC system by designing critical sub-modules on transistor level and verify the overall top-level ADC performance as a whole with Cadence simulation environment.

#### **REFERENCE:**

According to recommendations of supervisor

Assigment deadline: 8.2.2016 Submission deadline: 26.5.2016

Head of thesis: Ing. Vilém Kledrowetz, Ph.D.

Consultant:

doc. Ing. Lukáš Fujcik, Ph.D. Subject Council chairman

#### WARNING:

The autor of this diploma thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The autor is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following oc Act No 121/2000 Coll. on copyright and on amendments to some other laws (the Copyright Act) in the wording for subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapet IV, Article 4 of Criminal Code 40/2009 Coll.

# Diplomová práce

magisterský navazující studijní obor **Mikroelektronika** Ústav mikroelektroniky

Student:Bc. Jiří HolasID: 134312Ročník:2Akademický rok: 2015/16

**NÁZEV TÉMATU:**

#### Návrh převodníku AD s nízkým napájecím napětím v technologii CMOS

#### POKYNY PRO VYPRACOVÁNÍ:

Prostudujte struktury převodníků AD. Zaměřte se na struktury vhodné pro dosažení rozlišení > 10 bitů a zpracování signálů v řádu stovek kHz. Porovnejte vybrané struktury. Na vybrané struktuře proveďte simulace zahrnující reálné parametry dílčích bloků (Matlab). Navrhněte převodník AD na tranzistorové úrovni v technologii TSMC 180 nm a ověřte dosažené parametry.

#### DOPORUČENÁ LITERATURA:

According to recommendations of supervisor

Termín zadání: 8.2.2016 Termín odevzdání: 26.5.2016

Vedoucí práce: Ing. Vilém Kledrowetz, Ph.D.

Konzultant diplomové práce:

doc. Ing. Lukáš Fujcik, Ph.D., předseda oborové rady

#### UPOZORNĚNÍ:

Autor diplomové práce nesmí při vytváření diplomové práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

#### **ABSTRAKT**

Tato diplomová práce se zabývá návrhem 12 bitového řetězového A/D převodníku. Součástí návrhu bylo vytvořit referenční model převodníku v prostředí Matlab a determinovat faktory, které negativně ovlivňují výsledek konverze. S využitím nabytých poznatků navrhnout řetězový převodník na transistorové úrovni v prostředí Cadence. V teoretické části jsou shrnuty základy A/D převodu a dále jsou představeny nejčastěji používané architektury A/D převodníků. V dalších částech je popsán a diskutován vliv neidealit na vlastnosti řetězových převodníků. Praktická část se již věnuje popisu základních charakteristik řetězových převodníků a dokazuje funkci modelu. Z výsledků modelové struktury byly stanoveny reálné parametry, které byly dále využity v procesu tvorby návrhu v CMOS technologii TSMC 0,18μm s nízkým napájecím napětím.

# KLÍČOVÁ SLOVA

Řetězový A/D převodník, model, Matlab, Cadence, TSMC 0,18μm, 2,5 bit MDAC

#### **ABSTRACT**

This master thesis is dedicated to the design of 12-bit pipeline ADC. The part of the design was to create a reference model ADC in the Matlab environment and to determine factors that negatively affect the results of the conversion. Based on experiences gained in the mathematical model, the pipeline ADC on the transistor level was designed in the Cadence environment. The theoretical part summarizes the fundamentals of A / D conversion and introduces the most commonly used architecture of A / D converters. Furthermore, the influence of non-idealities on the conversion process is described and discussed. The practical part is dedicated to description of ADC's model basic characteristics and confirms the model functionality. From the results of the model structure the real parameters were determined and used in the design process in CMOS technology TSMC 0,18µm with low power supply.

#### **KEYWORDS**

Pipelined ADC, model, Matlab, Cadence, TSMC 0.18 µm, 2.5-bit MDAC

#### **DECLARATION**

I declare that I have written my semester project on the theme of "Design of AD converter with low supply voltage in CMOS technology" independently, under a guidance of semester's thesis supervisor and using the technical literature and other sources of information which are all quoted in the thesis and detailed in the list of literature at the end of the thesis.

As the author of semester thesis I furthermore declare that, as regards the creation of this thesis, I have not infringed any copyright. In particular, I have not unlawfully encroached on anyone's personal and/or ownership rights and I am fully aware of the consequences in case of breaking Regulation §11 and the following of the Copyright Act No 121/200Sb., and of the rights related to intellectual property rights and changes in some Acts (Intellectual Property Act) and formulated in later regulations, inclusive of the possible consequences resulting from the provisions of Criminal Act No 40/2009 Sb., Section2, Head VI, Part 4.

| Brno |                      |  |

|------|----------------------|--|

|      | (Author's signature) |  |

Faculty of Electrical Engineering and Communication

Brno University of Technology Technicka 12, CZ-61600 Brno, Czechia

http://www.six.feec.vutbr.cz

Výzkum popsaný v této diplomové práci byl realizován v laboratořích podpořených z projektu SIX; registrační číslo CZ.1.05/2.1.00/03.0072, operační program Výzkum a vývoj pro inovace.

| ACKNOWLEDGEMENT                                                                          |                      |

|------------------------------------------------------------------------------------------|----------------------|

| I would like to thank Mr. Ing. Vilém Kl<br>consultation, and suggestive ideas, that help |                      |

|                                                                                          |                      |

|                                                                                          |                      |

| D.                                                                                       |                      |

| Brno                                                                                     | (Author's signature) |

# **CONTENTS**

| CC  | NTEN   | TS     |                                                          | 1  |

|-----|--------|--------|----------------------------------------------------------|----|

| LIS | T OF F | IGUR   | RES                                                      | 3  |

| LIS | T OF T | ABLE   | ES                                                       | 6  |

| IN  | TRODU  | JCTIC  | ON                                                       | 7  |

| TH  | IEORE1 | ΓICAL  | _ PART                                                   | 8  |

| 1   | AD     | CON    | NVERTERS BASICS OVERVIEW                                 | 8  |

|     | 1.1    | ADC    | CONVERSION CHAIN                                         | 8  |

|     | 1.1    | 1      | Integral Non-Linearity and Differential Non-Linearity    | 11 |

|     | 1.1    | 2      | Signal to Noise Ratio                                    | 12 |

|     | 1.1    | 3      | Signal to Noise and Distortion Ratio                     | 12 |

|     | 1.1    | .4     | Effective Number of Bits                                 | 13 |

|     | 1.2    | ARCH   | HITECTURES                                               | 13 |

|     | 1.2    | 2.1    | Integrating ADC                                          | 14 |

|     | 1.2    | 2.2    | Delta - sigma ADC                                        | 16 |

|     | 1.2    | 2.3    | Successive approximation ADC                             | 17 |

|     | 1.2    | 2.4    | Flash ADC                                                | 19 |

| 2   | PII    | PELIN  | IE ADC                                                   | 21 |

|     | 2.1    | PRINC  | CIPLE OF PIPELINE ADC                                    | 21 |

|     | 2.2    | Muli   | TIPLYING DIGITAL TO ANALOG CONVERTER                     | 22 |

|     | 2.2    | 2.1    | 1.5-bit MDAC versus 2.5-bit MDAC                         | 22 |

|     | 2.3    | TIME   | CORRECTION BLOCK                                         | 24 |

|     | 2.4    | RSD    | CORRECTION BLOCK                                         | 25 |

|     | 2.5    | CALIB  | BRATION TECHNIQUES                                       | 27 |

|     | 2.6    | Influ  | JENCE OF NON-IDEALITIES ON CONVERSION PROCESS            | 27 |

|     | 2.6    | 5.1    | Comparator offset voltage error                          | 28 |

|     | 2.6    | 5.2    | Finite DC gain of operational amplifier                  | 29 |

|     | 2.6    | 5.3    | Finite bandwidth of operational amplifier                | 30 |

|     | 2.6    | 5.4    | Gain error of operational amplifier – capacitor mismatch | 31 |

| PR  | ACTIC  | AL PA  | ART                                                      | 32 |

| 3   | 12     | -BIT F | PIPELINE ADC MODEL                                       | 32 |

|     | 3.1    | Mod    | DEL STRUCTURE                                            | 32 |

|     | 3.1    | 1      | The 2.5-bit sub-ADC & sub-DAC model                      | 34 |

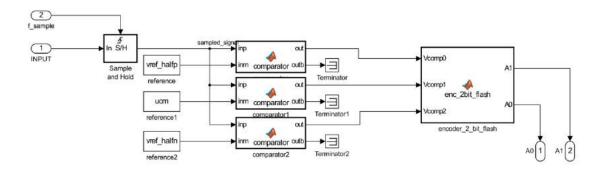

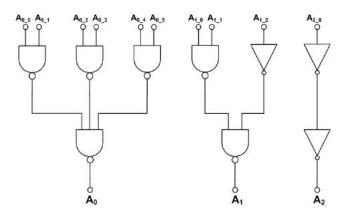

|     | 3.1    | 2      | 2-bit Flash ADC                                          | 38 |

|     | 3.1    | .3     | Time correction block                                    | 40 |

|    | 3    | 3.1.4    | RSD correction block                                            | 42    |

|----|------|----------|-----------------------------------------------------------------|-------|

|    | 3    | 3.1.5    | Model functionality                                             | 44    |

|    | 3    | 3.1.6    | Ideal transfer characteristic – simulation                      | 48    |

|    | 3.2  | Conv     | /ERSION NON-IDEALITIES — SIMULATION                             | 49    |

|    | 3    | 3.2.1    | Comparator offset voltage                                       | 49    |

|    | 3    | 3.2.2    | DC gain error of operational amplifier                          | 51    |

|    | 3    | 3.2.3    | Gain error of operational amplifier - capacitor mismatch        | 53    |

|    | 3    | 3.2.4    | Realistic parameters definition for transistor level design     | 55    |

| 4  |      | 12-BIT I | PIPELINE ADC DESIGN                                             | 57    |

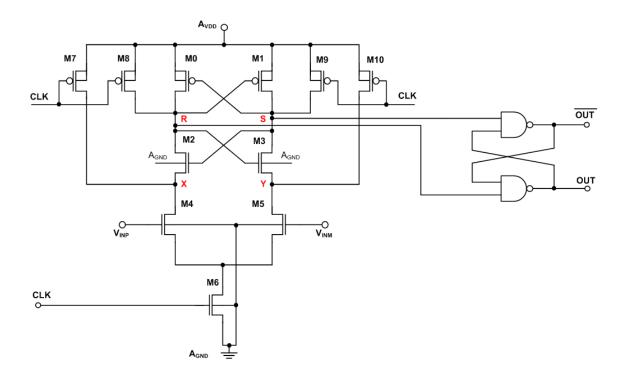

|    | 4.1  | Сомі     | PARATOR                                                         | 57    |

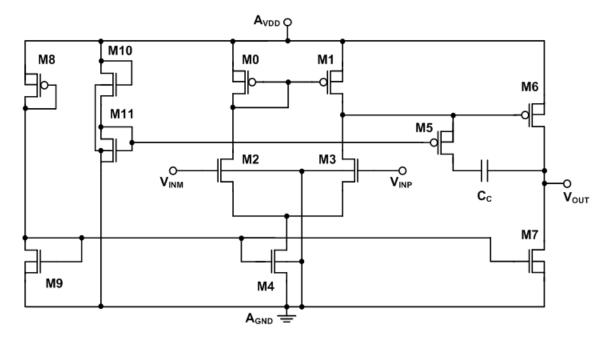

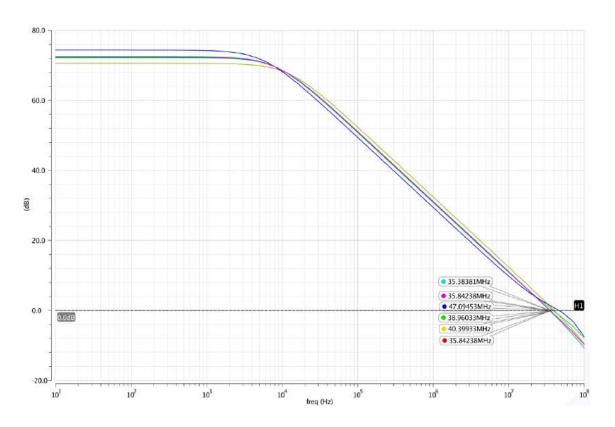

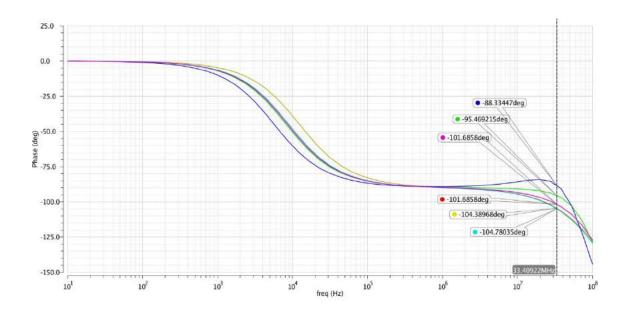

|    | 4.2  | OPER     | ATIONAL AMPLIFIER                                               | 60    |

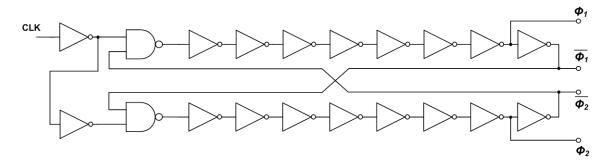

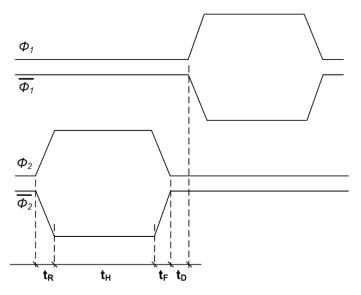

|    | 4.3  | Non-     | OVERLAP GENERATOR                                               | 65    |

|    | 4.4  | THE 2    | P-BIT FLASH ADC                                                 | 67    |

|    | 4.5  | THE 2    | 2.5-BIT MDAC                                                    | 69    |

|    | 4.6  | TIME     | CORRECTION                                                      | 73    |

|    | 4.7  | RSD      | CORRECTION                                                      | 75    |

|    | 4.8  | TOP L    | EVEL DESIGN SIMULATION                                          | 77    |

| 5  |      | NON-ID   | EALITIES COMPENSATION PROPOSAL – FOREGROUND CALIBRATION TECHNIQ | UE 82 |

| 6  |      | CONCLU   | JSION                                                           | 83    |

| ВІ | BLIC | GRAPH    | Υ                                                               | 85    |

| LI | ST O | F USED   | SHORTCUTS AND SYMBOLS                                           | 87    |

| LI | ST O | F ATTA   | CHMENTS                                                         | 88    |

| A. | ГТАС | HMENT    | Γ 0: OP-AMP EVALUATION SIMULATIONS                              | 89    |

| A. | TTAC | HMENT    | T 1: FULL DESIGN SCHEMATICS IN CADENCE ENVIRONMENT – PART 1     | 94    |

| A. | ГТАС | HMENT    | Γ 2: FULL DESIGN SCHEMATICS IN CADENCE ENVIRONMENT – PART 2     | 95    |

| A. | TTAC | CHMENT   | T 3: FULL DESIGN SCHEMATICS IN CADENCE ENVIRONMENT – PART 3     | 96    |

| A. | TTAC | HMENT    | Γ 4: THE 2.5 MHZ PIPELINE ADC – ADDITIONAL SIMULATIONS          | 97    |

# LIST OF FIGURES

| FIGURE 1: ANALOG TO DIGITAL CONVERSION PRINCIPLE                                                          | 8      |

|-----------------------------------------------------------------------------------------------------------|--------|

| FIGURE 2: SAMPLE AND HOLD CIRCUIT - SIMPLIFIED FUNCTION                                                   | 9      |

| FIGURE 3: A) TRANSFER CURVE FOR IDEAL 3-BIT ADC, B) QUANTIZATION ERROR CENTRED ABOUT ZERO                 | 11     |

| Figure 4: ADC architectures comparison                                                                    | 13     |

| FIGURE 5: DUAL-SLOPE INTEGRATING ADC [7]                                                                  | 14     |

| FIGURE 6: DUAL-SLOPE INTEGRATING ADC OUTPUT WAVEFORMS                                                     | 15     |

| Figure 7: First order delta-sigma ADC architecture                                                        | 16     |

| FIGURE 8: SUCCESSIVE APPROXIMATION ADC CONCEPTUAL SCHEMATIC DIAGRAM                                       | 17     |

| FIGURE 9: SUCCESSIVE APPROXIMATION ALGORITHM — GRAPHICAL EXPLANATION                                      | 18     |

| FIGURE 10: FLASH ADC CONCEPTUAL DIAGRAM                                                                   | 19     |

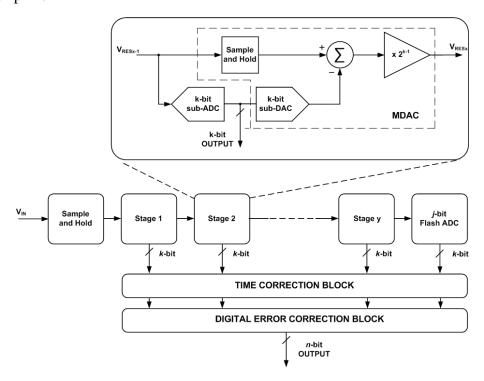

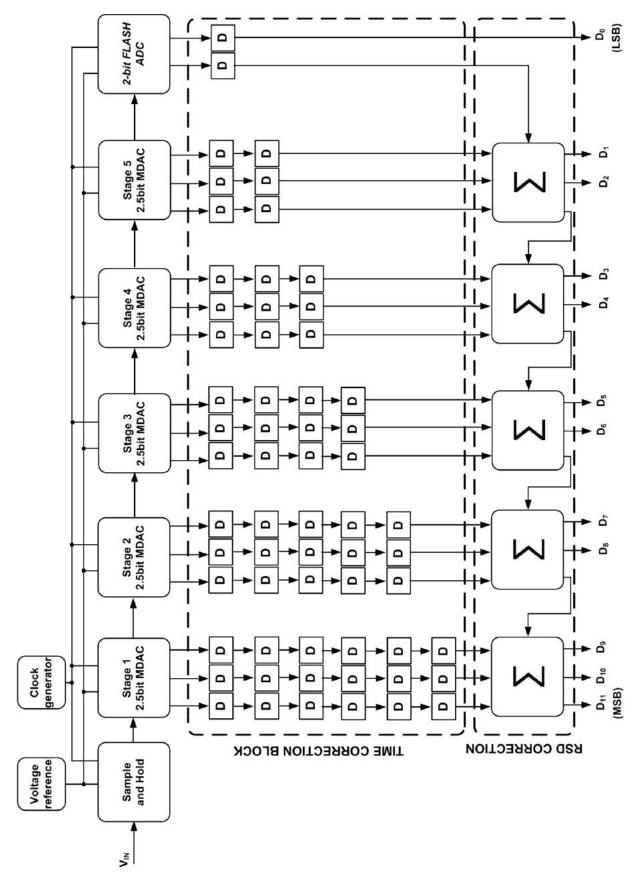

| FIGURE 11: PIPELINED ADC BLOCK SCHEME                                                                     | 21     |

| FIGURE 12: BLOCK SCHEME OF SINGLE PIPELINE STAGE                                                          | 23     |

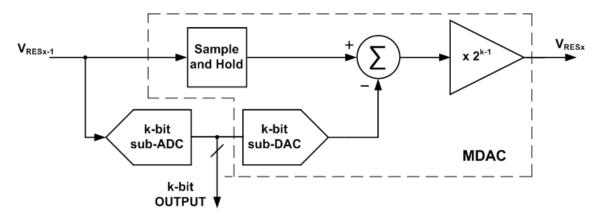

| FIGURE 13: A) 1.5-BIT MDAC AND B) 2.5-BIT MDAC TRANSFER CHARACTERISTIC                                    | 23     |

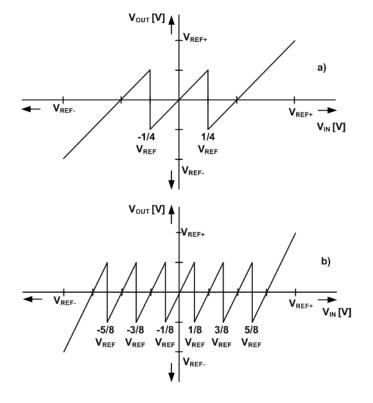

| FIGURE 14 : TIME CORRECTION BLOCK FOR 8-BIT PIPELINED ADC                                                 | 24     |

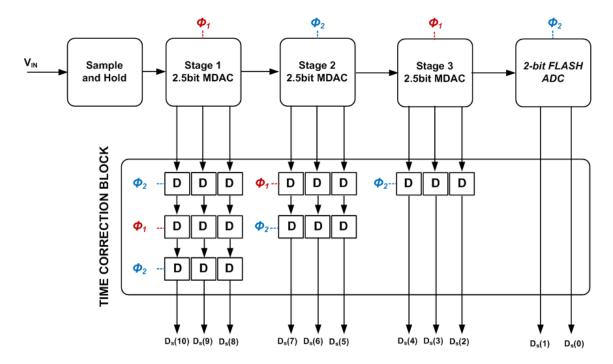

| FIGURE 15: TRANSFER FUNCTION OF 2.5BIT MDAC WITH COMPARATOR OFFSET ERROR.                                 | 25     |

| FIGURE 16: RSD CORRECTION PRINCIPLE                                                                       | 25     |

| FIGURE 17: RSD CORRECTION FUNCTION                                                                        | 26     |

| FIGURE 18: RSD CORRECTION FUNCTION WITH COMPARATOR OFFSET                                                 | 26     |

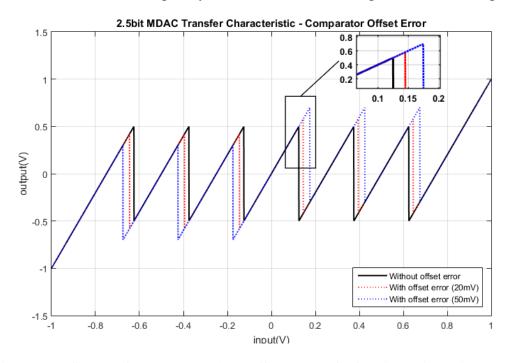

| FIGURE 19: 2.5 BIT MDAC TRANSFER CHARACTERISTIC WITH OFFSET VOLTAGE ERROR                                 | 28     |

| FIGURE 20: FINITE DC GAIN AND ITS INFLUENCE ON TRANSFER FUNCTION ON 2.5 BIT MDAC                          | 29     |

| FIGURE 21: FINITE OP-AMP BANDWIDTH AND IT INFLUENCE ON TRANSFER FUNCTION ON 2.5 BIT MDAC                  | 30     |

| FIGURE 22: GAIN ERROR (CAPACITY MISMATCH) AND ITS INFLUENCE ON TRANSFER FUNCTION                          | 31     |

| FIGURE 23: 12-BIT PIPELINED ADC MODEL WITH 2.5-BIT MDAC, TIME CORRECTION AND DIGITAL RSD CORRECTION BI    | LOCK — |

| BLOCK SCHEMATIC                                                                                           | 33     |

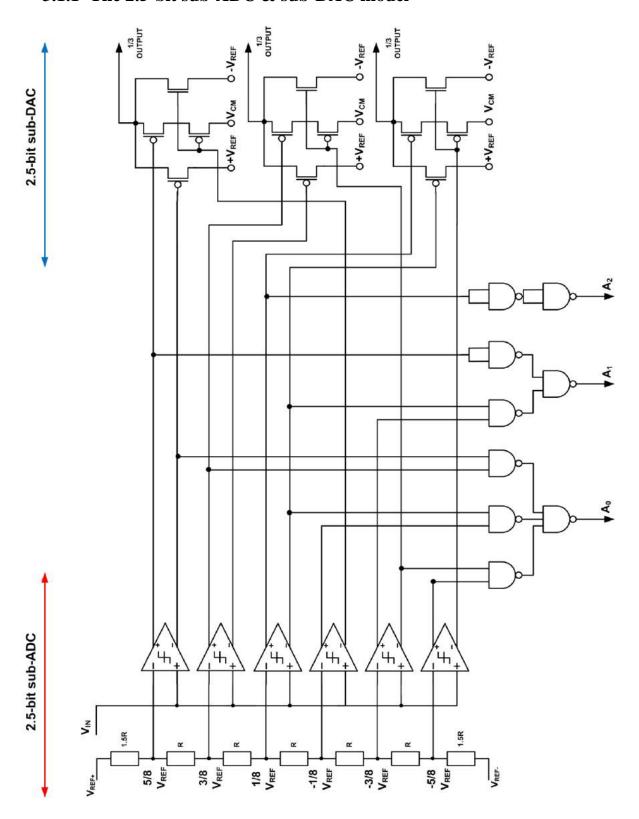

| FIGURE 24: SUB-ADC AND SUB-DAC SCHEMATIC FOR 2.5-BIT MDAC — STRUCTURAL LEVEL [2]                          | 34     |

| FIGURE 25: REAL SCHEMATIC OF 2.5-BIT MDAC IN MATLAB ENVIRONMENT                                           | 36     |

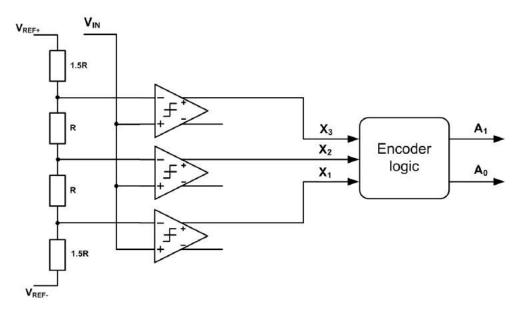

| FIGURE 26: 2-BIT FLASH ADC – CONCEPTUAL SCHEMATIC [2]                                                     | 38     |

| FIGURE 27: 2-BIT FLASH ADC – MATLAB SCHEMATIC                                                             | 39     |

| FIGURE 28: CONCEPTUAL BLOCK DIAGRAM OF TIME CORRECTION FOR 12-BIT PIPELINED ADC                           | 40     |

| FIGURE 29: TIME DELAY BLOCK FOR 12-BIT PIPELINED ADC – MATLAB SCHEMATIC                                   | 41     |

| FIGURE 30: RSD CORRECTION BLOCK FOR 12-BIT PIPELINED ADC — CONCEPTUAL SCHEMATIC                           | 42     |

| FIGURE 31: RSD CORRECTION BLOCK FOR 12-BIT PIPELINED ADC – REAL MATLAB IMPLEMENTATION                     | 42     |

| FIGURE 32: 12-BIT PIPELINED ADC - TOP LEVEL SCHEMATIC                                                     | 43     |

| FIGURE 33 : OUTPUT OF 12-BIT PIPELINED ADC. TOP — INPUT SIGNAL, BOTTOM — ADC OUTPUT                       | 44     |

| FIGURE 34: 12-BIT PIPELINE ADC. FIRST STAGE RESIDUE. TOP — INPUT SAMPLED SIGNAL. BOTTOM — RESIDUAL SIGNAL | AT THE |

| OUTPUT OF 1 <sup>ST</sup> STAGE                                                                                   | 45    |

|-------------------------------------------------------------------------------------------------------------------|-------|

| FIGURE 35: RESIDUAL SIGNALS AT THE END OF EACH STAGE. TOP — INPUT SIGNAL, THE OTHERS, RESIDUAL SIGNALS FOR        |       |

| PARTICULAR STAGES                                                                                                 | 46    |

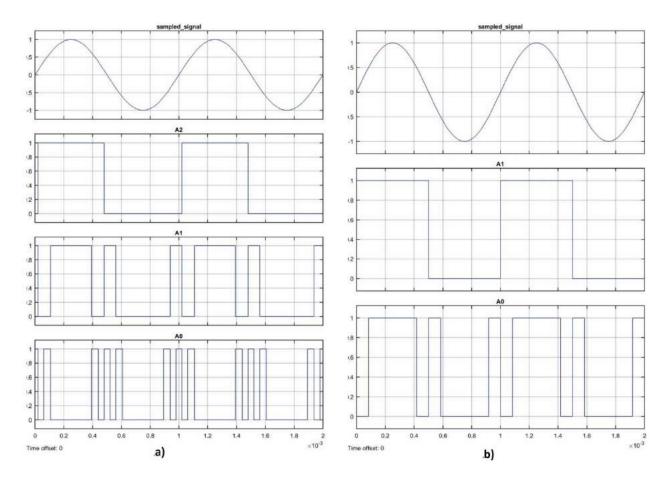

| FIGURE 36: A) OUTPUTS OF 2.5-BIT SUB-ADC, B) OUTPUTS OF 2-BIT FLASH ADC                                           | 47    |

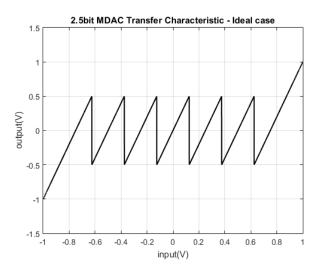

| FIGURE 37: IDEAL TRANSFER CHARACTERISTIC OF 2.5-BIT MDAC – SIMULATION RESULT                                      | 48    |

| FIGURE 38: A) IDEAL POWER SPECTRAL DENSITY OF THE ADC OUTPUT, B) IDEAL INL AND DNL, C) OUTPUT STAIRCASE           |       |

| FUNCTION — SIMULATION RESULTS                                                                                     | 48    |

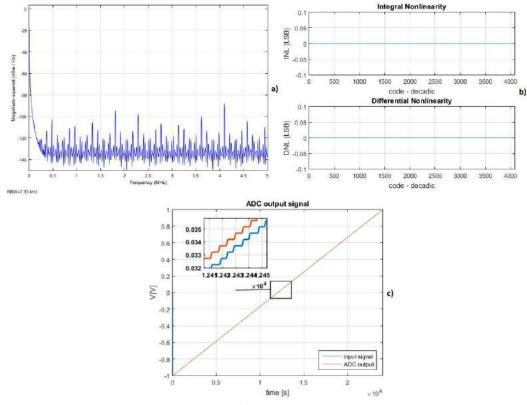

| FIGURE 39: INFLUENCE OF COMPARATOR VOLTAGE OFFSET ON TRANSFER FUNCTION — SIMULATION RESULT                        | 49    |

| Figure 40: A) Power spectral density for ADC with 150mV offset error voltage, B) corresponding INL                | AND   |

| DNL and c) corresponding ADC transfer function.                                                                   | 50    |

| Figure 41: Influence DC gain error on transfer function                                                           | 51    |

| FIGURE 42: A) POWER SPECTRAL DENSITY OF ADC WITH 50DB DC GAIN, B) CORRESPONDING INL AND DNL, C)                   |       |

| CORRESPONDING ADC OUTPUT                                                                                          |       |

| FIGURE 43: INFLUENCE OF CAPACITOR MISMATCH ON TRANSFER FUNCTION                                                   |       |

| FIGURE 44: A) POWER SPECTRUM DENSITY FOR ADC WITH 1% CAPACITOR MISMATCH ERROR, B) CORRESPONDING IN                |       |

| DNL, c) AN ADC "RIPPLED" OUTPUT.                                                                                  |       |

| FIGURE 45: FFT FOR OP-AMP GAIN ERROR A) 0.1%, B) 0.25%, C) 0.5% AND D) 1%                                         |       |

| FIGURE 46: MAXIMAL ACHIEVABLE ENOB AND SNDR IN MODEL SIMULATION ( $A0 = 60$ DB, $V_{OFFSET} = 140$ MV, $A_{MISM}$ |       |

| 0.1%)                                                                                                             |       |

| FIGURE 47: COMPARATOR AT TRANSISTOR LEVEL SCHEMATIC                                                               |       |

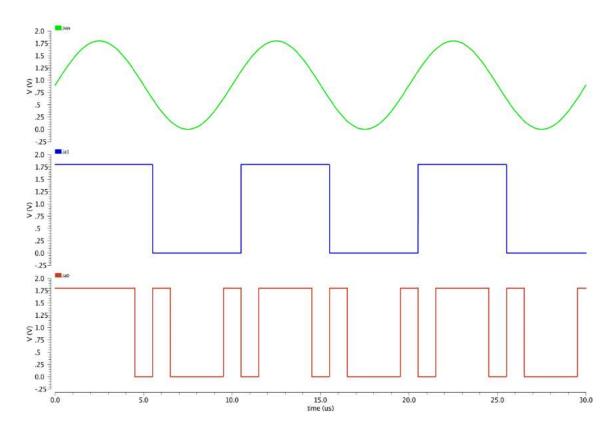

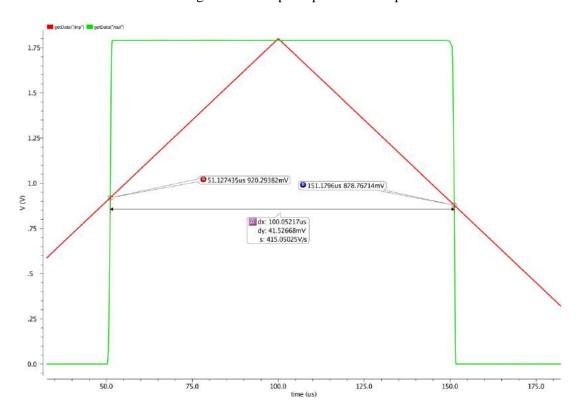

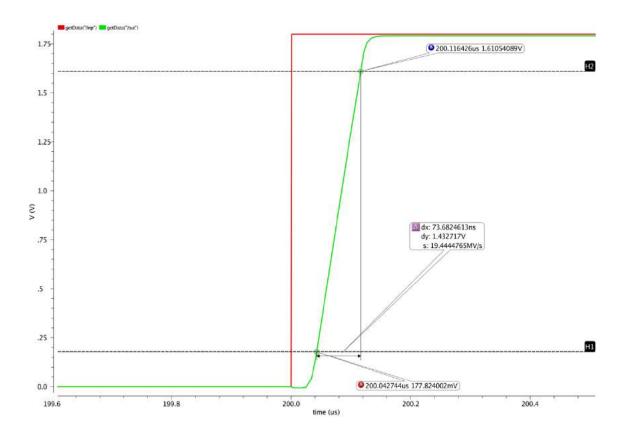

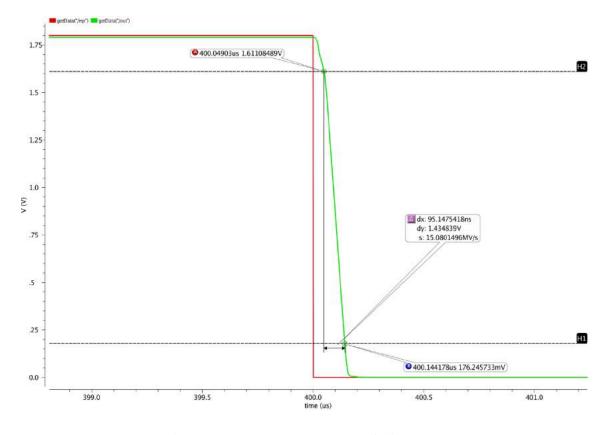

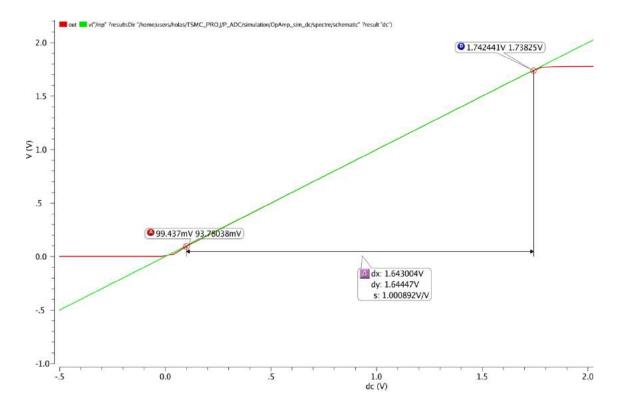

| FIGURE 48: CLOCKED COMPARATOR OUTPUTS                                                                             |       |

| FIGURE 49: OP-AMP SCHEMATIC                                                                                       |       |

| FIGURE 50: NON-OVERLAP GENERATOR SCHEMATIC VIEW                                                                   |       |

| FIGURE 51: IDEA OF GENERATED CLOCK PULSES                                                                         |       |

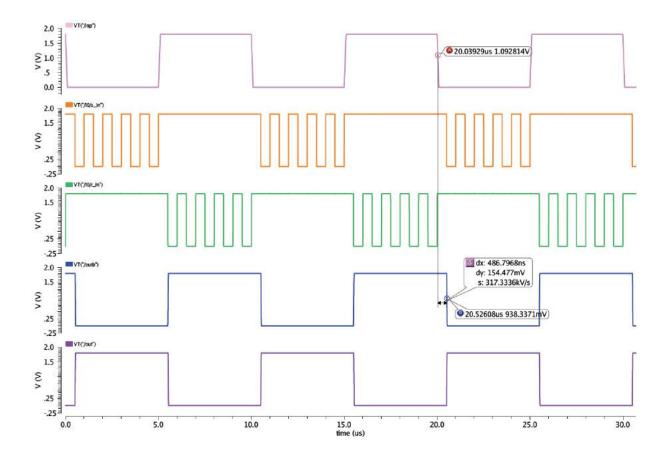

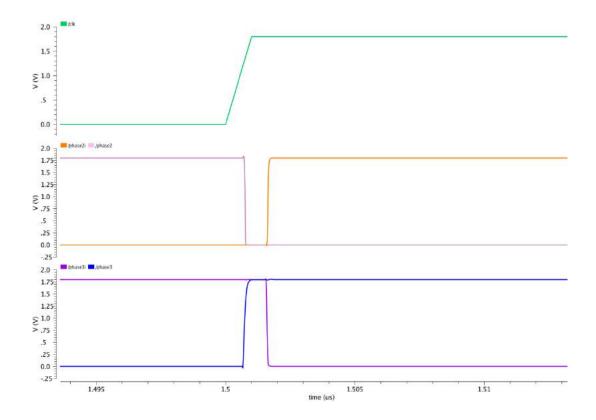

| FIGURE 52: NON-OVERLAP GENERATOR OUTPUTS                                                                          |       |

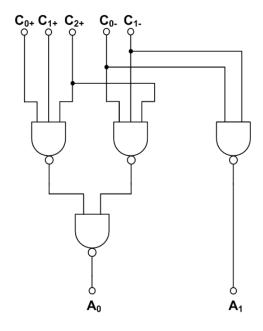

| FIGURE 53: 2-BIT FLASH ENCODER SCHEMATIC                                                                          |       |

| FIGURE 54: 2-BIT FLASH ADC OUTPUTS                                                                                |       |

| FIGURE 55: MDAC DIGITAL OUTPUT LOGIC                                                                              | 69    |

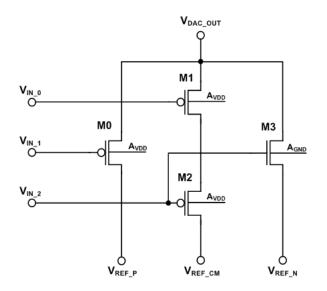

| FIGURE 56: 1.5-BIT SUB-DAC — MULTIPLEXER.                                                                         |       |

| FIGURE 57: SUBTRACTION CIRCUIT                                                                                    |       |

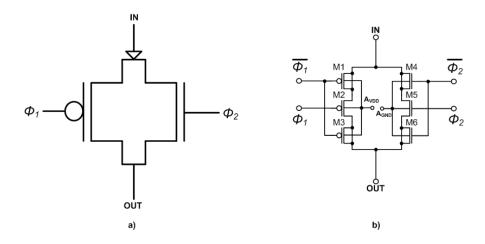

| Figure 58: a) Transmission Gate symbol, b) corresponding transistor level schematic                               |       |

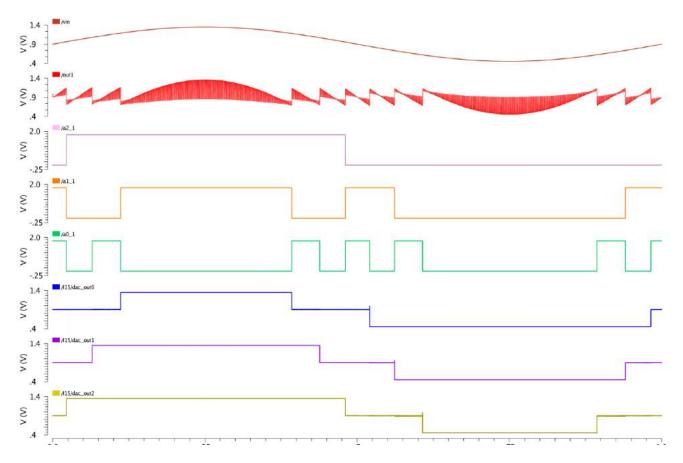

| FIGURE 59: THE 2.5-BIT MDAC OUTPUTS (FROM TOP TO BOTTOM): A) INPUT SIGNAL, B) OUTPUT RESIDUUM, C) DIGI            | TAL   |

| OUTPUT A2,D) DIGITAL OUTPUT A1, E) DIGITAL OUTPUT A0, F) $-$ H) SUB-DAC OUTPUTS 0,1,2                             |       |

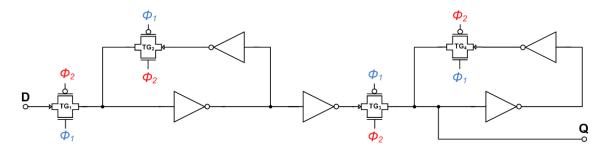

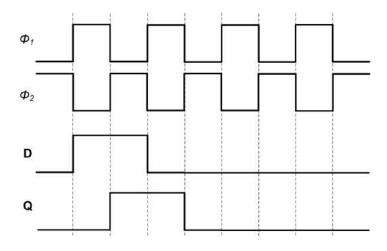

| FIGURE 60: D FLIP-FLOP MADE OF INVERTERS AND TRANSMISSION GATES                                                   | 73    |

| FIGURE 61: D FLIP-FLOP AS A SHIFT REGISTER                                                                        | 73    |

| FIGURE 62: D FLIP-FLOP FUNCTION DEMONSTRATION (FROM TOP TO BOTTOM): A) INPUT SIGNAL, B) DELAYED SIGNAL            | -     |

| CLOCK PHASE 1, D) CLOCK PHASE 1 INVERTED                                                                          | 74    |

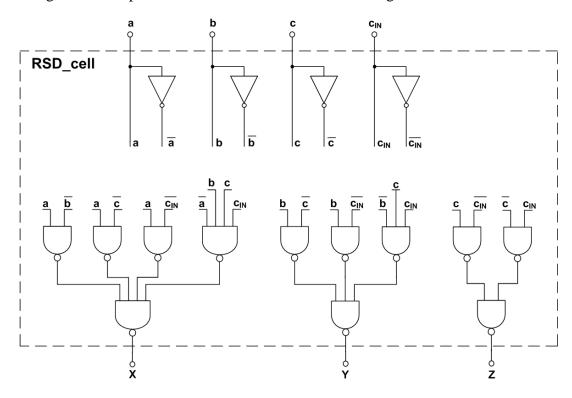

| FIGURE 63: RSD CORRECTION BLOCK SCHEMATIC                                                                         | 75    |

| FIGURE 64: IMPLEMENTATION OF RSD CELL USING NAND GATES                                                            | 76    |

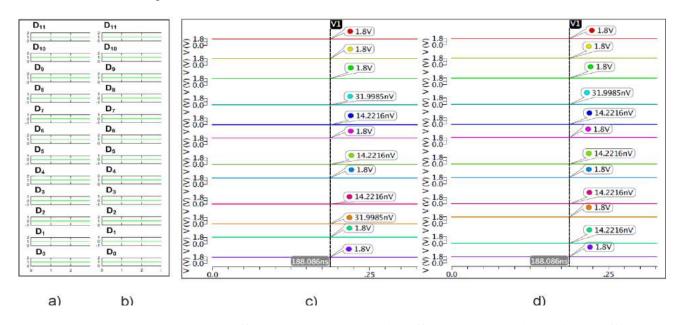

| Figure 65: RSD outputs: a) without offset error – Matlab, b) with offset error – Matlab, c) without o             | FFSET |

| ERROR – CADENCE, D) WITH OFFSET ERROR – CADENCE,                                                                  | 76    |

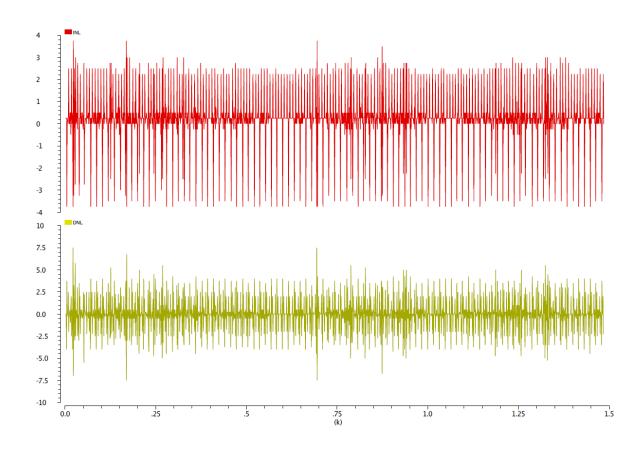

| FIGURE 66: EXTRACTED INL (TOP) AND DNL (BOTTOM)                                                                   | 77    |

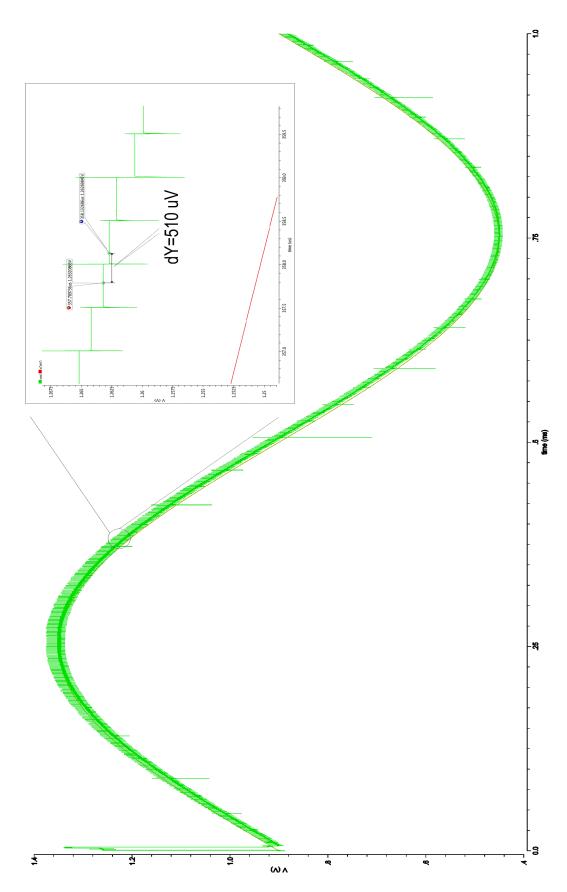

| FIGURE 67: RECONSTRUCTED ADC OUTPUT SIGNAL                                          | . 78 |

|-------------------------------------------------------------------------------------|------|

| FIGURE 68: DIGITAL OUTPUT WAVEFORMS OF 12-BIT PIPELINE ADC, MSB (TOP), LSB (BOTTOM) | . 79 |

| Figure 69: Residual signal between individual stages Stage1 (top) –Stage 5 (bottom) | 80   |

| FIGURE 70: FOREGROUND CALIBRATION BLOCK MODEL PROPOSAL                              | 82   |

# LIST OF TABLES

| TABLE 1: SUB-DAC TRUTH TABLE — SUMMATION OF THREE MULTIPLEXERS [2]        | 35 |

|---------------------------------------------------------------------------|----|

| TABLE 2: SUB-ADC AND SUB-DAC TRUTH TABLE [2]                              | 35 |

| Table 3: Table of multiplexers output summation [2]                       | 37 |

| Table 4: Encoder logic truth table                                        | 39 |

| Table 5: Technological parameters for TSMC 0.18mm                         | 57 |

| Table 6: Comparator – transistor's dimensions and achieved specifications | 59 |

| Table 7: Op-Amp specifications                                            | 63 |

| TABLE 8: OP-AMP CALCULATED AND OPTIMIZED TRANSISTORS DIMENSIONS           | 63 |

| Table 9 : Op-Amp's achieved specifications                                | 64 |

| TABLE 10: THE 12-BIT PIPELINE ADC ACHIEVED SPECIFICATIONS                 | 81 |

# **INTRODUCTION**

This master's thesis is dedicated to ADC conversion process and its classification. The first part of the document is a theoretical part, which deals with introducing the reader into Analog-to-Digital conversion basics. The fundamental parameters such an SNR, SNDR, INL, DNL and other common terms are introduced and explained.

The work continues with various ADC architectures introduction and aims to explain their advantages and disadvantages. Then the preferable pipelined ADC architecture is chosen and described in details.

Next part of the project is dedicated to the real design of 12-bit pipelined ADC model in Matlab environment. The model serves to determine weak parts of conversion chain in this structure and serves as a reference for following realization in TSMC 0.18µm CMOS technology.

The stated parameters were taken into account during the real design process in Cadence environment in next part of the document. This chapter also reveals the step-by-step design of individual stages along with numerous simulation results that confirm functionality of the converter.

At the end of the practical part, the model and real design results are discussed and compared. The theoretical proposal how to compensate non-idealities is introduced.

# THEORETICAL PART

This part of the document is dedicated to AD (Analog to Digital) conversion principles. It consists of detailed ADC function description and point to reveal conversion non-idealities.

# 1 AD CONVERTERS BASICS OVERVIEW

#### 1.1 ADC conversion chain

The AD converters facilitate the conversion of an analog input signal to relevant output digital signal. The input is an mostly voltage signal and the output represents a digital word with stated bit resolution. In Figure 1 is shown how the input signal is converted into its digital form.

Figure 1: Analog to digital conversion principle

The first segment of conversion chain is an anti-aliasing filter. Basically, it is represented by a low-pass filter. The reason why this block is used in almost every converter is due to filtering capability of higher frequencies to fulfill a Nyquist criterion. The Nyquist criterion (or theorem) determines maximal input frequency that is sensed and processed by converter to avoid appearance of aliasing effect. The equation (eq.1) shows,

$$f_{\text{Sample}} \ge 2 \cdot f_{\text{in_max}},$$

(1)

where  $f_{\text{Sample}}$  is ADC sample frequency and  $f_{\text{in\_max}}$  is maximal input frequency. If this condition is accomplished, the aliasing effect will not intervene the output signal and the signal obtained by conversion can be reversely reconstructed [1].

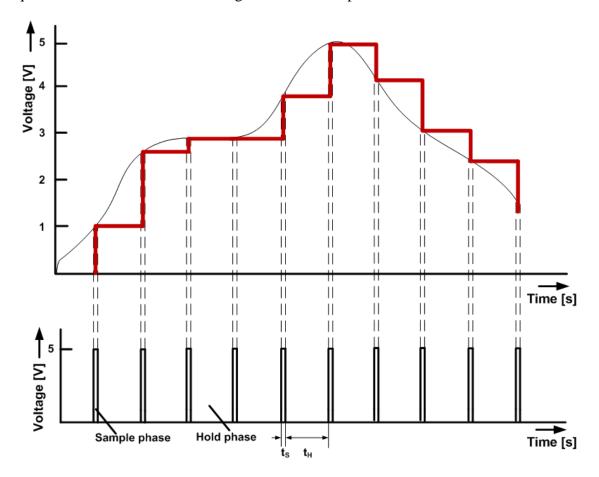

When the signal passes through anti-aliasing filter is further fed into Sample and Hold circuit (S&H). This signal is "sampled". It means that appropriate input voltage is held at the output for defined period of time. That is necessary for next processing in quantization block where actual signal value is compared to reference value.

Figure 2: Sample and Hold circuit - simplified function

The principle of S&H circuit function is shown in Figure 2. During the sampling phase, which should be as narrow as technology allows, the input voltage is sampled until the hold phase time occurs. During the hold phase is the sampled signal value held in memory – constant – as long as another sampling time arises. It serves to pick and maintain the actual signal value for quantization. All mentioned above depend on sampling speed. If the speed of sampling increases twice, the hold time decreases for the same amount and it introduces the main limitation of these types of circuits. In every real circuit, we have to calculate with settling time and overshoots caused by transitions during switching. As far as we know these limitations, we have to consider them in real design because sampling speed or sampling rate belongs to one of the key parameters in ADC conversion systems. Other non-idealities related with sampling are mentioned below [1].

#### Non-idealities in Sample and Hold circuits [1]:

- slew rate,

- settling time,

- nonlinearity,

- gain error,

- gain offset,

- aperture error.

Another block in conversion chain is quantization circuit where constant values from previous sample and hold block are converted into digital form. Quantization is a process that assigns a discrete binary value to individual sample. This value is influenced by resolution of whole ADC. Resolution is determined by number of levels which the input signal can be divided into. If we assume that the output digital word is usually expressed by binary code, then the resolution is determined by number of bits – in the other words, length of digital word [1].

Let's consider that we have 12-bit ADC, the resolution can be derived from the following formula

$$Resolution = 2^{N}, (2)$$

where N designates number of bits of the converter. If we substitute N into equation, the resolution (or the amount) of discrete levels is

$$Resolution = 2^{12} = 4096 \text{ levels.}$$

(3)

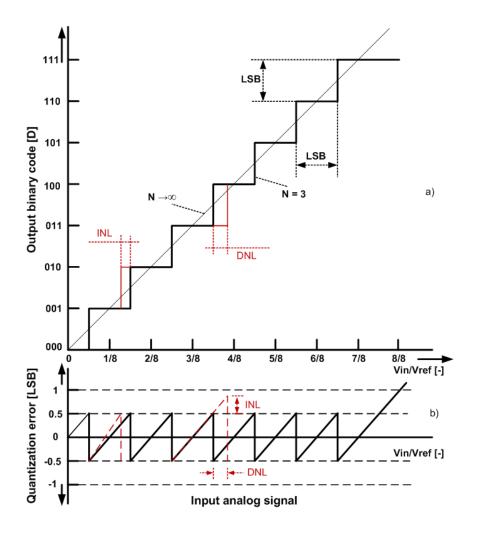

Unfortunately, a quantization error so-called quantization noise is formed during this process. If we want to minimize these errors in order to obtain uncorrupted digital word, the quantization noise has to be equal to one-half of LSB (Least Significant Bit) [1]. A transfer characteristic for an ideal 3-bit ADC and its quantization error is shown in Figure 3. As can be seen in this plot, the quantization error for ideal case is equal to one-half of LSB.

Figure 3: a) Transfer curve for ideal 3-bit ADC, b) quantization error centred about zero

## 1.1.1 Integral Non-Linearity and Differential Non-Linearity

The red curve in Figure 3 reveals further very important dynamic parameters such as INL (Integral Non-Linearity) and a DNL (Differential Non-Linearity) and can be thought of quantization error consequences.

- INL is defined as a deviation of an actual transfer function from ideal straight line connection between two end points of the converter's transfer function.

- **DNL** is defined as a difference between the size of an actual and an ideal step size. The ideal step size is equal to 1 LSB or  $V_{LSB} = V_{FS}/2^N$  where  $V_{FS}$  is a full-scale input range.

From mathematical point of view, the DNL can be described as

$$DNL(k) = \frac{(step \ size \ of \ code(k) - V_{LSB})}{V_{LSB}} \quad [LSB]$$

(4)

and for INL the following equation applies,

$$INL(k) = \sum_{i=0}^{k} DNL(i) \quad [LSB]. \tag{5}$$

#### 1.1.2 Signal to Noise Ratio

Signal to Noise Ratio (SNR) is the ratio of the power of full-scale input signal to total noise power present at the output of a converter. The SNR can be obtained by applying a sinusoidal signal to the converter and performing a Fast Fourier Transform (FFT) of the digital output of the converter. The equation to determine this parameter is then,

$$SNR = 10 \cdot log \left( \frac{Signal\ power}{Total\ Noise\ Power} \right) \quad [dB] \tag{6}$$

The maximum achievable theoretical SNR is given by,

$$SNR = 6.02 \cdot N + 1.76 \ [dB]$$

(7)

where N is ADC resolution and if only quantization noise is taken into account [3].

SNR parameter neglects higher harmonics of the signal but it consists of quantization and white noise.

### 1.1.3 Signal to Noise and Distortion Ratio

The Signal to Noise and Distortion Ratio is the ratio between the power of the full-scale input signal and total noise including harmonics. The corresponding formula can be written as

$$SNDR = 10 \cdot log \left( \frac{Signal\ power}{Noise\ and\ Harmonic\ Distortion\ Power} \right) \ [dB].$$

(8)

#### 1.1.4 Effective Number of Bits

The Effective Number of Bits (ENOB) can be calculated from SNDR by following equation

$$ENOB = \frac{SNDR - 1.76}{6.02} \quad [bits] \tag{9}$$

#### 1.2 Architectures

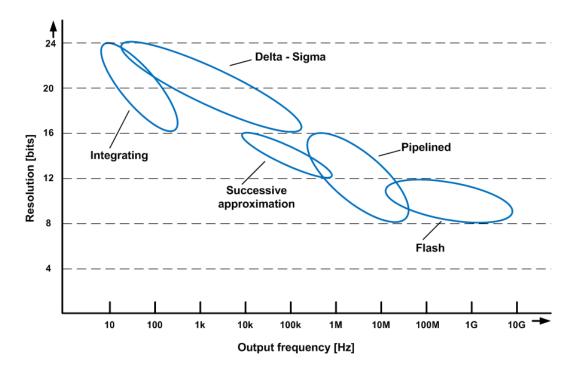

In the present time, ADCs come in several basic architectures, although many variations exist for each type. The most used structures were chosen and they will be explained in next parts of a document in a briefly way. The attention is aimed to introduce each architecture and compare its advantages and disadvantages with the other ones.

Figure 4: ADC architectures comparison

In Figure 4 is shown a resolution dependency on sample rate of individual converter architectures. It can be read out from a graph above that each architecture has its trade-offs due the parameters which influence the other. For example, very fast flash ADC architecture achieves very high conversion speed at the cost of lower resolution. On the other side the integrating ADC excels with very high-resolution parameter but the conversion rate comes up to units of kHz. Every architecture has got a different ratio of trade-offs and the next chapter aims to explain them shortly.

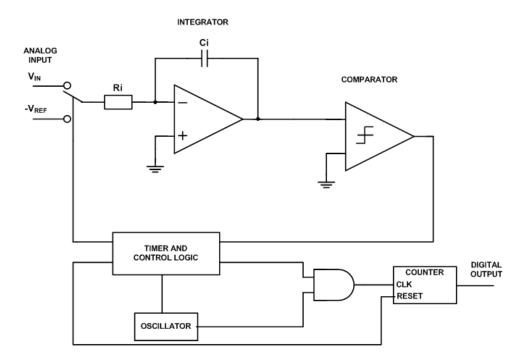

#### 1.2.1 Integrating ADC

The history of integrating ADC's dates back to 1950's and was a real breakthrough in high-resolution applications such as digital voltmeters [7]. The most used variant - a dual-slope integrating ADC is shown in Figure 5 and its output waveforms can be seen in Figure 6.

Figure 5: Dual-slope integrating ADC [7]

The input signal  $V_{\rm IN}$  is applied to an integrator. At the same time, the enable signal for the counter is asserted and it starts counting clock pulses. The time of integrating is fixedly determined. When this time is reached the reference voltage with a different polarity is applied to the integrator. The accumulated charge on integrating capacitor is directly proportional to average value of the input over integration interval T and can be expressed as

$$Charge_{slope} = \frac{V_{\rm IN}}{R \cdot C}. \tag{10}$$

The capacitor is discharging with slope that corresponds to equation

$$Discharge_{slope} = \frac{V_{\text{REF}}}{R \cdot C},\tag{11}$$

where RC is a charge/discharge constant of the capacitor. At the same time, the counter is again counting from zero and when the integrator output reaches zero, the count is stopped with the simultaneous reset of analog circuitry.

If we put equation (10) and equation (11) in equivalence, we can determine the discharge time that represents digital output word.

$$\frac{V_{\rm IN}}{R \cdot C} \cdot T = \frac{V_{\rm REF}}{R \cdot C} \cdot t_{x}$$

$$t_{x} = \frac{V_{\rm IN}}{V_{\rm REF}} \cdot T \quad [s]$$

(12)

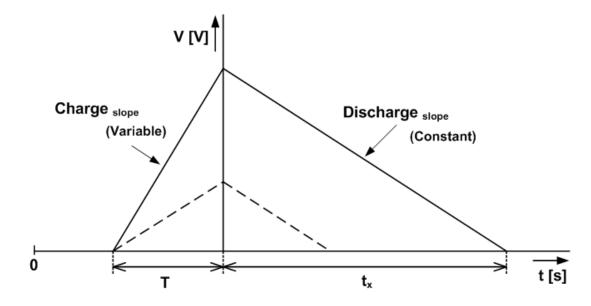

As is shown in Figure 6, the discharge slope remains still the same. On the other hand, the charging slope depends of on input signal amplitude.

Figure 6: Dual-slope integrating ADC output waveforms

#### **Advantages:**

- high reachable resolution (up to 24 bits),

- conversion accuracy is independent of capacitance and clock frequency affects both slopes (charge and discharge) by the same ratio.

#### **Disadvantages:**

— relatively low conversion speed – units of kHz.

#### 1.2.2 Delta - sigma ADC

A delta-sigma ADC is known as an oversampling data converter due to its operation on much higher samplings rates than the Nyquist rate [8]. The relation between how much is the sampling frequency above Nyquist frequency describes an oversampling ratio (OSR). With increasing OSR the quantization noise power decreases.

Another approach connected with oversampling ADCs is a noise-shaping technique. Thank this method the quantization noise is moved to higher frequencies using negative feedback, where is filtered out by digital low pass filter. It is not possible to eliminate quantization noise totally, but can be reduced by a significant amount.

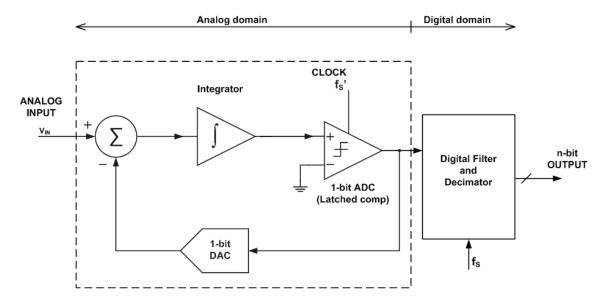

Figure 7: First order delta-sigma ADC architecture

With the increase of resolution of the quantizer, the total resolution of ADC can be enhanced. This method is limited with linearity of designed DAC and special method in layout procedure must be used. Another way how to enhance resolution is to increase the order of the modulator. This approach has its problems as well. With increasing order of the modulator, the stability problems are starting to enforce.

#### **Advantages:**

- high reachable accuracy (up to 24 bits),

- higher speed with respect to integrating ADC.

#### **Disadvantages:**

- higher speed at the cost of complexity,

- stability problems in higher order designs.

#### 1.2.3 Successive approximation ADC

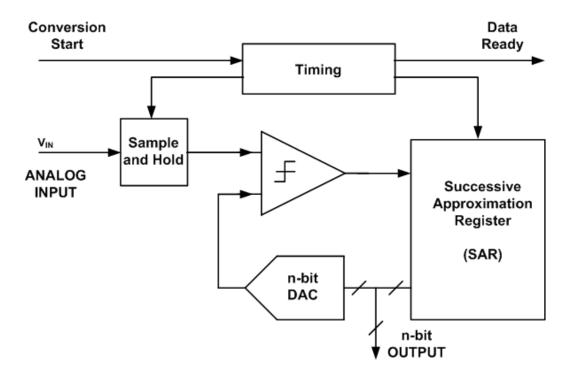

The conceptual block diagram of a successive approximation ADC is shown in Figure 8. It performs a conversion on command, which means, that for every conversion cycle the acquisition command has to be asserted. The principle of SAR ADC is as follows [9].

Figure 8: Successive approximation ADC conceptual schematic diagram

The input signal is first sampled and then compared to midscale DAC reference. The comparator, which ensures the comparison process, decides whether the sampled input value is above the midscale or not and the result (MSB) is stored in successive approximation register (SAR). The DAC is internally set to one-quarter or three-quarter scale (depending on the value of bit 1) and the comparator makes the decision for a less significant bit of the conversion. The result is again stored in shift register and the process continues until all of the bit values are determined. Accordingly to achieve *N*-bit resolution, the SAR ADC requires *N* clock cycles. Due to limited DAC linearity, the calibration is often used to achieve higher resolutions.

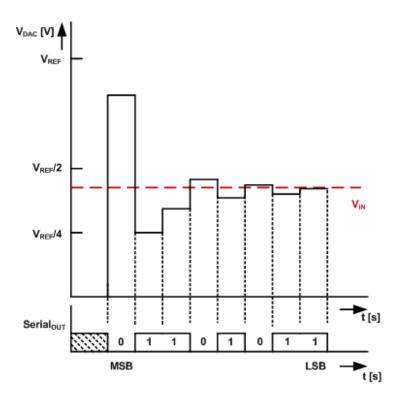

In Figure 9 is explained a successive approximation algorithm principle graphically.

Figure 9: Successive approximation algorithm – graphical explanation

## **Advantages:**

- high resolution (up to 16 bits),

- conversion accuracy,

- low power consumption.

## **Disadvantages:**

- higher demands on inner circuitry design,

- lower sampling rate with comparison to Flash and Pipelined ADCs.

#### 1.2.4 Flash ADC

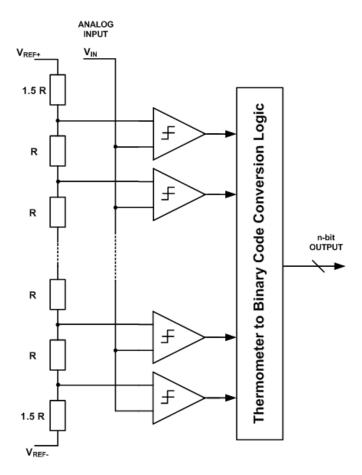

Flash ADCs, as well known as parallel converters, are the fastest converters in semiconductor technology [3],[10]. One example of simple flash ADC is shown in Figure 10. It uses a series of comparators  $(2^N)$  and resistors  $(2^N-1)$  to quantize the input analog signal in parallel and produce the output code, that is so called "thermometer code". The designation comes from analogy with well-known medical thermometer. Produced code is usually converted into N-bit binary signal, since the  $2^N-1$  data outputs are not practical at all.

Figure 10: Flash ADC conceptual diagram

The function of Flash ADC is simple. The input signal is applied to all comparators at once, so the thermometer output is delayed by only one comparator delay from the input. The additive delay is caused by few gate delays in binary conversion logic, so overall conversion speed is very fast. However, the flash converter uses a very large number of comparators and resistors, it is limited to low resolution. Another fact is that the speed of comparator is directly proportional to its bias current. This consequently results in high power consumption specifications.

## **Advantages:**

- fastest architecture,

- design simplicity.

## **Disadvantages:**

- high demands on comparators and resistors accuracy,

- high power consumption,

- high number of components (comparators, resistors),

- low reachable resolution (up to 12 bits).

# 2 PIPELINE ADC

This chapter aims to closely describe pipeline ADC architecture and define its major parameters that influence conversion speed, resolution, and accuracy. It further presents principle of operation and introduces a reader to basic converter block function. Also, it declares possible sources of errors and non-idealities and proposes a possibility for its compensation.

# 2.1 Principle of pipeline ADC

Pipeline ADCs are commonly used in applications that achieve resolution up to 16 bits and sampling rate in range from dozens MS/s up to hundreds MS/s. The pipelined architecture had largely replaced flash ADCs in modern applications due to its higher resolution, although the sampling rate is lower. As a trade for parameters, the pipelined ADC uses more sophisticated approaches to get higher resolution at the cost of system complexity. The main application portfolio of pipelined ADCs remains in image processing, communication and video processing [4],[5]. The typical pipeline architecture is illustrated in Figure 11. It contains five basic elements such as Sample and Hold circuit, a sub-ADC, a sub-DAC, a summation block and an inter-stage gain amplifier

Figure 11: Pipelined ADC block scheme

The operation principle of every single stage is as follows. The input analog signal is captured by sample and hold circuit. In sub-ADC is quantized and digital output is produced. The processed signal is sensed by sub-DAC and converted back to analog signal, where is subtracted from the original signal. After this step, the residuum of original signal is obtained and gained up to the full-scale range through the inter-stage amplifier. The residual signal (quantization error) is passed to next stage, where the described procedure is repeated. The last stage is usually *j*-bit flash ADC because at the end of the pipeline chain is no need to generate residual signal [4].

Due to the presence of sample and hold circuit in every stage, the conversion is done for each stage at the same time. Obviously, this type of signal processing brings a latency of y-clock cycles into process. Latency is described as a time difference between first sampled input signal and corresponding digital output prepared at the output. However, the latency is not present for next sample acquisition, since the y-clock cycles passed away. In other words, after y-clock cycles the overall ADC latency is equal to single clock cycle. The total conversion speed is determined by the speed of the single stage, but is independent of a number of stages [5]. In fact, the particular outputs of single stages are generated at the different time, the synchronization is necessary. The time synchronization block serves for this purpose and it will be discussed later in chapter 2.3.

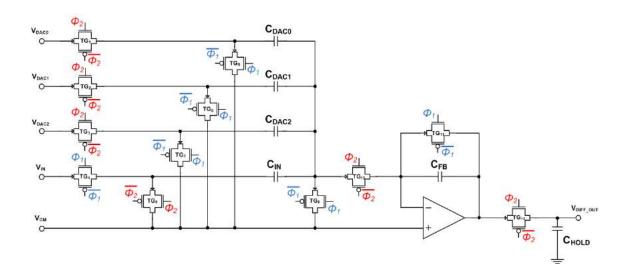

# 2.2 Multiplying Digital to Analog Converter

The Multiplying Digital to Analog Converter (MDAC) is a term for common implementation of S&H, sub-DAC, subtractor and inter-stage amplifier in Switched Capacitor (SC) technique. From top-block point of view, it can be said, that one stage of pipelined ADC can be realized from only two blocks — sub-ADC and MDAC (Figure 12). These blocks are frequently implemented with use of low-resolution flash ADCs. The MDAC resolution divided into two main branches during the time and they will be discussed in next chapter 2.2.1 [2],[3].

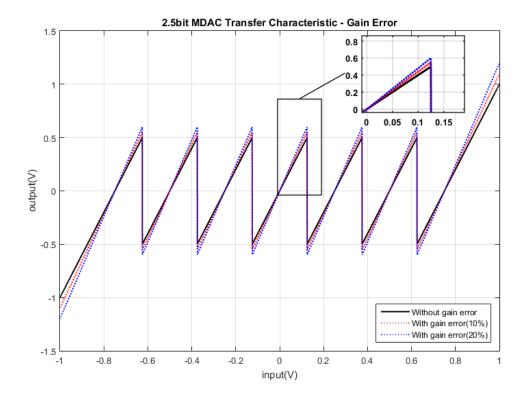

#### 2.2.1 1.5-bit MDAC versus 2.5-bit MDAC

A number of real designs contain an MDAC with 1.5-bit resolution. The justification for that is simple. The 1.5-bit resolution allows wider offset error correction with respect to the 2.5-bit variant. Conversion linearity is better as well. On the other hand, the 2.5-bit MDAC resolution requires only half number of comparators to achieve the same resolution. The disadvantage of 2.5-bit variant is higher demand on comparator offset.

For both architectures is the main specification identical. The accuracy of comparators must be as high as the overall accuracy of ADC conversion.

Figure 12: Block scheme of single pipeline stage

One possible specification improvement implies from the function of pipelined ADC in design process. If we consider the fact, that MSBs (Most Significant Bits) are processed on first stage, we can exploit it for power consumption reduction while maintaining the simultaneous accuracy and resolution specs. The idea is to relax comparator's accuracy requirements in the following stages. The Figure 13 shows typical transfer characteristics for 1.5 and 2.5-bit MDAC resolution [3],[4] and [5].

Figure 13: a) 1.5-bit MDAC and b) 2.5-bit MDAC transfer characteristic

## 2.3 Time correction block

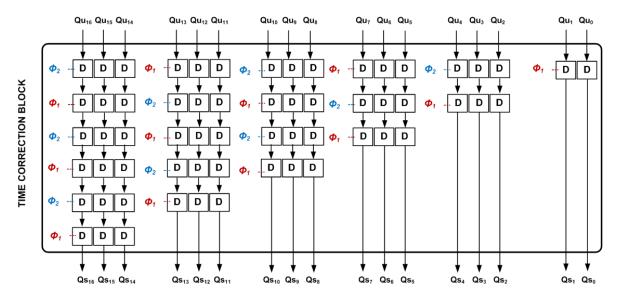

As it implies from function of pipelined ADC, the individual stages work in two phases and they are related to sampling signal. This results in signal delay on the output. It is necessary to synchronize these signals before they pass to digital correction block. It should be mentioned first, that delay of each individual stage is determined as half of period of sampling signal. As the signal passes trough pipeline chain the total delay is a sum of individual delays. The time correction block made from D Flip-Flops creates

Figure 14: Time correction block for 8-bit pipelined ADC

a shift register in Figure 14. During the phase  $\Phi_1$ , the input signal is processed and is shifted at the output when phase  $\Phi_2$  arises. The next stage process the signal in the same manner, but with reversed phases. The last stage (2-bit flash ADC) has a delay of its inner structure and is no need to add additional delay. All the mentioned above results in total delay, that is equal to  $2\Phi$  [2],[3].

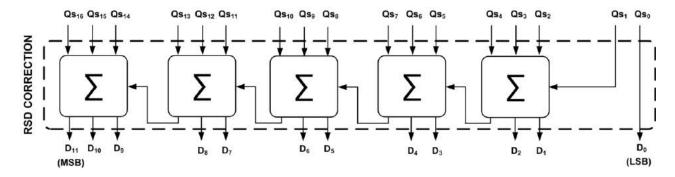

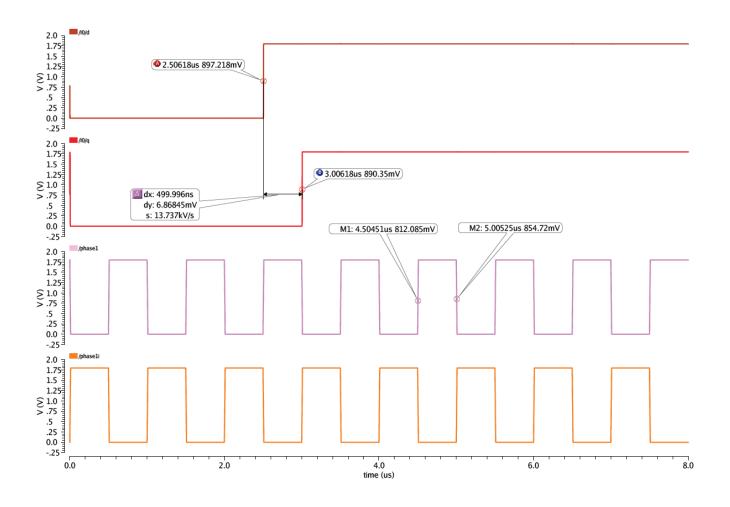

#### 2.4 RSD correction block

Redundant Signed Digit (RSD) is digital correction approach eliminating non-idealities of inner ADC structure. The main error contributor in pipelined ADC is the comparator offset voltage in the sub-ADC block. The ideal transfer characteristic with influence of offset error is shown in Figure 15.

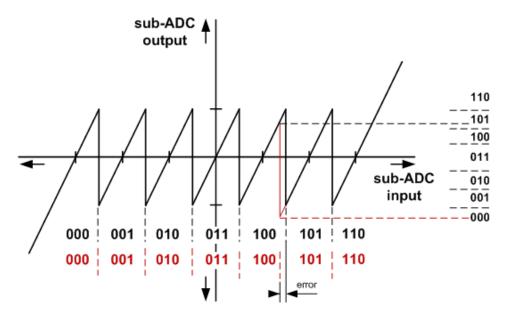

Figure 15: Transfer function of 2.5bit MDAC with comparator offset error.

Figure 16: RSD correction principle

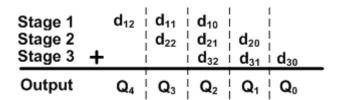

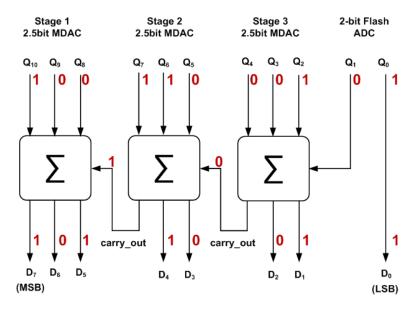

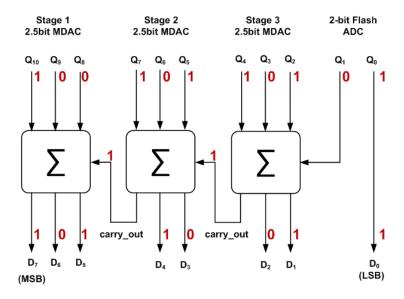

The 2.5 bit MDAC sends actually 2.5 bits into correction block, although half a bit is used as a correction bit in digital logic. The offset causes a shift between decision levels and in the end, it results in code miss-interpretation. To avoid these errors, RSD correction technique is often used in the literature [3],[4]. The partial MDACs outputs are cascaded, shifted by one position and added together. I other words, the most significant bit of first stage  $d_{12}$  is directly shifted to the output and produces digit  $Q_4$ . The second most significant bit  $d_{11}$  from first stage is added to most significant bit of second stage  $d_{22}$  and produces output  $Q_3$ , and so on. The visualization of these processes is shown in Figure 16. RSD correction technique can solve the over-range problem that

comes from comparator's offset. Comparison between function without offset of comparator, and with offset of comparator is shown in Figure 17, respectively in Figure 18. For case of 8-bit pipelined ADC, the total number of signals that are sensed by RSD correction block is 11 ( $Q_0$ - $Q_{10}$ ). The outputs of the correction block correspond to 8-bit digital signal ( $D_0$ - $D_7$ ). Now considering an example (Figure 18) where the comparator in stage 2 and 3 has some offset and produces an irrelevant output [2].

Figure 17: RSD correction function

Figure 18: RSD correction function with comparator offset

The bits have changed in stage 2 (from 110 to 101) and in stage 3 (from 001 to 101). This forces the internal logic (it is made of half and full adders) to change its inner state to correct and hold the same output value.

It can be said, that the most significant bits from each stage are added to next stage (except stage 1). As mention earlier in the text, one conversion bit is used for correction. This functional approach helps with correcting the most severe errors as they will not appear in output digital word.

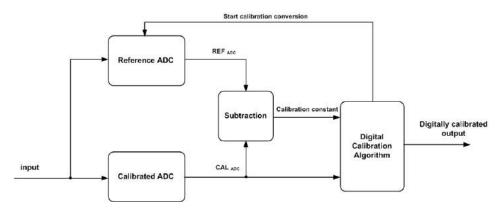

# 2.5 Calibration techniques

A number of calibration techniques can be found in the various resources. They are usually mixed signal techniques that help with improving performance over the frequency range and mainly over resolution. One of these techniques is called foreground calibration. This method uses an extra amount of additional circuitry to improve incorrect parameters during the conversion process. It can be said, that calibration algorithm influences the result of conversion.

The second type of calibration method is known as background calibration. The difference between the foreground and background calibration approach is that the foreground calibration does not force into conversion. Calibration mechanism corrects the output digital word passively. The advantage of foreground calibration is in its lower demand on system complexity, with respect to background calibration.

These techniques will be discussed later in practical part of document in chapter 5.

# 2.6 Influence of non-idealities on conversion process

As an every conversion process is encumbered by various errors, offset, uncertainties (in general non-idealities), the same applies for pipelined ADC. A presence of non-ideality degrades conversion specifications, such a speed, accuracy, resolution etc. The pipelined ADCs are always connected with switched capacitor design architecture.

Three main contributors of error are discussed a graphically displayed, in the chapter below. We will start with error mentioned earlier that can be compensated with using digital correction, as outlined in chapter 2.4 – comparator's offset voltage error.

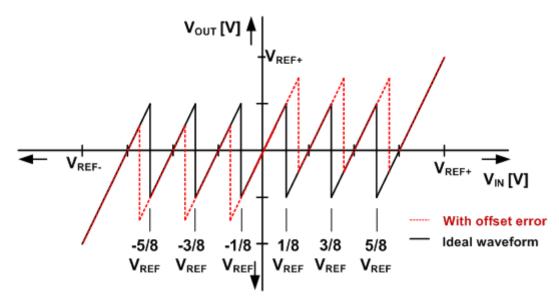

#### 2.6.1 Comparator offset voltage error

The offset voltage is the main error source in sub-ADC. The purpose of a comparator presence is to produce output signal, depending on the input signal. If the input signal is above reference level, the output goes high [3]. The offset voltage behaves as an additional voltage on the top of reference level causing increase or decrease the decision level. It results in possibility, that comparator makes a wrong decision. A number of sources can cause voltage offset, but the transistor mismatch is the main contributor. It is a trade-off for comparator's speed or accuracy.

Figure 19: 2.5 bit MDAC transfer characteristic with offset voltage error

With smaller devices (transistors), the mismatch increases and the total comparator offset error increases as well. On the other hand, with larger devices the matching is improved, but the power consumption increases.

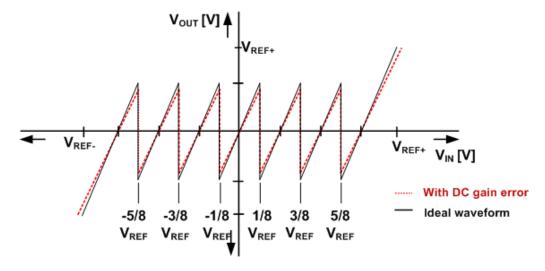

### 2.6.2 Finite DC gain of operational amplifier

An operational amplifier is one of the most critical blocks in pipelined ADC's implementation. Proper understanding and modelling impacts of non-idealities on pipelined ADCs performance are crucial.

Figure 20: Finite DC gain and its influence on transfer function on 2.5 bit MDAC

The differential amplifier is usually made with use of switched capacitor structure as can be found in the paper [3]. From this source implies that the output of the MDAC can be described as

$$V_{RESx} = V_{RESx-1} \left( \frac{C_S + C_F}{C_F} \right) + V_{REF-} \cdot \left( \frac{C_S + C_F + C_P}{C_F} \right) - V_{DAC} \cdot \frac{C_S}{C_F}. \tag{13}$$

The feedback factor beta describes how much of the output voltage of operational amplifier is fed back to Op-Amp input and is given by,

$$\beta = \left(\frac{C_S}{C_S + C_F + C_P}\right). \tag{14}$$

The DC gain requirement can be obtained from (13).

The Op-Amp error gain should be smaller than ¼ LSB of remaining resolution and can be calculated from (14).

$$\frac{1}{A \cdot \beta} < \frac{1}{4} LSB \tag{15}$$

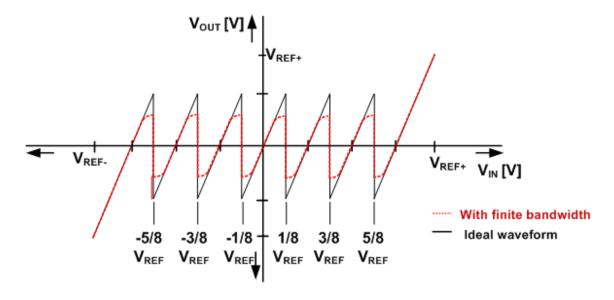

### 2.6.3 Finite bandwidth of operational amplifier

Finite bandwidth of Op-Amp is another important non-ideality to study in designing pipelined ADCs.

The settling behaviour of the Op-Amp in switched capacitor circuits is not entirely linear. The settling error is largest when the input signal voltage is close to  $\pm V_{\text{REF}}$ , where the output voltage changes to full scale.

Figure 21: Finite Op-Amp bandwidth and it influence on transfer function on 2.5 bit MDAC

The consequence of settling error is harmonic distortion at the output. Therefore, the gain bandwidth of Op-Amp should be large enough to avoid harmonic distortion, caused by settling error [3]. The example of how the DC gain affects transfer characteristic is shown in Figure 21. The black line represents an ideal transfer function and the red dotted line shows transfer function with finite gain bandwidth.

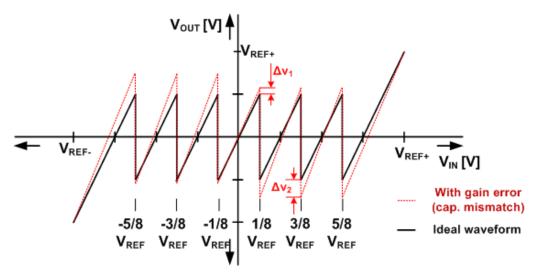

#### 2.6.4 Gain error of operational amplifier – capacitor mismatch

The gain of switched capacitor MDAC is given by a capacitor ratio. From that reason, it is necessary to produce capacitors that match as much as possible. The capacitor value is given by equation (16),

$$C = A \cdot \frac{\varepsilon_{oxid}}{t_{oxid}} = A \cdot C_{oxid} \tag{16}$$

Where A is the area of a capacitor,  $\varepsilon_{\text{oxid}}$  is the dielectric constant of silicon dioxide,  $t_{\text{oxid}}$  is the oxide thickness and  $C_{\text{oxid}}$  is a capacitance per unit area.

From equation above arises fact, that overall capacity is directly proportional to capacitor oxide thickness and its area. The improvement in capacity matching can be done by increasing the area. The integrated circuit capacitor can be determined as

$$C' = C + \Delta C, \qquad (17)$$

where  $\Delta C$  is a mismatch error of capacitor C. Then the ratio of  $C_F$  a  $C_S$  can be written as

$$\frac{C'_s}{C'_F} = \frac{C_s + \Delta C_s}{C_F + \Delta C_F},\tag{18}$$

where  $C_F$  is a feedback capacity and  $C_S$  is a sample capacity in switched capacitors circuit[5].

Figure 22: Gain error (capacity mismatch) and its influence on transfer function

The typical transfer function of 2.5-bit MDAC is shown in Figure 22. The black line represents an ideal transfer function and the red line shows a transfer function with capacitor mismatch.

# PRACTICAL PART

This part of thesis is dedicated to MATLAB model creation. The main sources of error and non-idealities were described and the objective of next parts is to create functional model that can emulate behaviour of the circuit. Also, the non-idealities are incorporated in model. The primary purpose of model creation is to simulate and determine the weak parts of design with aim to achieve best performance in given technology. In other words, the model will serve as a reference for oncoming work where real technology TSMC 0.18µm is used.

### 3 12-BIT PIPELINE ADC MODEL

The modern ADC architectures were introduced in theoretical part 1.2. The practical part aims to develop a simulation model of 12-bit pipelined ADC in Matlab environment. The detailed model structure is present in following parts concerning chosen topology and its advantages. The basic structure is taken from literature [2],[3],[4],[5],[12] and [14].

#### 3.1 Model structure

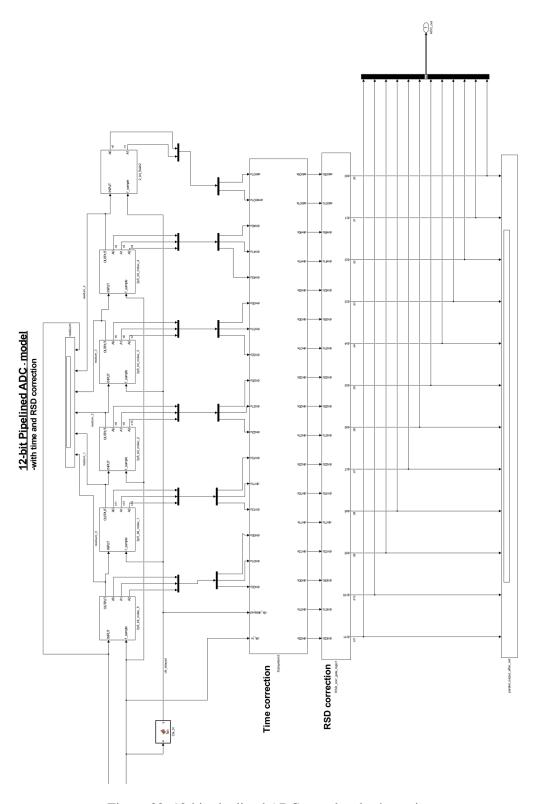

Block model of 12-bit pipelined ADC model is shown in Figure 23. It consists of six stages. The first five stages are identical. Each individual stage is made of 2.5-bit sub-ADC, 2.5-bit MDAC, sample and hold circuit subtraction circuit and gain amplifier. The last stage is a 2-bit flash ADC. Corresponding to the introduced architecture in part 2.2.1 the residual signals from each block go to time correctional block where they are synchronized. Then the already synchronized signals pass to digital correction block (RSD correction block) where conversion errors are processed and corrected. Overall structure will be designed in switched capacitor technology, so the model includes block that emulates behaviour of SC technique.

Figure 23: 12-bit pipelined ADC model with 2.5-bit MDAC, time correction and digital RSD correction block – block schematic

## 3.1.1 The 2.5-bit sub-ADC & sub-DAC model

Figure 24: Sub-ADC and sub-DAC schematic for 2.5-bit MDAC – structural level [2].

The complete schematic of 2.5-bit MDAC is shown in Figure 24. It is created with use of six comparators, three 1.5-bit multiplexers, and NAND gates. The input signal  $V_{\text{RESx-1}}$  is compared with reference voltage using comparators in the first phase. Reference voltages  $V_{\text{REF+}} = 1\text{V}$  and  $V_{\text{REF-}} = -1\text{V}$  are set according to maximal amplitude of input signal that is 2V peak-to-peak. The outputs of the comparators are sensed by 1.5-bit multiplexers and are transformed to analog signal reversely. Every multiplexer creates one-third of total amplitude that is subtracted from input  $V_{\text{RESx-1}}$  in next phase. The truth table of sub-DAC is shown in Table 1.

Table 1: Sub-DAC truth table – summation of three multiplexers [2]

| Sub-DAC output |                   |            | After summation       |

|----------------|-------------------|------------|-----------------------|

| $V_{DAC2}$     | V <sub>DAC1</sub> | $V_{DAC0}$ | $V_{DACtotal}$        |

| $V_{REF+}$     | $V_{REF+}$        | $V_{REF+}$ | $V_{ m REF+}$         |

| $V_{REF+}$     | $V_{REF+}$        | $V_{CM}$   | $2/3 V_{REF+}$        |

| $V_{REF+}$     | $V_{CM}$          | $V_{CM}$   | 1/3 V <sub>REF+</sub> |

| $V_{CM}$       | $V_{CM}$          | $V_{CM}$   | $V_{CM}$              |

| $V_{CM}$       | $V_{CM}$          | $V_{REF-}$ | 1/3 V <sub>REF-</sub> |

| $V_{CM}$       | $V_{REF-}$        | $V_{REF-}$ | $2/3 V_{REF}$         |

| $V_{REF}$      | $V_{REF-}$        | $V_{REF-}$ | $V_{ m REF-}$         |

The output of the comparator goes to encoding logic that uses NAND gates and converses the signal into desired code. These outputs then pass to time correction block, where they are synchronized. A truth table and function description of relation between sub-ADC, output code, and sub-DAC is summarized in Table 2.

Table 2: Sub-ADC and sub-DAC truth table [2]

| Input signal                             | Output code    |                |                | Sub-DAC output |                    |                   |

|------------------------------------------|----------------|----------------|----------------|----------------|--------------------|-------------------|

| $ m V_{RESx	ext{-}1}$                    | $\mathbf{A_2}$ | $\mathbf{A_1}$ | $\mathbf{A_0}$ | $V_{DAC2}$     | V <sub>DAC1</sub>  | V <sub>DAC0</sub> |

| $V_{RESx-1} > 5/8V_{REF}$                | 1              | 1              | 0              | $V_{REF+}$     | $V_{REF+}$         | $V_{REF+}$        |

| $5/8V_{REF} > V_{RESx-1} > 3/8V_{REF}$   | 1              | 0              | 1              | $V_{REF+}$     | $V_{REF+}$         | $V_{CM}$          |

| $3/8V_{REF} > V_{RESx-1} > 1/8V_{REF}$   | 1              | 0              | 0              | $V_{REF+}$     | $V_{CM}$           | $V_{CM}$          |

| $1/8V_{REF} > V_{RESx-1} > -1/8V_{REF}$  | 0              | 1              | 1              | $V_{CM}$       | $V_{CM}$           | $V_{CM}$          |

| $-1/8V_{REF} > V_{RESx-1} > -3/8V_{REF}$ | 0              | 1              | 0              | $V_{CM}$       | $V_{CM}$           | $V_{REF-}$        |

| $-3/8V_{REF} > V_{RESx-1}-5/8V_{REF}$    | 0              | 0              | 1              | $V_{CM}$       | V <sub>REF</sub> - | $V_{REF-}$        |

| $V_{RESx-1} > 5/8V_R >_{EF}$             | 0              | 0              | 0              | $V_{ m REF}$   | $V_{ m REF}$       | V <sub>REF-</sub> |

As it was said earlier, the converted signal has to be subtracted from input signal, to produce residual signal. Furthermore, it needs to be amplified to full-scale range. This is achieved with differential amplifier [2]. The complete model of 2.5-bit MDAC in Matlab is shown in Figure 25.

Figure 25: Real schematic of 2.5-bit MDAC in Matlab environment

The Figure 25 shows internal circuitry of 2.5-bit MDAC that emulates real pipelined ADC behaviour in SC technique. The particular blocks are modelled by behavioural description. The reasons for that are practical. The behavioural model facilitates the same functionality as gate level model. This approach can be exploited for modelling wide variety of circuits in Matlab environment if the functionality of circuit isknown. The circuit function can be expressed as a truth table or as mathematical expressions. It was decided to model the particular blocks behaviourally because the necessary data are presented in literature [2],[3],[4],[12] and [14] on which the work is based. The reference voltage levels are produced via pre-determined constants instead of resistor divider as is described in Figure 24. In this part, it is not necessary to include errors caused by resistor divider mismatch. As it corresponds to function mentioned earlier, the input voltage passes to comparators. There is it decided, whether the voltage is above the reference level or not. This produces output digital signal that address the multiplexers. The 1.5-bit multiplexers function is based on the data from Table 2.

The next necessary part of model is a summation block. As was mentioned above, the subtraction in SC technique is made by differential amplifier. This functionality represents behavioural description of the MDAC in model. Table 3 fully explains the relation between input signal  $V_{\rm RESx-1}$  and output signal  $V_{\rm RESx}$ .

Table 3: Table of multiplexers output summation [2]

| Condition                                     | $V_{RESx}[V]$                                    |

|-----------------------------------------------|--------------------------------------------------|

| If $V_{RESx-1} > 5/8 V_{REF+}$                | $4V_{RESx-1} - 3V_{REF+}$                        |

| If $5/8 V_{REF+} > V_{RESx-1} > 3/8 V_{REF+}$ | $4V_{RESx-1} - 2V_{REF+}$                        |

| If $3/8 V_{REF+} > V_{RESx-1} > 1/8 V_{REF+}$ | $4V_{RESx\text{-}1} - \textcolor{red}{V_{REF+}}$ |

| If $1/8 V_{REF+} > V_{RESx-1} > 1/8 V_{REF-}$ | $4V_{RESx-1}$                                    |

| If $1/8 V_{REF-} > V_{RESx-1} > 3/8 V_{REF-}$ | $4V_{RESx-1} + V_{REF+}$                         |

| If $3/8 V_{REF} > V_{RESx-1} > 5/8 V_{REF}$   | $4V_{RESx-1} + 2V_{REF+}$                        |

| If $V_{RESx-1} < 5/8 V_{REF}$                 | $4V_{RESx-1} + 3V_{REF+}$                        |

The error sources such as Op-Amp gain error, comparator voltage offset, and Op-Amp finite DC gain are parts of real design. These non-idealities are also implemented in the model.

#### **Modelling comparator offset voltage:**

The additional voltage can be added to comparator reference via constant *comp\_off*. This facilitates the option to model comparator's offset voltage and observe its influence on conversion process and transfer characteristic of MDAC.

#### Modelling Op-Amp gain error:

The capacitor mismatch or Op-Amp gain error can be modelled with error amplifier when gain  $\neq 1$  (parameter  $gain_f$ ). The error amplifier is shown in Figure 25.

#### Modelling Op-Amp DC gain error:

The finite DC gain of the operational amplifier is designated as A0 and was mentioned in theoretical part. For this purpose, the model consists of another amplifier with gain = (1/A0). The error portion formed by amplifier is then subtracted from output residual signal, which produces additional error that corresponds to finite gain of operation amplifier.

In previous chapters, the block, structural and behavioural structure was described. The simulation results and transfer characteristic, with discussion about functionality, are described later.

#### **3.1.2 2-bit Flash ADC**

The 2-bit Flash ADC is the last element in pipeline conversion chain. It facilitates full two-bit conversion as there is no need to produce residuum. It consists of three comparators and encoding logic, which converts the input signal to desired output value. The conceptual schematic is shown in Figure 26 and real Matlab model can be seen in Figure 27.

Figure 26: 2-bit Flash ADC – conceptual schematic [2]

Figure 27: 2-bit Flash ADC – Matlab schematic

The input signal is sampled and fed to comparators inputs. The comparator makes a decision if the sample is above reference level or not and set its output accordingly to logical 1 or 0. The encoder logic in Matlab model uses these comparators outputs to produce the output code. This logic table is described in Table 4.

Table 4: Encoder logic truth table

| Encoder input |             |             | <b>Encoder output</b> |                |  |

|---------------|-------------|-------------|-----------------------|----------------|--|

| $V_{COMP2}$   | $V_{COMP1}$ | $V_{COMP0}$ | $\mathbf{A_1}$        | $\mathbf{A_0}$ |  |

| 0             | 0           | 0           | 0                     | 0              |  |

| 0             | 0           | 1           | 1                     | 0              |  |

| 0             | 1           | 1           | 0                     | 1              |  |

| 1             | 1           | 1           | 1                     | 1              |  |

The difference between 2.5-bit sub-ADC and 2-bit flash ADC is that at the output of flash converter is full two-bit digital word – including combination 11.

### 3.1.3 Time correction block

This chapter is based on chapter 2.3 where time correction principle was described for 8-bit pipelined ADC. The situation is the same for 12-bit ADC. The only difference is in a number of stages (increased from 4 to 6) that has to be synchronized. The conceptual block schematic is shown in Figure 28 and the real model in Matlab can be seen in Figure 29.

Figure 28: Conceptual block diagram of time correction for 12-bit pipelined ADC

Figure 29: Time delay block for 12-bit pipelined ADC – Matlab schematic

As it was mentioned in part dedicated to time delay block explanation, the principle stays the same for 12-bit variant. Signals designated as  $Qu_0 - Qu_{16}$ . (Figure 28) represent the unsynchronized digital outputs of each pipeline stage. The D Flip-Flops shift its inputs to the outputs accordingly to clock phase as is described in the picture. The clock phase  $\Phi_2$  is shifted by half of a sample period with respect to  $\Phi_1$ . The synchronized outputs are marked as  $Qs_0 - Qs_{16}$ . This structure guarantees, that the captured samples are synchronized in time and signals can forward to the last stage – to RSD correction block.

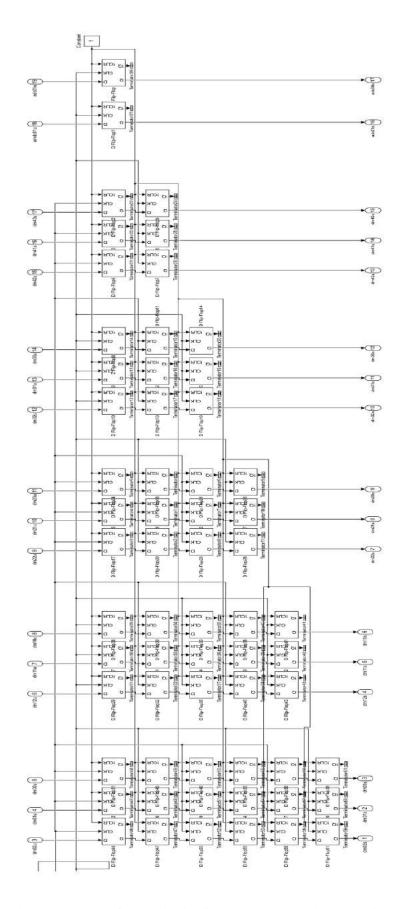

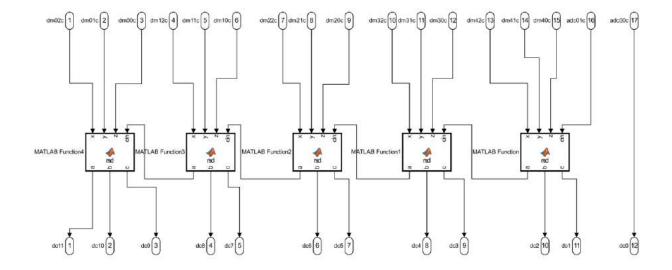

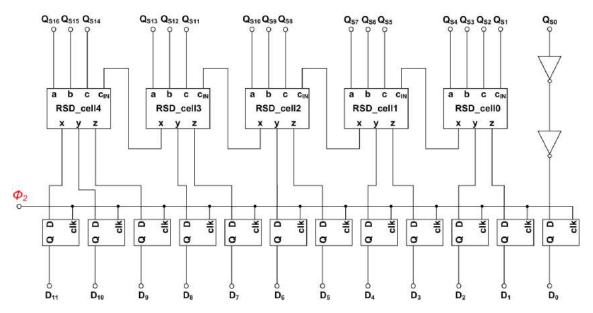

#### 3.1.4 RSD correction block

Digital correction, described in part 2.4, is an important element in high-resolution pipelined ADCs. The 2.5-bit MDACs produce redundant codes and they are used for correction process. It widely improves the converter performance. Conceptual block schematic is shown in Figure 30 and Matlab implementation is described in Figure 31.

Figure 30: RSD correction block for 12-bit pipelined ADC – conceptual schematic

Figure 31: RSD correction block for 12-bit pipelined ADC – real Matlab implementation

When the signal passes through RSD correction block, the conversion is accomplished and the 12-bit digital word is prepared at the output. The whole Matlab model schematic is showed in Figure 32.

Figure 32: 12-bit pipelined ADC - top level schematic

Next part is dedicated to show practical simulation results and confirm theoretical expectations described in this document earlier.

### 3.1.5 Model functionality

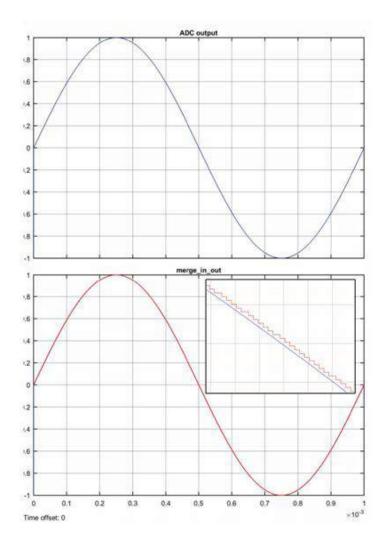

Figure 33 shows the output of the ADC after conversion for ideal case. That means with presence of no non-idealities (offset, gain error etc.). The simulation parameters are as follows.

Figure 33 : Output of 12-bit pipelined ADC. Top – input signal, bottom – ADC output

Sample frequency  $F_{\text{SAMPLE}}=10\text{MHz}$ , input signal frequency  $F_{\text{SIGNAL}}=1\text{kHz}$ , input signal amplitude  $A_{\text{SIGNAL}}=2\text{V}$ , common mode signal  $V_{\text{CM}}=0\text{V}$ , reference voltages  $V_{\text{REF+}}=1\text{V}$ ,  $V_{\text{REF+}}=-1\text{V}$ .

### The MDAC output residue is shown in Figure 34.

Figure 34: 12-bit pipeline ADC, first stage residue. Top – input sampled signal, bottom – residual signal at the output of 1<sup>st</sup> stage.

The output residue corresponds to theoretical expectations from articles [3],[4] and [5].

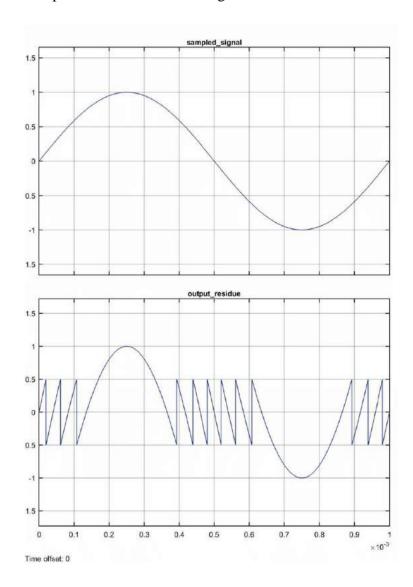

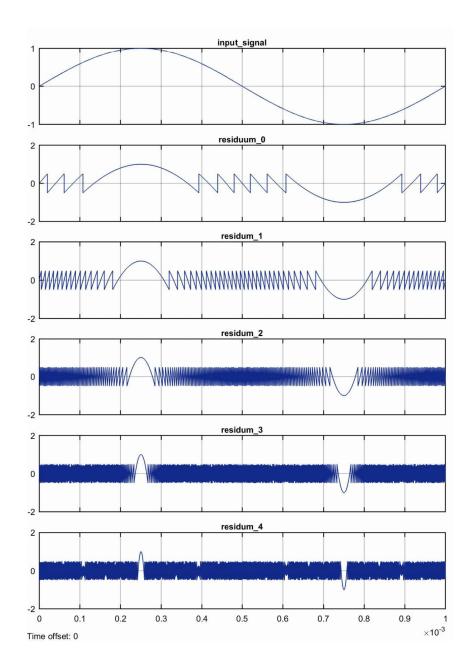

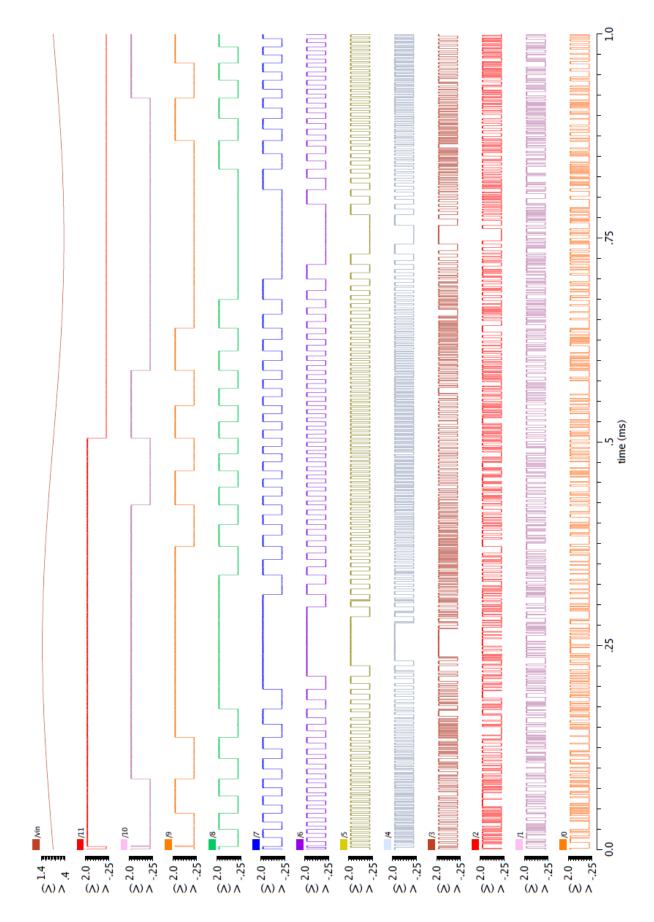

The rest of residual signals (signals between all stages) are shown in Figure 35.

Figure 35: Residual signals at the end of each stage. Top - input signal, the others, residual signals for particular stages

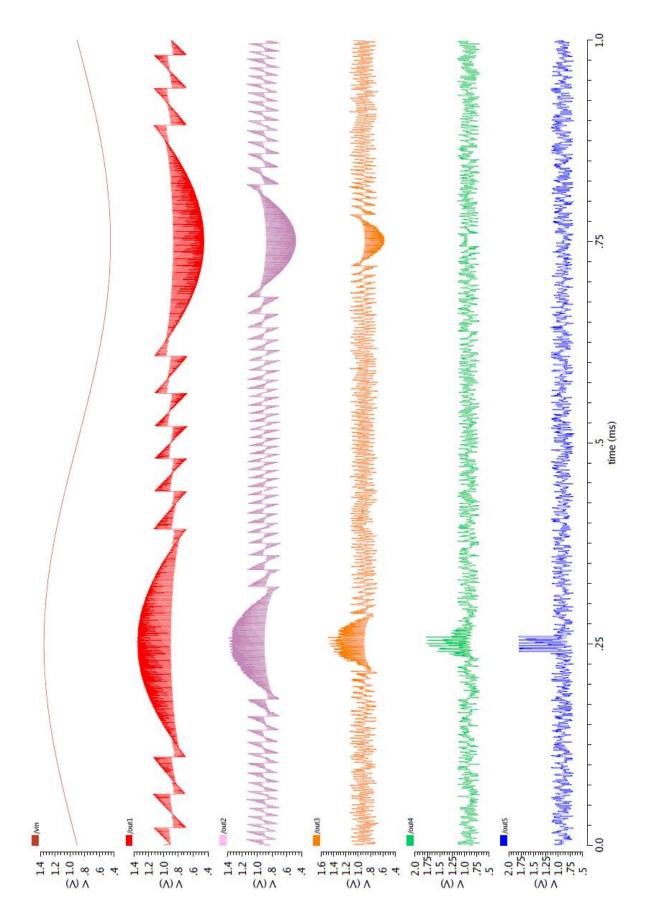

Figure 36: a) Outputs of 2.5-bit sub-ADC, b) outputs of 2-bit flash ADC

The important outputs of sub-ADC and 2-bit flash ADC are showed in Figure 36.

### 3.1.6 Ideal transfer characteristic – simulation

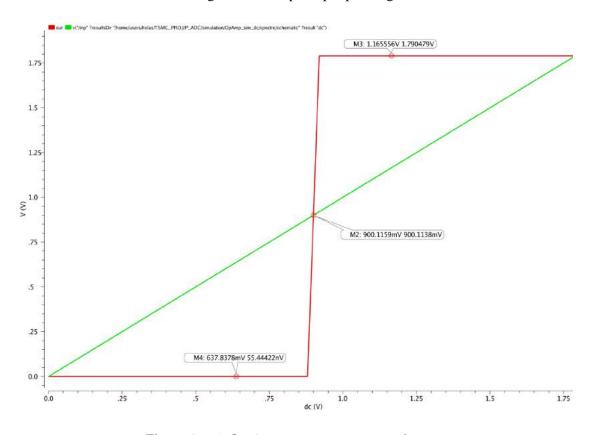

The ideal transfer function of 2.5-bit MDAC is plotted in Figure 37.

Figure 37: Ideal transfer characteristic of 2.5-bit MDAC – simulation result

Picture above describes and ideal transfer characteristic of 2.5-bit MDAC model and confirms model functionality. Theoretical (Figure 13) and simulated transfer functions (Figure 37) are identical.

The ideal waveforms such as INL, DNL, power spectral density and ADC output

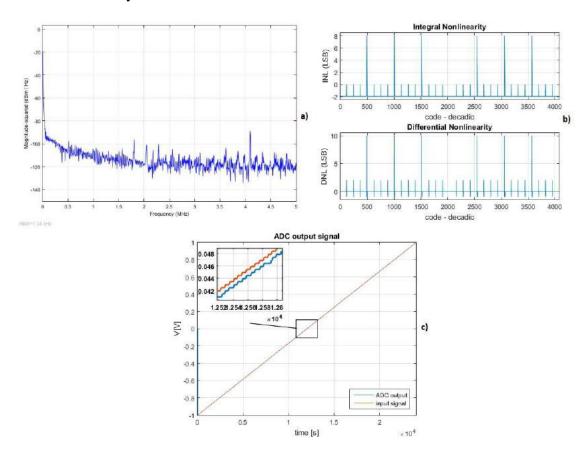

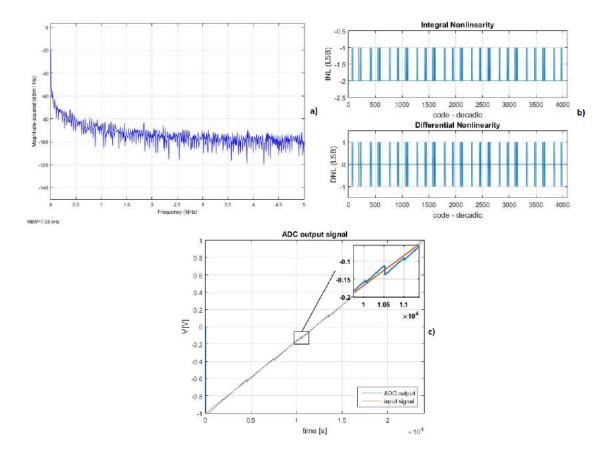

Figure 38: a) Ideal Power spectral density of the ADC output, b) ideal INL and DNL, c) output staircase function – simulation results

are shown in Figure 38. The output ADC signal has typical staircase shape with the step width of 1 LSB over whole operation range. This ensures that the INL and DNL equal to zero. The mean noise floor level reaches value 130dB in power spectral density diagram. Within these ideal conditions (no errors were involved) the ENOB is equal to 12 bit. Unfortunately, this resolution is very difficult to reach, because the errors are present in every real conversion process. To get closer to ideal specifications it is necessary to understand, which error parameter has got the highest influence on conversion process. The simulations with error contributors are presented in next chapter.

### 3.2 Conversion non-idealities – simulation

In following parts, the particular errors in simulation are introduced and discussed. The simulations aim to explain the influence of particular error, so the other error contributors are neglected. For example, if the comparator offset voltage error is under scope, the gain error and the finite DC gain of Op-Amp are suppressed and not taken into account.

### 3.2.1 Comparator offset voltage

This chapter is dedicated to discovering the real influence of mentioned errors on transfer function, and consequently on overall conversion process. The comparator

Figure 39: Influence of comparator voltage offset on transfer function – simulation result

voltage offset error is shown in Figure 39. Offset voltage of the comparator results in reference level shift that causes output code misinterpretation. The transfer characteristic appears to be shifted from ideal reference value to the right for positive reference levels and to the left for negative reference levels. The vertical shift is present in the picture as well. As the offset voltage increases, the shift is more significant. The simulation results for comparator offset voltage  $V_{\text{COMPerr}} = 150 \text{mV}$  are shown in Figure 40.

As the offset voltage increases, the staircase waveform starts to have some missing codes. The DNL and INL graph shows the amount of these presented errors. The power spectral density shows a noise floor level shift to approximately 110dB. However, it has to be mentioned, that 150mV offset voltage is really high value even in real process implementation. The offset voltage does not influence the accuracy specification until the mentioned value 150mV. The explanation for this comes from RSD block function. The RSD correction block can correct the gain over-shots caused by comparator. Once the offset error is higher than the limit, the RSD correction cannot fully handle out produced error and the offset occurs at the output. This value was determined by simulation exactly to 150mV.

Figure 40: a) Power spectral density for ADC with 150mV offset error voltage,

b) corresponding INL and DNL and c) corresponding ADC transfer function.

As it implied in the paragraph above, the comparator offset voltage has got significant influence on conversion accuracy. On the other hand, it can be successfully compensated with RSD correction. In the end, it results in comparator offset specs relaxation because there is no need to design comparator with, for example, 1mV offset voltage specification.

### 3.2.2 DC gain error of operational amplifier

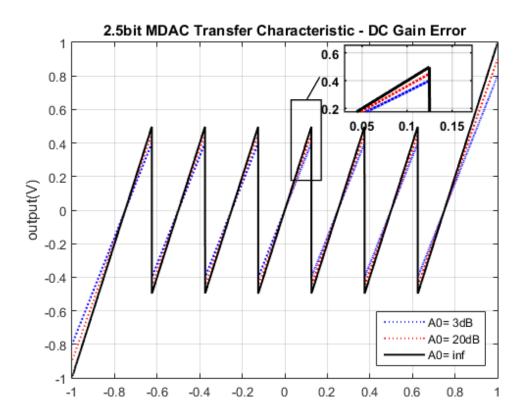

The finite DC gain error is plotted in Figure 41. Op-Amp's non-ideal DC gain causes a decrease in output voltage amplitude. The feedback factor  $\beta$  determines the amount of output voltage, that is fed back to input of the Op-Amp.

Figure 41: Influence DC gain error on transfer function

If we consider pipeline structure, the error in first block is projected to the next one, and causes another error increase. The Op-Amp DC gain has to be as high as the technology allows for high-resolution designs. Figure 42 shows the same characterization utilities as in previous two parts, but for finite DC gain of Op-Amp A0 = 50dB. This DC gain introduces error in MDAC and has influence on integral and

differential nonlinearity of converter. The 50dB finite DC gain shows its influence on conversion accuracy.

Figure 42: a) Power spectral density of ADC with 50dB DC gain ,b)corresponding INL and DNL, c) corresponding ADC output

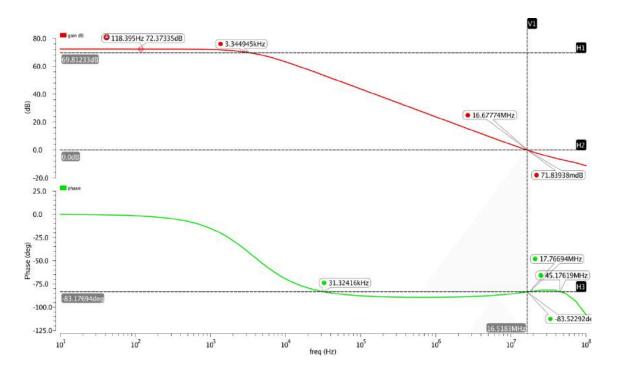

The effect of DC gain error in DNL an INL characteristic disappears when the DC gain of Op-Amp increases to 60dB. This is the second parameter that was deducted from simulation results. It results in following conclusion. To obtain conversion without influence of finite DC gain, the DC gain should be larger than 60dB in real design application.

### 3.2.3 Gain error of operational amplifier - capacitor mismatch

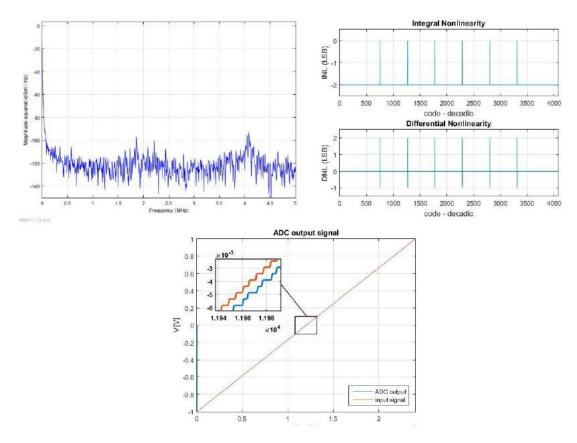

If the capacitors are not sufficiently matched, the transfer characteristic gets stretched vertically. It means that output signal has a higher amplitude than the input

Figure 43: Influence of capacitor mismatch on transfer function

signal. This ratio uncertainty is responsible for the main error source in pipeline ADC architecture. Figure 44 shows a shifted power spectrum density for 1% gain mismatch, which is represented in SC circuits by capacitor mismatch ratio. The INL and DNL had increased and their occurrence over full-scale range became more frequent. The transfer characteristic became more rippled as well (Figure 44c).

Figure 44: a) Power spectrum density for ADC with 1% capacitor mismatch error, b) corresponding INL and DNL, c) an ADC "rippled" output.

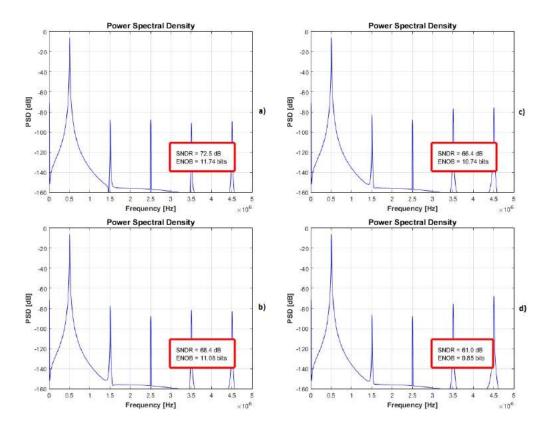

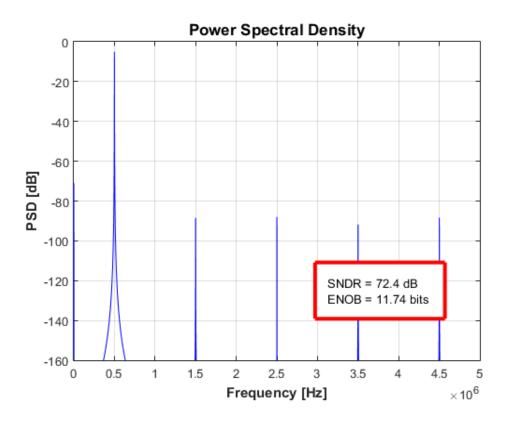

Figure 45 approaches the capacitor mismatch influence on SNDR and ENOB parameters. The FFT – Fast Fourier Transform was performed for the output of the ADC with following simulation parameters. The sample frequency  $F_{\text{SAMPLE}}=10\text{MHz}$ , the input signal frequency  $F_{\text{SIGNAL}}=500$  kHz, the input signal amplitude  $A_{\text{SIGNAL}}=2\text{V}$ , the common mode signal  $V_{\text{CM}}=0\text{V}$ , reference voltages  $V_{\text{REF}}=1\text{V}$ ,  $V_{\text{REF}}=-1\text{V}$ . The number of FFT points  $N_{\text{FFT}}=2048$ . The picture shows how the ENOB and SNDR parameters decrease with increasing capacitor mismatch.

Figure 45: FFT for Op-Amp gain error a) 0.1%, b) 0.25%, c) 0.5% and d) 1%

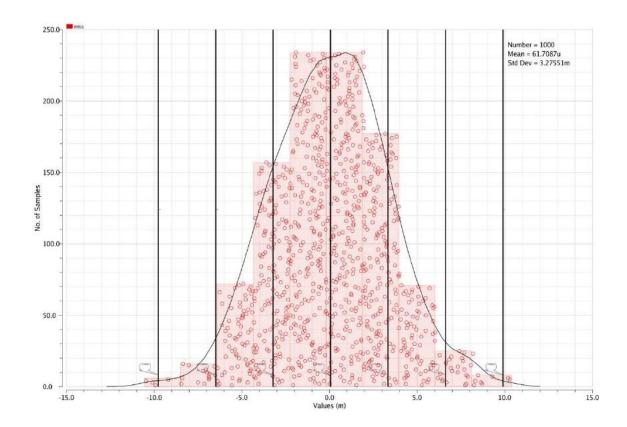

### 3.2.4 Realistic parameters definition for transistor level design

As it was introduced, explained and proved in chapter 3.2, the non-idealities in conversion process can negatively influence all converter specifications. The minimal error parameter specifications were estimated to avoid (or at least eliminate) a presence of those errors in real design.

- the comparator offset voltage has to be lower than **150mV**,

- the Op-Amp DC gain (or the bandwidth) has to be larger than **60dB**,

- the Op-Amp gain error has to be lower than **0.1%**.

The estimated parameters are supported by numerous simulation results during a model development. The absolute maximal ratings of ADC conversion including conversion non-idealities are determined using ENOB and SNDR parameters and can be seen in Figure 46.

The following design work aimed to achieve this specification in TSMC 0.18μm technology.

Figure 46: Maximal achievable ENOB and SNDR in model simulation (A0=60db,  $V_{\rm OFFSET}=140$ mV,  $A_{\rm MISMATCH}=0.1\%$ )

# 4 12-BIT PIPELINE ADC DESIGN

Following chapter deals with description of fundamental blocks on transistor level that are further used in the design process. Moreover, chapter covers their design and results of particular simulations in TSMC 0.18µm technology with use of these main technological parameters:

Table 5: Technological parameters for TSMC 0.18µm

| Cell name | Parameter description | Parameter       | Corner(SS) | Corner(TT) | Corner(FF) | Units       |

|-----------|-----------------------|-----------------|------------|------------|------------|-------------|

| nmos2v    | Threshold voltage     | $V_{THN}$       | 0.597      | 0.557      | 0.483      | V           |

|           | Transconductance par. | KP <sub>N</sub> | 168        | 185        | 225        | $\mu A/V^2$ |

| pmos2v    | Threshold voltage     | $V_{THP}$       | - 0.583    | - 0.561    | - 0.471    | V           |

|           | Transconductance par. | KP <sub>P</sub> | 37         | 43         | 65         | $\mu A/V^2$ |