## **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

## FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

#### DEPARTMENT OF RADIO ELECTRONICS

ÚSTAV RADIOELEKTRONIKY

# AN EMC ROBUST PRECISE VOLTAGE REFERENCE FOR AUTOMOTIVE APPLICATIONS

EMC ROBUSTNÍ PŘESNÁ NAPĚŤOVÁ REFERENCE PRO AUTOMOBILOVÉ APLIKACE

#### **DOCTORAL THESIS**

DIZERTAČNÍ PRÁCE

AUTHOR Ing. David Krolák

**AUTOR PRÁCE**

SUPERVISOR doc. Dr. Ing. Pavel Horský

ŠKOLITEL

**BRNO 2023**

#### **Abstract**

A crucial component of modern integrated circuits is the voltage reference that acts like the heart for analog blocks providing stable voltage. This doctoral thesis explores advanced methods to reduce electromagnetic interference (EMI) susceptibility of low-power voltage references for an automotive environment with a wide temperature range. The EMI susceptibility is an unwanted phenomenon that can cause electronic system malfunctions. Electromagnetic disturbances can easily couple to the circuit via a cable harness and a printed circuit board. This thesis provides a literature overview, research suggestions, and results that focus on hidden effects in the voltage reference core, such as the impact of parasitic capacitance from bipolar transistors' collectors to the substrate and the effects of a used operational amplifier. Recommendations for improving voltage reference EMI robustness are presented and implemented. To prove the validity of the suggested improvements, test chips with proposed voltage references using various technologies were fabricated and measured.

### **Keywords**

Bandgap voltage reference, Brokaw bandgap voltage reference, electromagnetic compatibility, electromagnetic interference, electromagnetic susceptibility, element-by-element extraction, passive network synthesis, transmission line, voltage reference.

#### **Abstrakt**

Klíčovou součástí moderních integrovaných obvodů je napěťová reference, která funguje jako srdce analogových bloků poskytující stabilní napětí. Tato disertační práce zkoumá pokročilé metody pro snížení citlivosti nízko příkonových referencí na elektromagnetické interference (EMI) pro automobilová prostředí s širokým teplotním rozsahem. Citlivost na EMI je nežádoucí jev, který může způsobit poruchy elektronického systému. Elektromagnetické rušení se může snadno vázat do obvodu prostřednictvím kabelového svazku a desky s plošnými spoji. Práce poskytuje přehled literatury, návrhy výzkumu a výsledky, které se zaměřují na skryté efekty v napěťovém referenčním jádru, jako je vliv parazitní kapacity z kolektorů bipolárních tranzistorů do substrátu integrovaného obvodu a efekty použitého operačního zesilovače. Jsou uvedena a implementována doporučení pro zlepšení EMI odolnosti napěťové reference. Aby se prokázala platnost navrhovaných vylepšení, byly vyrobeny a změřeny testovací čipy s navrženými napěťovými referencemi v různých technologiích.

#### Klíčová slova

Brokawova napěťová reference typu bandgap, elektromagnetická citlivost, elektromagnetická interference, elektromagnetická kompatibilita, extrakce prvek-po-prvku, napěťová reference typu bandgap, napěťová reference, přenosové vedení, syntéza pasivního obvodu.

## **Bibliographic Citation:**

KROLÁK, David. *An EMC Robust Precise Voltage Reference for Automotive Applications*. Brno, 2023. Doctoral Thesis. Brno University of Technology, Faculty of Electrical Engineering and Communication, Department of Radio Electronics. 152 p. Supervisor doc. Dr. Ing. Pavel Horský.

#### **Declaration**

I declare that I have written this doctoral thesis on the theme of "An EMC Robust Voltage Reference for Automotive Applications" independently, under the guidance of the supervisor, and using the technical literature and other sources of information which are all cited in the text and detailed in the list of literature at the end of this text. As the author of this text on the doctoral thesis, I furthermore declare that, as regards the creation of the text on the doctoral thesis, I have not infringed any copyright. In particular, I have not unlawfully encroached on anyone's personal and/or ownership rights and I am fully aware of the consequences in the case of breaking Regulation § 11 and the following of the Copyright Act No 121/2000 Sb., and of the rights related to the intellectual property right and changes in some Acts (Intellectual Property Act) and formulated in later regulations, inclusive of the possible consequences resulting from the provisions of Criminal Act No 40/2009 Sb., Section 2, Head VI, Part 4.

| In Brno |                    |

|---------|--------------------|

|         | Author's signature |

## Acknowledgment

I would like to thank the onsemi company for the provided opportunity. I would like to thank my supervisor doc. Dr. Ing. Pavel Horský for all the helpful advice, support, and availability throughout the whole time. I would like to also thank Ing. Jan Plojhar and Ing. Martin Dušek, Ph.D. for their technical help and consultations. In addition, I thank my family and friends for their support during my doctoral study.

## **Contents**

| Π | $\Gamma V$ | ROD    | UCTION                                                              | 22 |

|---|------------|--------|---------------------------------------------------------------------|----|

| 1 |            | STAT   | TE OF THE ART                                                       | 23 |

|   | 1          | .1.    | Introduction to the Temperature Compensated Voltage Reference       | 23 |

|   | 1          | .2.    | Brokaw Bandgap Voltage Reference                                    | 24 |

|   | 1          | .3.    | Methods Used in Voltage References for EMI Susceptibility Reduction | 27 |

| 2 |            | AIMS   | S OF DISSERTATION                                                   | 35 |

| 3 |            | EMI S  | SUSCEPTIBILITY MEASURING CONCEPT AT THE IC LEVEL                    | 36 |

|   | 3          | .1.    | Direct Power Injection Measurement Method                           | 36 |

|   | 3          | .2.    | Impact of the DPI Measurement Setup                                 | 39 |

|   |            | 3.2.1. | Synthesis of Passive Circuit Network Model                          | 39 |

|   |            | 3.2.2. | Accuracy Check of the Passive Circuit Network Model Synthesis       | 44 |

|   |            | 3.2.3. | Bias-Tee High-Frequency Circuit Model                               | 46 |

| 4 |            | PROI   | POSED VOLTAGE REFERENCES                                            | 51 |

|   | 4          | .1.    | Existing EMC Improved Brokaw Voltage Reference                      | 51 |

|   | 4          | .2.    | EMI Susceptibility Analysis of the Voltage Reference                | 55 |

|   |            | 4.2.1. | EMI Susceptibility of the Voltage Reference Core                    | 55 |

|   |            | 4.2.2. | EMI Susceptibility of the OPA                                       | 61 |

|   |            | 4.2.3. | EMI Susceptibility of the Overall Voltage Reference                 | 68 |

|   |            | 4.2.4. | EMI Susceptibility Measurement Results                              | 70 |

|   |            | 4.2.5. | New EMI DPI Simulation Method                                       | 72 |

|   | 4          | .3.    | Possibilities of the Power Supply EMI Susceptibility Reduction      | 76 |

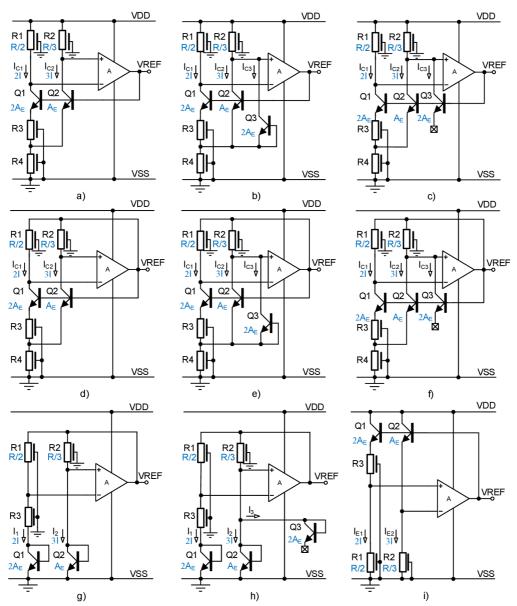

|   | 4          | .4.    | Study of Different Integrated Basic Bandgap Cores                   | 78 |

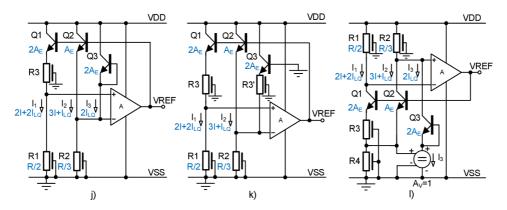

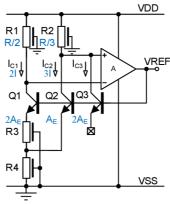

|   |            | 4.4.1. | Integrated Basic Bandgap Core Topologies                            | 79 |

|   |            | 4.4.2. | Collector Leakage Current Compensation                              | 80 |

|   |            | 4.4.3  | Investigated Bandgap Cores                                          | 82 |

|   |            | 4.4.4. | OPA Model                                                           | 84 |

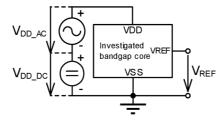

|   |            | 4.4.5  | Simulation Setup                                                    | 84 |

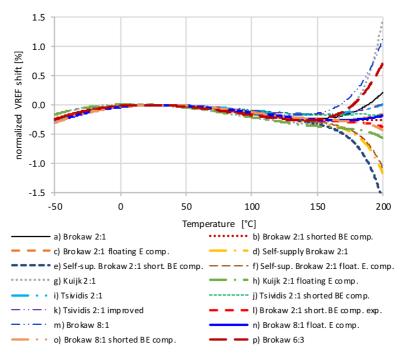

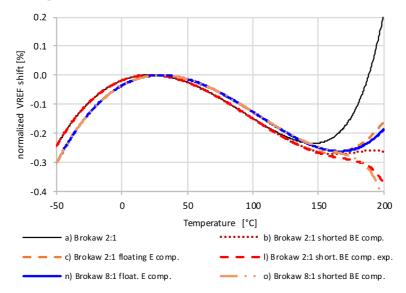

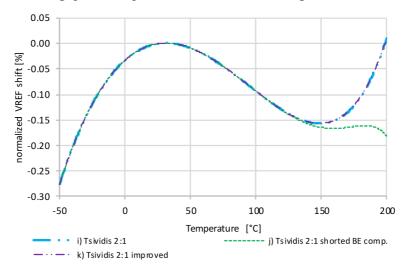

|   |            | 4.4.6  | Temperature Drifts                                                  | 85 |

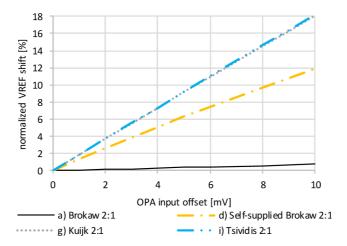

|   |            | 4.4.7  | Sensitivity to the OPA Input Offset                                 | 88 |

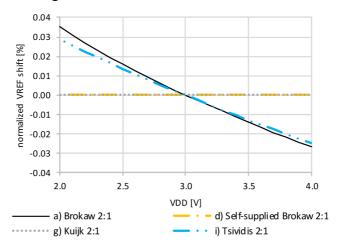

| 4.4.8. | Line Regulation                                           | 89  |

|--------|-----------------------------------------------------------|-----|

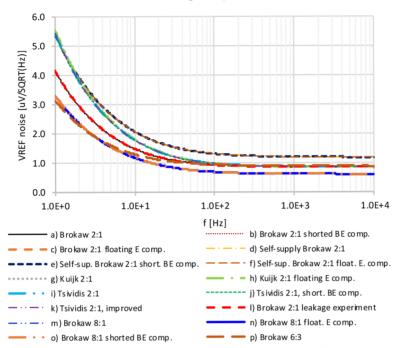

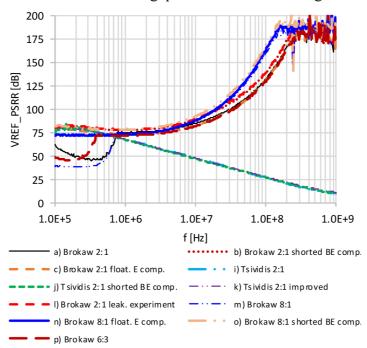

| 4.4.9. | Reference Voltage Noise                                   | 90  |

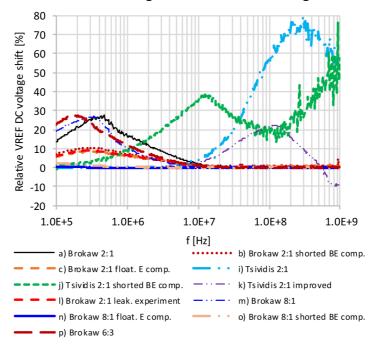

| 4.4.10 | EMI Susceptibility                                        | 91  |

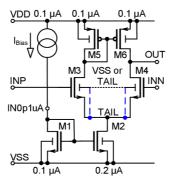

| 4.5.   | Study of Different Integrated OTA Topologies              | 94  |

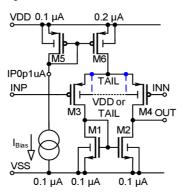

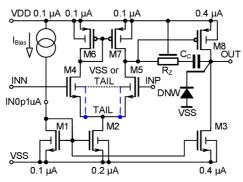

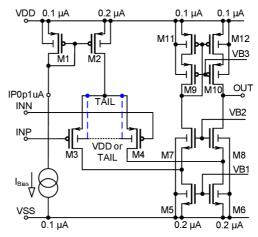

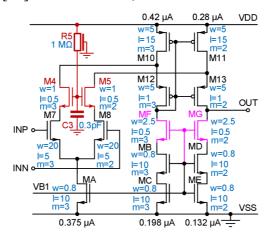

| 4.5.1. | Simple NMOS OTA                                           | 96  |

| 4.5.2. | Simple PMOS OTA                                           | 96  |

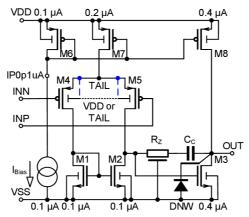

| 4.5.3. | Miller PPDAL OTA                                          | 97  |

| 4.5.4. | Miller NPDAL OTA                                          | 98  |

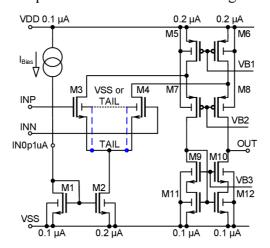

| 4.5.5. | Folded NMOS Cascode OTA                                   | 98  |

| 4.5.6. | Folded PMOS Cascode OTA                                   | 99  |

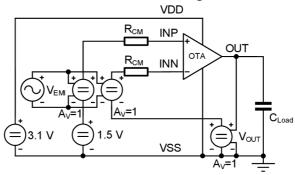

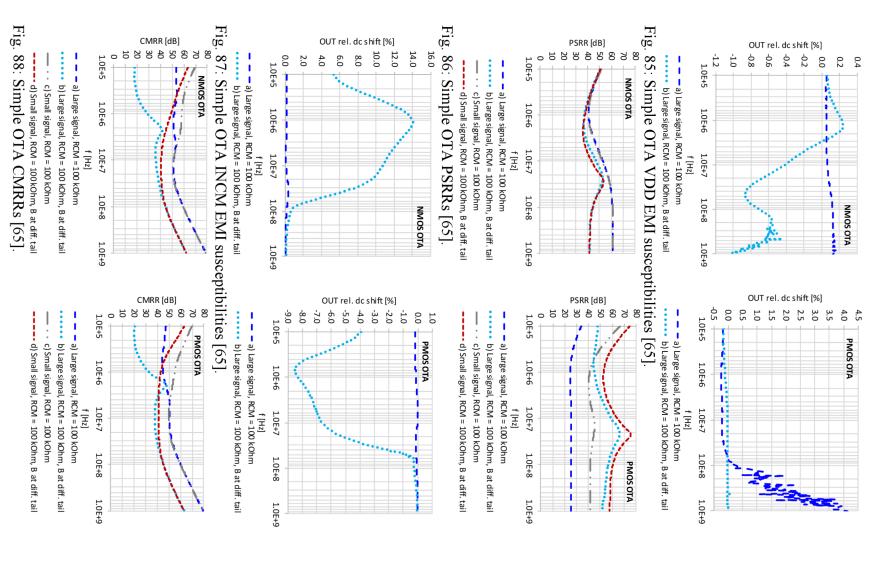

| 4.5.7. | OTA Parameters                                            | 100 |

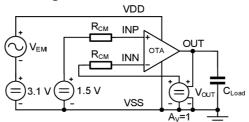

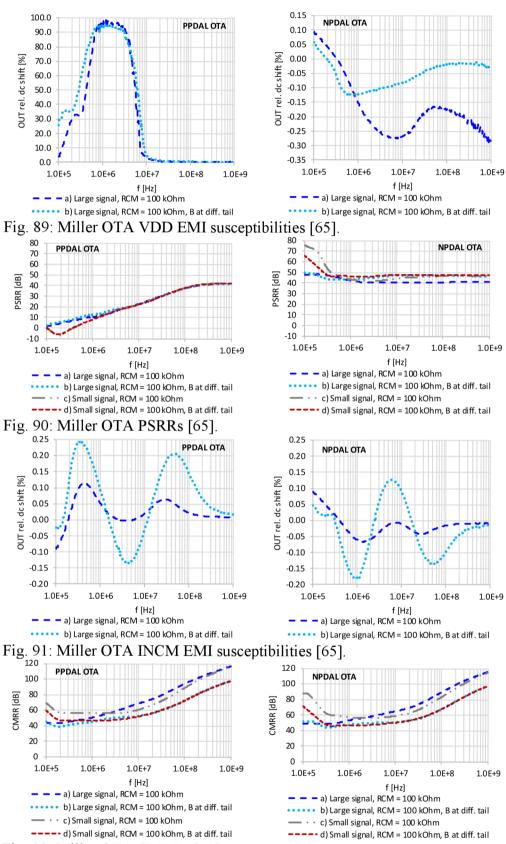

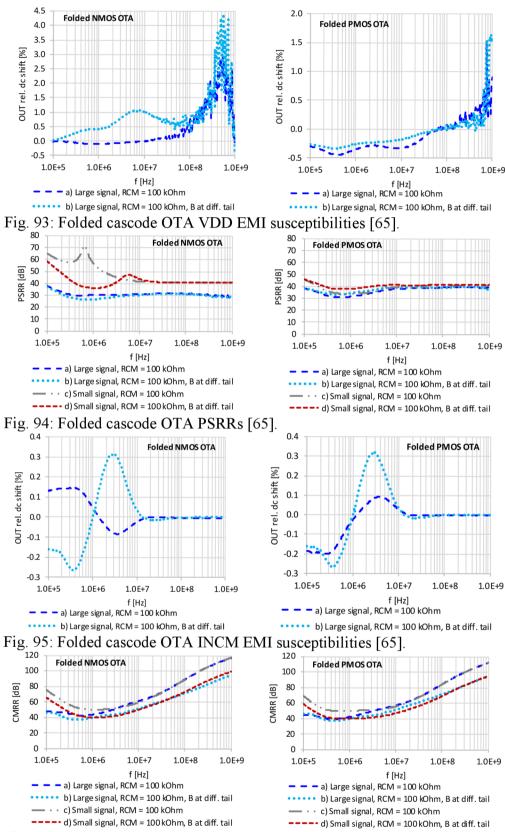

| 4.5.8. | Supply EMI Susceptibility                                 | 102 |

| 4.5.9. | Common Mode EMI Susceptibility                            | 103 |

| 4.5.10 | . Summary of OTA EMI Susceptibility Results               | 104 |

| 4.6.   | EMI Susceptibility Improved Voltage Reference             | 109 |

| 4.6.1. | Selection of the Bandgap Reference Core                   | 109 |

| 4.6.2. | OTA Improvements                                          | 109 |

| 4.6.3. | EMI Susceptibility of the OTA                             | 111 |

| 4.6.4. | Bandgap Reference Improvements                            | 113 |

| 4.6.5. | EMI Susceptibility of the Bandgap Reference               | 117 |

| 4.6.6. | Achieved Results of the Realized Voltage Reference        | 121 |

| 4.6.7. | An EMI Susceptibility Measurement with A Constant Voltage |     |

| Ampl   | tude on the Tested Pin                                    | 128 |

| 4.6.8. | Summary of Recommendations for Robust EMC Design          | 130 |

| CONG   | CLUSIONS                                                  | 132 |

## **List of Symbols and Abbreviations**

## Symbols:

| U | 015.             |                                                        |                        |

|---|------------------|--------------------------------------------------------|------------------------|

|   | A                | <br>Area of the semiconductor junction, voltage gain   | . [m <sup>2</sup> , -] |

|   | B                | <br>Bandwidth.                                         | [Hz]                   |

|   | C                | <br>Electric capacity.                                 | [F]                    |

|   | f                | <br>Frequency.                                         | [Hz]                   |

|   | gm               | <br>Transconductance.                                  | [S]                    |

|   | I                | <br>Electric current.                                  | [A]                    |

|   | J                | <br>Electric current density.                          | $[A/m^2]$              |

|   | $oldsymbol{J}_0$ | <br>The first order Bessel function of the first kind. | [-]                    |

|   | k                | <br>Boltzmann constant.                                | [J/K]                  |

|   | K                | <br>Scaling factor.                                    | [-]                    |

|   | $k_{\rm z}$      | <br>Impedance norm factor.                             | [-]                    |

|   | L                | <br>Electric inductance.                               | [H]                    |

|   | n                | <br>Temperature coefficient of charge carrier mobilit  | y. [-]                 |

|   | P                | <br>Electric power.                                    | [W]                    |

|   | q                | <br>Elementary charge of an electron.                  | [C]                    |

|   | Q                | <br>Quality factor of RLC circuit.                     | [-]                    |

|   | R                | <br>Electric resistance.                               | $[\Omega]$             |

|   | S                | <br>Laplace operator.                                  | [rad/s]                |

|   | T                | <br>Absolute temperature, period of the signal.        | [K, s]                 |

|   | $T_{\rm a}$      | <br>Ambient temperature                                | [°C]                   |

|   | $T_{ m j}$       | <br>Junction temperature of semiconductor              | [°C]                   |

|   | t                | <br>Time.                                              | [s]                    |

|   | TC               | <br>Temperature coefficient.                           | [unit/K]               |

|   | V                | <br>Electric voltage.                                  | [V]                    |

|   | Y                | <br>Electric admittance.                               | [S]                    |

|   | Z                | <br>Electric impedance.                                | $[\Omega]$             |

|   | α                | <br>Current density temperature coefficient.           | [-]                    |

|   | β                | <br>Electric current gain coefficient.                 | [-]                    |

|   |                  |                                                        |                        |

Absolute difference of value. [-]  $\Delta$  $\delta$ Relative error. [%] . . . Channel length modulation factor. λ [-] Average value. [-] μ . . . Standard deviation. [-]  $\sigma$ . . . Time constant. [s] τ Electric phase. [rad, °] . . . Circular frequency. [rad/s]  $\omega$

#### **Abbreviations:**

AC ... Alternating Current.

BCD ... Bipolar-CMOS and DMOS technology.

BCI ... Bulk Current Injection.

BG ... Band-Gap.

BLN ... Buried Layer of N-type semiconductor.

CMOS ... Complementary Metal Oxide Semiconductor technology.

CMRR ... Common-Mode Rejection Ratio.

CTAT ... Complementary to Absolute Temperature.

DC ... Direct Current.

DMOS ... Double-Diffused MOS transistor.

DPI ... Direct Power Injection.

DTI ... Deep Trench Isolation.

DUT ... Device Under Test.

DVI ... Direct Voltage Injection.

EMC ... Electro-Magnetic Compatibility.

EME ... Electro-Magnetic Emission.

EMI ... Electro-Magnetic Interference.

ESD ... Electro-Static Discharge.

GBW ... Gain Band-Width.

GND ... Electric ground.

HF ... High-Frequency signal.

IC ... Integrated Circuit.

ICM ... Input Common Mode.

ICMR ... Input Common Mode Range.

LC ... Electric circuit consisting of inductor and capacitor.

NBLHV ... High-voltage BLN.

NDMOS ... N-type DMOS transistor.

NEPI ... N-type semiconductor Epitaxial layer.

NMOS ... N-type Metal Oxide Silicon transistor.

NPD ... N-type Pass Device.

NPDAL ... N-type Pass Device with Active Load.

NWELL ... N-type semiconductor Well.

OPA ... Operational Amplifier.

OTA ... Operational Transconductance Amplifier.

PCB ... Printed Circuit Board.

pdf ... Probability density function.

PDMOS ... P-type DMOS transistor.

PEPI ... P-type semiconductor Epitaxial layer.

PMOS ... P-type Metal Oxide Silicon transistor.

PPD ... P-type Pass Device.

PPDAL ... P-type Pass Device with Active Load.

PSRR ... Power Supply Rejection Ratio.

PSUB ... P-type semiconductor Substrate of IC.

PTAT ... Proportional to Absolute Temperature.

PWELL ... P-type semiconductor Well.

RC ... Electric circuit consisting of resistor and capacitor.

RF ... Radio Frequency signal.

RFI ... Radio Frequency Interference.

RLC ... Electric circuit consisting of resistor, inductor and capacitor.

SUB ... Substrate of IC.

UGBW ... Unity Gain Band-Width.

VCVS ... Voltage-Controlled Voltage Source.

## **List of Figures**

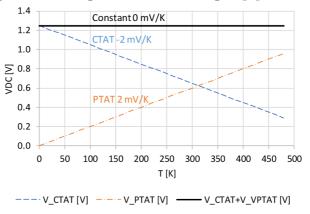

| Fig. 1: An ideal first-order temperature compensation in electronic circuits [5]23                      |

|---------------------------------------------------------------------------------------------------------|

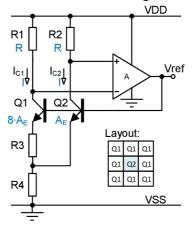

| Fig. 2: Idealized two-transistor Brokaw bandgap cell [6]                                                |

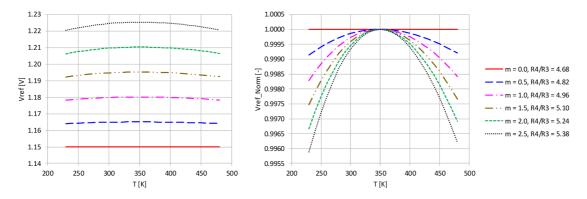

| Fig. 3: The reference voltage temperature characteristics after first-order                             |

| temperature compensation for various $m$ coefficients ( $T_0 = 350 \text{ K}$ )26                       |

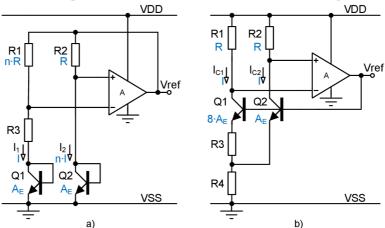

| Fig. 4: Fundamental circuits of a) Kuijk [24] and b) Brokaw [6] voltage references.                     |

|                                                                                                         |

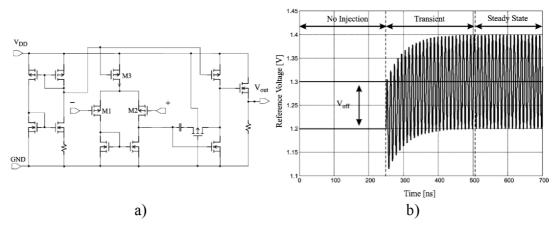

| Fig. 5: a) The PMOS-input two-stage Miller OPA circuit schematic and b) typical                         |

| voltage reference output waveform in the presence of 100 MHz and 1 V amplitude                          |

| EMI signal at V <sub>DD</sub> supply [11].                                                              |

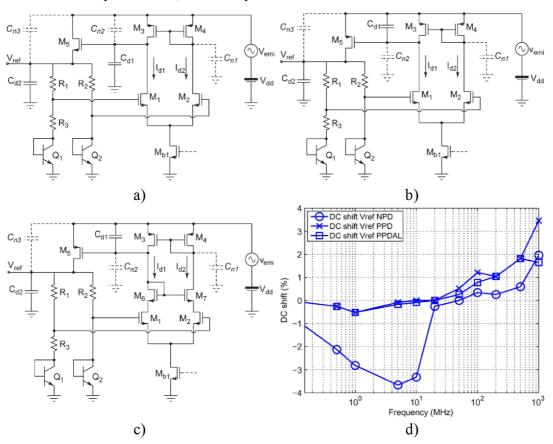

| Fig. 6: Kuijk voltage reference with a) NPD or b) PPD or c) PPDAL OPA and d)                            |

| DC voltage shift of these references for 0.5 V amplitude EMI at the power supply                        |

| [14]                                                                                                    |

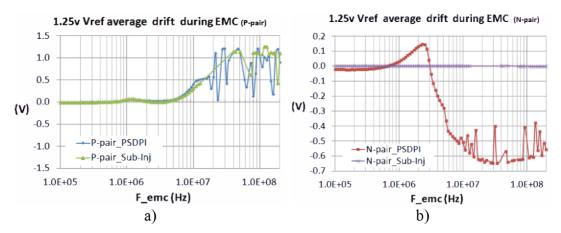

| Fig. 7: Power supply (PSDPI) and substrate (Sub-Inj) EMI susceptibility simulations                     |

| of Kuijk voltage reference with a) PMOS or b) NMOS differential pair OPA [15]. 29                       |

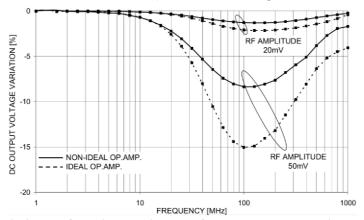

| Fig. 8: Simulations of Brokaw voltage reference power supply EMI susceptibility                         |

| with Miller OTA and an ideal OPA with the same gain and cutoff frequency [20]. 29                       |

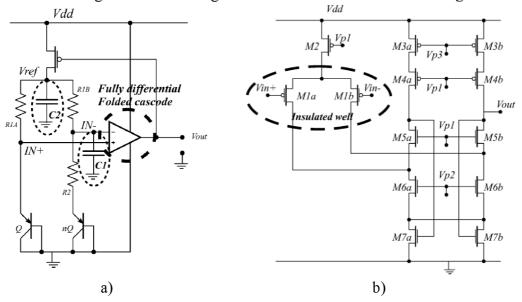

| Fig. 9: a) The improved Kuijk voltage reference with additional filtration capacitors                   |

| and b) the fully differential folded cascode OPA [16]                                                   |

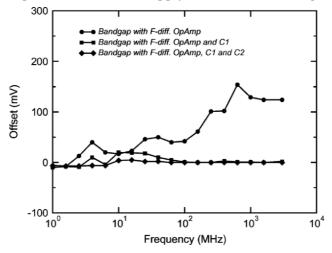

| Fig. 10: Reference voltage offset of the improved Kuijk voltage reference induced                       |

| by 0.5 V amplitude EMI at $V_{DD}$ supply [16].                                                         |

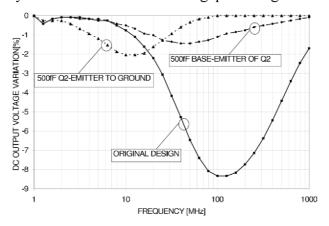

| Fig. 11: The EMI supply line simulations of the Brokaw bandgap with the original                        |

| design and with two different filtration solutions in the core [21]31                                   |

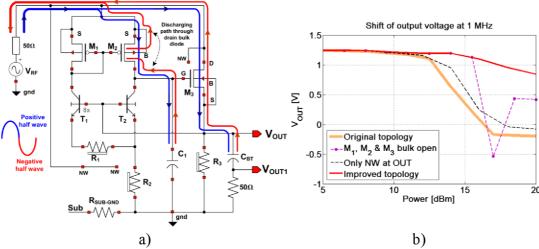

| Fig. 12: a) Interaction between M <sub>2</sub> and M <sub>3</sub> during the positive and negative half |

| wave of high EMI excitation in original topology and b) output reference voltage                        |

| DC offset induced by EMI at different power levels and constant frequency of                            |

| 1 MHz [23]                                                                                              |

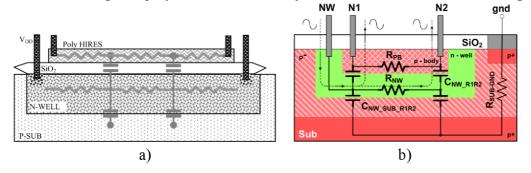

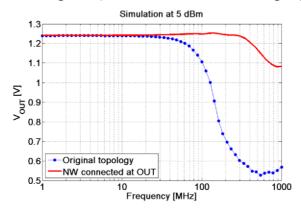

| Fig. 13: Simplified cross sections of one finger of a) the polysilicon resistor [20] and                |

| b) the P-body diffusion resistor [23].                                                                  |

| Fig. 14: Output reference voltage DC offset induced by EMI with original topology           |

|---------------------------------------------------------------------------------------------|

| from Fig. 12 a) and topology when N-well of resistors is connected to $V_{\rm OUT}$ [23] 33 |

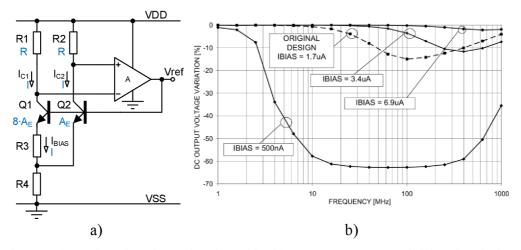

| Fig. 15: a) Brokaw bandgap circuit and its b) VDD EMI susceptibility simulations            |

| of decreasing or increasing the basic bandgap core bias current [20]                        |

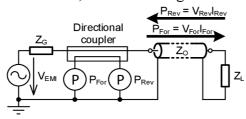

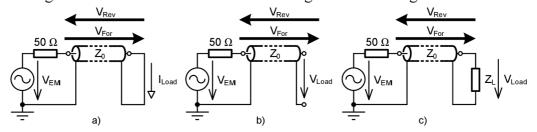

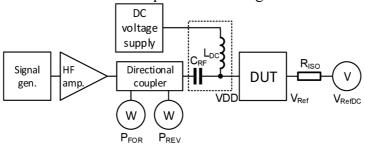

| Fig. 16: RF power on the line and its transfer in the typical DPI setup [27]36              |

| Fig. 17: Three possible states of the RF power injection: a) short, b) open, and            |

| c) general load at the end of the transmission line (DPI coupling point)                    |

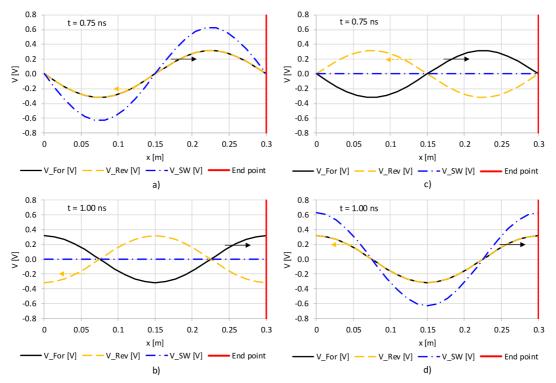

| Fig. 18: Examples of 1 GHz ideal voltage standing waves at the endpoint of the loss-        |

| less line for a) and b) short or c) and d) open-circuited end for two different times       |

| and $P_{For} = 1 \text{ mW } (0 \text{ dBm}).$ 38                                           |

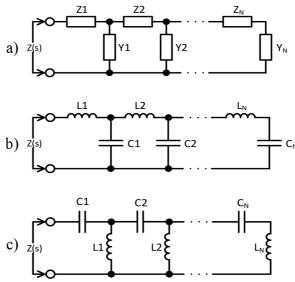

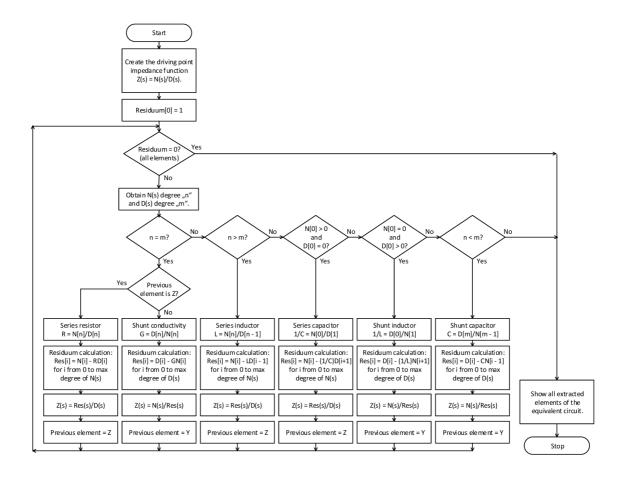

| Fig. 19: a) The general Cauer passive network impedance model, b) the first Cauer,          |

| and c) the second Cauer canonical form [28]                                                 |

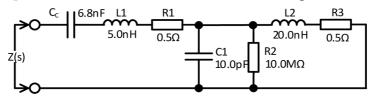

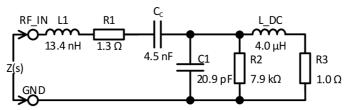

| Fig. 20: A passive circuit network model example of the proposed element-by-                |

| element extraction method                                                                   |

| Fig. 21: The reference passive circuit model for the impedance synthesis method             |

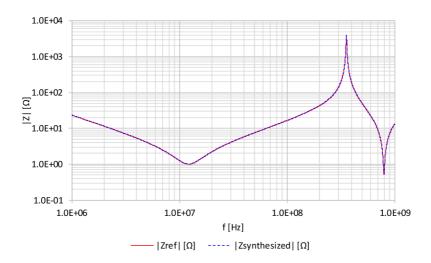

| verification [28]                                                                           |

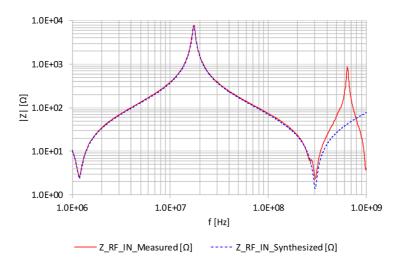

| Fig. 22: The impedance magnitude characteristics of reference and synthesized               |

| circuit model [28]46                                                                        |

| Fig. 23: The impedance phase characteristics of reference and synthesized circuit           |

| model [28]                                                                                  |

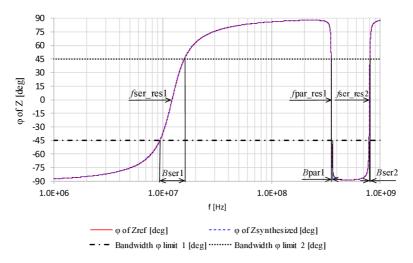

| Fig. 24: The bias-tee a) photo, b) its schematic diagram, and c) its impedance              |

| measurement setup schematic diagram [28]                                                    |

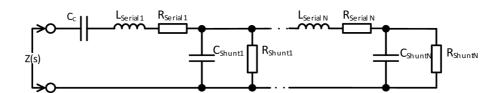

| Fig. 25: The synthesized passive circuit model of the bias-tee [28]47                       |

| Fig. 26: The impedance magnitude characteristics of the measured bias-tee and its           |

| synthesized circuit model [28]                                                              |

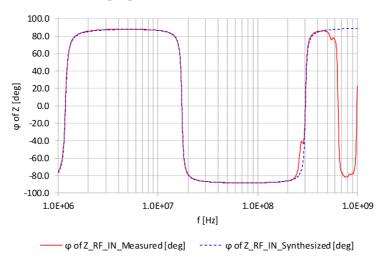

| Fig. 27: The impedance phase characteristics of the measured bias-tee and its               |

| synthesized circuit model [28]                                                              |

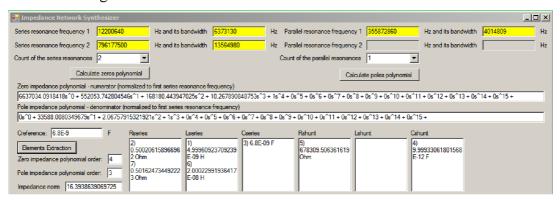

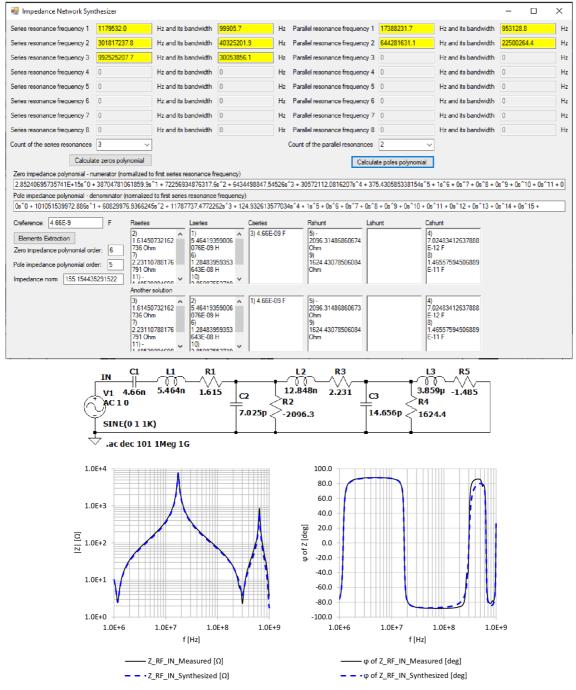

| Fig. 28: The passive network impedance synthesizer software using the proposed              |

| element-by-element extraction method (results are rounded to appropriate decimal            |

| places) [28]                                                                                |

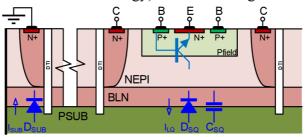

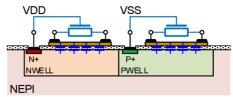

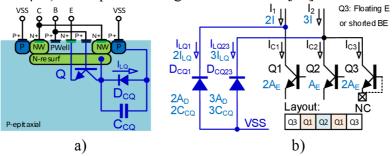

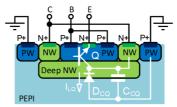

| Fig. 29: Simplified cross-section of I3T50 vertical NPN BJT in the IC (NEPI is an                        |

|----------------------------------------------------------------------------------------------------------|

| N-type epitaxial layer, BLN is an N-type buried layer, PSUB is a P-type substrate,                       |

| and DTI is deep trench isolation) [48]                                                                   |

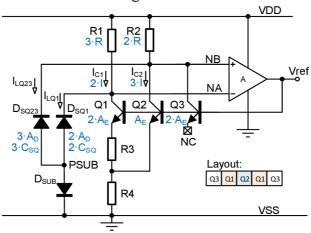

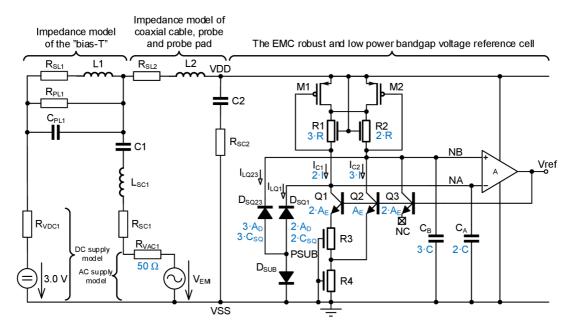

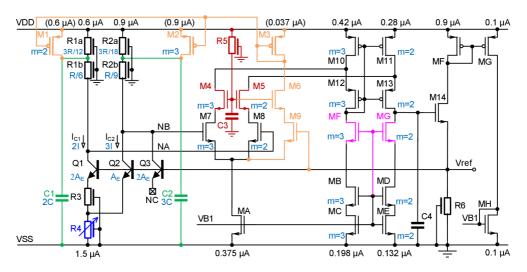

| Fig. 30: Brokaw bandgap with bipolar transistor leakage current compensation $52$                        |

| Fig. 31: Simplified cross-section of polysilicon resistors                                               |

| Fig. 32: Final low power and wide temperature range Brokaw bandgap with bipolar                          |

| transistor leakage current compensation                                                                  |

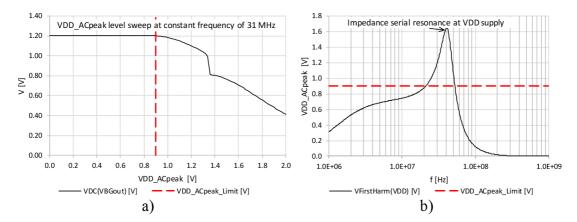

| Fig. 33: The voltage room estimation for maximum harmonic VDD supply                                     |

| disturbance. 54                                                                                          |

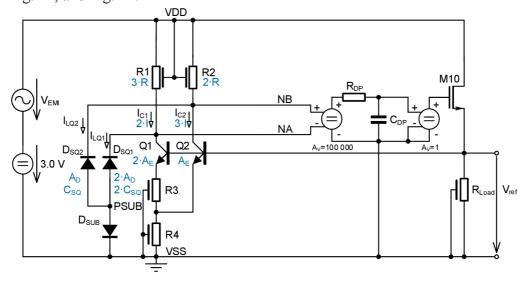

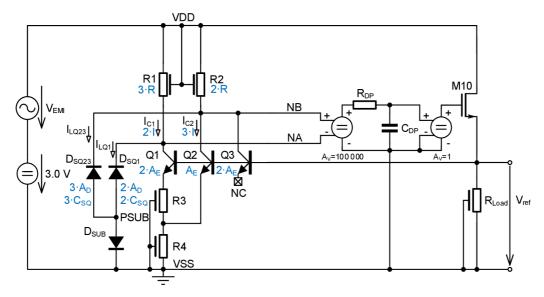

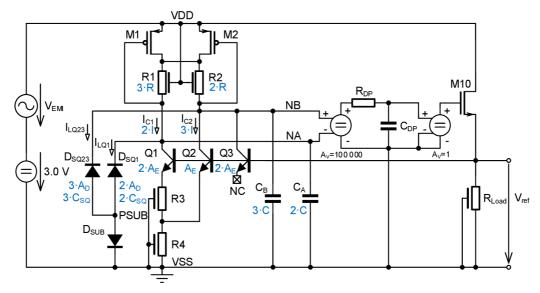

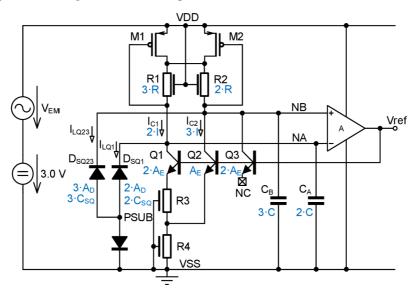

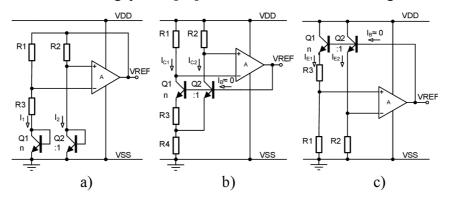

| Fig. 34: Configuration a), the basic bandgap core without leakage compensation55                         |

| Fig. 35: Configuration b), the basic bandgap core with leakage compensation                              |

| (additional transistor Q3, for more information, see chapter 4.1)56                                      |

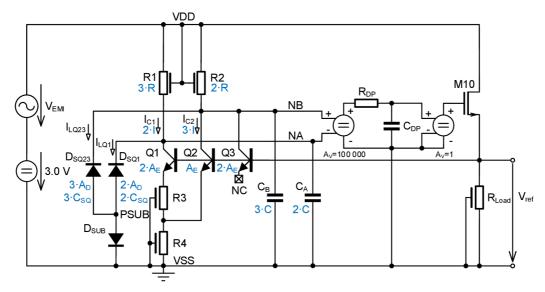

| Fig. 36: Configuration c), the basic bandgap core with leakage compensation (Q3)                         |

| and filtration capacitors $C_{\rm A}$ and $C_{\rm B}$ (for more information see chapter 4.1)56           |

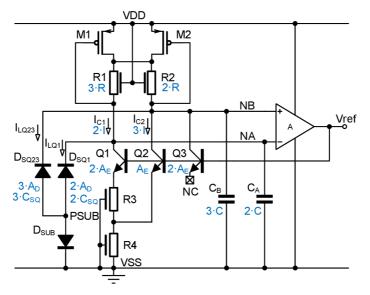

| Fig. 37: Configuration d), the basic bandgap core with leakage compensation (Q3),                        |

| filtration capacitors $C_A$ and $C_B$ , and common mode regulator (M1 and M2, for more                   |

| information, see chapter 4.1)                                                                            |

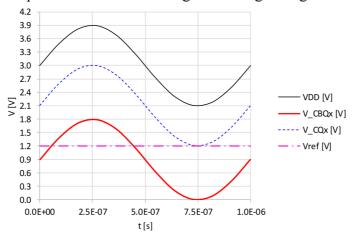

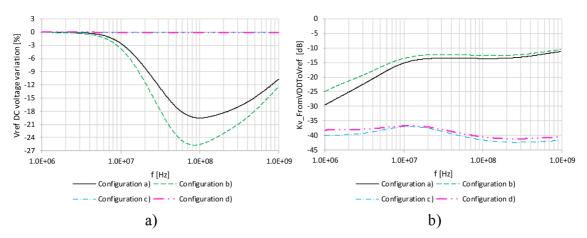

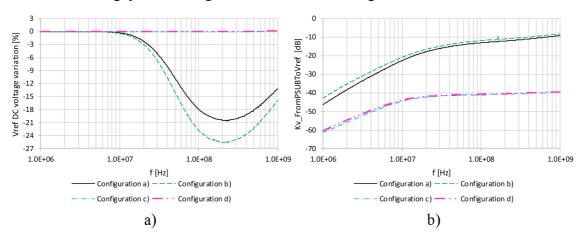

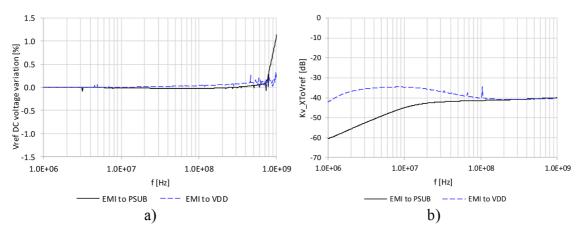

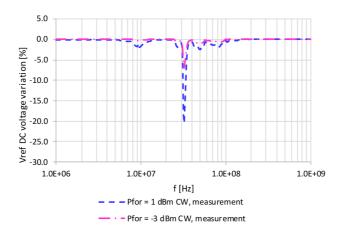

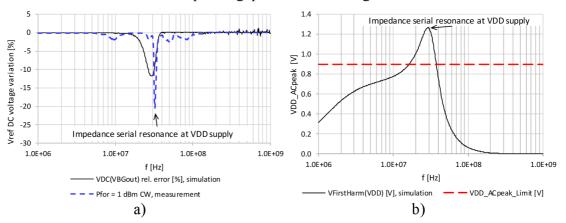

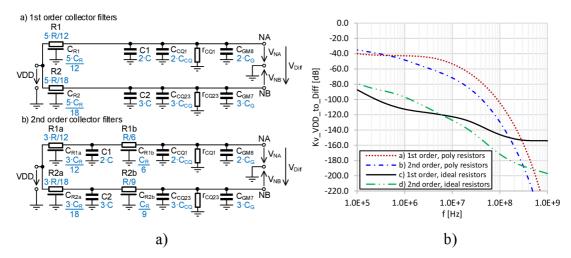

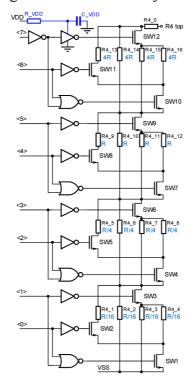

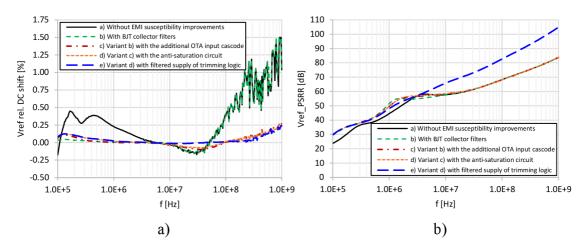

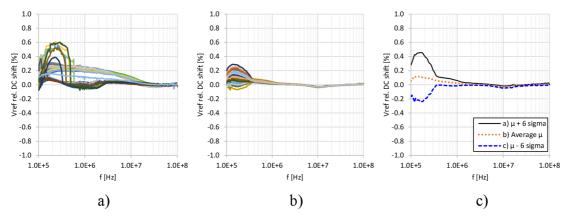

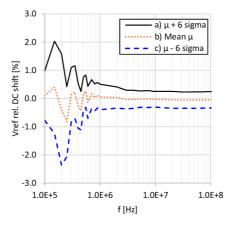

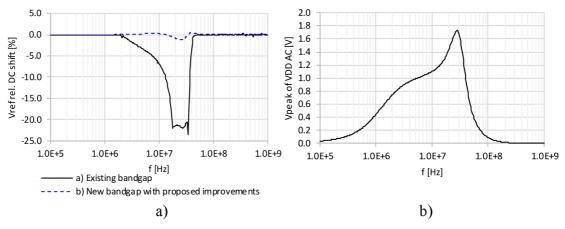

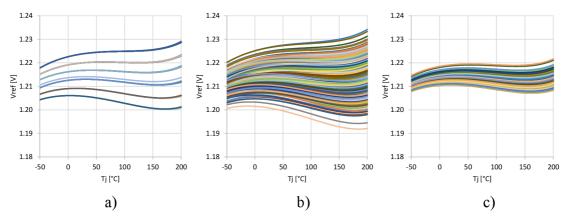

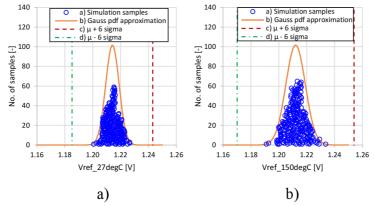

| Fig. 38: Basic VDD EMI susceptibility of the bandgap core various configurations:                        |

| a) $V_{ref}$ DC voltage variations and b) AC voltage transmissions with $V_{DD\_EMIpeak}$ of             |

| 0.632 V                                                                                                  |

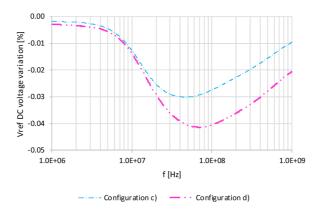

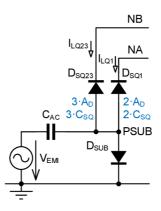

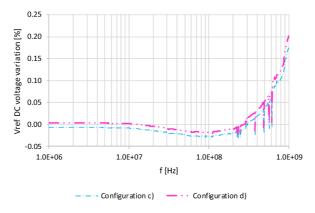

| Fig. 39: Detail of basic VDD EMI susceptibility: $V_{\text{ref}}$ DC voltage variations for the          |

| bandgap core configurations c) and d) with $V_{DD\_EMIpeak}$ of 0.632 $V_{\cdot\cdot\cdot\cdot\cdot}$ 58 |

| Fig. 40: Detail of simulation schematics of the bandgap core susceptibility to EMI                       |

| coming from the IC substrate (in the figure is part of the configuration b))59                           |

| Fig. 41: Basic PSUB (P-substrate) EMI susceptibility of the bandgap core various                         |

| configurations: a) $V_{\text{ref}}$ DC voltage variations and b) AC voltage transmissions with           |

| V <sub>PSUB_EMIpeak</sub> of 0.632 V                                                                     |

| Fig. 42: Detail of basic PSUB (P-substrate) EMI susceptibility: $V_{\text{ref}}$ DC voltage              |

| variations for the bandgap core configurations c) and d) with $V_{PSUB\_EMIpeak}$ of                     |

| 0.632 V                                                                                                  |

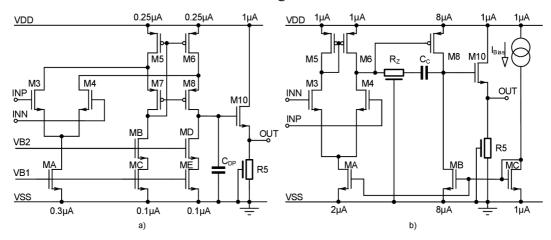

| Fig. 43: The OPAs for Brokaw bandgap: a) folded cascode and b) basic Miller C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | )PA.  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

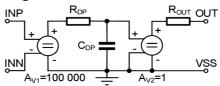

| Fig. 44: The simulation schematic diagram for the OPA AC open loop gain anal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

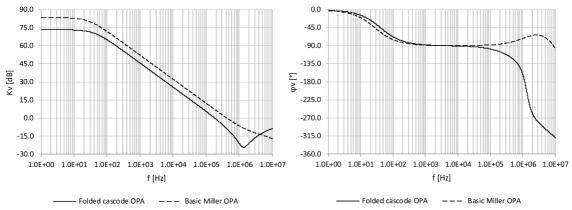

| Fig. 45: The AC open loop characteristics of the folded cascode and the basic M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| OPA (the open loop gain magnitude and phase).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

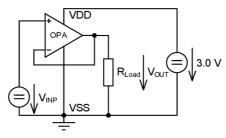

| Fig. 46: The OPA ICMR simulation schematic [51].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

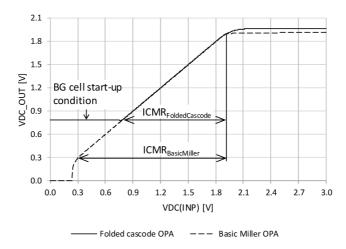

| Fig. 47: The DC voltage ICMR of the folded cascode and the basic Miller OPA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63    |

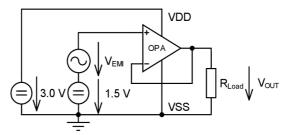

| Fig. 48: The input differential EMI susceptibility simulation schematic of the Ol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| in voltage follower mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63    |

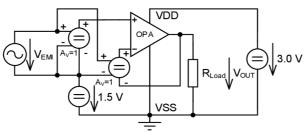

| Fig. 49: The VDD EMI susceptibility simulation schematic of the OPA in voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ge    |

| follower mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64    |

| Fig. 50: The EMI susceptibility of the ideal OPA in the ideal common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64    |

| Fig. 51: Simulation of an OPA CMRR (taken and edited from [51])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64    |

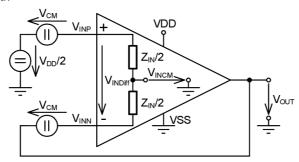

| Fig. 52: Simulation schematic for the EMI common mode susceptibility of the C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | )PA.  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66    |

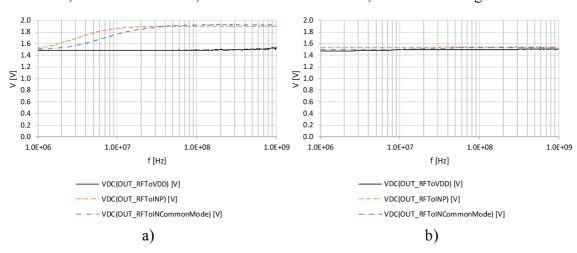

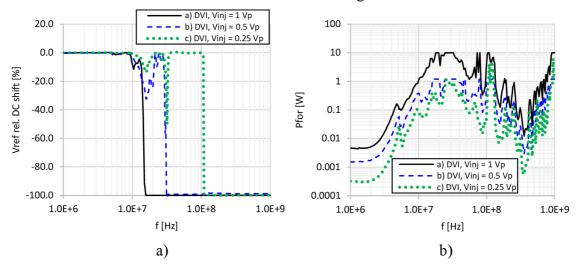

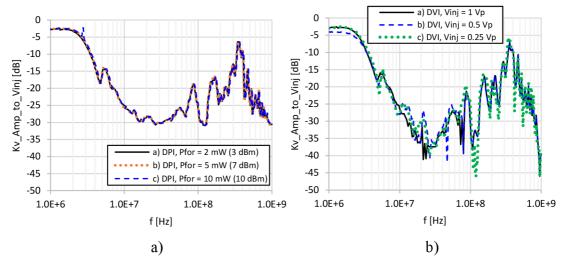

| Fig. 53: The EMI (RF) susceptibility simulations of a) folded cascode and b) based on the transfer of the tran | sic   |

| Miller OPA with V <sub>EMIpeak</sub> of 0.632 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66    |

| Fig. 54: The HF signal transfers (the first harmonic) of a) folded cascode and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| b) basic Miller OPA with $V_{\text{EMIpeak}}$ of 0.632 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67    |

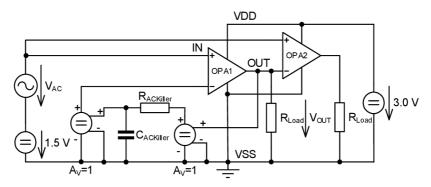

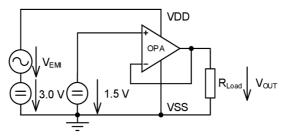

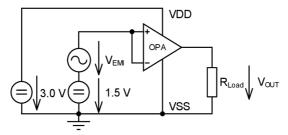

| Fig. 55: The basic VDD EMI susceptibility simulation schematic of the overall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| voltage reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68    |

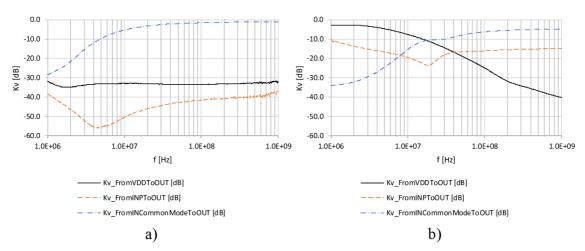

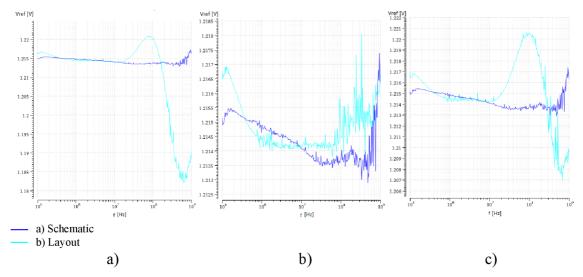

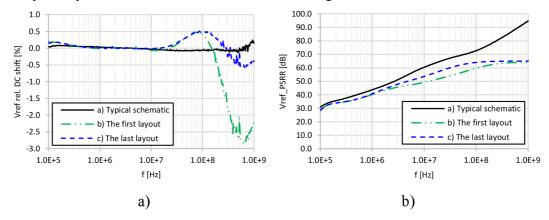

| Fig. 56: The a) $V_{\text{ref}}$ DC voltage variations and b) HF signal transmissions from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| coupling point to $V_{\text{ref}}$ (first harmonic) within basic EMI susceptibility simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns of |

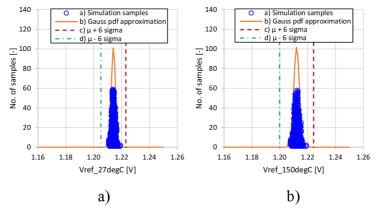

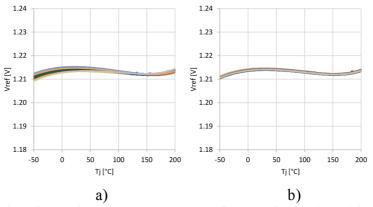

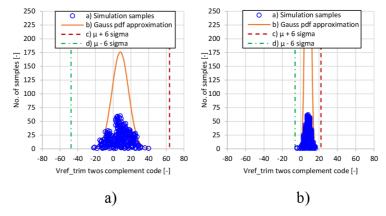

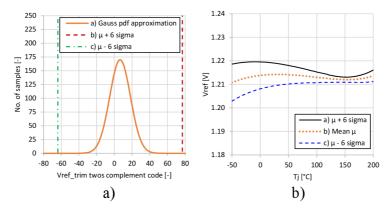

| the overall bandgap with $V_{\text{EMIpeak}}$ of 0.632 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |