# BRNO UNIVERSITY OF TECHNOLOGY

# Faculty of Electrical Engineering and Communication

# MASTER'S THESIS

Brno, 2024

Bc. Matyáš Sedláček

# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

## **DEPARTMENT OF RADIO ELECTRONICS**

ÚSTAV RADIOELEKTRONIKY

# A SHORT-PULSE GENERATOR FOR UWB APPLICATIONS

GENERÁTOR KRÁTKÝCH PULSŮ PRO UWB APLIKACE

MASTER'S THESIS DIPLOMOVÁ PRÁCE

AUTHORBc. Matyáš SedláčekAUTOR PRÁCESUPERVISORSUPERVISORdoc. Ing. Martin Štumpf, Ph.D.VEDOUCÍ PRÁCEVEDOUCÍ PRÁCE

BRNO 2024

# Diplomová práce

magisterský navazující studijní program Elektronika a komunikační technologie

Ústav radioelektroniky

Student: Bc. Matyáš Sedláček Ročník: 2 *ID*: 221069 *Akademický rok*: 2023/24

NÁZEV TÉMATU:

#### Generátor krátkých pulsů pro UWB aplikace

#### POKYNY PRO VYPRACOVÁNÍ:

Seznamte se s principy generování krátkých napěťových pulsů pro Ultra-Wide-Band (UWB) aplikace. Zaměřte se na generátory využívající step-recovery diody (SRD). Proveďte analýzu generátoru.

Vybraný koncept generátoru realizujte a experimentálně ověřte. Získané výsledky diskutujte.

#### DOPORUČENÁ LITERATURA:

[1] UWB Theory and Applications. Ed. I. OPPERMANN, M. HÄMÄLÄINEN, J. IINATTI. Chichester, UK: John Wiley, 2004. ISBN 0-470-86917-8.

[2] JEONGWOO HAN a C. NGUYEN. On the development of a compact sub-nanosecond tunable monocycle pulse transmitter for UWB applications. IEEE Transactions on Microwave Theory and Techniques. 2006, 54(1), 285-293 [cit. 2023-05-22]. ISSN 0018-9480.

Termín zadání: 16.2.2024

Termín odevzdání: 20.5.2024

Vedoucí práce: doc. Ing. Martin Štumpf, Ph.D.

doc. Ing. Lucie Hudcová, Ph.D. předseda rady studijního programu

#### UPOZORNĚNÍ:

Autor diplomové práce nesmí při vytváření diplomové práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

Fakulta elektrotechniky a komunikačních technologií, Vysoké učení technické v Brně / Technická 3058/10 / 616 00 / Brno

## ABSTRACT

This master's thesis is concerned with the analysis and design of a short-pulse generator. It focuses on the utilization of step recovery diodes and reactance-based circuit elements. A model of the SRD for the use in simulation is tuned. A pulse shaping network (PSN) is designed, the properties of which are described via parametric analysis. Consequently, aiming at improving the output characteristics of the device, possible modifications to the circuit are explored, e.g., the inclusion of transmission line stubs. A PSN driver and supply circuits are designed. The pulse generator is powered by a battery, to comply with portability and energy self-sufficiency requirements. The properties of the manufactured generator are then tested via measurements.

## **KEYWORDS**

impulse generator, ultra-short voltage pulses, dioda s krokovým zotavením, ultra-wide band, unipolar pulse

## ABSTRAKT

Tato diplomová práce je zaměřena na analýzu a návrh generátoru krátkých pulsů. Při vypracování jsou pro tvarování pulsu využity step recovery diody a reaktanční prvky. Za účelem simulace je odladěn ekvivalentí model SRD. Je proveden návrh tvarovacího obvodu, jehož vlastnosti jsou popsány za pomoci parametrické analýzy. Dále jsou prověřeny možné úpravy zapojení, např. zahrnutí pahýlů přenosových vedení, za účelem zlepšení výstupních parametrů zařízení. Je navržen budící obvod tvarovače a obvod napájení. Aby zařízení vyhovělo požadavkům na přenosnost a energetickou soběstačnost, je napájeno z baterie. Vlastnosti vyrobeného generátoru jsou následně ověřeny měřením.

## KLÍČOVÁ SLOVA

impulsní generátor, krátké napěťové pulsy, step-recovery diode, ultra-wide band, unipolární puls

Typeset by the thesis package, version 4.07; http://latex.feec.vutbr.cz

SEDLÁČEK, Matyáš. *A short-pulse generator for UWB applications*. Brno: Brno University of Technology, Faculty of Electrical Engineering and Communication, Department of Radio Electronics, 2024, 84 p. Master's Thesis. Supervised by doc. Ing. Martin Štumpf, Ph.D.

## Author's Declaration

| Author:        | Bc. Matyáš Sedláček                               |

|----------------|---------------------------------------------------|

| Author's ID:   | 221069                                            |

| Paper type:    | Master's Thesis                                   |

| Academic year: | 2023/24                                           |

| Торіс:         | A short-pulse generator for UWB appli-<br>cations |

I declare that I have written this paper independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the paper and listed in the comprehensive bibliography at the end of the paper.

As the author, I furthermore declare that, with respect to the creation of this paper, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation  $\S$  11 of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll. of the Czech Republic, Section 2, Head VI, Part 4.

Brno .....

author's signature<sup>\*</sup>

$<sup>^{*}\</sup>mathrm{The}$  author signs only in the printed version.

## ACKNOWLEDGMENT

I would like to thank the supervisor of my thesis, Dr. Martin Štumpf, for his valuable comments and advice.

# Contents

| In            | Introduction                                              |                                                                                                                                                                                              | 13                                                                     |  |

|---------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|

| 1             | <b>Prin</b><br>1.1<br>1.2<br>1.3                          | Aciples of generating very short pulses         Step recovery diodes         1.1.1         Modeling SRD behavior for transient analysis         Pulse shaping network         Driver circuit | <ol> <li>14</li> <li>16</li> <li>18</li> <li>20</li> <li>24</li> </ol> |  |

| 2             | <ul><li>Sim</li><li>2.1</li><li>2.2</li><li>2.3</li></ul> | ulations and analysis         Tuning the SRD model         Analysis of the PSN         2.2.1         The simulation setup & the ideal case         Possible modifications and improvements   | 29                                                                     |  |

| 3             | Circ<br>3.1<br>3.2<br>3.3                                 | cuit & PCB designGeneral design requirementsPulse shaping networkPower delivery & Driver circuit3.3.1Power source and protection3.3.2Buffer3.3.3Oscillator3.3.4DC voltage generation         |                                                                        |  |

| 4             | <b>Tes</b><br>4.1<br>4.2                                  | ting & Measurement<br>PSN measurements                                                                                                                                                       | <b>56</b><br>56<br>61                                                  |  |

| C             | onclu                                                     | ision                                                                                                                                                                                        | 64                                                                     |  |

| Bi            | bliog                                                     | graphy                                                                                                                                                                                       | 65                                                                     |  |

| Sy            | mbo                                                       | ols and abbreviations                                                                                                                                                                        | 70                                                                     |  |

| $\mathbf{Li}$ | st of                                                     | appendices                                                                                                                                                                                   | 72                                                                     |  |

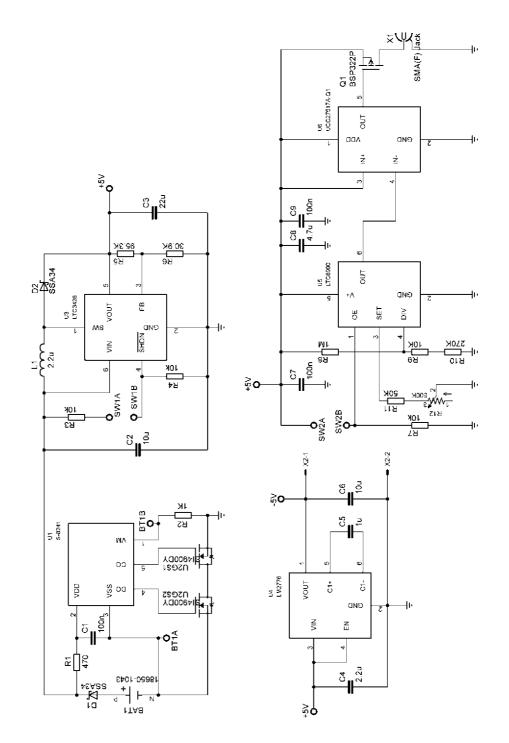

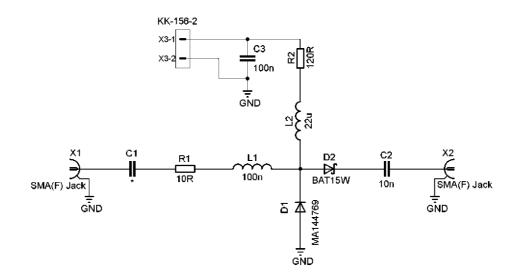

| $\mathbf{A}$  | A.1                                                       | cuit schematics Power & Driver                                                                                                                                                               | <b>73</b><br>73<br>74                                                  |  |

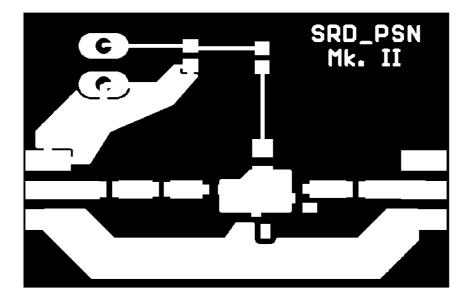

| В            | Printed circuit boards                   | <b>75</b> |

|--------------|------------------------------------------|-----------|

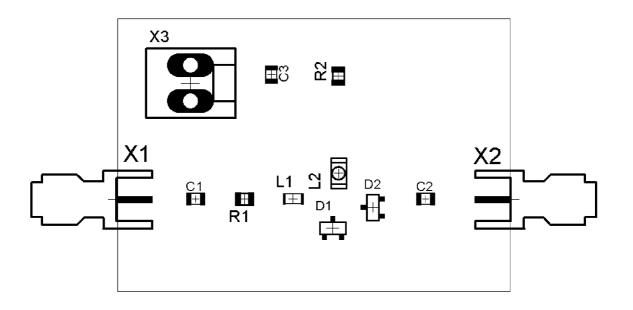

|              | B.1 PSN - Top layer                      | 75        |

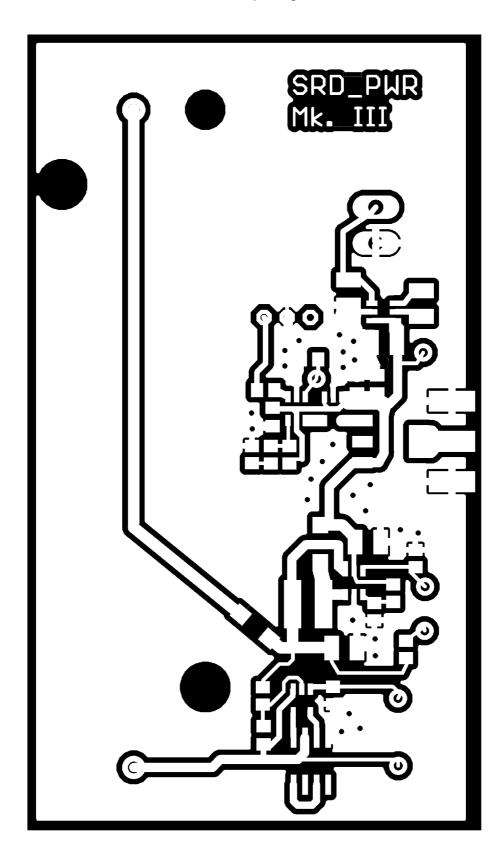

|              | B.2 PSN - Bottom layer                   |           |

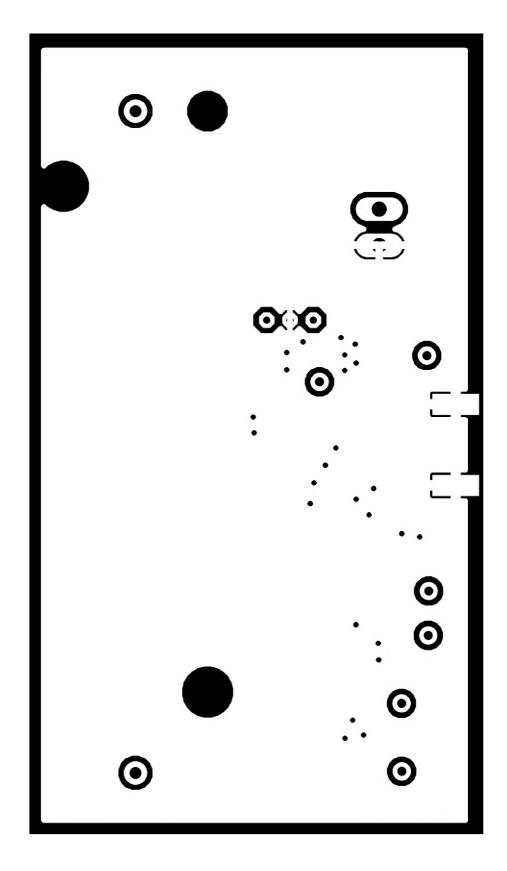

|              | B.3 PSN - Component placement            | 76        |

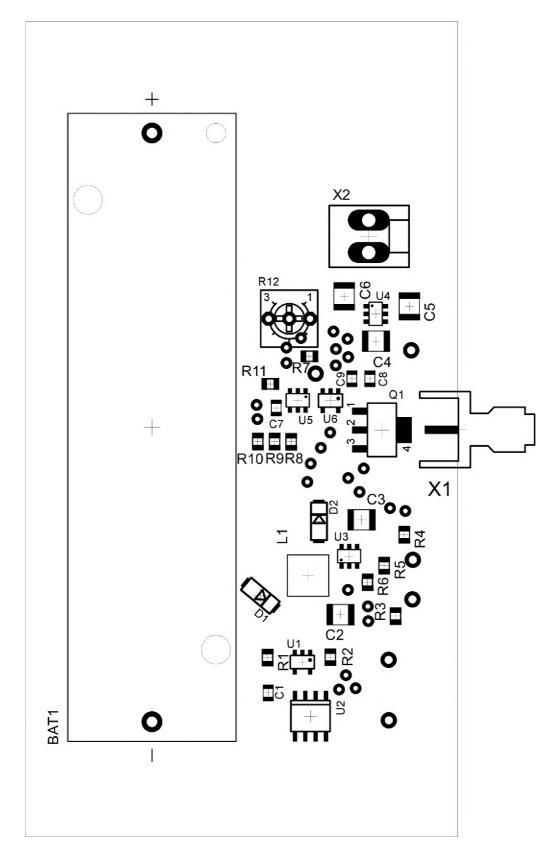

|              | B.4 Power & Driver - Top layer           | 77        |

|              | B.5 Power & Driver - Bottom layer        | 78        |

|              | B.6 Power & Driver - Component placement | 79        |

| $\mathbf{C}$ | List of components                       | 80        |

|              | C.1 PSN                                  | 80        |

|              | C.2 Power & Driver                       | 81        |

| D            | Photos                                   | 82        |

|              | D.1 Power & Driver                       | 82        |

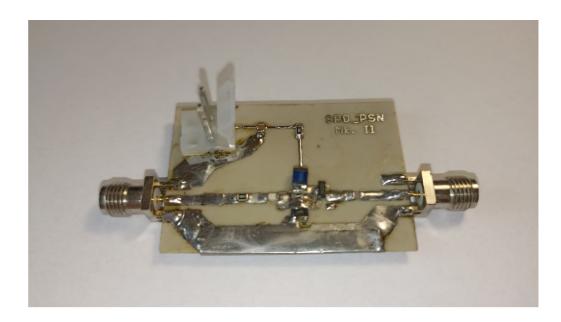

|              | D.2 PSN                                  | 83        |

|              | D.3 Inside enclosure                     | 83        |

| $\mathbf{E}$ | Instructions                             | 84        |

# List of Figures

| Gaussian pulses                                                                                                       | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pulse generator structure                                                                                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example of typical SRD dynamic behavior                                                                               | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Capacitance based model of SRD                                                                                        | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

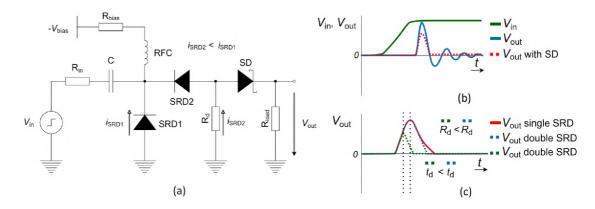

| Double SRD circuit; pulse falling edge effects                                                                        | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

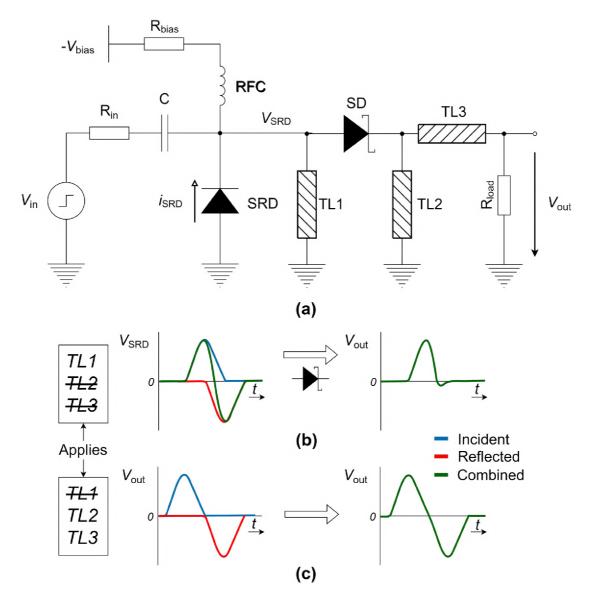

| Shorted stub for sharpening the falling edge or differentiating the pulse                                             | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

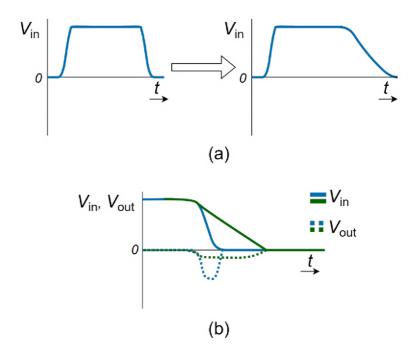

| Deformation at the output for the input falling edge                                                                  | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

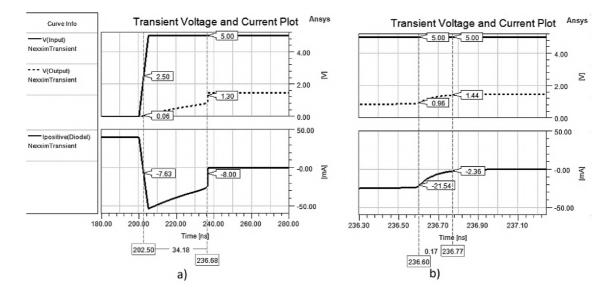

| Time waveforms from tuning the model                                                                                  | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

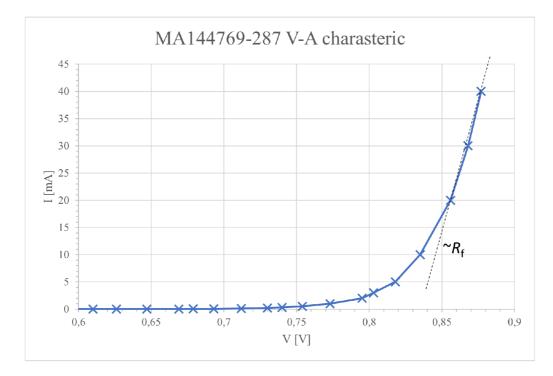

| V-A characteristic of MA144769-287                                                                                    | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

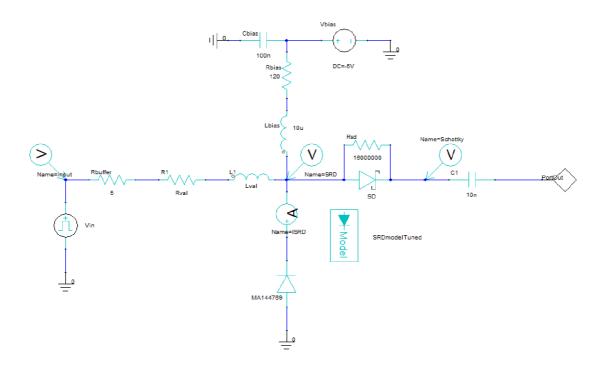

| Initial ideal PSN                                                                                                     | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

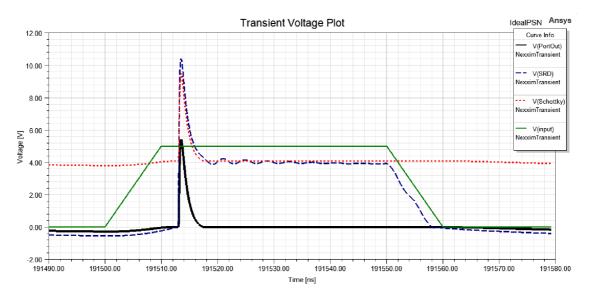

| Initial ideal PSN waveforms                                                                                           | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

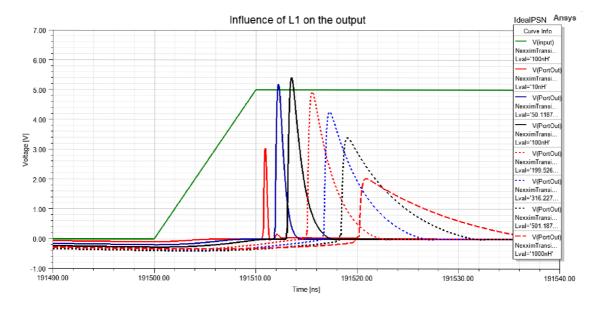

| Impact of series inductor value on output voltage                                                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

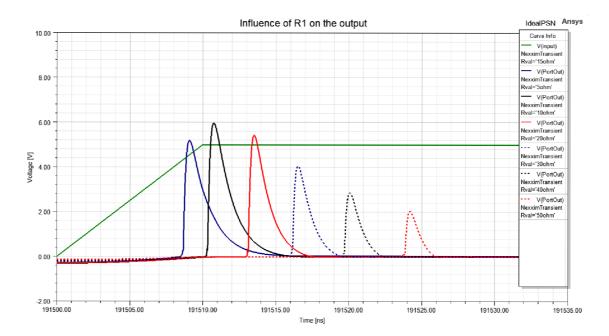

| Impact of series resistor value on output voltage                                                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

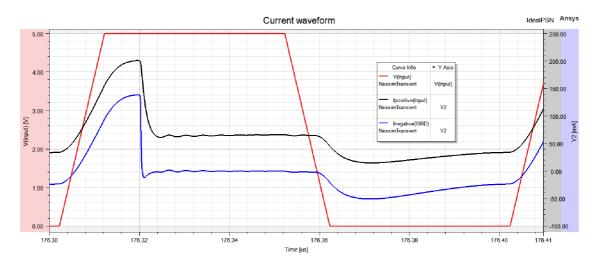

| Current drawn over one period                                                                                         | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

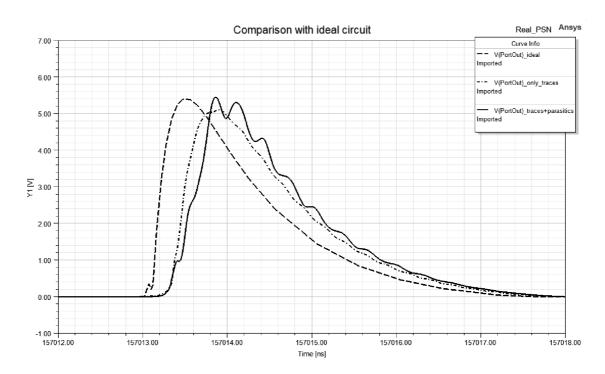

| Comparison of ideal and parasitic effects included output pulse                                                       | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

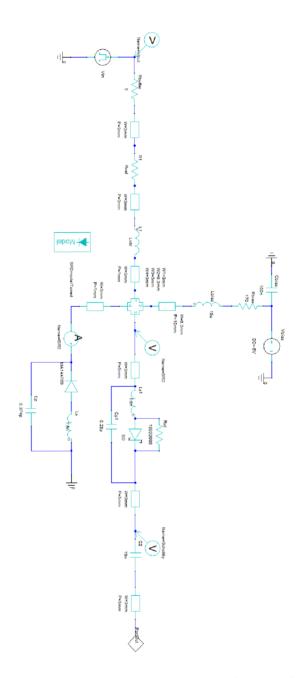

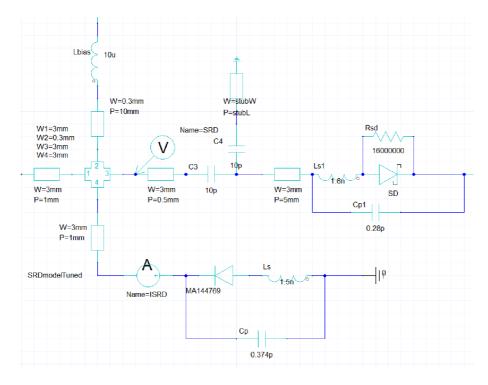

| Schematic of the PSN with transmission lines and package parasitics                                                   | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

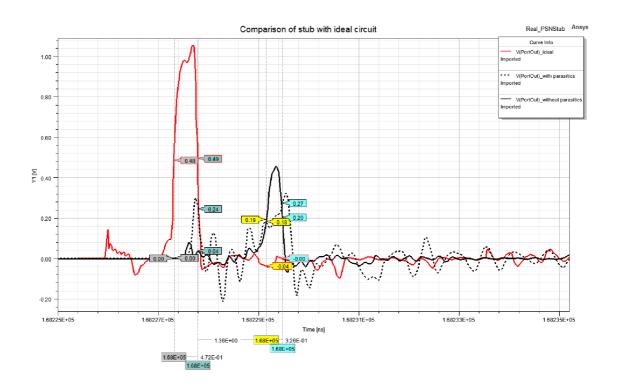

| Circuit modification for the simulation of the shorted stub $\ldots$ .                                                | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Simulation results for the shorted stub                                                                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

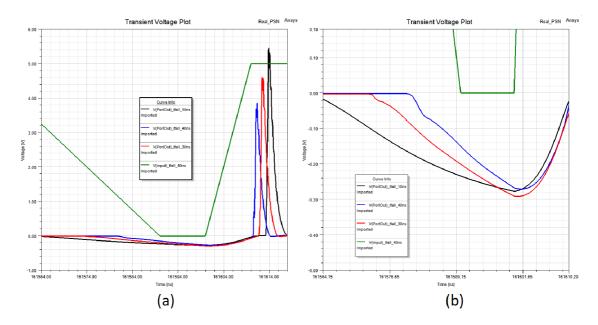

| Comparison of different input falling edge durations                                                                  | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Comparison of different input falling edge durations with an input                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| blocking capacitor                                                                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

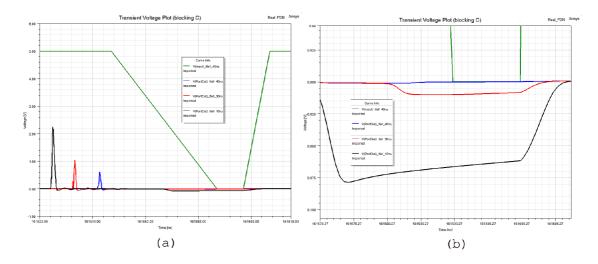

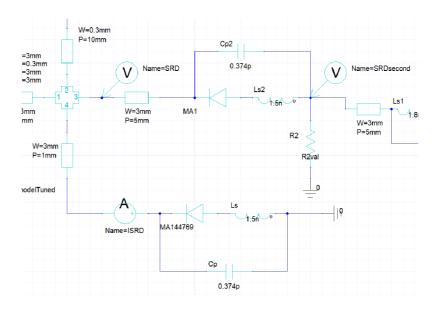

| Addition of the second SRD to the circuit                                                                             | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

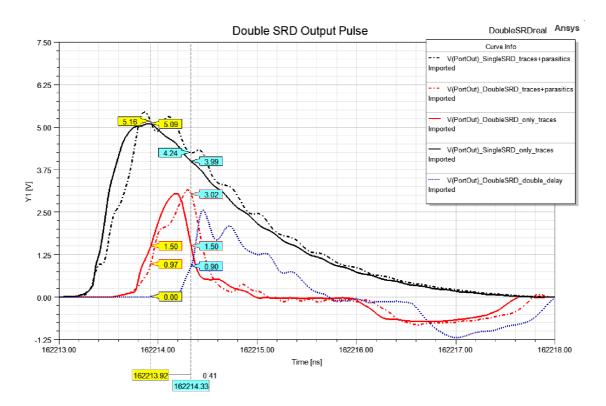

| Output waveforms for the double SRD variant                                                                           | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| The final schematic for the PSN                                                                                       | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Component value impact on pulse shape $\ldots \ldots \ldots \ldots \ldots \ldots$                                     | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Parasitic oscillations due to improper grounding                                                                      | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

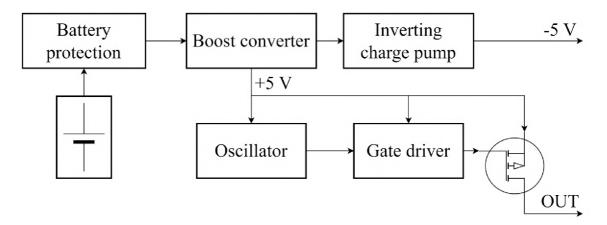

| Power delivery and driver board block diagram                                                                         | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

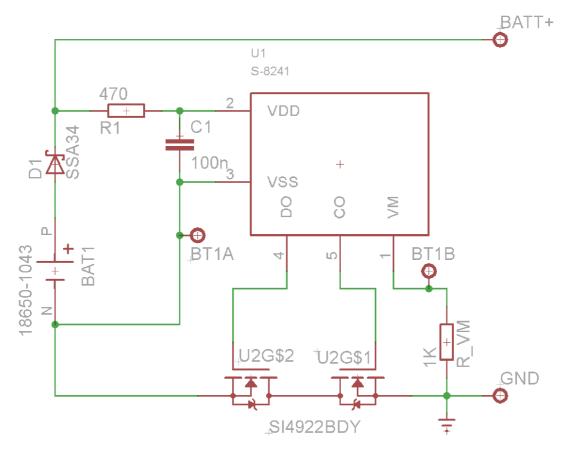

| Battery protection                                                                                                    | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

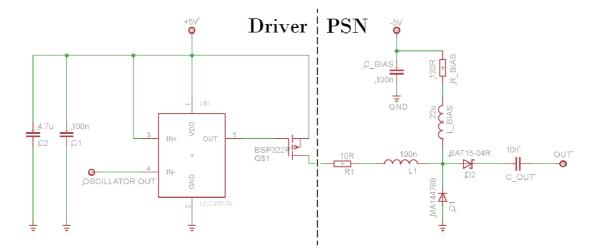

| Buffer structure schematic                                                                                            | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

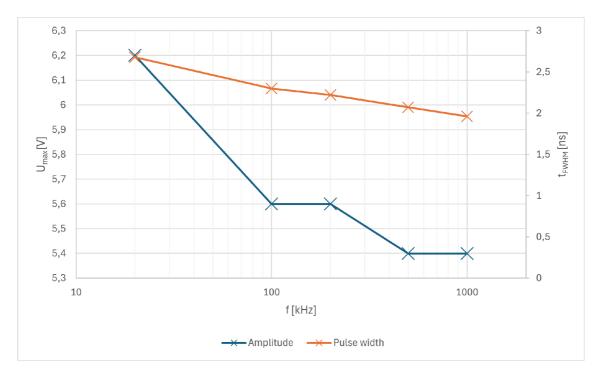

| Output amplitude dependence on input frequency                                                                        | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

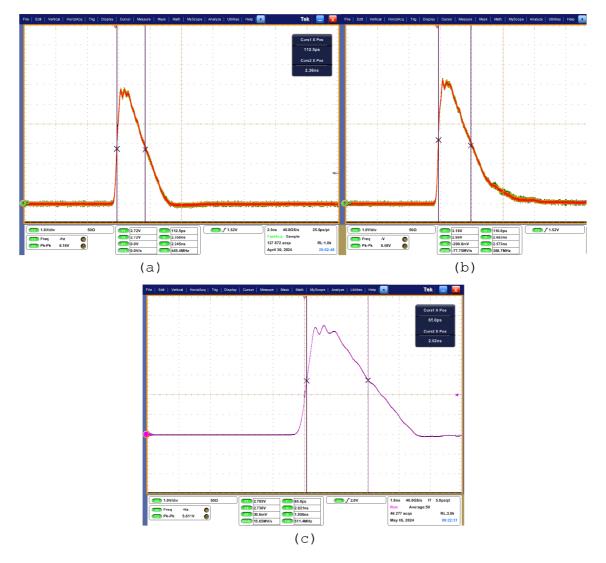

| Comparison of pulse shapes                                                                                            | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

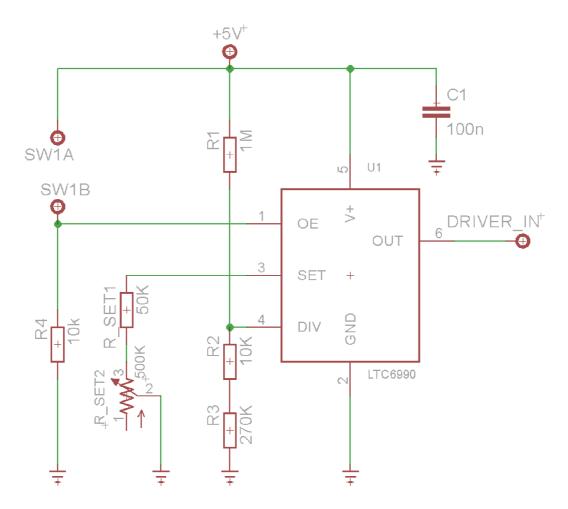

| Oscillator schematic                                                                                                  | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

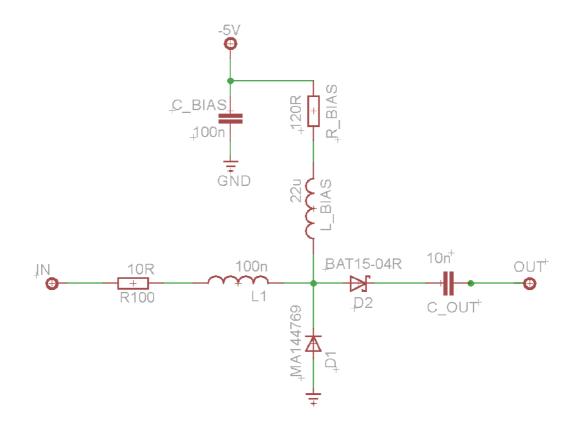

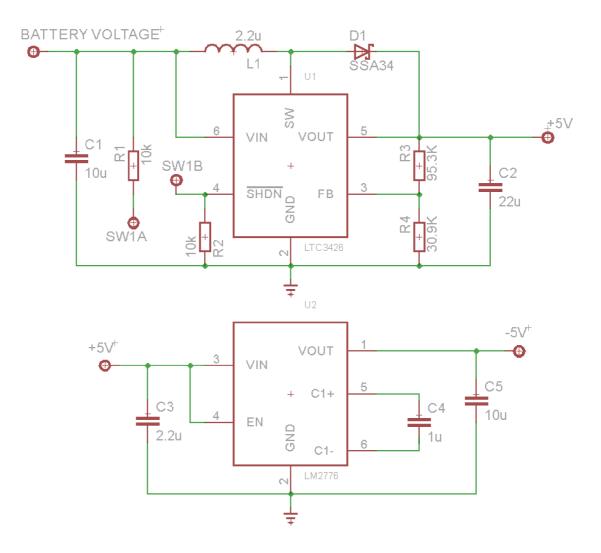

| DC supply network                                                                                                     | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

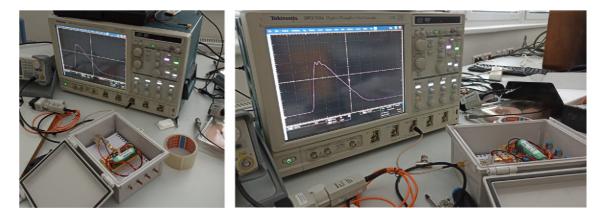

| Measurement setup                                                                                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

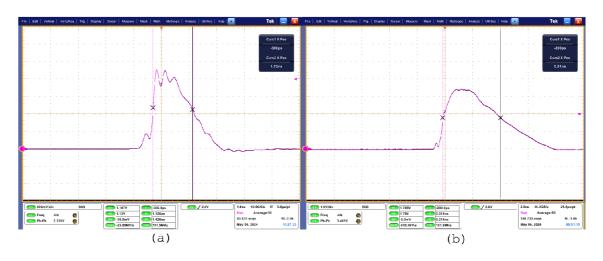

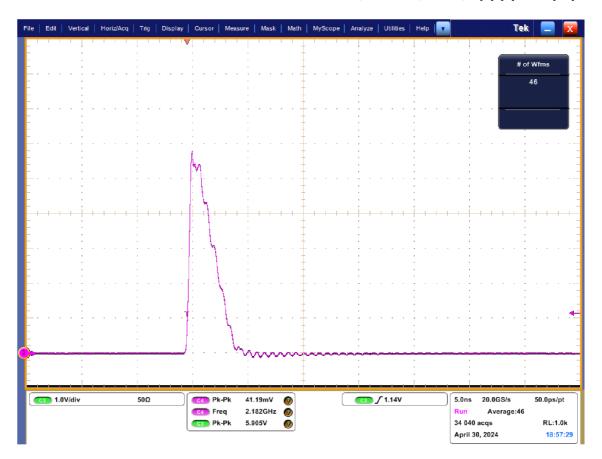

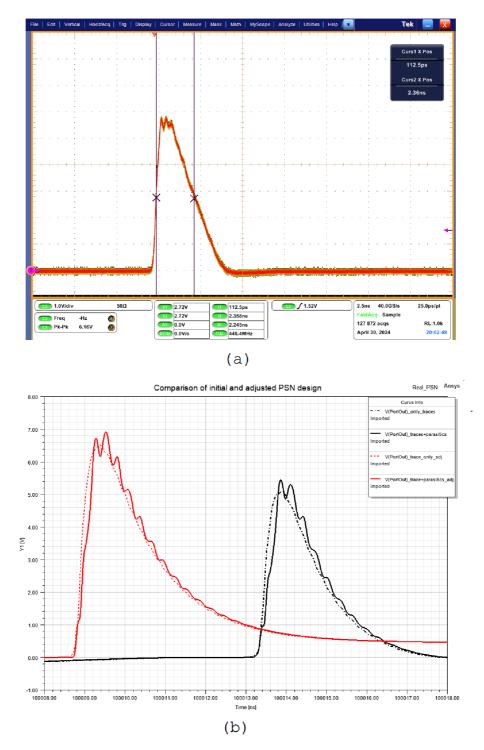

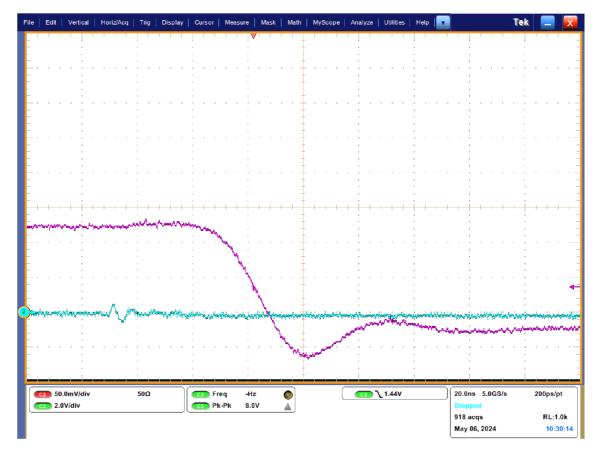

| PSN output pulse                                                                                                      | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

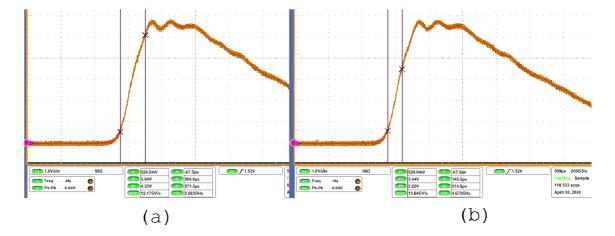

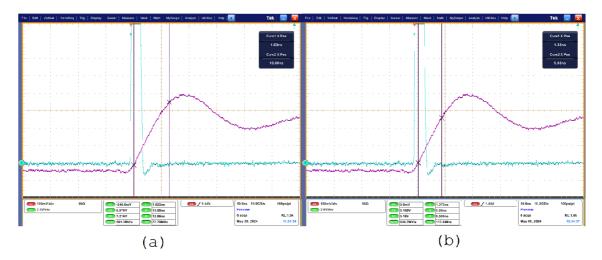

| Close-up of the rising edge $\ldots$ | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Zoom-in on the parasitic effects                                                                                      | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                       | Pulse generator structure .       .         Example of typical SRD dynamic behavior .       .         Capacitance based model of SRD .       .         Double SRD circuit; pulse falling edge effects .       .         Shorted stub for sharpening the falling edge or differentiating the pulse         Deformation at the output for the input falling edge .       .         Time waveforms from tuning the model .       .         V-A characteristic of MA144769-287 .       .         Initial ideal PSN .       .         Impact of series inductor value on output voltage .       .         Impact of series resistor value on output voltage .       .         Current drawn over one period .       .         Comparison of ideal and parasitic effects included output pulse .       .         Schematic of the PSN with transmission lines and package parasitics       .         Circuit modification for the simulation of the shorted stub .       .         Comparison of different input falling edge durations .       .         Addition of the second SRD to the circuit .       .         Output waveforms for the double SRD variant .       .         The final schematic for the PSN .       .         Component value impact on pulse shape .       .         Parasitic oscillations due to improper grounding .       . |

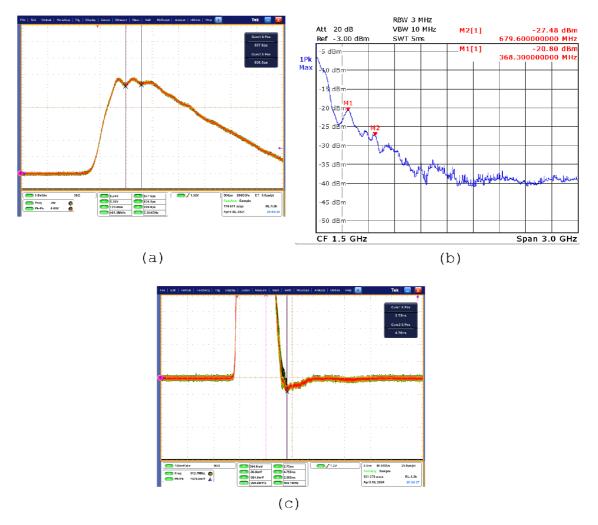

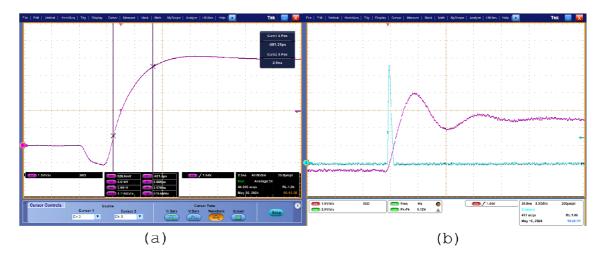

| 4.5 | Negative voltage swing on falling edge                                                       | 60 |

|-----|----------------------------------------------------------------------------------------------|----|

| 4.6 | Driver output waveforms by load                                                              | 61 |

| 4.7 | Driver output waveforms by load                                                              | 62 |

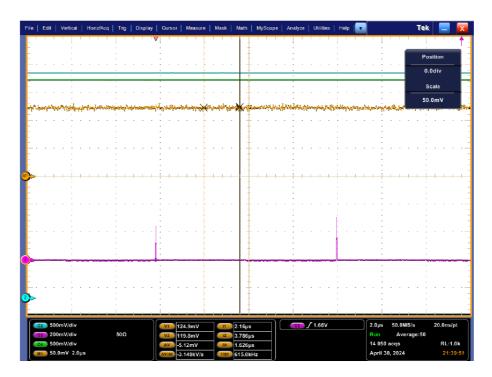

| 4.8 | Measurement of current consumption $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 62 |

# List of Tables

| 2.1 | SRD model parameters                                             | 28 |

|-----|------------------------------------------------------------------|----|

| 3.1 | Output pulse parameter dependence on component values $\ldots$ . | 43 |

| 3.2 | Gate driver options                                              | 49 |

## Introduction

This thesis concerns itself with the generation of wide band pulses. Its objective is to explore pulse generation using step recovery diodes and transmission lines. The outcomes of an initial feasibility study are used to design a pulse generator.

The device that will be developed within this research work is to be used as a standalone wide band pulse generator. The pulse generator is to be integrated in a measurement device that serves for non-invasive estimation of the electrical conductivity of tissue, a key parameter for designing on-body wireless interconnections. As such, the produced pulses should have a mathematically well definable shape for modeling and be distinctly separate, not interfering with each other. An important parameter is the pulse time width as it influences the physical dimensions of the measurement device. With the intended application in mind, we have set this parameter to 1 ns or more. Since the initial motivation for development is to replace an unwieldy and expensive piece of laboratory equipment, the device should be portable, energetically self-sufficient and reasonably low-cost.

The text that follows is divided into four chapters. The first chapter introduces the reader to the principles of generating wide band pulses. Here, a general structure of a pulse generator is described, including selected properties of step recovery diodes and their circuit models for transient analysis. Further, properties of pulse shaping networks utilizing these diodes are analyzed, including biasing, configurations, the inclusion of transmission lines and energy-storage elements. Finally, requirements on the driver are discussed. The second chapter specifies first how the diode model was tuned for its use in the chosen simulator. Subsequently, the results of simulation are used to provide a parametric study of the proposed generator. Finally, possible modifications based on the literature are tested and reviewed. The third chapter is a description of the design of the circuitry for the entire project and subsequent PCB design. The chapter is split into sections describing each module individually. The fourth chapter concerns itself with the measurement and analysis of the manufactured device, using the simulation results as a benchmark.

## 1 Principles of generating very short pulses

Very short electrical pulses are being utilized in many fields of engineering and science. As far as electrical engineering is concerned, one such field is the rather broad family of ultra-wide band (UWB) technologies. Applications of UWB stem from its key feature: a wide-band, noise-like spectrum in the frequency domain of a low power spectral density. From a communication standpoint, this enables UWB systems to co-exist with narrow-band ones in the shared frequency band without introducing mutual electromagnetic (EM) interference. In addition, the broad frequency spectrum of a short EM pulse plays an important role in inversion methods employing transient EM data, where the pulse distortion caused by its passing through an analyzed material sample provides the sample's EM properties in a wide band of frequencies. This is advantageous in radar technology, where shorter pulses lead to a higher spatial resolution. Accordingly, it follows that UWB technology relies on pulses with fast transition times and a low duration [1]. A method in this respect is described in the present chapter.

#### **Pulse shapes**

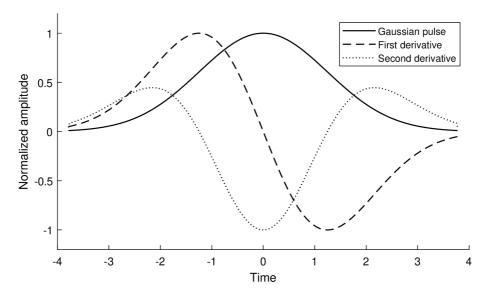

The Gaussian pulse with its first and second derivatives, which can be seen in Fig. 1.1 are the most commonly used pulse shapes in UWB-based communication systems, each with their own benefits. Given the fact that time-differentiated Gaussian pulses are mostly obtained by adding differentiators to a Gaussian-pulse generator, the generation of a Gaussian pulse requires the least complicated and most compact circuit.

Owing to its relatively low clutter level (meaning unwanted echoes due to multidirectional spreading) and high-resolution characteristics [2], the Gaussian pulse is also frequently employed in ground penetrating radar (GPR) applications.

Its first derivative, usually termed as monocycle, is very common in impulse radio or radar. It does not contain a DC component, which implies that less energy is wasted in converting it to a radiated EM wave at the antenna [3].

Fig. 1.1: Gaussian pulse and its first two derivatives

#### Pulse generator structure

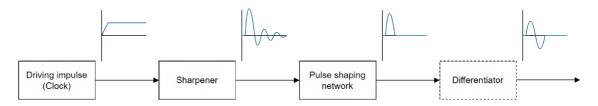

A general pulse generator circuit consists of three main parts, which are depicted in Fig. 1.2. Here, for the sake of clarity, the differentiator is not a part of the pulse shaping network.

The first section is the **driver circuit**, which provides some form of time-varying voltage. In existing generator designs, the driver circuit dominantly generates a square wave produced by a clock oscillator (or a function generator if the design is not stand-alone) [4], a square wave with different rise and fall times [5] or a sine wave [6]. The driver should be able to handle sudden current draws from the following circuitry, otherwise it needs to be buffered.

Fig. 1.2: Generalized structure of a Gaussian pulse (monocycle) generator

The next part is the **sharpener**, the purpose of which is to increase the slope of the rising/falling edge of the waveform coming from the driver. This is a crucial part of the generator, since the type of sharpener that is used determines a baseline for achievable output pulse properties, such as the pulse time width and its amplitude. The other blocks must be designed to be compatible with to the chosen type of sharpener. This is explored in more detail below, in the ensuing Sec. 1.1.

Obviously, devices which are used for sharpening the pulse edges are not ideal. Owing to parasitic effects due to surrounding circuit elements and the circuit board itself, the sharpener will produce pulses with undesirable traits. A typical unwanted effect is ringing that manifests itself by decaying oscillations of the pulse's trailing tail. It might also be the case that the pulse width or amplitude need to be modified to better fit the application at hand. The solution to both of these problems is the **pulse shaping network** (PSN).

#### **1.1 Step recovery diodes**

The pulse sharpener may be realized in various ways. Despite the existence of other options (e.g., vacuum tubes, mercury-wetted mechanical switches, non-linear transmission lines), we shall limit the scope of this work to designs based on semiconductor devices, the most common option in low power applications. The most popular semiconductor devices are: (a) tunnel diodes, that can achieve rise times of the order of tens of picoseconds with sub-volt amplitudes [7]; (b) avalanche transistors, with rise times in the range of hundreds of picoseconds and amplitudes in the range of tens of volts [7][8]. And, finally, (c) step recovery diodes (SRDs), which are capable of producing rise times in the range from high tens to low hundreds of picoseconds, with amplitudes of the order of volts and lower tens of volts [7][9]. This thesis focuses on the use of SRDs. For this reason, only SRD-based solutions are considered further.

The SRD (also known as the snap-off or charge storage diode) is a special type of silicon PIN diode, which finds its use in pulse sharpeners, comb generators, frequency multipliers and others. Static properties of SRDs are similar to those of a standard PN junction diode. The most important difference is in its dynamic behavior. Indeed, in contrast to standard diodes, it possesses the ability to very abruptly change its impedance on reversing the voltage bias. When the diode is forward biased and thus appears as a low impedance, charge is being stored inside the junction. This charge is in the form of minority carriers, that need a finite time to recombine. If the bias is reversed the diode still acts as a low impedance, thereby conducting electrical current. During this period, the stored charge starts to be depleted. Once the junction discharges completely, the diode will close abruptly, thus returning to its high impedance state. This causes the current to drop to zero in a very fast step [9].

Designing pulse sharpeners with SRDs relies on the knowledge of basic relations describing how the diode accumulates and releases charge. The two most important formulas, that have been presented in [9] and utilized in e.g. [3][10][11], state

$$\frac{t_{\rm S}}{\tau} \simeq \ln\left[1 + \frac{I_{\rm F}(1 - \exp\left(-t_{\rm F}/\tau\right)}{I_{\rm R}}\right] \tag{1.1}$$

where  $t_{\rm S}$  is the time required to remove the charge stored by the forward current  $I_{\rm F}$ , which has been previously applied for the duration  $t_{\rm F}$ ;  $I_{\rm R}$  represents the constant reverse current, used to remove the charge. Furthermore,  $\tau$  denotes the minority carrier lifetime, which is intrinsic to the diode. The other relation,

$$t_{\rm r} = \sqrt{t_{\rm t}^2 + (2.2R_{\rm eq}C_{\rm vr})^2},$$

(1.2)

describes the dependencies between the transition rise time  $t_{\rm r}$ , the intrinsic transition time of the diode  $t_{\rm t}$ , and the circuit controlled rise time  $(2.2R_{\rm eq}C_{\rm vr})^2$ . This relation holds when the rise time is measured from 10%-90% of the edge. Next,  $R_{\rm eq}$  represents the equivalent resistance of the surrounding circuit from the diode's perspective, and  $C_{\rm vr}$  is the capacitance of the diode under reverse bias. Equation (1.2) therefore serves to isolate the effect that the external circuitry has on the pulse edge from what is contributed by the diode itself.

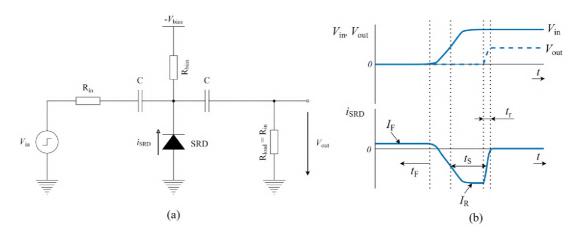

Fig. 1.3: Typical dynamic behavior of the SRD: (a) Demonstration circuit; (b) Current and voltage waveforms

The typical dynamic behavior of an SRD is represented in the waveforms of Fig. 1.3, corresponding to Eq. (1.1). In the given circuit, the fast transition of current through the diode also causes a corresponding transition of the output voltage. As far as the voltages are concerned, the effect appears like a shortening of the rising edge, as expected.

If the circuit design fulfills the condition  $t_{\rm F} >> \tau$ , Eq. (1.1) can be simplified:

$$\frac{t_{\rm S}}{\tau} \simeq \ln\left(1 + \frac{I_{\rm F}}{I_{\rm R}}\right) \,. \tag{1.3}$$

Equation (1.3) can be used to determine the maximum achievable pulse repetition frequency (PRF) of the generator. If the reverse-biasing voltage ends sooner than the charge is siphoned from the junction, the step transition cannot occur. Consequently, the generator will not produce an output. The equation is especially useful for simulations, since it allows for determining how to set the parameters of a model in order to match a real diode as specified by the manufacturer.

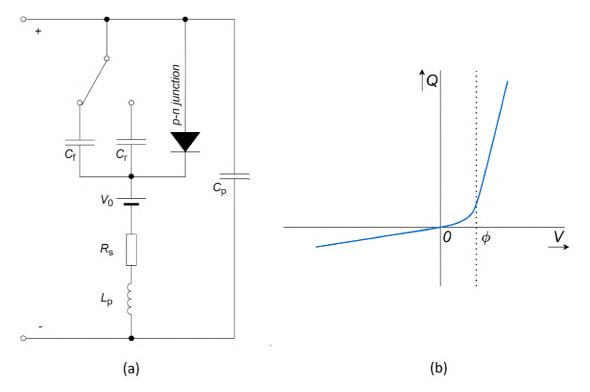

#### 1.1.1 Modeling SRD behavior for transient analysis

The SRD is a non-linear device. While this makes it useful in the applications mentioned above, it also has an effect on how accurately can its behavior be represented in a SPICE based transient simulation. Traditionally, designs involving the diodes have relied on the iteration of manufactured prototypes. This has led to the development of several different ways to model SRDs in a computer-friendly manner [12].