## **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

## **DEPARTMENT OF MICROELECTRONICS**

ÚSTAV MIKROELEKTRONIKY

# ANALYSIS AND DESIGN OF DECOUPLING CAPACITORS IN THE 65 NM CMOS DIGITAL STANDARD LIBRARY

ANALÝZA A NÁVRH BLOKOVACÍCH KONDENZÁTORŮ V DIGITÁLNÍ STANDARDNÍ KNIHOVNĚ TECHNOLOGIE CMOS 65 NM

#### **BACHELOR'S THESIS**

BAKALÁŘSKÁ PRÁCE

AUTHOR Radek Kučera

**AUTOR PRÁCE**

SUPERVISOR Ing. Vojtěch Král

**VEDOUCÍ PRÁCE**

**BRNO 2024**

## Bakalářská práce

bakalářský studijní program Mikroelektronika a technologie

Ústav mikroelektroniky

Student: Radek Kučera ID: 240855

Ročník: 3 Akademický rok: 2023/24

NÁZEV TÉMATU:

## Analýza a návrh blokovacích kondenzátorů v digitální standardní knihovně technologie CMOS 65 nm

#### POKYNY PRO VYPRACOVÁNÍ:

Seznamte se s digitálními standardními knihovnami v technologii CMOS 65 nm. Zvláště se zaměřte na blokovací kondenzátory v souvislosti s digitálně standardní knihovnou a jejich použitím na čipu. Vysvětlete účel a princip blokovacích kondenzátorů a charakterizujte jejich možné vlastnosti. Prozkoumejte různé topologie blokovacích kondenzátorů a navrhněte vlastní varianty, které následně porovnáte v jednoduché simulaci. Na základě těchto porovnání vyberte blokovací kondenzátory pro hlubší analýzu. Pro vybrané kondenzátory vytvořte layout a pomocí parazitní extrakce a detailní simulace zkoumejte jejich chování a vlastnosti. Prioritně se zaměřte na kapacitu vzhledem k ploše buňky, rychlost odezvy a s tím spojenou maximální frekvenci a svodový proud. Monitorujte tyto parametry v závislosti na teplotě, napětí a procesních variacích. Na závěr zhodnoťte všechny analyzované blokovací kondenzátory a doporučte nejvhodnější varianty pro začlenění do digitální standardní knihovny.

#### DOPORUČENÁ LITERATURA:

Podle pokynů vedoucího práce.

Termín zadání: 5.2.2024 Termín odevzdání: 30.5.2024

Vedoucí práce: Ing. Vojtěch Král

doc. Ing. Pavel Šteffan, Ph.D. předseda rady studijního programu

#### UPOZORNĚNÍ:

Autor bakalářské práce nesmí při vytváření bakalářské práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

## **Bachelor's Thesis**

#### Bachelor's study program Microelectronics and Technology

Department of Microelectronics

Student: Radek Kučera ID: 240855

Year of 3 Academic year: 2023/24 study:

TITLE OF THESIS:

## Analysis and design of decoupling capacitors in the 65 nm CMOS digital standard library

#### **INSTRUCTION:**

Familiarize yourself with digital standard libraries in 65 nm CMOS technology. Specifically, focus on decoupling capacitors in relation to the digital standard library and their application on chips. Explain the purpose and principle of decoupling capacitors and characterize their possible properties. Investigate various topologies of decoupling capacitors and propose your own variants, which you will then compare in a simple simulation. Based on these comparisons, select decoupling capacitors for deeper analysis. For the selected capacitors, create a layout and examine their behavior and properties using parasitic extraction and detailed simulation. Focus primarily on the capacitance relative to the cell area, response time, associated maximum frequency, and leakage current. Monitor these parameters depending on temperature, voltage, and process variations. Finally, evaluate all analyzed decoupling capacitors and recommend the most suitable variants for integration into a digital standard library.

#### **RECOMMENDED LITERATURE:**

Podle pokynů vedoucího práce.

, , , , ,

Date of project 5.2.2024 Specification: Deadline for 30.5.2024 submission:

Supervisor: Ing. Vojtěch Král

**doc. Ing. Pavel Šteffan, Ph.D.**Chair of study program board

#### WARNING:

The author of the Bachelor's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

#### **ABSTRACT**

This work deals with the design of decoupling capacitors in the form of CMOS transistors for stabilizing the supply voltage in a digital standard library, focusing on 65 nm technology. The introduction provides an overview of CMOS technology and a description of MOS structures. The analysis compares four topologies of decoupling capacitors (NMOS, PMOS, CMOS, Cross-Coupled) and identifies Cross-Coupled as the best choice. The last part focuses on the design and optimization of the layout of decoupling capacitors. Four different layouts were created, optimized for capacity, quality factor, leakage current, and a compromise between these factors, to be integrated into standard digital libraries according to specific applications.

#### **KEYWORDS**

CMOS, MOSFET, decoupling capacitors, leakage, noise, voltage drops, integrated circuit, digital standard cells, 65 nm technology

#### **ABSTRAKT**

Tato práce se zabývá návrhem blokovacích kondenzátorů ve formě CMOS tranzistorů pro stabilizaci napájecího napětí v digitální standardní knihovně se zaměřením na 65 nm technologii. Úvod poskytuje přehled CMOS technologie a popis MOS struktur. Analýza porovnává čtyři topologie blokovacích kondenzátorů (NMOS, PMOS, CMOS, Cross-Coupled) a identifikuje Cross-Coupled jako nejlepší volbu. Poslední část se zaměřuje na návrh a optimalizaci layoutu blokovacích kondenzátorů. Byly vytvořeny čtyři různé layouty, optimalizované pro kapacitu, činitel jakosti, svodový proud a kompromis mezi těmito faktory, aby mohly být integrovány do standardních digitálních knihoven podle specifických aplikací.

## KLÍČOVÁ SLOVA

CMOS, MOSFET, blokovací kondenzátor, šum, úbytky napětí, integrovaný obvod, digitálně standardní buňky, 65 nm technologie

Typeset by the thesis package, version 4.09; https://latex.fekt.vut.cz/

## ROZŠÍŘENÝ ABSTRAKT

Trh s polovodiči se neustále vyvíjí, tranzistory se zmenšují a integrované obvody jsou stále složitější. Tento pokrok umožňuje vytvářet zařízení, která jsou výkonnější a energeticky úspornější. Nicméně toto neustálé zmenšování CMOS technologií přináší nové výzvy, včetně problémů se svodovým proudem, udržováním konstantního napájecího napětí a šumem.

Tato bakalářská práce se zaměřuje na podrobnou analýzu a návrh blokovacích kondenzátorů v rámci technologie CMOS 65 nm (Complementary Metal Oxide Semiconductor), které jsou klíčovým prvkem pro potlačení rušení napájecího napětí na čipu a vykrytí výkonových špiček. Úvodní část práce je věnována technologii CMOS, kde jsou vysvětleny základní principy. Je zde uveden podrobný popis tranzistoru MOSFET (Metal Oxide Semiconductor Field-Effect Transistor), který je nezbytný pro pochopení funkce blokovacích kondenzátorů v této technologii. Tato část se rovněž zaměřuje na kapacity spojené s tranzistory MOSFET a stručně se zabývá různými typy svodových proudů.

Následně je představen koncept digitálních standardních buněk, jejich význam v procesu návrhu čipů a typické složení. V práci je rozebrána problematika fyzického návrhu těchto buněk a diskutována omezení, která mohou při návrhu nastat.

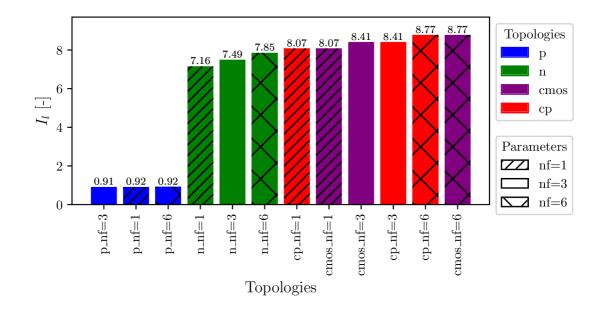

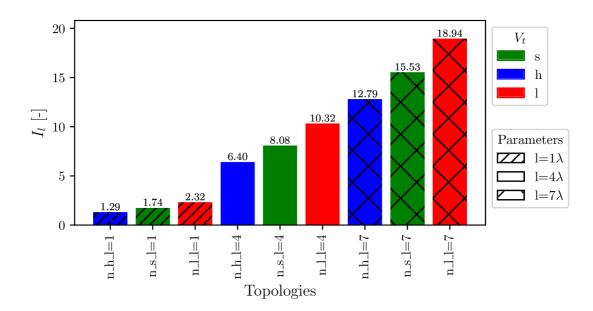

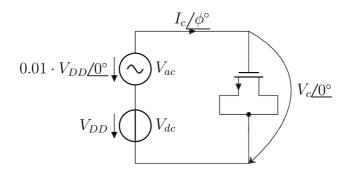

Hlavní část práce se soustředí na analýzu čtyř různých topologií blokovacích kondenzátorů (NMOS, PMOS, CMOS a Cross-Coupled). Byly sledovány změny klíčových parametrů (činitel jakosti Q, efektivní odpor  $R_{ef}$ , efektivní kapacita  $C_{ef}$  a svodový proud  $I_l$ ) v závislosti na změně základních charakteristik tranzistorů (šířka W, délka L a počet hřebínků NF). Pro simulaci těchto parametrů byl navržen obvod a byly stanoveny vztahy pro jejich výpočet. Na tyto simulace byly použity pouze netlisty ze schématu, tudíž bez parazitních prvků. K simulacím byly vytvořeny skripty v jazyce Python, které umožnily automatizaci tohoto procesu. Výsledky simulací byly normalizovány z důvodu podepsaného NDA (Non Disclosure Agreement) ohledně technologie 65 nm.

Z výsledků simulací vyplývá, že PMOS topologie vykazuje nejnižší svodový proud a dosahuje nejvyššího činitele jakosti, i když její kapacita je menší ve srovnání s NMOS topologií o stejné ploše. U NMOS topologie činitel jakosti dosahuje nejvyšších hodnot při vyšších frekvencích. CMOS topologie kombinuje vlastnosti NMOS a PMOS a nabízí vyvážené vlastnosti. Cross-Coupled topologie má shodnou kapacitu a svodový proud s CMOS, ale dosahuje nejhorších hodnot činitele jakosti. Z analýzy také vyplynulo, že s rostoucími parametry délky a šířky klesá činitel jakosti a frekvence při které dosahuje maxima. Naopak, zvyšování počtu hřebínků vedlo k vyššímu činiteli jakosti a frekvenci jeho maxima, ale mělo minimální vliv na kapacitu a svodový proud. Nižší prahové napětí zlepšilo frekvenci maxima činitele jakosti, ale zvýšilo svodový proud.

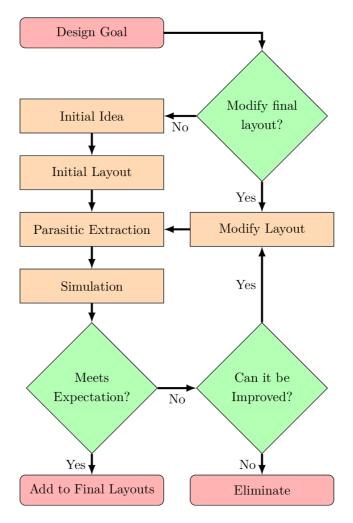

V závěrečné části práce byla pro podrobnou analýzu vybrána Cross-Coupled topologie. Byla vybrána primárně kvůli svým výrazně lepším ESD (Electrostatic Discharge) vlastnostem ve srovnání s ostatními topologiemi a také, že dosahuje stejných hodnot kapacity a svodového proudu jako CMOS topologie. Ostatní topologie mají připojené napájecí napětí přímo na hradle, což je v technologii 65 nm nebezpečné kvůli nízkému průraznému napětí oxidu křemíku. Cílem bylo vytvoření čtyř layoutů v digitálně standardní buňce, z nichž se každý zaměřoval na optimalizaci určitých parametrů, konkrétně kapacity, činitele jakosti, svodového proudu a jeden zaměřený na vyvážení těchto tří parametrů. Tyto layouty byly vytvářeny iterativně, počínaje počátečními návrhy, které byly postupně upravovány na základě zjištění ze simulací s parazitní extrakcí z layoutu v kombinaci se zjištěními z jednoduchých simulací z netlistu. V průběhu bylo navrženo více než šedesát různých variant. Výsledky simulací byly opět normalizovány.

Byly navrženy různé layouty buněk, které by mohly být integrovány do digitálních standardních knihoven na základě jejich specifických aplikací. Například buňka navržená pro minimalizaci svodového proudu by vyhovovala knihovně zaměřené na použití v aplikacích s nízkou spotřebou energie, kde je minimalizace ztráty energie prioritou. Dále by buňka optimalizovaná pro činitel jakosti byla přínosná v knihovnách vyžadujících vysoké spínací rychlosti a nízké rušení spojené s vysokými spínacími frekvencemi. Navíc by univerzálně optimalizovaná buňka byla ideální pro knihovnu, která se snaží optimalizovat různé parametry, jako je rychlost, plocha a svodový proud. Kromě toho by buňka optimalizovaná pro kapacitu vzhledem k ploše mohla být zahrnuta do všech knihoven a použita v případě potřeby zvýšení kapacity bez zvětšení plochy. Nakonec je možné přidat všechny tyto buňky do jedné knihovny, což umožní návrháři vybrat vhodnou buňku na základě konkrétní aplikace.

V pracích navazujících na tuto analýzu by bylo možné provést více simulací modelujících realističtější aplikace těchto buněk. Například by bylo možné prozkoumat, jak se chování navržených buněk mění, když jsou obklopeny jinými buňkami s různými funkcemi nebo vyššími kovovými vrstvami. Nakonec by jejich chování mohlo být fyzicky ověřeno, pokud by byly vyrobeny na testovacím čipu a simulované výsledky by mohly být porovnány se skutečným chováním. Případně by bylo možné použít tyto buňky v již vyráběném návrhu, který by se vyrobil na testovacím čipu, a následně by se tyto dvě implementace mohly fyzicky porovnat.

## **Author's Declaration**

| Author:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Radek Kučera                                                                                                                                                   |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Author's ID:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 240855                                                                                                                                                         |  |  |

| Paper type:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bachelor's Thesis                                                                                                                                              |  |  |

| Academic year:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2023/24                                                                                                                                                        |  |  |

| Topic:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Analysis and design of decoupling capacitors in the 65 nm CMOS digital standard library                                                                        |  |  |

| and using exclusively the technical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | paper independently, under the guidance of the advisor all references and other sources of information cited in ehensive bibliography at the end of the paper. |  |  |

| As the author, I furthermore declare that, with respect to the creation of this paper, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation § 11 of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll. of the Czech Republic, Section 2, Head VI, Part 4. |                                                                                                                                                                |  |  |

| Brno                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>author's signature*                                                                                                                                        |  |  |

<sup>\*</sup>The author signs only in the printed version.

## **ACKNOWLEDGEMENT**

I would like to express my gratitude to my thesis supervisor, Ing. Vojtěch Král, for his valuable advice and invaluable assistance in writing this thesis. I would also like to thank Ing. Jiří Šolc, whose support allowed me to work on this project. My thanks also go to all my colleagues who provided me with advice and inspiration.

Furthermore, I would like to thank my family and friends for their constant support throughout my studies. Last but not least, I would like to thank my classmates for the joint projects and mutual support that greatly helped me during my studies.

## **Contents**

| In       | trod                   | uction                                             | 17   |

|----------|------------------------|----------------------------------------------------|------|

| 1        | $\mathbf{C}\mathbf{M}$ | os                                                 | 18   |

|          | 1.1                    | Technology Nodes                                   | . 19 |

|          | 1.2                    | Principle of CMOS                                  | . 20 |

|          |                        | 1.2.1 Inverter                                     | . 21 |

|          | 1.3                    | MOSFET                                             | . 22 |

|          |                        | 1.3.1 Layout                                       | . 23 |

|          |                        | 1.3.2 Capacitance                                  | . 24 |

|          |                        | 1.3.3 Leakage                                      | . 28 |

| <b>2</b> | Sta                    | ndard Cells                                        | 29   |

|          | 2.1                    | Physical View                                      | . 30 |

|          |                        | 2.1.1 Symbol View                                  | . 30 |

|          |                        | 2.1.2 Schematic View                               |      |

|          |                        | 2.1.3 Layout View                                  | . 31 |

| 3        | Dec                    | coupling Capacitors                                | 32   |

|          | 3.1                    | Power Supply Noise                                 | . 32 |

|          | 3.2                    | Power Supply Decoupling                            |      |

|          |                        | 3.2.1 Topologies                                   | . 34 |

|          | 3.3                    | Simulation                                         | 36   |

|          |                        | 3.3.1 Simulation Methodology                       | 38   |

|          | 3.4                    | Simulation Results                                 | 40   |

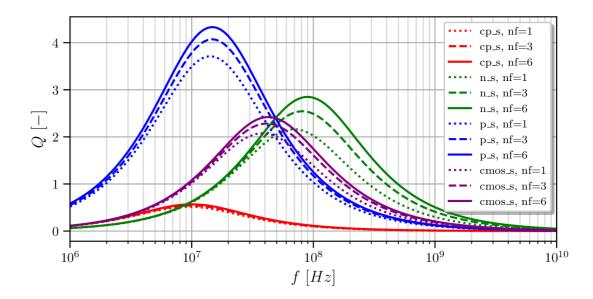

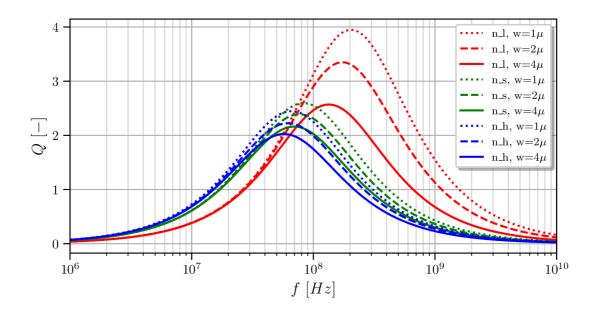

|          |                        | 3.4.1 Quality Factor                               | 40   |

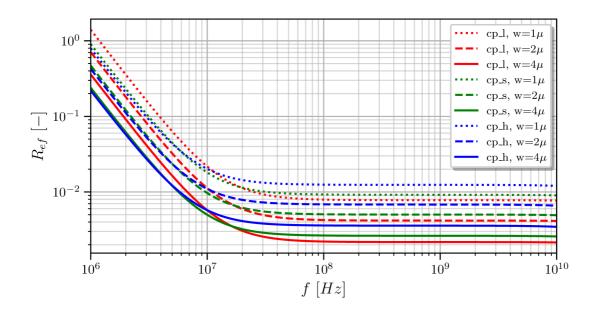

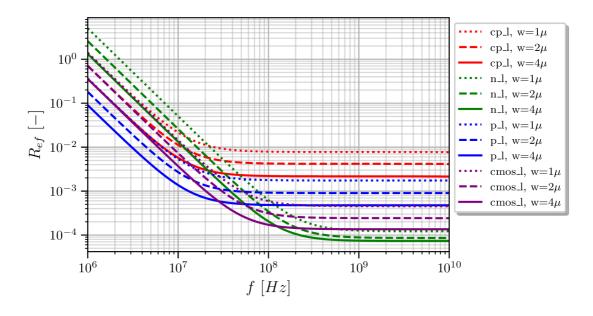

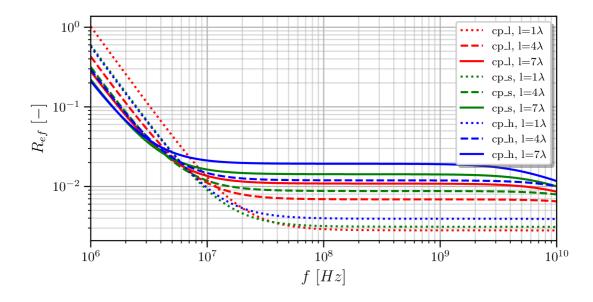

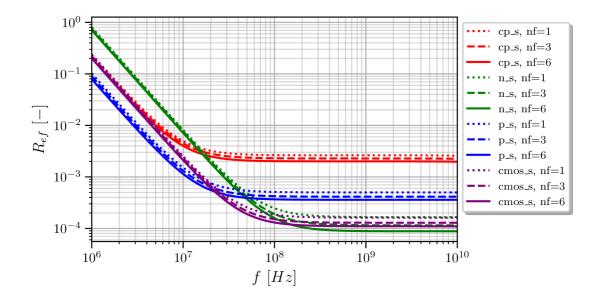

|          |                        | 3.4.2 Effective Resistance                         | 44   |

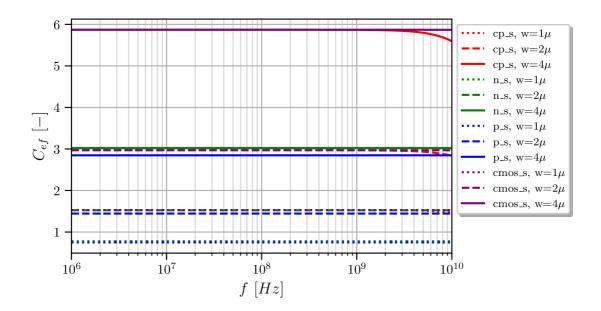

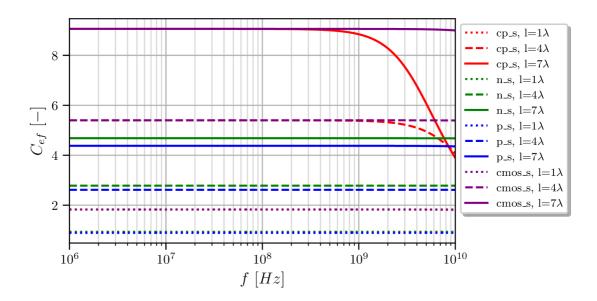

|          |                        | 3.4.3 Effective Capacitance                        | 46   |

|          |                        | 3.4.4 Leakage                                      | 49   |

| 4        | Ana                    | alysis of Selected Decoupling Capacitor Topologies | 53   |

|          | 4.1                    | Simulation                                         | 53   |

|          |                        | 4.1.1 Simulation Methodology                       | 55   |

|          | 4.2                    | Iterative Layout Design                            | 56   |

|          | 4.3                    | Final Layouts                                      | 57   |

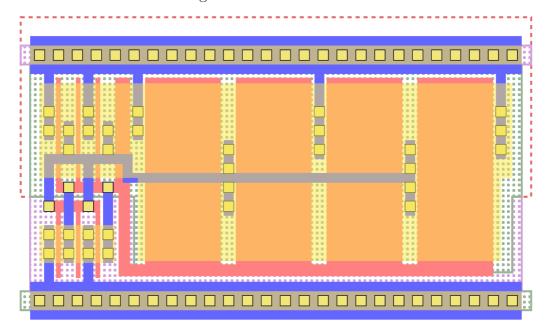

|          |                        | 4.3.1 Optimized for Capacity                       |      |

|          |                        | 4.3.2 Optimized for Leakage                        | 61   |

|          |                        | 4.3.3 Optimized for Quality Factor                 | 61   |

|          |                        | 4.3.4 Balanced Optimization                        | 63   |

| Co                     | onclu | sion                        | 68 |

|------------------------|-------|-----------------------------|----|

| $\mathbf{Bi}$          | bliog | raphy                       | 70 |

| $\mathbf{S}\mathbf{y}$ | mbo   | ls and abbreviations        | 72 |

| Li                     | st of | appendices                  | 73 |

| $\mathbf{A}$           | Spe   | ctre                        | 74 |

|                        | A.1   | Spectre netlist             | 74 |

|                        | A.2   | Spectre MDL                 | 76 |

|                        | A.3   | Topology subcircuits        | 79 |

|                        | A.4   | PVT definitions             | 80 |

| В                      | Pyt   | hon scripts                 | 82 |

|                        | B.1   | Data normalization          | 82 |

|                        | B.2   | All topology simulation run | 83 |

## List of Figures

| 1.1  | Moore's law: The number of transistors per microprocessor [6]                    | 18 |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | CMOS: Cross-sectional view and transistor symbols                                | 20 |

| 1.3  | Schematic diagram (A), symbol (B) and truth table (C) of the CMOS                |    |

|      | inveter                                                                          | 22 |

| 1.4  | Layout of a NMOS and its cross-section                                           | 23 |

| 1.5  | CMOS: Cross-sectional view and transistor symbols                                | 25 |

| 1.6  | MOS capacitance-voltage curves (A) low frequency, (B) high fre-                  |    |

|      | quency [3]                                                                       | 26 |

| 1.7  | Comparison of capacitance and series resistance with transistor in               |    |

|      | accumulation (left) and in inversion (right)                                     | 27 |

| 1.8  | MOSFET capacitances [3]                                                          | 27 |

| 2.1  | Symbol view of an inverter (A), NAND (B) and NOR (C)                             | 30 |

| 2.2  | Schematic view of a NAND (A) and NOR (B)                                         | 30 |

| 2.3  | Standard cell template                                                           | 31 |

| 3.1  | Power delivery system, with non-ideal interconnection lines [16]                 | 33 |

| 3.2  | CMOS decoupling capacitors topologies: (A), NMOS (B), PMOS (C),                  |    |

|      | CMOS and (D) Cross-Coupled                                                       | 35 |

| 3.3  | NMOS modeled as lumped RC circuit                                                | 36 |

| 3.4  | Circuit for simulation of selected parameters                                    | 37 |

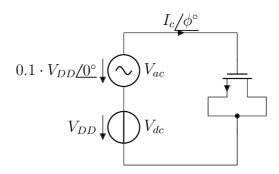

| 3.5  | Effect of width variation on the quality factor for all topologies at            |    |

|      | standard threshold voltage and at a constant length $l{=}2\lambda$ and number    |    |

|      | of fingers $nf=1$                                                                | 41 |

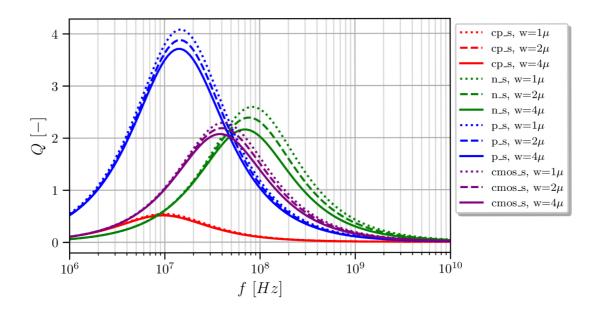

| 3.6  | Effect of length variation on the quality factor for all topologies at           |    |

|      | standard threshold voltage and at a constant width w=2 $\mu$ and number          |    |

|      | of fingers nf=1                                                                  | 41 |

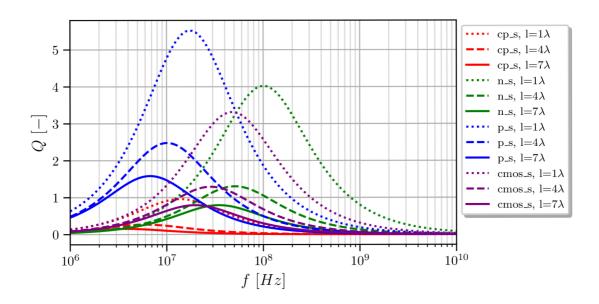

| 3.7  | Effect of changing the number of fingers on the quality factor for               |    |

|      | all topologies at standard threshold voltage and at a constant length            |    |

|      | $l=7\lambda$ and width $w=2\mu$                                                  | 42 |

| 3.8  | Effect of width variation on the quality factor for NMOS topology                |    |

|      | with all threshold voltages and at a constant length $l=2\lambda$ and number     |    |

|      | of fingers nf=1                                                                  | 43 |

| 3.9  | Effect of width variation on resistance for cross-coupled topology with          |    |

|      | all threshold voltages and at a constant length $l=2\lambda$ and number of       |    |

|      | fingers nf=1                                                                     | 45 |

| 3.10 | Effect of width variation on resistance for all topologies at low thresh-        |    |

|      | old voltage and at a constant length $l=2\lambda$ and number of fingers $nf=1$ . | 45 |

| 3.11         | Effect of length variation on resistance for cross-coupled topology with                                                                                                                              |     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | all threshold voltages and at a constant width $w=2\mu$ and number of                                                                                                                                 | 4.0 |

| 0.10         | fingers nf=1                                                                                                                                                                                          | 46  |

| 3.12         | Effect of changing the number of fingers on resistance for all topologies                                                                                                                             |     |

|              | at standard threshold voltage and at a constant length $l=7\lambda$ and                                                                                                                               | 47  |

| 9 19         | width $w=2\mu$                                                                                                                                                                                        | 47  |

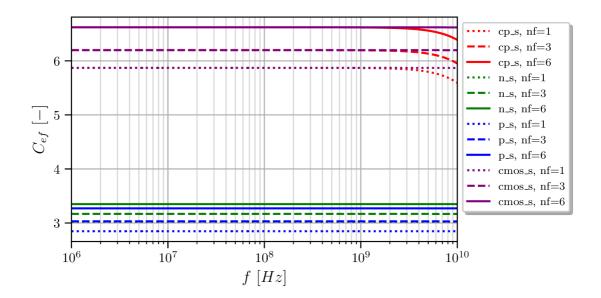

| 3.13         |                                                                                                                                                                                                       |     |

|              | threshold voltage and at a constant length $l=2\lambda$ and number of fingers $nf=1$                                                                                                                  | 48  |

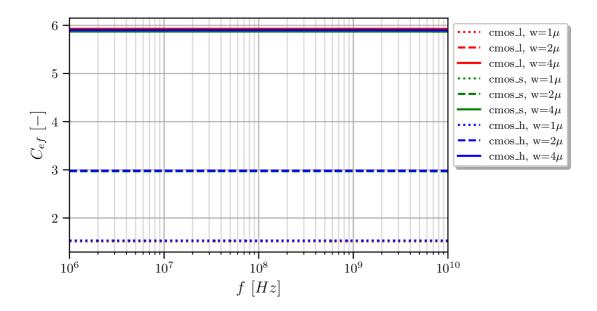

| 2 1 <i>1</i> | Effect of length variation on capacity for all topologies at standard                                                                                                                                 | 40  |

| 0.14         | threshold voltage and at a constant width $w=2\mu$ and number of fin-                                                                                                                                 |     |

|              | gers $nf=1$                                                                                                                                                                                           | 48  |

| 3 15         | Effect of changing the number of fingers on capacity for all topologies                                                                                                                               | 40  |

| 0.10         | at standard threshold voltage and at a constant length $l=7\lambda$ and                                                                                                                               |     |

|              | width $w=2\mu$                                                                                                                                                                                        | 49  |

| 3.16         | Effect of width variation on capacity for CMOS topology with all                                                                                                                                      |     |

|              | threshold voltages and at a constant length $l=2\lambda$ and number of fin-                                                                                                                           |     |

|              | gers nf=1                                                                                                                                                                                             | 49  |

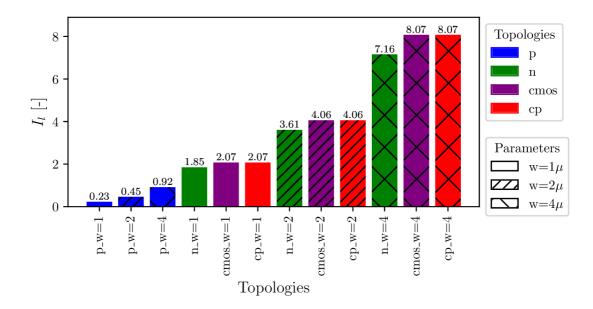

| 3.17         | Effect of width variation on leakage for all topologies at standard                                                                                                                                   |     |

|              | threshold voltage and at a constant length $l=2\lambda$ and number of fingers                                                                                                                         |     |

|              | nf=1                                                                                                                                                                                                  | 50  |

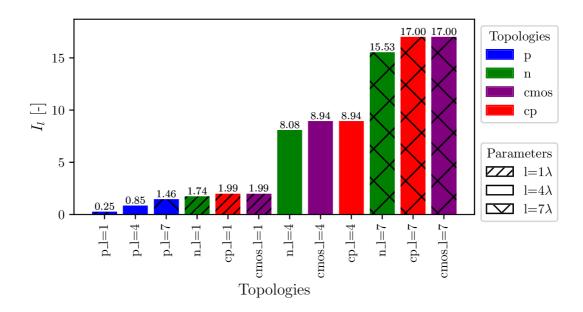

| 3.18         | Effect of length variation on leakage for all topologies at standard                                                                                                                                  |     |

|              | threshold voltage and at a constant width $w=2\mu$ and number of fin-                                                                                                                                 |     |

|              | $gers\ nf{=}1.\ \dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ | 50  |

| 3.19         | Effect of changing the number of fingers on leakage for all topologies                                                                                                                                |     |

|              | at standard threshold voltage and at a constant length l=2 $\lambda$ and                                                                                                                              |     |

|              | width $w=4\mu$                                                                                                                                                                                        | 51  |

| 3.20         | Effect of length variation on leakage for NMOS topology with all                                                                                                                                      |     |

|              | threshold voltages and at a constant width $w=2\mu$ and number of                                                                                                                                     |     |

|              | fingers $nf=1$                                                                                                                                                                                        | 52  |

| 4.1          | Circuit for simulation of selected parameters                                                                                                                                                         | 54  |

| 4.2          | Methodology for iterative layout design                                                                                                                                                               | 57  |

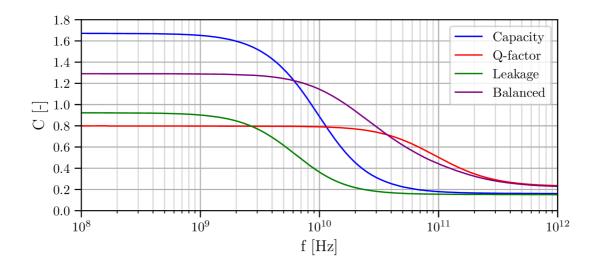

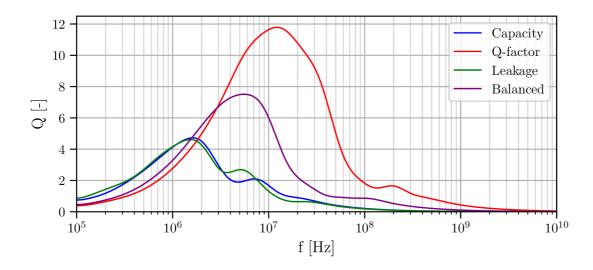

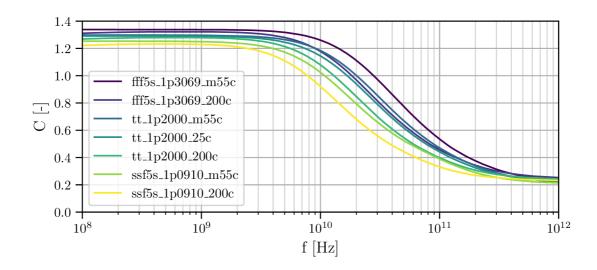

| 4.3          | Trend of capacity as a function of frequency for all layouts                                                                                                                                          | 59  |

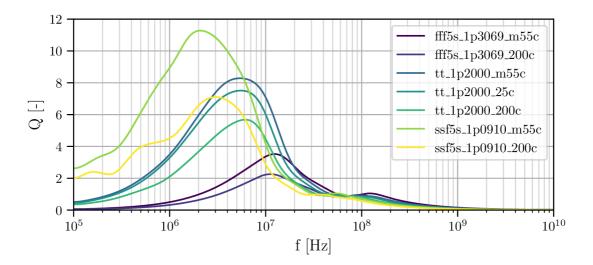

| 4.4          | Trend of quality factor as a function of frequency for all layouts                                                                                                                                    | 59  |

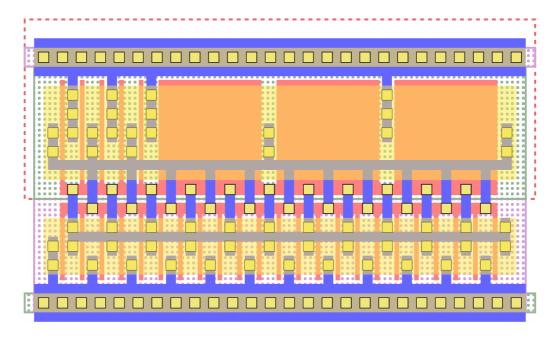

| 4.5          | Layout optimized for capacity                                                                                                                                                                         | 60  |

| 4.6          | Dependency of capacity on frequency for a layout optimized for ca-                                                                                                                                    |     |

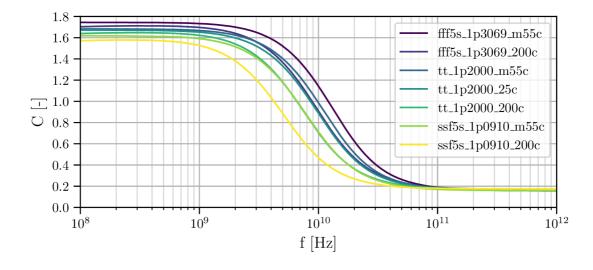

|              | pacity, under various PVT conditions                                                                                                                                                                  | 60  |

| 4.7          | Layout optimized for leakage                                                                                                                                                                          | 62  |

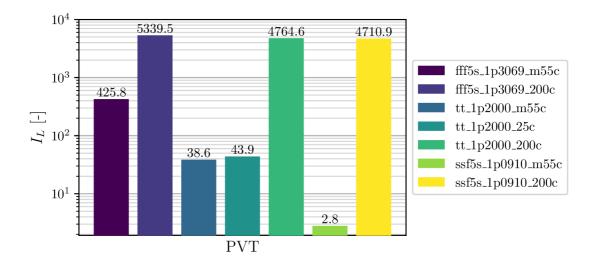

| 4.8  | Leakage for a layout optimized for leakage, under various PVT con-   |    |

|------|----------------------------------------------------------------------|----|

|      | ditions                                                              | 62 |

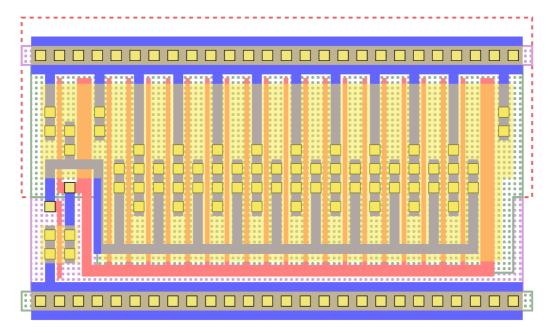

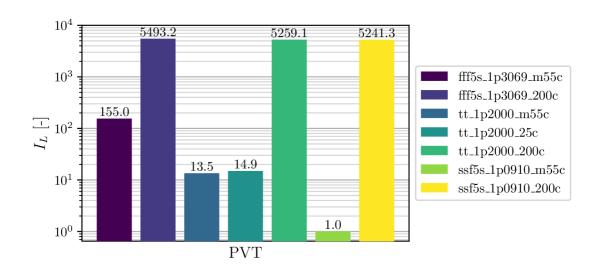

| 4.9  | Layout optimized for quality factor                                  | 63 |

| 4.10 | Dependency of quality factor on frequency for a layout optimized for |    |

|      | quality factor, under various PVT conditions                         | 64 |

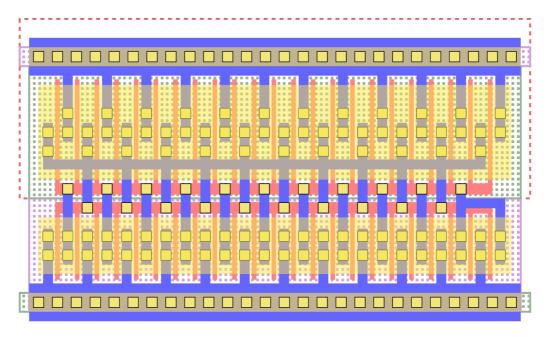

| 4.11 | Layout optimized for balance between capacity, quality factor, and   |    |

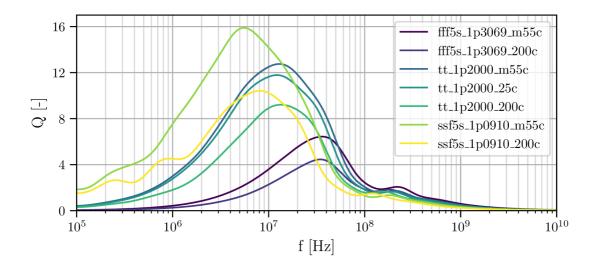

|      | leakage                                                              | 65 |

| 4.12 | Dependency of quality factor on frequency for a layout optimized for |    |

|      | balance, under various PVT conditions                                | 65 |

| 4.13 | Dependency of capacity on frequency for a layout optimized for bal-  |    |

|      | ance, under various PVT conditions                                   | 66 |

| 4.14 | The effect of different PVTs on the leakage of the layout optimized  |    |

|      | for balance                                                          | 66 |

## **List of Tables**

| 2.1 | List of common cells in the digital standard cell library [13]                    | 29 |

|-----|-----------------------------------------------------------------------------------|----|

| 3.1 | Threshold voltage and topology labeling                                           | 35 |

| 3.2 | Maximal observed values for Cross-Coupled topology with l=1 $\lambda$ , w=1 $\mu$ |    |

|     | and nf=1 after the normalization                                                  | 39 |

| 3.3 | Maximal quality factor values for NMOS topology corresponding to                  |    |

|     | the data presented in Figure 3.7                                                  | 42 |

| 3.4 | Effect of threshold voltage variation on the $f_{Qmax}$ and $Q$ for PMOS          |    |

|     | topology at a constant length $l=2\lambda$ , width $w=2\mu$ , and number of       |    |

|     | fingers $nf=1$                                                                    | 43 |

| 3.5 | Effect of length variation on the maximal values of quality factor for            |    |

|     | PMOS topology with all threshold voltages and at a constant width                 |    |

|     | $w=2\mu$ and number of fingers $nf=1$                                             | 44 |

| 4.1 | List of PVTs used in the simulation                                               | 54 |

| 4.2 | Results of Simulations for Selected Layouts                                       | 58 |

| 4.3 | The effect of different PVTs on the capacity of the layout optimized              |    |

|     | for capacity                                                                      | 61 |

| 4.4 | The effect of different PVTs on the leakage of the layout optimized               |    |

|     | for leakage                                                                       | 63 |

| 4.5 | The effect of different PVTs on the quality factor of the layout opti-            |    |

|     | mized for quality factor                                                          | 64 |

| 4.6 | The effect of different PVTs on the monitored parameters of the layout            |    |

|     | optimized for balance (fist part)                                                 | 67 |

| 4.7 | The effect of different PVTs on the monitored parameters of the layout            |    |

|     | optimized for balance (second part)                                               | 67 |

## Listings

| 3.1 | Example of a Spectre netlist used for simulations with subcircuit ex-      |    |

|-----|----------------------------------------------------------------------------|----|

|     | ample                                                                      | 38 |

| 3.2 | Example MDL script for parameter sweep in Spectre simulations              | 39 |

| 4.1 | Example of a Spectre netlist used for simulations                          | 55 |

| 4.2 | Eample of MDL scrip used for simulations                                   | 56 |

| A.1 | Spectre netlist used for simulations                                       | 74 |

| A.2 | Spectre netlist used for layout simulation with parasitic extraction. $$ . | 74 |

| A.3 | MDL script for parameter sweep in Spectre simulations                      | 76 |

| A.4 | MDL script for layout simulation with parasitic extraction                 | 76 |

| A.5 | Spectre subcircuits used for simulations                                   | 79 |

| A.6 | PVT definitions for the MDL script                                         | 80 |

| B.1 | Script for data normalization                                              | 82 |

| B.2 | Script for running Spectre for each topology                               | 83 |

## Introduction

The semiconductor market is constantly evolving, transistors are getting smaller and integrated circuits are getting more complex. These advances are making it possible to create devices that are both more powerful and more energy-efficient. However this continual shrinking poses challenges, including problems with leakage current, noise and the complexity of heat management.

The focus of this work will primarily be on addressing issues related to noise and, to a lesser extent, leakage. A key aspect of this work is the investigation of decoupling capacitors in 65 nm technology within digital standard cells. Decoupling capacitors, which can occupy up to 20 % of the chip area [1], play a crucial role in noise mitigation. Because of this large area, care must be taken to ensure that leakage is considered when designing these decoupling capacitors.

The initial part of the work is dedicated to CMOS (Complementary Metal Oxide Semiconductor) technology, where the fundamental principles and operations are explained. A detailed description of the MOSFET (Metal Oxide Semiconductor Field-Effect Transistor) transistor, essential for understanding the function of decoupling capacitors in this technology, is provided. This section is focused on the capacitances associated with MOSFET transistors and briefly discuss various types of leakage currents.

The next section describes digital standard digital cells and introduces how the complexity of digital circuit design is currently handled. All the important views for understanding circuit design and layout are also explained there.

In the preceding section, various topologies of decoupling capacitors that can be implemented in standard cells are introduced, along with a description of their basic properties. The specific parameters of these capacitors, crucial for assessment and evaluation, are clearly defined and outlined. A circuit for the simulations are designed to monitor these parameters, and the methodology for performing the simulations will be described. Finally, the results are evaluated.

In the final part, based on the results from the preceding sections, one topology is selected for deeper analysis. For this chosen topology, four layouts are created, each optimized for capacity, quality factor, leakage, and one balanced between these three parameters. These layouts are designed within the context of a digital standard cell. The design process is iterative, incorporating insights gained from initial simulations. The methodology for both design and simulation is thoroughly described.

## 1 CMOS

In 1958, Jack Kilby built the first integrated circuit with two transistors [2]. Just a few years later in 1963 Frank Wanlass invented CMOS (Complementary Metal Oxide Semiconductor) while he was working for Fairchild Semiconductor [3]. CMOS slowly became the favored choice over bipolar transistors because of its low power consumption, speed, greater noise immunity, and smaller on-chip area. This technological change has enabled the rapid development of integrated circuits.

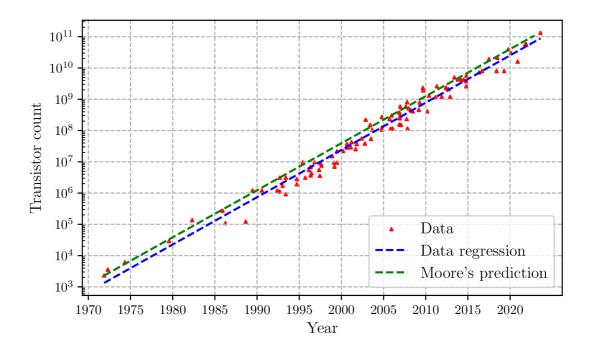

Now Apple's latest M2 Ultra processor contains 134 billion transistors [4]. That's a 47% annual growth in the number of transistors over the last 65 years. This exponential growth was predicted by Gordon Moore in 1965 when he noticed that the number of transistors was doubling every year. This growth was adjusted to doubling every 2 years in 1975. This prediction is called Moore's law and is still valid to this day [5]. In Figure 1.1 the green line indicates Moore's prediction, which was calculated by doubling the first data point every two years, while the blue line is a regression of the actual transistor counts. Such exponential growth is possible only because of the CMOS scalability.

Figure 1.1: Moore's law: The number of transistors per microprocessor [6].

## 1.1 Technology Nodes

A technology node refers to a specific generation of chip manufacturing technology. The progression from one technology node to the next meant a reduction in the physical dimensions of the transistor. This meant higher performance, lower power consumption, and more efficient use of space, it also introduces several challenges. As transistors become smaller, issues like increased leakage current, susceptibility to electronic noise, and thermal management problems become more pronounced.

The technology node originally referred to a specific physical dimension in a chip design, namely the length of a transistor, measured first in micrometers (µm) and later in nanometers (nm). When the 32 nm node was reached around 2009, the term "technology node" started being used more for marketing than for precise technical measurement [7]. However, the trend of scaling down transistors in nanometer terms remained, though not directly linked to gate length. This shift meant smaller, yet not precisely defined, transistor sizes that continued to improve chip performance and efficiency.

This work will be focused on 65 nm node technology. At this specific node technology, transistors with three different threshold voltages (low, standard, and high) are available. Different threshold voltages can be used to optimize between performance or power consumption. Additionally, in static timing analysis (STA), different threshold voltages are employed to meet timing constraints. In this technology, silicon oxide is used as the gate dielectric. With this material, at this scale, challenges arise, specifically quantum mechanical effects become noticeable.

## 1.2 Principle of CMOS

The CMOS technology utilizes a pair of transistors to implement logic functions. These transistors are of two types: n-type (NMOS) and p-type (PMOS) MOSFETs (Metal Oxide Semiconductor Field-Effect Transistor). For example, the full name is NMOSFET, but it is often shortened to NMOS. MOSFET is a four-pin component consisting of the source, drain, gate, and bulk terminals. CMOS circuits are fabricated through multiple layers both inside and on the surface of a single silicon wafer, in this case, a p-type wafer. This wafer is then doped with donor or acceptor impurities, to form n-type regions and p-type regions, respectively. In manufacturing, NMOS transistors are fabricated directly on the substrate, and PMOS transistors are fabricated in the n-well. N-well is formed by diffusion of donors into the substrate [2, 3].

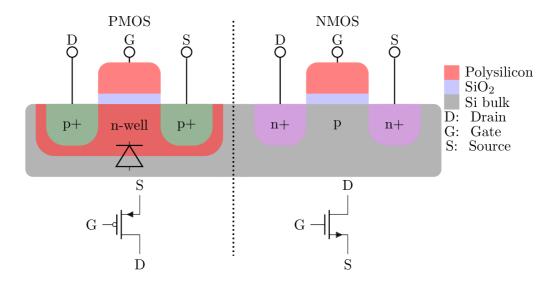

In Figure 1.2 the cross-sectional view of the CMOS pair can be seen. On the left side is PMOS, and on the right side is NMOS, with the corresponding schematic symbol below them. PMOS is formed in the n-well, and the drain and source are formed by p+ diffusion regions, where the "+" indicates they are heavily doped. The NMOS transistor is formed directly on the substrate, with the drain and source formed by n+ diffusion. It is important to mention that the drain and source are interchangeable because the transistor is symmetric. The gate is directly connected to a polysilicon. Polysilicon is a form of silicon made from small crystals and serves as a conductive layer. Between the substrate and this polysilicon there is a really thin layer of SiO<sub>2</sub>, which is called gate oxide. The substrate or n-well is also called the body or bulk of the MOSFET. The colors used to describe the different parts in this Figure 1.2, are going to be same throughout this work.

Figure 1.2: CMOS: Cross-sectional view and transistor symbols

The boundary between the n-well and the p-substrate together forms a PN junction that acts as a diode. This diode is illustrated in Figure 1.2. The area of this boundary is quite large, therefore, the p-substrate is usually connected to the lowest potential and the n-well to the highest potential in the circuit, so that the diode is reverse biased. MOSFET is a four-pin component, and the fourth pin is already mentioned bulk, and since in this case it is connected to the lowest potential or the highest potential, it is not shown in the schematic symbols. In this work, the lowest potential will be referred to as  $V_{SS}$ , which represents the logical zero, and the highest potential will be called  $V_{DD}$ , represents the logical one.

The main principle of CMOS is the use of complementary pairs to implement logic functions. Complementary means that NMOS and PMOS transistors are used together, where the NMOS passes a strong logic zero and the PMOS passes a strong logic one, unlike other logic families. Passing strong logic zero or one means that the output voltage is almost  $V_{SS}$  or  $V_{DD}$  [2]. Importantly, only one of these two transistors is open at a time, which means that there are practically no static power losses, and the only power loss is during the switching phase. Compared to bipolar transistors, which are current-controlled, CMOS is voltage-controlled, which further reduces static losses.

Many combinational logic gates, such as inverter (NOT), AND, OR, NAND, and others, as well as sequential circuits like the D flip-flop, can be created through the right combination of complementary pairs. More of these functions will be explored in Chapter 2. The principle of operation for these gates, starting with the simplest one, the inverter (NOT), can be explained to facilitate understanding.

#### 1.2.1 Inverter

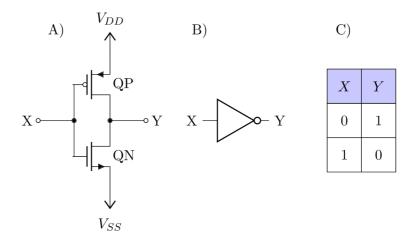

An inverter is a circuit that outputs inverse of its input logic value. In Figure 1.3(A), the schematic of the inverter is shown, where 'X' is the input that is connected to the gates of the transistors and 'Y' is output. The transistors labeled QP and QN are PMOS and NMOS respectively.

Before the operation of the inverter is explained, it is necessary to clarify the basic operation of a transistor. For the purposes of the initial explanation, the transistor can be thought of as a switch that is controlled by a voltage on the gate which determines whether the switch is 'on' or 'off.' For a PMOS transistor, a logic one turns it 'off', while for an NMOS, a logic one turns it 'on'.

Figure 1.3: Schematic diagram (A), symbol (B) and truth table (C) of the CMOS inveter.

The operation of the inverter is such that when voltage  $V_{DD}$  is applied to an input (X), the transistor QP turns off (closes) and QN turns on (opens), thus connecting  $V_{SS}$  to output (Y). When voltage  $V_{SS}$  is applied to an input (X) transistor, QP turns on (opens) and QN turns of (closes), thus connecting  $V_{DD}$  to output (Y). If voltage  $V_{DD}$  and  $V_{SS}$  represents logical one and zero, respectively, then this circuit performs logical inversion.

## 1.3 MOSFET

MOSFET is a majority-carrier device; for NMOS, the majority carriers of electric charge are electrons, and for PMOS, the major carriers are holes. It is important to note that, when NMOS and PMOS transistors are the same size, NMOS is faster than PMOS because the electron mobility is approximately three times higher than the hole mobility. When a voltage is applied between the source and gate, the magnitude of the current flowing through the channel can be controlled by applying voltage to the gate. The channel is the area between the drain and the source. Beyond a certain voltage level on the gate, this channel becomes conductive, and the transistor starts to open. This voltage is called the threshold voltage. As mentioned in Section 1.1 the 65 nm technology used in this work allows the use of transistors with three different threshold voltages (low, standard, and high).

The dimensions of a transistor channel are usually described by two parameters: width and length. Another important parameter is the number of fingers. Number of fingers means that a single transistor is split into multiple parallel transistors with the same channel length, but their widths are divided by the number of fingers.

### 1.3.1 **Layout**

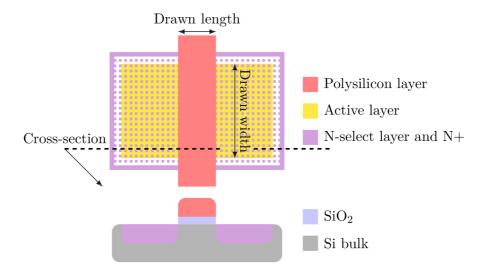

Before proceeding further, it is important that the method of creating a NMOS transistor in the layout design environment is explained, so that several frequently mentioned parameters are understood. In this section, many aspects, especially the production process, will be simplified as they are not essential for this work. Figure 1.4 illustrates a transistor in its drawn form, showing the active layer that outlines an opening in the silicon oxide. This opening indicates the physical location of the transistor. The n-select layer, in conjunction with the active layer, defines where the silicon is going to be doped with n-type donors. During the fabrication process, polysilicon is first laid down, and then the region outlined by the active layer is exposed and doped with donors, resulting in the formation of an NMOS transistor. This is illustrated in the cross-section below the drawn layers in Figure 1.4. Additionally, the drawn length and width, as seen in the figure, will slightly differ in the fabricated transistor, due to manufacturing variabilities.

Figure 1.4: Layout of a NMOS and its cross-section

### 1.3.2 Capacitance

#### **Capacitor**

Capacitance is the ability of an object to store an electrical charge. The basic component that has capacitance is the capacitor. In its basic form, a capacitor are two conductive plates close together separated by an insulator (dielectric). Assuming there is a charge Q and -Q on the plates and a voltage V between them, then the capacitance is given by:

$$C = \frac{Q}{V} \quad [F] \tag{1.1}$$

where C is the capacitance in farads (F), Q is charge in coulombs (C), and V is voltage in volts (V). The capacitance of a capacitor can also be calculated from the physical dimensions by this equation:

$$C = \epsilon_0 \cdot \epsilon_r \cdot \frac{A}{d} \quad [F] \tag{1.2}$$

where  $\epsilon_0$  is the permittivity of the vacuum,  $\epsilon_r$  is the relative permittivity of the insulating material between the two plates. The A is area and d is the distance of the two plates.

#### **MOS Capacitor**

Looking again at Figure 1.2, it can be seen that the polysilicon and substrate is separated by an  $SiO_2$ . Which are two conducting surfaces separated by an insulator, thus forming a capacitor. The capacitance of this structure is based on the same relationship as equation 1.2. Due to the constant thickness of the oxide, the  $C'_{ox}$  constant is added for ease of calculation. The  $C'_{ox}$  is given by:

$$C'_{ox} = \frac{\epsilon_r \cdot \epsilon_0}{t_{ox}} = \frac{\epsilon_{ox}}{t_{ox}} \quad [\text{F m}^{-2}]$$

(1.3)

where  $\epsilon_0 = 8.85 \times 10^{-12} \,\mathrm{F\,m^{-1}}$  and the relative dielectric constant  $\epsilon_r$  of SiO<sub>2</sub> is 3.9. The  $t_{ox}$  is the thickness of the SiO<sub>2</sub>, which is also a constant. Then the capacitance  $C_{ox}$  of the structure can be calculated by:

$$C_{ox} = C'_{ox} \cdot A = C'_{ox} \cdot l_{drawn} \cdot w_{drawn} \quad [F]$$

(1.4)

where A is the area between the polysilicon and the substrate. The  $l_{drawn}$  is the length and the  $w_{drawn}$  is the width of this transistor. Why the area is a multiplication of the length and width can be better seen in the Figure 1.4. The reason for using the drawn width and length is that the  $C_{ox}$  capacitance consists of the capacitance between the gate and drain/source overlaps and the capacitance between the gate and substrate. By using the drawn dimensions, these capacitances are accounted for.

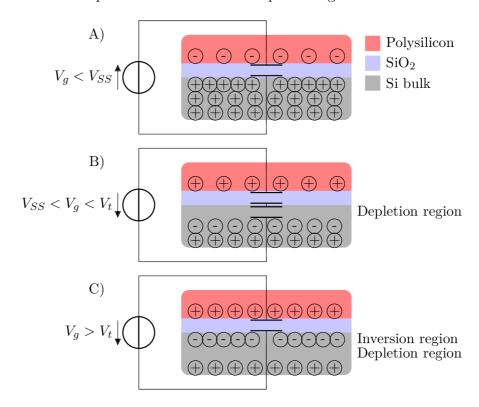

The value of this capacitance will depend not only on the area and distance between the substrate (bulk) and the polysilicon (gate), but also on the voltage between the gate and bulk, due to the behavior of the semiconductor. This capacitance relationship can be explained by looking at the isolated structure only with gate and substrate body without a source and drain, which can be seen in Figure 1.5. Despite the earlier statement in Section 1.2 that  $V_{SS}$  represents the lowest potential, this figure, for consistency in labeling, presents an exception. Here, in the specific scenario where  $(V_g < V_{SS})$ , the  $V_{SS}$  is not the lowest potential.

In the figure the body is p-type so that means the carriers are holes. In Figure 1.5 (A) a negative voltage  $V_g$  is applied to gate and the holes are attracted to the region under the gate oxide, this mode is called accumulation. In this mode the value of capacitance is given by the equations 1.3 and 1.4

In Figure 1.5 (B) the voltage  $V_g$  is greater than  $V_{SS}$  but less than the threshold voltage  $V_t$ . This mode is called a weak inversion. In this case there is a positive charge on the polysilicon and the electrons from the substrate are repelled away, thus creating a depletion region under the silicon oxide. In this region, a small negative charge remains, which is built into the lattice of the crystal. Examining the capacitance in this mode reveals two capacitors connected in series. The first one is the oxide capacitor with the same capacitance as in accumulation mode. The second one is the capacitance between the depleted region and substrate.

Figure 1.5: CMOS: Cross-sectional view and transistor symbols

In Figure 1.5 (C) is the voltage  $V_g$  bigger than the threshold voltage  $V_t$ . At this voltage, the free electrons are drawn directly under the region below the oxide and forms a conductive layer, called inversion layer. A transistor with this inversion layer formed is referred to as being in inversion mode. In this mode the resulting capacitance is again given by the equations 1.3 and 1.4 as the one operating in accumulation mode.

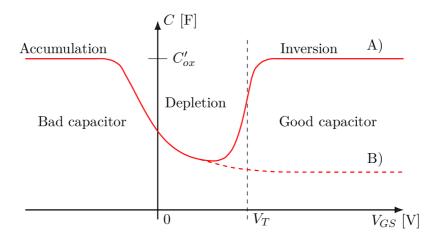

The behavior of capacitance  $C'_{ox}$  as a function of the voltage on the gate can be seen in Figure 1.6, where curve A) shows the behavior at low frequencies and curve B) at high frequencies. The reason why this capacitance is small at high frequencies is that the inversion channel does not have enough time to form. Therefore, the capacitance remains low.

Figure 1.6: MOS capacitance-voltage curves (A) low frequency, (B) high frequency [3].

Further in 1.6 it can be seen, that in accumulation the MOS forms a bad capacitor and in inversion a good capacitor. This can be explained when looking at Figure 1.7. In this figure, there is NMOS transistor with the source, drain, and bulk connected to  $V_{SS}$  in two modes of operation. To save space, only half of NMOS in each mode is shown. On the left side, the NMOS is connected to operate in accumulation, so the gate voltage is  $V_g < V_{SS}$ . On the right side, the NMOS is connected to operate in inversion, so the gate voltage is  $V_g > V_t$ . When the transistor operates in accumulation, the closest  $V_{SS}$  is at the substrate connection and thus the substrate resistance is connected to the capacitor in series. This resistance significantly slows down the charging and discharging of the capacitor and thus degrades the frequency response. On the contrary, in inversion, a channel is formed between the drain and source, and the nearest path to  $V_{SS}$  is through this channel, where its resistance is negligible.

Figure 1.7: Comparison of capacitance and series resistance with transistor in accumulation (left) and in inversion (right)

#### Other Capacitance

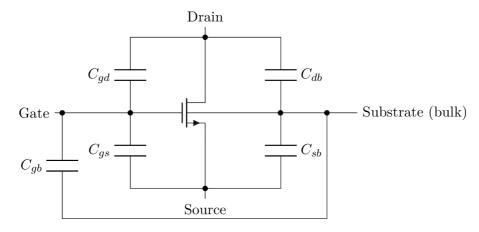

MOSFET has many other parasitic capacitances. However, they are not so essential for this work and a detailed explanation would be lengthy and, moreover, not entirely necessary. So a few further parasitic capacitances will be roughly mentioned here.

In the Figure 1.8, different parasitic capacitances on an NMOS transistor can be seen. For the oxide capacitance described in the previous section, it is assumed that half of it is between gate and drain and the other half is between gate and source. Therefore, this capacitance is referred to as  $C_{gd}$  and  $C_{gs}$ . For this transistor there are also capacitances between the bulk and the drain, gate and source. The values of these capacinatces will vary depending on how the transistor is connected.

Figure 1.8: MOSFET capacitances [3].

## 1.3.3 Leakage

Unfortunately, the gradual shrinking of transistors has a negative effect, which is an increase in leakage current. This leakage current has a significant impact on power consumption, and in many technologies, it accounts for 30-50 % of total power losses [8].

Leakage current refers to the undesirable flow of current through a circuit when it is supposed to be off or in a non-conductive state. In MOSFET transistors, several mechanisms can cause this unwanted leakage current [8]. Leakage is dependent on the technology used; for instance, in 65nm technology, specific factors become the primary contributors [9].

#### **Gate Tunneling Leakage**

Gate tunneling leakage current is a quantum mechanical effect where electrons pass through a thin gate oxide [10]. The solution to this problem is the use of high permittivity gate dielectrics, which greatly reduce quantum tunneling, while maintaining a thin layer [11]. In this research, the focus is on the 65 nm technology node, where silicon oxide is still used as the gate dielectric. At this scale, gate tunneling poses a significant challenge. And given the topologies that will be used, which will be mentioned in Section 3.2.1, this leakage will be the biggest contributor.

#### Sub-threshold Leakage

Sub-threshold current flows between drain and source when the device is in weak inversion. This weak inversion layer allows a small current to flow. As the transistors get smaller, the threshold voltages get smaller. This results in it being easier for the inversion layer to form. As the threshold voltage shrinks, the sub threshold current grows exponentially [8].

#### Reverse Bias Leakage

As mentioned in Section 1.2, a diode is formed in the CMOS structure and is connected to be reverse biased. When the diode is in reverse bias, there is still some current flowing through it. This is due to the thermal generation of minority carriers that can drift across the depletion region.

## 2 Standard Cells

In this day and age when integrated circuits contain billions of transistors, as mentioned in Section 1, cost-effective and rapid development of a new chip is necessary. Given the huge cost to produce a few samples of chips, correct functionality on the first production run is absolutely crucial.

To manage the complexity and scale of chip design, a circuit is first described with a system specification, which might be described in text or a system specification language. This is then converted by designers into Register-Transfer Level (RTL) written in Hardware Description Language (HDL) such as VHDL or Verilog. Next step is to synthesize the RTL description, this includes several steps, with the most important being the conversion of RTL into a generic gates and registers and optimization of the logic for speed and area. The final step is mapping these generic gates to a specific set of cells [2]. These cells are called standard cells, and they are a predefined and pre-laid out function blocks.

The most important property of standard cells is their fixed height, while their width can vary. With this fixed height, they can be connected side by side and will align. They can also be flipped along the y-axis and still align. Additionally, when flipped around the x-axis, they can be connected directly above each other.

Standard cells are designed and optimized either for low power, high speed, or minimal layout area [12]. Additionally, they can be fine-tuned to achieve a compromise among these three key parameters, balancing the requirements based on specific design needs. The standard cell library contains a large number of cells with different functions, a few basic ones can be seen in the Table 2.1.

Table 2.1: List of common cells in the digital standard cell library [13].

| Name of cell         | ne of cell Description of the cells                            |  |  |

|----------------------|----------------------------------------------------------------|--|--|

| BUF, INV, AND, OR,   | Simple logical functions with multi-inputs and different       |  |  |

| NAND, NOR, XOR, XNOR | output strengths                                               |  |  |

| HALF / FULL ADDER    | 2-bit half or full adder with different output strengths       |  |  |

| MUX / DEMUX          | Multiplexer or demultiplexer with different output strengths   |  |  |

| ECO CELLS            | Universal cells that can be tuned in case of need              |  |  |

| AOI / OAI            | Multi-input AND/OR or AND/OR logical combination               |  |  |

| FLIP-FLOPS / SCAN    | Flip-flops (plain, reset, set) with different output strengths |  |  |

| FLIP-FLOPS           |                                                                |  |  |

| LATCHES              | Flip-flop controlled with level                                |  |  |

| FILLER / FILL CAP    | The cell can connect power rails or can be used as decoupling  |  |  |

|                      | capacitances                                                   |  |  |

| CLOCK GATING CELLS / | Used to synchronize the clock signal, delays are used for      |  |  |

| DELAYS               | compensation of STA violations                                 |  |  |

## 2.1 Physical View

In the context of a standard cell library, the term "view" is used to describe different representations or models of the standard cell. In this work, the physical view will be the most important.

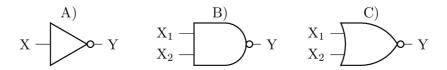

## 2.1.1 Symbol View

The view symbol serves as a view of the cell at the highest level of abstraction showing only the most important elements such as inputs and outputs. An example of such a symbol can be seen in the Figure 2.1.

Figure 2.1: Symbol view of an inverter (A), NAND (B) and NOR (C).

### 2.1.2 Schematic View

The schematic view shows a detailed electrical representation of the standard cell. It displays how transistors and other passive components are internally connected and how such a standard cell works internally. In the Figure 2.2 the NAND (A) and NOR (B) circuit schematic can be seen.

Figure 2.2: Schematic view of a NAND (A) and NOR (B).

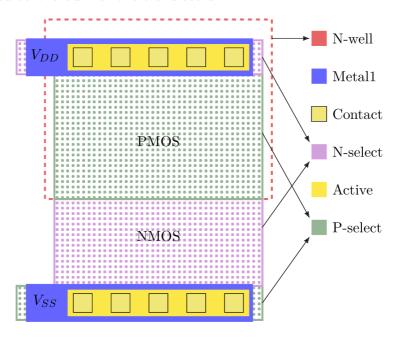

### 2.1.3 Layout View

In Figure 2.3 standard cell template is shown. In this cell, there is a designated space for NMOS at the bottom with layers prepared for its formation. The same applies to PMOS, for which there is a reserved space at the top. This figure does not show the actual proportions of the individual layers so that all layers are easily visible. The reason why the space allocated for PMOS is larger than NMOS is that PMOS is slower than NMOS. Next, there are power rails,  $V_{DD}$  at the top and  $V_{SS}$  at the bottom. With all these pre-prepared layers to form a transistor, the designer only needs to outline the active layer and the polysilicon layer, as detailed in Section 1.3.1. Then the transistors can be connected to the power rails and to each other using metals and contacts. The metal layer is a conductor that is used to connect components to each other. The designation "Metal1" for the layer suggests that multiple metal layers are available, with their number being dependent on the specific manufacturing technology and the chosen metallization option. These layers are crucial for forming interconnections between the various components of the device. The next layer is the contact layer, which is used to connect the metal layers to each other or to connect the metal directly to the substrate. The active layer can be seen around the contacts on the power rails, indicating that the contacts are connected to the bulk of the transistors.

Figure 2.3: Standard cell template.

## 3 Decoupling Capacitors

In this chapter, the primary sources of power supply noise, primarily voltage drops, are introduced, along with potential solutions using decoupling capacitors. Various topologies are also presented, followed by a simple netlist simulation that allows for the determination of parameters important for these capacitors. The results of the simulation are then evaluated.

## 3.1 Power Supply Noise

With the increase in chip sizes and the reduction in transistor sizes, the corresponding wires become narrower while extending in length. This combination, with increasing switching speed and decreasing power supply voltage, causes a serious noise immunity problem, and maintaining good quality of the power supply becomes an issue [14].

#### Ripple

Ripple in the context of power supply noise refers to the small, unwanted residual periodic variation of the DC voltage within a power supply after being rectified. The magnitude of the ripple is typically influenced by the design of the power supply and its filtering. A higher ripple can lead to increased noise within the circuit, affecting signal integrity and potentially leading to incorrect operations, especially in sensitive digital circuits.

#### **EMI**

EMI is caused by a change in a current over time, which is referred to as  $\Delta I/\Delta t$  noise [15]. This change in current causes electromagnetic emissions, and conversely external electromagnetic emissions can also cause a change in current in the circuit. In integrated circuits such a change can be caused by a fast rising or falling edge of a clock signal or a data signal, thus emitting an electromagnetic emission. On the contrary, these external emissions can be received by the integrated circuit and cause unintended logic switching.

#### **Voltage Drops**

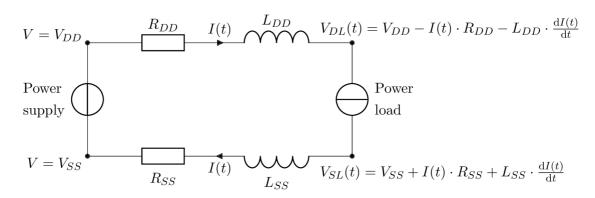

In the Figure 3.1, a simple power delivery system is depicted. Such a system contains a power supply and a power load. The wiring between the power supply and the power load is not ideal and consists of parasitic resistance  $R_{dd}$  and  $R_{ss}$ , and inductance  $L_{dd}$  and  $L_{ss}$ . When the current I(t) is drawn into the load, there is a

voltage loss in these parasitic elements. On the wiring there is resistive voltage drop  $\Delta V_R(t)$  and inductive voltage drop  $\Delta V_L(t)$  described by the following equations:

$$\Delta V_R(t) = I(t) \cdot R \quad [V], \tag{3.1}$$

$$\Delta V_L(t) = L \cdot \frac{\mathrm{d}I(t)}{\mathrm{d}t}$$

[V]. (3.2)

The symbols R and L refer to the parasitic resistance and inductance on the wiring, with units in ohms  $(\Omega)$  and henries (H), respectively. Therefore, at the terminals to which the load is connected, the voltage changes by these losses. As can be seen in Figure 3.1, the voltage at the first terminal decreases to:

$$V_{DL}(t) = V_{DD} - \Delta V_R(t) - \Delta V_L(t) \quad [V]. \tag{3.3}$$

Conversely, the voltage at the second ground terminal increases to:

$$V_{SL}(t) = V_{SS} + \Delta V_R(t) + \Delta V_L(t) \quad [V]$$

(3.4)

In these expressions,  $V_{DL}(t)$  and  $V_{SL}(t)$  represent the voltages at the terminals where the load connects to the power supply's  $V_{DD}$  and  $V_{SS}$  potentials, respectively.

This power supply uncertainty caused by voltage drop is referred to in literature as "power supply noise" [16]. Power supply noise negatively affects the behavior of circuits. It causes uncertainty in clock and timing signals, on-chip clock jitter, lowering noise margin, and degrading gate oxide reliability [16]. When designing a load circuit, it is assumed that the supply voltage is within a certain range, this range is called the noise margin and is typically 10% of  $V_{DD}$ . Therefore, the main objective of a power supply system is to deliver sufficient current to each circuit and not to exceed the noise margin. One potential solution to mitigate power supply noise is the use of decoupling capacitors [14, 16, 17].

Figure 3.1: Power delivery system, with non-ideal interconnection lines [16].

## 3.2 Power Supply Decoupling

Decoupling capacitors are used to keep the supply voltage in the noise margin to ensure signal integrity while reducing electromagnetic interference (EMI) radiated noise. From a physical point of view, the decoupling capacitor serves as a storage of charge and energy. The energy stored in a capacitor is given by

$$E_C = \frac{1}{2} \cdot C \cdot V^2 = \frac{1}{2} \cdot \frac{Q^2}{C} = \frac{1}{2} \cdot V \cdot Q \quad [J],$$

(3.5)

where C is capacity, V is the voltage and Q is the charge stored in capacitor. Since the voltage in a chip is fixed, it's desirable to have as large a capacitance as possible [16]. If the equation 1.4 is recalled, a larger capacity can be achieved either by enlarging the width or length, or by reducing the gate oxide thickness. However, several limitations are faced: the area is constrained by the cell size and primarily by the available area on the chip, and the thickness of the oxide is determined by the manufacturing technology. Even if variation in the oxide thickness were possible, an increase in the leakage current caused by tunneling would start to be observed, as described in section 1.3.3.

In a design these capacitors are placed between the power supply and the power load, ideally as close to the load as possible. When the load switches it needs energy, which is supplied by the decoupling capacitor that is nearby, and does not need to take energy from the power supply. The wiring path between the load and a capacitor is much shorter, then that from power supply, thus resistive and inductive voltage drop is reduced.

## 3.2.1 Topologies

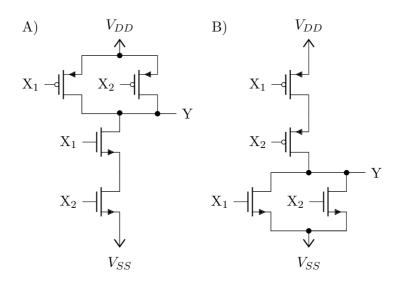

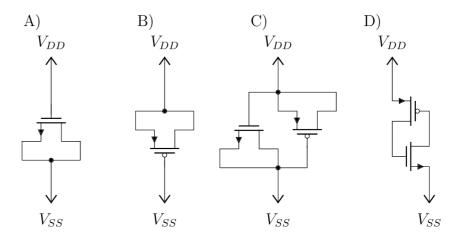

In a Figure 3.2 four possible topologies in CMOS 65 nm are presented [1]. The first two topologies 3.2(A) and (B) are NMOS and PMOS transistors connected in inversion mode between the power supply rails. The third topology is the CMOS seen in Figure 3.2(C), which is just a combination of the previous two. And the fourth last topology in the Figure 3.2(D) is Cross-Coupled.

As can be observed, the first two topologies, NMOS and PMOS, consist of only one transistor each. This will be reflected in the simulation results, as their capacitance will be smaller due to their smaller area. In all simulations, the same parameters will be used for all transistors to ensure that the results can be reasonably compared and processed. It would be possible to use two transistors in parallel for the simulation and this would solve this problem, but from a layout point of view two transistors of the same type would not fit in a standard cell because of the layer spacing rules. For this reason they will be simulated as a single transistor

For these four topologies, three different devices will be used, each with a different threshold voltage. As mentioned in 1.1, there are three different threshold voltages available in 65 nm technology, namely low, standard and high. In total, four different topologies with three different threshold voltages will be examined, which makes a total of twelve combinations. The Table 3.1 shows a list of these combinations and appropriate labels, which will subsequently be used in this work.

Figure 3.2: CMOS decoupling capacitors topologies: (A), NMOS (B), PMOS (C), CMOS and (D) Cross-Coupled

Table 3.1: Threshold voltage and topology labeling.

|           | Topologies |      |        |               |

|-----------|------------|------|--------|---------------|

| Threshold | NMOS       | PMOS | CMOS   | Cross-Coupled |

| Low       | n_l        | p_l  | cmos_l | cp_l          |

| Standard  | n_s        | p_s  | cmos_s | cp_s          |

| High      | n_h        | p_h  | cmos_h | cp_h          |

Furthermore, all combinations of the following parameters will be used for all topologies:

• Length values:  $1\lambda$ ,  $2\lambda$ ,  $4\lambda$ ,  $5\lambda$ ,  $7\lambda$

• Width values:  $1\mu$ ,  $2\mu$ ,  $4\mu$

• Number of fingers values: 1, 3, 6

That's five different values for the length, three different values for the width, and three different values for the number of fingers, for a total of forty-five different combinations. Together these forty-five combinations with four different topologies and three threshold voltages make five hundred and forty different combinations. However, not all of these combinations will be valid, because for some combinations

of width and number of fingers, the division will result in a smaller width than the minimum allowed. These invalid combinations will be filtered out during processing. Unfortunately, due to the NDA, all potentially sensitive information will presented in a normalized form. The channel lengths and widths will be normalized to values where  $1\lambda$  will corresponds to the lowest used length value and  $1\mu$  for lowest used width. The number of fingers remains the same. This means that if the lowest width of 420 nm was used for the simulation, this width would be marked here as  $1\mu$  and then the 840 nm width would be marked here as  $2\mu$  and so on.

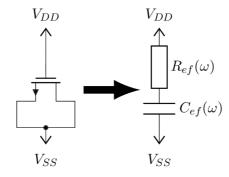

## 3.3 Simulation