### **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

**DEPARTMENT OF INFORMATION SYSTEMS**ÚSTAV INFORMAČNÍCH SYSTÉMŮ

# DECOMPILATION OF SPECIALIZED AND ADVANCED INSTRUCTION SETS

ZPĚTNÝ PŘEKLAD SPECIALIZOVANÝCH A POKROČILÝCH INSTRUKČNÍCH SAD

**BACHELOR'S THESIS**

**BAKALÁŘSKÁ PRÁCE**

AUTHOR JURAJ HOLUB

**AUTOR PRÁCE**

SUPERVISOR Ing. ZBYNĚK KŘIVKA, Ph.D.

**VEDOUCÍ PRÁCE**

**BRNO 2020**

Department of Information Systems (DIFS)

Academic year 2019/2020

# **Bachelor's Thesis Specification**

Student: Holub Juraj

Programme: Information Technology

Title: Decompilation of Specialized and Advanced Instruction Sets

Category: Compiler Construction

### Assignment:

- 1. Study the problems of reverse engineering. Focus on the decompilation of a binary code to its high-level representation.

- 2. Familiarize yourself with RetDec decompiler and research technologies used in this decompiler (LLVM, Capstone, Keystone, etc.).

- 3. Familiarize yourself with the processor architectures supported by RetDec decompiler. Focus on unsupported or partially supported processor extensions and instruction sets.

- 4. Analyze current flaws and potential obstacles in adding support for these instruction sets. Select a set of instruction extensions with the best ratio of positive impact for the decompilation quality to difficulty of their implementation.

- 5. Design new components and propose modifications to RetDec decompiler necessary for the implementation of the instruction sets chosen in point 4.

- 6. After a discussion with the supervisor and the consultant, implement features from point 5.

- 7. Carefully test the implemented solution. Include real-world programs making use of the selected instruction extensions in your test suite.

- 8. Summarize your thesis and discuss future developments.

#### Recommended literature:

- E. Eilam: Reversing: Secrets of Reverse Engineering, Wiley 2005, ISBN 978-076457481.

- Project documentation for RetDec, LLVM, Capstone, Keystone etc.

- Documentations for architectures of x86, x86\_64, ARM, ARM64, MIPS, PowerPC processors.

- According to the supervisor/consultant recommendation.

### Requirements for the first semester:

• First five items and partially item 6.

Detailed formal requirements can be found at https://www.fit.vut.cz/study/theses/

Supervisor: **Křivka Zbyněk, Ing., Ph.D.**Consultant: Matula Peter, Ing., Avast

Head of Department: Kolář Dušan, doc. Dr. Ing.

Beginning of work: November 1, 2019

Submission deadline: May 28, 2020 Approval date: October 21, 2019

### Abstract

Nowadays, the process of analyzing malicious software is an important part of information technologies. One of the crucial techniques is decompilation of malicious binary programs. The decompilation is a complex process, and there are multiple projects with such a goal. The project RetDec aims to develop retargetable and flexible decompiler. The goal of this research is to improve the decompilation of advanced instruction sets for architecture x86. The new optimization for FPU register stack manipulation is designed, and the support of FPU and SSE instruction set translation is extended. The new extensions are implemented and tested in the manner of decompilation efficiency and quality.

### Abstrakt

V dnešnej dobe je proces analýzy nebezpečného softvéru dôležitou súčasťou informačných technológií. Jedna z kľúčových techník je spätný preklad škodlivých binárnych programov. Spätný preklad je komplexný proces, ktorý rieši niekoľko projektov. Projekt RetDec sa zameriava na flexibilný návrh a riešenie spätného prekladača s možnosťou znovupoužiteľnosti. Cieľom tejto práce je zlepšenie spätného prekladu pokročilých inštrukčných sád pre architektúru x86. Bola navrhnutá nová optimalizácia pre FPU registrový zásobník. Bola rozšírená podpora prekladu inštrukčných sád jednotiek FPU a SSE. Nové rozšírenia boli implementované a otestované z hľadiska efektivity a kvality spätného prekladu.

# Keywords

compiler, decompiler, reverse engineering, x86, FPU, SSE, RetDec

### Klíčová slova

prekladače, spätné prekladače, reverzné inžinierstvo, x86, FPU, SSE, RetDec

### Reference

HOLUB, Juraj. Decompilation of Specialized and Advanced Instruction Sets. Brno, 2020. Bachelor's thesis. Brno University of Technology, Faculty of Information Technology. Supervisor Ing. Zbyněk Křivka, Ph.D.

### Rozšířený abstrakt

Táto práca sa zaoberá využitím reverzného inžinierstva v oblasti softvérových technológií. Reverzné inžinierstvo je všeobecne metóda získavania informácií alebo plánov o akýchkoľvek objektoch vytvorených človekom. V oblasti informačných technológií je význam tejto disciplíny najmä v rámci kybernetickej bezpečnosti. Táto technika je využívaná tvorcami škodlivého softvéru (tzv. malvér). Malvér využíva reverzné inžinierstvo na získavanie citlivých informácií o operačnom systéme s potenciálnym cieľom získať kontrolu nad zariadenim. Ďalšia rozšírená oblasť je softvérové pirátstvo, kedy sa útočník snaží prelomiť ochranu komerčného digitálneho obsahu ako sú knihy, filmy, hudba, hry alebo rôzne platené programy. Na druhej strane môže pomôcť práve pri analýze malvéru za účelom zvýšenia bezpečnosti voči danému softvéru.

Jedna z kľúčových techník pre analýzu malvéru je analýza pomocou programu všeobecne nazývaneho spätný prekladač. Spätný prekladač je program, ktorý analyzuje spustiteľné binárne súbory a zrekonštruuje vysoko úrovňový výstup, napríklad v podobe grafu alebo kódu v programovacom jazyku. V dnešnej dobe existuje niekoľko projektov spätných prekladačov. Projekt RetDec sa zameriava na vytvorenie open-source nástroja, ktorý je rozdelený na viacero knižníc. Takýto návrh má za cieľ umožniť znovupoužiteľnosť jednotlivých nástrojov spätného prekladača.

Cieľom tejto práce je rozšíriť podporu spätného prekladu v projekte RetDec o špecializované inštrukčné sady FPU a SSE (procesorová architektúru x86). Bol vytvorený návrh nových rozšírení na základe zhodnotenia aktuálnej podpory inštrukčných sád FPU a SSE. Inštrukčná sada FPU bola v rámci práce rozšírená na 100 % inštrukcií. RetDec už v súčasnosti novú implementáciu podporuje. Pre sadu SSE bol vytvorený a čiastočne implementovaný návrh, ktorý rozlišuje inštrukcie na skalárne a vektorové.

Druhé rozšírenie sa zameriava na optimalizáciu spätného prekladu FPU registrov, ktoré tvoria zásobníkovú štruktúru. V rámci práce bola navrhnutá nová optimalizácia, ktorá transformuje prácu s FPU zásobníkom na preurčenú sústavu lineárnych rovníc. V ďalšej časti práce sa zhodnotili rôzne aproximačné metódy na riešenie získaného systému. Bol vykonaný výkonnostný experiment, ktorý bol meraný na spätnom preklade stoviek skutočných binárnych spustitelných súborov. Experiment porovnal efektivitu skutočnej implemntácie pre jednotlivé navhované metódy a zvolil najoptimálnejšiu, ktorá bola následne integrovaná do novej optimalizácie.

Záver práce popisuje testovanie implementácie nových rozšírení v spätnom prekladači RetDec. V rámci testovania boli použité tri testovacie nástroje. Prvé dva nástroje testovali nové rozšírenia pomocou jednotkového a regresného testovania. Do jednotkových testov boli pridané testy zvlášť pre každú novo podporovanú inštrukciu (a jej varianty). Nástroj regresných testov otestoval nové rozšírenie na 822 skutočných binárnych programoch, ktoré boli preložené pre architektúru x86 a manipulovali FPU zásobník. Nástroj vyhodnotil spätný preklad pre zvolenú testovaciu sadu za úspešný. Tretí nástroj sa v rámci projektu RetDec nazýva ako nočné testy. Tento nástroj otestoval nové rozšírenia na tisíckach reálnych spustitelných súboroch. Výsledky nočných testov zaznamenali výkonnostný pokles spätného prekladu. Nové spracovanie FPU registrov je priemerne šesťkrát pomalšie oproti originálnemu riešeniu. Avšak takýto výkonnostný pokles bol očakávaný a je akceptovateľný vzhľadom na komplexnosť novej optimalizácie.

# Decompilation of Specialized and Advanced Instruction Sets

### **Declaration**

Hereby I declare that this bachelor's thesis was prepared as an original author's work under the supervision of Zbyněk Křivka. The supplementary information was provided by Peter Matula. All the relevant information sources, which were used during preparation of this thesis, are properly cited and included in the list of references.

Juraj Holub May 19, 2020

# Acknowledgements

I would like to express thanks to my supervisor Zbyněk Křivka, and to the people from Avast team which provided professional help. Namely I would like to thanks Peter Matula, Jakub Křoustek, and others for their consultation and valuable comments.

# Contents

| 1 Introduction |                |         |                                            |    |

|----------------|----------------|---------|--------------------------------------------|----|

| 2              | Rev            | erse ei | ngineering                                 | 5  |

|                | 2.1            | Revers  | sing in area of software security          | 5  |

|                |                | 2.1.1   | Malicious software                         | 5  |

|                |                | 2.1.2   | Reversing cryptographic algorithms         | 6  |

|                |                | 2.1.3   | Digital Rights Management                  | 6  |

|                | 2.2            |         | sing in area of software development       | 6  |

|                |                | 2.2.1   | Proprietary software documentation         | 7  |

|                |                | 2.2.2   | Development of competitive software        | 7  |

|                |                | 2.2.3   | Software quality metrics                   | 7  |

|                | 2.3            |         | evel software                              | 7  |

|                |                | 2.3.1   | Assembly language                          | 8  |

|                |                | 2.3.2   | Compilers                                  | 8  |

|                | 2.4            |         | ppilation                                  | Ö  |

|                |                | 2.4.1   | Intermediate Representations               | Ö  |

|                |                | 2.4.2   | Static Single Assignment (SSA) form        | S  |

|                |                | 2.4.3   | Typical Decompiler Architecture            | ç  |

|                | 2.5            |         | ng reversing tools                         | 11 |

|                |                |         |                                            |    |

| 3              | $\mathbf{Ret}$ | argeta  | ble Decompiler (RetDec)                    | 12 |

|                | 3.1            | Techno  | ologies used in decomplier                 | 12 |

|                |                | 3.1.1   | LLVM IR                                    | 12 |

|                |                | 3.1.2   | Capstone                                   | 14 |

|                | 3.2            | Decon   | apiler structure                           | 14 |

|                |                | 3.2.1   | The preprocessing                          | 15 |

|                |                | 3.2.2   | The core                                   | 15 |

|                |                | 3.2.3   | Backend                                    | 16 |

|                |                |         |                                            |    |

| 4              |                |         | point extensions of architecture Intel x86 | 17 |

|                | 4.1            |         | ng-point unit x87                          | 17 |

|                |                | 4.1.1   | Floating-point registers                   | 17 |

|                |                | 4.1.2   | Register stack                             | 18 |

|                |                | 4.1.3   | FPU instructions                           | 19 |

|                | 4.2            |         | ng-point conventions for calling functions | 19 |

|                |                | 4.2.1   | Standardization of procedure calls         | 19 |

|                |                | 4.2.2   | Architecture x86 calling conventions       | 20 |

|                | 4.3            | Stream  | ming SIMD Extensions (SSE)                 | 21 |

|    |             |         | mization unit testing                                                             | <b>5</b> 1      |

|----|-------------|---------|-----------------------------------------------------------------------------------|-----------------|

| Bi |             | graphy  |                                                                                   | 48              |

| 9  | Sun         | nmary   |                                                                                   | 47              |

|    | 8.3         |         | ssion tests                                                                       | 4!              |

|    | ~· <b>-</b> | 8.2.1   | FPU optimization evaluation                                                       | 4!              |

|    | 8.2         |         | tests                                                                             | $\overline{4}$  |

|    |             | 8.1.2   | Decoder of Capstone into LLVM IR                                                  | 4               |

|    | 0.1         | 8.1.1   | FPU optimization                                                                  |                 |

| J  | 8.1         |         | ests                                                                              | 43              |

| 8  | Tes         | ting of | extension                                                                         | 43              |

|    |             | 7.2.3   | Summary                                                                           | 42              |

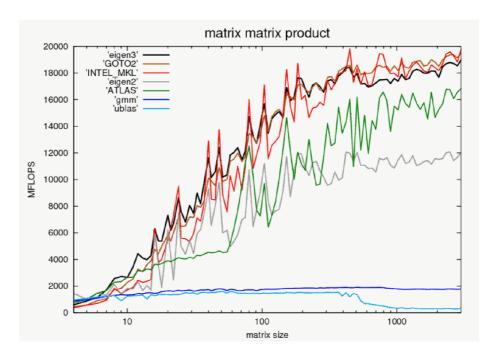

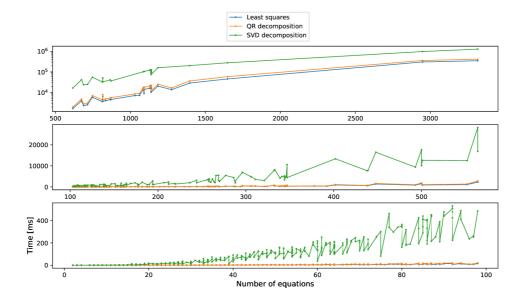

|    |             | 7.2.2   | Selection of solver for a linear system                                           |                 |

|    |             | 7.2.1   | Eigen3 project                                                                    |                 |

|    | 7.2         |         | algebra library                                                                   |                 |

|    | 7.1         |         | er support of advanced instruction sets                                           |                 |

| 7  | Imp         |         | tation of extensions                                                              | 39              |

|    |             |         | ·                                                                                 |                 |

|    |             | 6.3.5   | Summary                                                                           | 38              |

|    |             | 6.3.4   | SVD decomposition                                                                 | 37              |

|    |             | 6.3.2   | QR decomposition                                                                  | 37              |

|    |             | 6.3.2   | Cholesky decomposition                                                            | 36              |

|    | 0.0         | 6.3.1   | Least squares solution                                                            | 36              |

|    | 6.3         |         | ds for solving linear systems                                                     | 36              |

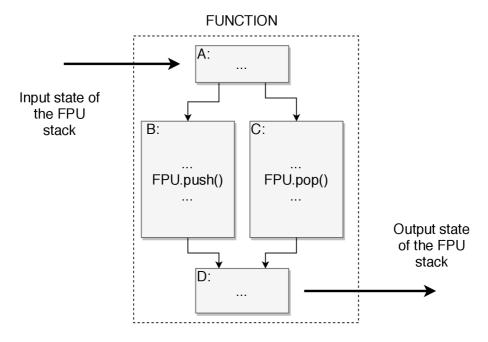

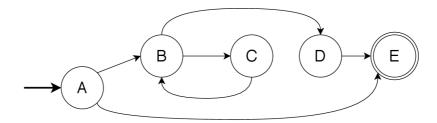

|    |             | 6.2.1   | Function Control Flow Graph analysis                                              | 33              |

|    | 0.2         | 6.2.1   | Function-based optimization                                                       | 33              |

|    | 6.2         | 0       | ced reconstruction of FPU stack                                                   | $\frac{32}{33}$ |

|    | 6.1         | 6.1.1   | 86 decoder extends of the advaced instruction set                                 | $\frac{32}{32}$ |

| 6  |             | •       | extensions of RetDec                                                              | <b>32</b>       |

| •  | ъ           |         | t t t t t t t t t t t t t t t t t t t                                             | 99              |

|    |             | 5.2.2   | The current state of FPU stack optimization $\ \ldots \ \ldots \ \ldots \ \ldots$ | 30              |

|    |             | 5.2.1   | Semantic model of FPU instruction set                                             | 29              |

|    | 5.2         | LLVM    | IR optimization for FPU instruction set $\ldots \ldots \ldots \ldots$             | 29              |

|    |             | 5.1.4   | Advanced instruction sets of x86 architecture                                     | 28              |

|    |             | 5.1.3   | Translation process                                                               | 26              |

|    |             | 5.1.2   | Decoder library structure                                                         | 25              |

|    | J.1         | 5.1.1   | Translation modes                                                                 | 24              |

| 9  | 5.1         |         | er of Capstone into LLVM IR                                                       | 24              |

| 5  | Rev         | iew of  | RetDec deficiencies                                                               | 24              |

|    |             | 4.3.4   | Compilers built-in functions                                                      | 23              |

|    |             | 4.3.3   | Instruction set                                                                   | 22              |

|    |             | 4.3.2   | SSE register set and data types                                                   | 21              |

|    |             | 4.3.1   | Idea of SIMD processing                                                           | 21              |

|    |             |         | 4 077 57                                                                          | 0.1             |

# Chapter 1

# Introduction

Nowadays, the process of analysing malicious software is an important part of informal technologies. One of the essential methods is decompilation of malicious binary programs. The decompilation is a complex process, and there are many projects with such an intent. The project RetDec intends to develop retargetable and flexible decompiler. The research proposes designs and tests new extensions for RetDec that improve the decompilation of advanced instruction sets for architecture x86. The support of FPU and SSE instruction set translation is extended. The new optimization for FPU register stack manipulation is designed. These extensions are tested in term of decompilation efficiency and quality.

The thesis, besides the general introduction, is split into eight logical Chapters. Chapter 2 introduces the concept of reverse engineering. Expressly, it presents the typical process of decompilation and explains the usual difficulties.

The Chapter 3 discusses the project RetDec, presents its architecture, and technologies applied in this decompiler (LLVM, Capstone, Keystone, and others).

Chapter 4 discusses the processor architecture Intel x86 supported by RetDec decompiler. The Chapter discusses the floating-point extensions FPU and SSE. The Chapter offers information that explains the problems and obstacles of this processor extension decompilation.

The Chapter 5 analyse actual state and potential obstacles of RetDec with the support of FPU and SSE instruction sets. It reviews these deficiencies in term of information obtained from the previous Chapter.

The Chapter 6 proposes a new advanced FPU optimization. It presents several methods for solving the designed task. It also proposes better support of SSE instruction set for Ret-Dec decompiler. At last, the modifications to decompiler necessary for the implementation of the new extensions are discussed.

The Chapter 7 reviews the final implementation of the proposed extensions. The Chapter examines the newly proposed optimization implementation efficiency for various method of task solution, and it selects the best alternative. It also shows the result of the implementation for the advanced support of SSE instruction set.

The Chapter 8 tests implemented extensions in term of efficiency and functionality. The Chapter introduces three testing framework and shows the results of these tests.

Finally, the Chapter 9 summarize the entire work and point out the proposed and actual results.

# Chapter 2

# Reverse engineering

The concepts of reverse engineering, actual and historical reasons and conditions are presented at the base of the following book [8].

Reverse engineering, in general, is a method of obtaining information or blueprints about any object created by human. The idea of reverse engineering does not associate only to modern computer technologies. The concept has already existed in the era of the industrial revolution. The method has been typically used to examine commercially available technical products. Such a product has been physically decomposed, and each part was investigated to figure out its purpose. The process reveals the secrets of merchandise design without owning the original blueprints. Retrieved designs were commonly used to improve the product of the competing company.

The reverse engineering, in the domain of software technologies, is commonly named just reversing. Reversing is a fully abstract process of looking inside a computer program. There is not any physical object but only binary data, which are executable on a specific processor. Reversing requires knowledge of computers and software development processes.

The software reversing exploitation is useful for a variety of different purposes, the most significant are security-related reversing, and software development reversing. Both of these reversing purposes has discussed in the following Chapter. Software reversing considerably relates with a low-level layer of software architecture. Terms associated to low-level software describe this Chapter. At last, the Chapter introduces the concept of automatized reversing of software by the special program intended for this purpose.

# 2.1 Reversing in area of software security

In the area of software security, the reversing is used by both malware developers and by those creating security measures. In the area of computer security, the typical application of reversing is to analyses of malicious software. Also reversing of the cryptographic algorithms can discover implementation-dependent deficiency. Analysing of proprietary software program binaries, and searching for security vulnerabilities. Some of these applications are discussed in this Section.

### 2.1.1 Malicious software

In the beginning, a malicious software spread was fairly slow, and the precautions were much simpler because the human intervention was required to infect computer device. Internet network expansion dramatically changes the security character of computer technology.

Nowadays, nearly every computer on earth is connected to this virtual network. The malicious software spreads much faster, and the protection of computer devices is considerably more difficult. Computer attackers use reversing to capture vulnerabilities of the operating system or some other software. The reversing allows attackers to locate sensitive information about users, or even to take over control of the system. On the contrary, developers of antivirus software use reversing for analyzing malicious programs. They monitor every step of the malicious program to determine the damage it could cause and to find a possible method of protection.

### 2.1.2 Reversing cryptographic algorithms

Cryptography is a method of preserving information by transforming it into a human unreadable format. Protection of e-mails, credit cards information, or any other sensitive data are obtained by cryptography. [15]

The specific method of data transformation is called a cryptographic algorithm. Cryptographic algorithms in the manner of reversing purposes divide into two groups: key-base and restricted algorithms. The restricted algorithms are secret because the knowledge of the algorithm allows encryption and decryption of the message. Further, the key-based algorithms are typically public and well-known, but it uses the secret key. The secret key is necessary for encrypting and decrypting the message. Reversing try to analyses the restricted algorithm. The restricted algorithms are weak protection of information because exposing the algorithm makes it unsafe. Reversing of the key-based algorithm can look like ineffective. However, there are cases where it makes sense. Understanding of specific implementation can offer some interesting security details.

### 2.1.3 Digital Rights Management

In contrast with the past, providers of the most kinds of copyrighted materials turned their products into digital content. The products, like books, music, films, or games, are now available digitally. This produces huge benefits for customers, but also enormous complications for providers and content owners. The duplication of digital information, between consumers, is easy and unfortunately common practise. Commonly, the software owners wrap their product with additional copy protection software. Over the years, piracy protection technologies become more advanced, and this type of software are collectively called Digital Rights Management (DRM). DRM technologies are active protection, which decides about the availability of protected digital media. Software pirates use reverse engineering techniques to defeat DRM protection. Reversing of DRM technologies allow pirates to understand the inner secrets of software protection. Their goal is to find out how to modify it to disable the protection.

### 2.2 Reversing in area of software development

Reversing has as well great importance in the field of software development. Developers use reversing techniques to analyse partially documented or undocumented software, to improving competitive software, or to evaluating software quality and robustness.

### 2.2.1 Proprietary software documentation

Proprietary software documentation is almost always insufficient. Vendors of proprietary software can make a huge effort to provide adequate documentation. But customers typically encounter a problem with an unclear, or an undocumented solution. Developers in such a situation have to contact the vendor, which is a time-consuming solution. Differently, a developer can use reversing. Reversing can solve several of these problems with small effort. Typically, third-party software contains undocumented proprietary file formats, or networking protocols, which has to be reversed. Consider a famous Microsoft Word document format .doc. This format is also undocumented. But there is a lot of programs, which wants to support this format. Someone had to reverse the Microsoft Word file format, to provide support of it.

### 2.2.2 Development of competitive software

The development of a competitive product is, without a doubt, the most leading utilization of reverse engineering. Although, software engineering industry creates considerably complex products. Reversing whole software to create a competing product is almost always worthless. More often then not, it is effortless to create a new product from scratch or integrate the third-party libraries for more complex parts. Nevertheless, there are exceptions where the application of reversing is reasonable. Some extremely complex algorithms might be reversed, because of time-saving reasons. The legal aspect of reversing competitive software discuss the following book (see [8], Chapter 1, Section 'Is Reversing Legal?').

### 2.2.3 Software quality metrics

Software development includes techniques and metrics that evaluate software robustness, security and other general qualities of source code. Such techniques require access to the source code of the software. The disadvantage of the proprietary software is that there is no access to source code for customers. The users have to trust the vendor or apply revere engineering. Of course, reversing will never be as effective as analysing of source code itself, but it can be highly informative. The need for evaluating source code of critical software by users is even confirmed by large companies. For example, Microsoft gives access to Windows sources for large customers.

### 2.3 Low-level software

Generally, software is composed of layered architecture (see [8]). The bottom layer relates with the physical hardware. Hardware control provides assembly language. Usually, the assembler is different for each processor architecture and specific hardware device. Above physical layer is low-level software layer. It consists of an operating system and development tools such as compilers, linkers, or debuggers. The operating system encapsulates specific hardware architecture dependency, and development tools encapsulate assembly language dependency. Today, low-level software is encapsulated by another layer. At the top layer, there are some high-level languages, which greatly simplify development.

Reverse engineering strongly relates with low-level software layer. The reason is that the low-level details about the original program are typically the only pieces of information obtainable from the executable binary program. The Section introduces key aspects of low-level software.

### 2.3.1 Assembly language

Assembly language (or simply assembler) is a family of languages. Each processor architecture has its assembly language. And these languages usually significantly differ from each other. The knowledge of chosen architecture assembler is the necessary basis for the reverse engineer.

Assembler is a representation of processor instructions in a human-readable form. On the other hand, the machine code, or binary code is a representation of processor instructions in a sequence of bits, which is more effective for the processor itself. The machine code and assembler are just a different representation of the same object.

The illustrative example presents the translation process of assembler instruction to machine code. The instruction belongs to processor Intel 8086 (see [14], Chapter 12, Section 'x86 Instruction Encoding'). The process of encoding instruction example from Table 2.1 includes the following steps:

- 1. The unique code for instruction PUSH with 16-bit register operand is 0x50.

- 2. The unique identification for register CX is 0x01. Addition of 0x50 and 0x01 produces 0x51.

| Assembly instruction | Machine instruction |  |

|----------------------|---------------------|--|

| PUSH CX              | 0x51                |  |

Table 2.1: Mapping assembler instruction to machine code for Intel 8086 processor.

For the reversing purposes, the opposite (or backward) process of translation is important. A *disassembler* is a specific type of program that transforms the input binary executable program into a text file. Such a file contains assembler code equivalent to input machine code. It is a relatively simple process that maps binary code into assembler.

### 2.3.2 Compilers

As described in Section 2.3.1, the software consists of layered architecture, where the assembly language creates the bottom layer. High-level language is an abstraction over the assembly language. However, the high-level languages (for example Java, or C++) have to be transformed into machine code at the end. The reason is that machine code is the only language executable at the processor. The transformation performs a program called a compiler. The resulting machine code classifies into two categories. Either it is standard platform-dependent binary code, which is straight executable by a processor. Or it is a platform-independent format of code that is called bytecode. The specific program called a virtual machine process the bytecode and executes the specific hardware functionality.

Compilers of standard programming languages convert source code into machine code, which is directly executable at the processor (for example C or Pascal). During the conversion, a lot of optimizations over the machine code is applied. They increase program performance, but reversing of the optimized program is considerably more challenging. The reconstruction of the original high-level programming constructions from the optimized machine code is a complicated process. It is not an exception that the reconstruction is not achievable.

On the contrast, the second class of compilers transforms source code into bytecode (for example Java). In comparison to reversing of the standard binary code, the reversing of

bytecode is a completely different process. In general, it is a more straightforward process, because bytecode offers higher abstraction.

### 2.4 Decompilation

The process of reversing binary executable software into high-level programming language is called decompilation. The decompiler program reverses the executable binary file and produces high-level language code output. The Section introduces common decompiler architecture. It also describes the widely used techniques such as an intermediate representation of the program and static single assignment form of code representation. Finally, the Section discusses existing decompilers and compares them.

### 2.4.1 Intermediate Representations

Section 2.3.2 introduces the concept of compilers. The result of compilation is machine code that depends on the processor architecture (see Section 2.3.1). Intermediate Representation (IR) provides a generic set of instruction independent from architecture but with the ability to adequately represent the reversed program. Some decompilers transform source program to IR and just iteratively eliminate low-level detail. Other decompilers use more IRs, typically one for low-level representation and another for higher-level representation in later stages. Generally, the IR contains the following instruction set: assignment, push, pop, call, ret, branch, and unconditional jump (for more detail information about typical IR instruction set see [8], Chapter 13.). The IR instruction set is considerably smaller than the usual assembler instruction set. However, IR instructions typically represent complex expressions. For the representation of such complex expressions, the decompiler uses a structure called an expression tree. An expression tree effectively represents the sequence of arithmetic instructions. Expression tree provides reasonably more accessible input for generating high-level language expression.

Decompilers must create a *Control Flow Graph (CFG)* to reconstruct high-level control flow information from low-level IR. The CFG always represents the control flow of a single procedure. The reason for CFG representation is a simple transformation to high-level control flow constructs like loops and branches.

### 2.4.2 Static Single Assignment (SSA) form

SSA is a naming convention for variables in low-level program representation. Program code is in SSA form if each variable is a target of exactly one assignment statement. This lead to referential transparency, which means that for a variable with exactly one definition, the variable value is independent of its position in code. This knowledge is used for code optimizations such as data-flow analysis. For example, the dead code elimination in the fourth version of the GCC compiler is based on SSA intermediate representation, and an earlier version of the GCC compiler does not use SSA. The fourth version of the GCC compiler analyses around 40 % less of code lines then the equivalent optimizer pass with the third version of the GCC compiler. [27]

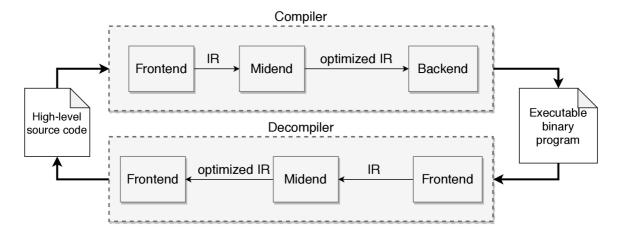

### 2.4.3 Typical Decompiler Architecture

The compiler is a special program, which transforms high-level programing language representation of program into a binary executable program. On the other hand, the decompiler

Figure 2.1: The typical architecture of compiler in contrast to decompiler.

reconstructs high-level language representation from some binary program. Decompiler typical architecture consists of similar parts as compiler architecture but in reversed order.

The compiler **frontend** is a component that parses input source code. The decompiler frontend decodes assembler instructions into some IR. In the beginning, there is only an input binary executable program, which has to be parsed. Frontend also provides semantic analysis because a lot of these assembly instructions hardly make sense individually. Instead, many of them create architecture-specific sequences. The output of frontend additionally represents control flow. The IR creates blocks of instructions where each block reference to some other part of code.

The midend of both architectures performs a set of optimizations over IR but with opposite goals. The compiler performs a code analysis to increase the performance speed of the final executable program. On the contrary, the decompiler code analysis aims to transform code into the more abstract form. At this stage, the decompiler eliminates the hardware concepts (registers and low-level conditional code) and converts it into the high-level programming constructions (variables, loops, branches and others). Typically for CFG analysis, the SSA notation is used (see Section 2.4.2). Data flow analysis can also provide information about data type propagation (e.g., the data type propagation of function return value). But before the data type propagation, the decompiler has to find out data types by itself. Registers often do not define data type information, but some instructions are data type sensitive. This information allows decompiler to scan for primitive data types. Decompilers also reconstruct complex data types. For such purposes, decompiler applies various advanced code scanning techniques:

- Certain registers are analysed to find out a memory address pointing to some data structure.

- The program commonly uses a hard-coded constant for manipulating data structure. Identification of such constant allows access to the analysed data structure.

- Detection of an array provides identification of standard loop iteration sequence and others.

Usually, the analysed program contains a lot of library functionality. Identification of such code is very beneficial. It provides very accurate information about data types without type-analysis process.

Finally, **the backend** takes this improved IR and generates output. Separation of output generation brings flexibility benefits. The generator produces various programing language output but always work with the same IR input. Such an approach allows an easy way to generate different programming language product.

### 2.5 Existing reversing tools

The Section introduces some decompiler projects and discusses their comparison. The goal of this thesis is to design new extensions for RetDec decompiler. As a result, the comparison of existing decompilers relates to this reference project (RetDec is detailed in Chapter 3).

**IDA** (Interactive Disassembler)<sup>1</sup> is cross-platform, multi-processor disassembler and debugger developed by Hex-Rays company. The part of the project is also the **Hex-Ray Decompiler**<sup>2</sup>. It generates human-readable C-like pseudocode. Currently, the supported input processor architectures are x86, x64, ARM32, ARM64, PowerPC, and PowerPC64. Nowadays, Hex-Rays offers one of the best decompilers on the market, but it is a paid tool, and because it is proprietary software, it cannot be used commercially.

**Ghidra**<sup>3</sup> is open-source reverse engineering framework developed by The National Security Agency of the U.S. Government. The framework was released in 2019, but it presents functionality comparable to the IDA project. It provides support of multiple processor architectures and operating systems. On the other hand, it is a robust tool, and it does not allow the use of individual framework tools separately.

<sup>&</sup>lt;sup>1</sup>IDA project: https://www.hex-rays.com/products/ida/index.shtml

<sup>&</sup>lt;sup>2</sup>Hex-Ray Decompiler: https://www.hex-rays.com/products/decompiler/index.shtml

<sup>&</sup>lt;sup>3</sup>Ghidra project: https://www.nsa.gov/resources/everyone/ghidra/

# Chapter 3

# Retargetable Decompiler (RetDec)

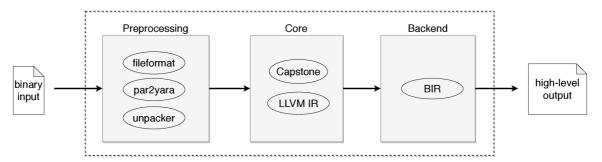

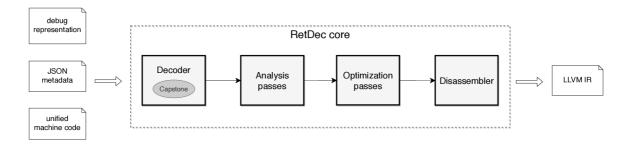

RetDec decompiler project is a set of open-source reversing tools that are chained together. The goal of the decompiler is to become architecture, operating system and executable file format independent. The Chapter introduces RetDec architecture and software technologies used by this framework. Figure 3.1 shows the schema of RetDec and technologies used in each part of the decompiler. The core technologies used in decompiler are LLVM IR (see Section 3.1.1) and Capstone (see Section 3.1.2).

Figure 3.1: The architecture of RetDec and software technologies used by decompiler.

### 3.1 Technologies used in decomplier

Decompiler contains various open source technologies. The core of the decompiler design uses LLVM project. Capstone and Keystone libraries perform binary parsing and assembler generating. The Section explains details about these technologies.

#### 3.1.1 LLVM IR

Low Level Virtual Machine (LLVM) IR defines common, low-level code representation. It is freely available under a non-restrictive license. LLVM representation uses an SSA form (see Section 2.4.2). LLVM code representation resembles an abstract RISC instruction set with high-level information for efficient analyses. For example, language-independent type system, control flow graphs or typed register set in SSA form. LLVM IR representation is independent of source language because it uses low-level instruction set slightly richer than common assembly language. It is important to note that LLVM IR has not intended to be a universal compiler IR. In particular, it does not provide high-level language features such as

classes, inheritance or exception handling. These features could be provided only indirectly. It also does not guarantee type or memory safety any more than assembly language. LLVM is complementary to high-level virtual machines such as in Self and Smalltalk. Benefits of LLVM are ideal for statically compiled languages like C and C++. [20]

The Section describes the basic concept of LLVM syntax and representation. For further details about LLVM syntax, see the official documentation of the project<sup>1</sup>, or book [22]. LLVM representation of the program consists of the following data structures:

- 1. **Module**: The module is a top-level abstraction. It defines the content of an entire LLVM file. Naturally, the program can consist of multiple modules combined with the language linker. Each module consists of a sequence of functions. It also contains external entities, such as global variables, external function prototypes, or definition of data structures.

- 2. Function: The function representation is similar to C language syntax. There are function definition and a declaration signature syntax. The function declaration signature begins with declare keyword followed with the return type, name of the function and argument list. The function name is the global identifier and always begin with © prefix. Each argument consists of a data type and argument label. The argument label needs % prefix because it is a local identifier. The body of the procedure sets function definition, which explicitly breaks the function into a sequence of basic blocks.

- 3. Basic Block: The basic blocks form the CFG for the function. Each block begins with a unique identifier. Such identification can be explicitly defined, or an implicit numeral label is assigned. A block represents a sequence of instructions with a single entry point (first instruction) and a single exit point (last one). The terminating instruction changes control flow to another basic block or returns from the function.

- 4. **Instruction**: The instructions classification split instruction set into several classes: terminator instructions, binary instructions, memory instructions, and other instructions. Terminating instruction are explained previously, together with the basic block concept. Binary instructions perform general operations, for example, arithmetic operations, bitwise shifting, bitwise logical operations, etc.. Memory instructions read, write, or allocate memory. The remaining instructions cover mixed functionality (comparations, special constants, a function call, etc.). Typically, the instructions form a three-address code with two sources and one destination operand.

The code Listing 3.1 shows possible content of LLVM IR module. This module contains one definition of a function with a globally unique label <code>@foo</code>. The function has two arguments with explicit type definition (a 32-bit wide integer), and return data type is also an integer. The model also defines one global variable <code>@GLOBAL\_VAR</code>. The body of the function contains three basic blocks: <code>%label0</code>, <code>%label1</code>, and <code>%label2</code>. The basic blocks <code>%label1</code> and <code>%label2</code> are terminating blocks of function, and basic block <code>%label0</code> ends with branching instructions. The expressive ability of instructions inside the basic block is very similar to assembler, but besides, it explicitly defines data types and variables. Lines 4 and 8 shows a characteristic load/store architecture.

<sup>&</sup>lt;sup>1</sup>Official documentation of LLVM project: https://llvm.org/docs/

```

1 @GLOBAL_VAR = global i32

2 define i32 @foo(i32 %arg0, i32 %arg1) {

3

label0:

%flag = load i1, i32* @GLOBAL_VAR

4

5

br i1 %flag, label %label1, label %label2

6

label1:

7

%x = add i32 %arg0, %arg1

8

store i1 false, QGLOBAL VAR

9

return i32 %x

10

11

%y = mul i1 %arg0, %arg1

12

return i32 %y

13 }

```

Listing 3.1: Example of LLVM IR syntax.

### 3.1.2 Capstone

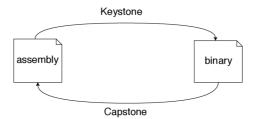

Capstone is a disassembly framework for reverse engineering. It is an open-source project under a BSD license. The framework is compatible with multiple platforms. According to the official documentation (see [2]), the engine supports the following hardware architectures: x86 (16-bit, 32-bit, 64-bit), ARM, ARM64, MIPS, PowerPC, Sparc, SystemZ and XCore. Capstone has native support for the Windows operating system and it also supports Linux, OSX, iOS, Android, BSD, and Solaris. The disassembler engine provides architecture-independent Application Programming Interface (API). As shown in Figure 3.2, Capstone disassembler is complementary to Keystone assembler project (see [3]). Keystone is an assembler framework, which compile assembly instructions to binary. Ret-Dec decompiler uses Capstone library for disassembling, and Keystone library as a testing framework.

Figure 3.2: Complementary reverse engineering engines Capstone and Keystone.

# 3.2 Decompiler structure

The Section describes the architecture of the decompiler (for further details see [18]). The decompiler is structured into three main blocks. Every block consists of smaller units. Such a design makes the project units reusable because each unit works as the library with its interface. The three main blocks chains framework into the pipeline in the following sequence:

1. **Preprocessing** part unifies and analyses binary files. Unified binary files and extracted metadata are input for the core block.

- 2. **The core** block creates an IR and applies dozens of analyses and optimizations. The optimized IR is the output of the core block.

- 3. The backend block creates an Abstract Syntax Tree (AST). It applies optimizations over AST and generates a final high-level representation.

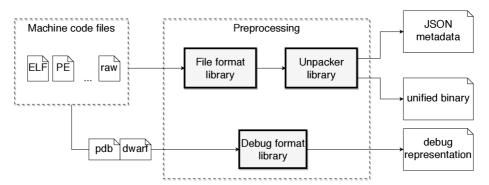

### 3.2.1 The preprocessing

The structure of the preprocessing part describes Figure 3.3. The input of the preprocessing phase is a set machine code files. There are a lot of different formats for different platforms. The File format library analyses and unifies various file formats into uniform representation. Currently, the library supports the following machine code formats: ELF, PE, Mach-O, COFF, AR (archive), Intel HEX, and raw machine code.

Typically, the executable binary program additionally includes debugging data. This metadata creates a relationship between source code and binary data. Such relation is originally created for the debugger program, but also decompiler makes use of it. *The Debug Format library* parses this data and transforms them to debug representation used in next phases of decompilation. The library support DWARF and PDB format. [7]

The compiler that creates analysed binary program might use a tool so-called *packer*. The packing of binary files is done for two main reasons - code compression and code protection. As a consequence, the decompiler uses *Unpacker library*, which examines and identifies possible compression of the binary file. The library contains third-party tool YARA<sup>2</sup>. YARA tool helps identifies and detects binary patterns. The output of preprocessing is a metadata file in JSON format and uniform representation of machine code. The JSON metadata file contains information like compiler type and version, or processor architecture.

Figure 3.3: Preprocessing phase of decompilation.

### 3.2.2 The core

The functionality of the decompiler core illustrates Figure 3.4. The core block receives as an input JSON metadata, unified and unpacked machine code, and debug representation. Firstly, the machine code is transformed into LLVM IR. The transformation process performs the *Decoder library*. Decoder starts traversing binary data from the entry point of the program, and it follows the control flow of the reversed program. Capstone library maps the binary code into Capstone IR, which is transformed into LLVM IR.

<sup>&</sup>lt;sup>2</sup>YARA tool: https://yara.readthedocs.io/

Figure 3.4: Transformation of binary code into LLVM IR by RetDec core.

The main part of the decompiler core performs modifications over obtained LLVM IR. The sequence of passes modifies IR. There are two types of passes: analysis and optimization passes. Analysis passes do not modify IR, but they obtain additional information. For example, analysis helps identify global variables, data types, function arguments, or return types of functions. The optimization passes iterate over IR and modify it. At last, the transformed LLVM IR is dissasembled. The result of this process is optimized LLVM IR, which is the output of the decompiler core block.

### 3.2.3 Backend

Backend does not operate with LLVM IR but transforms it into special IR so-called *Backend IR (BIR)*. This transformation is done because LLVM IR is a rather low-level representation similar to the assembler. On the other hand, BIR is a high-level representation based on the AST. AST allows better reconstruction of high-level control-flow patterns like conditional branches and loops. Backend restructures BIR when it identifies high-level constructs like *if-else*, for-loop, while-loop, switch, break, or continue.

Backend performs many high-level optimizations. It removes redundant variables, reduces constants in arithmetic expressions to simpler form. Backend optimization converts expressions to form more readable for programmers. Consider the following C source code:

As you can see, there are used constants defined in the standard C library. The meaning of this literals depends on the context. But the context of this literals is lost after disassembling. The decompiled code looks like:

The optimizer searches for context literals and refactors them. Backend can generate the output in the following formats: C, Control-Flow Graph (CFG), or Call Graph. [19]

# Chapter 4

# Floating-point extensions of architecture Intel x86

In the beginning the Intel x86 architecture was developed to manipulate only with integer values. The floating-point calculation was possible to emulate through software but with a considerable performance penalty. As a consequence, a separate floating-point coprocessor unit was introduced. Nowadays, the Floating-Point Unit (FPU) is typically part of the main processor. The Section 4.1 explains details about FPU registers and instruction set, and Section 4.2 details calling conventions of function with floating-point values.

Next, the architecture extends support of the floating-point calculation with parallel processing of floating-point vectors. The Section 4.3 introduces SSE extension, the instruction set and their manipulations.

### 4.1 Floating-point unit x87

The Section details FPU registers and instruction set according to assembly language documentation for x86 processors (see [14]). FPU does not operate with x86 general-purpose registers because it contains its own set of registers. Floating-point instructions manipulate with these registers similarly to the stack data structure.

#### 4.1.1 Floating-point registers

FPU has eight 80-bit general-purpose data registers named R0 through R7. These registers handling differs from manipulation of general-purpose data registers for integer evaluations. Hardware registers like EAX, EBX, ECX, etc., are direct operands of assembly instructions. But floating-point data registers forms an abstract stack data structure, and they cannot be accessed directly. Access to such hardware register is relative as explained in Section 4.1.2. As an addition to floating-point data registers, the unit has six special-purpose registers:

- Control register determines the rounding method and precision of FPU.

- Status register contains condition and exception flags. A three-bit field of status word so-called TOP identifies the register that is currently at the top of the stack.

- Tag register indicates the contents of data registers (valid number, zero, or special value like NaN, infinity, denormalized number, etc.). Register has a three-bit field for each data register.

- Opcode register contains the last executed instruction opcode.

- Last instruction pointer register points to the last executed instruction.

- Last data (operand) pointer register points to operands used by the last executed instruction (if the instruction has any data operand).

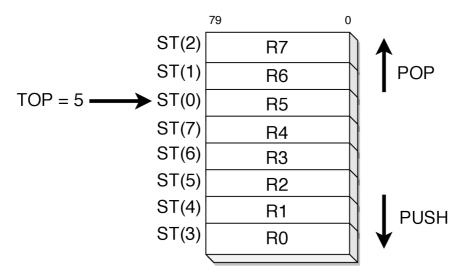

### 4.1.2 Register stack

FPU loads and stores values from the register stack where it performs floating-point arithmetic calculations. The x87 instructions evaluate arithmetic expressions in *postfix* form due to stack evaluation advantages of this form. Consider the following *infix* expression:

$$(A+B)*C$$

And equivalent *postix* expression:

$$AB + C*$$

The *postfix* format does not require parenthesis to override precedence rules. The transformation algorithm from infix to postfix form is not a subject of this thesis.

Figure 4.1 shows the abstraction of FPU stack data manipulation. Stack operands are labelled ST(0) through ST(7), where ST(0) label points to data register on the top of the stack. The value of TOP points to data register labelled ST(0). A push (alternatively load) instruction decrements TOP and moves the content of operand to ST(0) register. Overriding of existing data in the stack generates a floating-point exception. Decrementation of TOP with value 0 (ST(0) points to RO(0) leads to underflow TOP value to 7 (RO(0) points to RO(0)). A pop (alternatively store) instruction moves content of RO(0) register to operand and increment TOP. Incrementation of TOP with value 7 (RO(0)) points to RO(0)0 points to RO(0)1 points to RO(0)2 points to RO(0)3 points to RO(0)4 points to RO(0)5 points to RO(0)6 points to RO(0)6 points to RO(0)7 value to 0 (RO(0)6 point to RO(0)8.

Figure 4.1: FPU data register stack abstraction. [14]

### 4.1.3 FPU instructions

The floating-point instruction operands allow only one addressing mode. Operands are always in general-purpose data registers. An instruction can inherently manipulate with register stack (implicit push, or store). The set of floating-point instructions contains the following basic instructions categories:

- Basic arithmetic instructions.

- Constant loading instructions.

- Data transfer instructions.

- Exponential, logarithmic and trigonometric instructions.

- Data comparsion instructions.

- FPU control instructions.

### 4.2 Floating-point conventions for calling functions

The procedure, alternatively function, or subroutine is a fundamental abstraction for general-purpose procedural programming languages. The program is divided into various parts, and such part of code could be used several times. The procedure abstraction eliminates repetitions of program code segments and allows their reusability. An execution of program subroutine is known as a procedure call. The Section explains details about procedures with the floating-point interface and their calling conventions.

### 4.2.1 Standardization of procedure calls

In past, procedure calling interface differed for every operating system or compiler. It led to compatibility problems. Nowadays, there is an effort on the standardization of the procedure calling interface. The calling conventions determine the following low-level details:

- For interaction between caller (calling program) and callee (a subroutine), the program reserves specific hardware registers.

- The system of arguments transfer between calle and caller. Arguments are typically passed within registers, on the stack or in shared memory.

- Caller has to pass arguments in the right order. Typically, arguments are passed from the first to the last or in the reversed order.

- Arguments could be passed by value or by reference.

- The result of procedure execution (return value) has to be passed to the callee.

- The method of stack pointer restoration after the procedure execution.

| Architecture | Calling convention | Passing registers |

|--------------|--------------------|-------------------|

|              | cdecl              |                   |

| 16 bit       | pascal             | AX                |

| 10 010       | fastcall           |                   |

|              | watcom             | Inconclusive.     |

|              | cdecl              |                   |

|              | stdcall            |                   |

| 32 bit       | pascal             | ST(0)             |

| 32 010       | fastcall           |                   |

|              | thiscall           |                   |

|              | watcom             | Inconclusive.     |

| 64 bit       | Windows            | SSE registers     |

| 04 010       | Linux, BSD, Mac OS | DDE registers     |

Table 4.1: Usage of registers for passing floating-point values across calling conventions for x86 architecture.

### 4.2.2 Architecture x86 calling conventions

Architecture x86 has three modes: 16-bit, 32-bit, and 64-bit mode. The bit-wide of mode specifies wide of registers, memory address, etc. in bits. The 16-bit and 32-bit mode have usually calling conventions independent on operating systems. Instead of the operating system, the calling convention is defined by the compiler. The thesis assumes Microsoft, Borland, Watcom and Gnu compilers brands. On the other hand, the 64-bit mode has a default calling convention for each operating system, while other calling conventions are rare in 64-bit mode. The thesis considers calling conventions for Windows, Linux, BSD, Unix and Mac OS X operating system. [9]

For **16-bit mode**, there is calling conventions so-called *cdecl*, *pascal*, *fastcall* and *watcom*. Watcom is inconclusive because the method of registers usage depends on options in effect. All others calling conventions do not return floating-point value in ST(0). The called function is expected to allocate space for value in memory and write the return value to this address. The address where is the result stored is passed in AX register. [5]

System V (see [30]) application binary interface for a **32-bit mode** of x86 architecture defines the usage of floating-point stack registers. In case that procedure returns a floating-point value, then the value is stored in ST(0) register. It does not matter if the floating-point value is in the representation of single or double precision. If the procedure does not return floating-point value, then register ST(0) must be empty. Also, register ST(0) must be empty before every procedure call. Registers ST(1) through ST(7) are unused in the standard calling sequence of the procedure with floating-point arguments or return value. The standard defines that these registers must be empty before and upon every procedure call. Most used calling conventions for architecture x86 in 32-bit mode are cdecl, stdcall, pascal, fastcall, thiscall and watcom. System V standard follows all of these conventions except watcom. Watcom same like in 16-bit mode is inconclusive.

As described in Section 4.3, the x86 platform over time introduced extensions the Streaming SIMD Extensions (SSE). SSE adds new instructions and registers, which also manipulates floating-point values. System V for **the 64-bit mode** of architecture x86 defines that function with floating-point arguments, or return value does not pass these values through FPU registers (see [10]). Preferably, it uses SSE registers. The convention

is followed in Linux, BSD, Unix, and Mac OS X operating system. The Windows operating system uses different conventions then System V. Nevertheless, the Microsoft function calling convention with floating-point values also uses only SSE registers, and it does not specify any convention for FPU registers. [25]

The x86 architecture function calling conventions are summarized in Table 4.1.

### 4.3 Streaming SIMD Extensions (SSE)

Over the years, the architecture x86 includes multiple extensions, which operate in mode commonly called the Single Instruction Multiple Data (SIMD). These technologies have dedicated to the parallel processing of data. The first extension was MMX, and it created support of basic SIMD processing for the integer arithmetic. The successor of MMX is the Streaming SIMD Extension (SSE), which is a set of the hardware improvements. SSE regularly increases the CPU ability of SIMD processing. It increases integer arithmetic with new registers and instructions, and it extends processor with floating-point SIMD facilities.

Eventually, SSE multiple time upgrades hardware facilities and functionality. The original SSE gradually evolves to SSE2, SSE3, SSE4, AVX (Advanced Vector Extensions), AVX2, and AVX-512. However, this research discusses the general aspects of this hardware extension, and it uses the general label SSE. When the specific version of SSE has discussed, the version name is used.

Following Subsections details SSE, and also explains the standard of compilers builtin functions. The SIMD technology details are obtained from the publication of the x86 assembler programming guide (for further details see [17]).

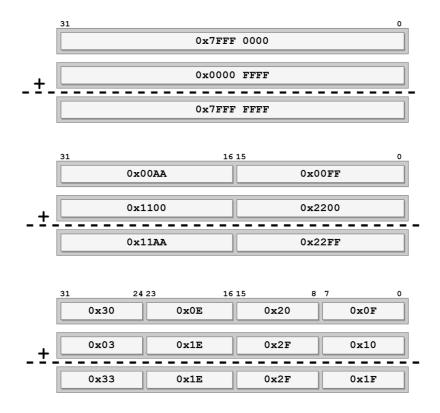

### 4.3.1 Idea of SIMD processing

This Subsection introduces the general concept of SIMD technology. The hardware unit allows executing the same operation on the collection of the data elements at the same time. Typically, the performed operations are basic arithmetic computation, for instance, subtraction, addition, multiplication, division, bitwise operations, and conversion. Such parallelism achieves specific interpretation of the register, or memory location content.

To illustrate considers Figure 4.2 that shows 32-bit width register intended to integer data processing. The register can hold the single 32-bit integer value, but SIMD allows to reinterpret it as two 16-bit integers, or four 8-bit integers. The processor handles each subsequence of register separately, but simultaneously. The hardware supports the usual service of data processing for each bit pattern individually, for example, integer overflow, underflow, rounding, and others.

The effectivity of SIMD strongly depends on the compiler. The compiler must correctly detect and splits the program data that can process simultaneously. The Intel provides documentation for the developers of the compilers that allows them to optimize the efficiency of the resulting program binary. The documentation also contains a guide for the Intel built-in functions, as closely explained in Section 4.3.4.

### 4.3.2 SSE register set and data types

SSE extends the 32-bit architecture of x86 with eight general-purpose registers, which are 128-bit width. The 64-bit architecture appends another eight registers. They are labelled XMM0 through XMM15. These registers allow carrying floating-point values. The original

Figure 4.2: SIMD processing demonstration for integers addition with 32-bit width registers. [17]

SSE supports single-precision, but SSE2 starts supporting double-precision floating-point data. As a contrast to FPU, SSE uses direct addressing of registers. SSE does not operate with register as a stack structure (see Section 4.1.2).

SSE supports various integer and floating-point data types. These data types create two categories:

- Scalar data types: The XMM register or memory location holds 32-bit (single-precision), or 64-bit (double-precision) floating-point value. As mentioned before, the XMM register is 128-bit width, but SSE supports maximally 64-bit width floating-point data types. Suppose that SSE performs some double-precision floating-point scalar operation and saves the result value into specific XMM registers. In such a case, SSE saves the result value into lower 64-bits of a destination XMM register, while the rest of the register content stay untouched.

- Packed data types: The register or memory location holds four 32-bit or two 64-bit floating-point values. Also, it can hold integers with various bitlength: 16 bytes, 8 words, 4 doublewords, or 2 quadword integer values.

#### 4.3.3 Instruction set

As detailed in Section 4.3.2, SSE support two categories of data types. In consequence, also SSE instruction set split instructions into these two categories: instructions with scalar, or packed operands. SSE floating-point instruction has typically four modes:

• Scalar Single-precision mode with instruction suffix SS.

| Compiler     | Built-in ADDPS                     |

|--------------|------------------------------------|

| GCC          | v4sfbuiltin_ia32_addps(v4sf, v4sf) |

| Clang        | v4sfbuiltin_ia32_addps(v4sf, v4sf) |

| Microsoft VS | m128                               |

| Intel        | m128 _mm_add_ps(m128 a,m128 b)     |

Table 4.2: The example of the built-in function for the assembly instruction that performs vector addition of four float operands.

- Packed Single-precision mode with instruction suffix PS.

- Scalar Double-precision mode with instruction suffix SD.

- Packed Double-precision mode with instruction suffix PD.

SSE support following basic functionality for floating-point data (always in packed and scalar version): data transfer, arithmetical and logical operations, and data type conversions. For packed mode only, it allows data shuffle, data unpack or element insertion.

SSE supports only packed processing of integer operands. The integer processing instructions offer almost the same functionality, as for packed floating-point operands, but each instructions differs four modes (byte, word, doubleword, and quadword). At last, SSE supports text string processing. It performs string compares, and string length calculation. It can accelerate a pattern search and replaces algorithm. For full information about all instructions read Intel Software Developer Manual (see [1]).

### 4.3.4 Compilers built-in functions

Compilers built-in functions (also known as intrinsic functions) are C/C++ functions that allow calling assembler instruction in the high-level programming language. Built-in functions are equivalent to the inline assembler. However, the built-in functions offer benefits of high-level programming: better code readability, or advantages of debugging. In general, the developers use these functions when they need some very low-level assembly functionality. In the case of the architecture x86, the built-in functions offer instructions related to MMX, SSE or AVX. Typically, these instructions work with vector operands. [1]

The method of use built-in functions in the program source depends on the compiler. The GCC compiler offers built-in functions for architecture x86 with 32-bit mode and 64-bit mode (see [28]). Clang compiler offers very similar built-in functions with the same syntax (see [29]). On the contrary, the Microsoft Visual Studio defines their built-in functions with different syntax (see [26]). The Microsoft includes a definition of the x86 built-in functions in header <intrin.h>. However, the Intel defines manufacturer-specific built-in functions in header <immintrin.h>. The Intel also offers a detailed guide <sup>1</sup> for compiler developers that describes the semantic meaning of these built-in function. These Intel built-in functions are most general equivalent because of their definition shares between all common compilers. Table 4.2 illustrate the example of the built-in function for the assembly instruction that performs vector addition.

<sup>&</sup>lt;sup>1</sup>The Intel Intrinsics Guide: https://software.intel.com/sites/landingpage/IntrinsicsGuide

# Chapter 5

# Review of RetDec deficiencies

The chapter reviews the design and implementation details of RetDec core. The chapter analysis the flaws and deficiencies of the current RetDec core design. The process of translation Capstone IR into LLVM IR is introduced, and specific problems and restrictions with the translation of FPU instruction set are presented.

### 5.1 Decoder of Capstone into LLVM IR

The section generally explains the model of RetDec for the mapping of disassembled instructions into LLVM IR. The section demonstrates Decoder library (briefly introduced in Section 3.2.2) that controls this process. The possible modes of translation and reasons for such a design are presented. [23]

#### 5.1.1 Translation modes

RetDec decompiler does not aim to entirely translate the semantic meaning of the disassembled machine code. The goal of the decompiler is to generate easy and understandable C/C++ output. Such output can be effectively analysed by a reverse engineer. Decoder library performs mapping of assembly instructions in four modes:

- 1. Full translation mode: Instructions are simple enough to capture their full semantics with a sequence of LLVM IR. This mode captures mostly the core instruction set (basic arithmetic and data transfer instructions).

- 2. Pseudo assembly functions: Some instructions cannot be represented through LLVM IR sequence. For example, instruction FWAIT checks for pending floating-point exceptions. Library represents instruction like a self-explanatory pseudo function @\_asm\_fwait().

- 3. Partial translation mode: Some assembler instructions are too complex in LLVM IR representation. As an example, consider instruction <code>FXSAVE [addr]</code>, which saves the state of FPU, MMX, SSE units, and their registers to 512-bytes in memory to address <code>addr</code>. Entirely mapped instruction produces dozens of LLVM instructions. On the contrary, partial conversion mode produces pseudo assembly function as described previously. But this mode also explicitly informs about storing 512-bytes to memory.

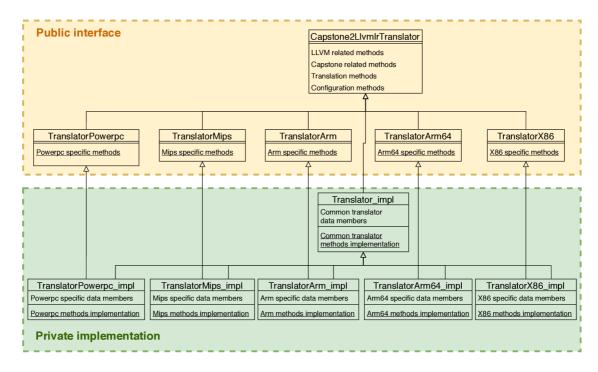

Figure 5.1: Class diagram of the decoder library (*Capstone2LlvmIr* [23]) implementation in RetDec core.

4. **Ignore instruction**: Instruction FNOP performs no FPU operation. The occurrence of this instruction in C output is unnecessary, and decompiler skips it.

RetDec project is developed mainly for decompilation purposes. For some other use-cases, where full semantic meaning is needful, there are other projects like QEMU<sup>1</sup> or McSema<sup>2</sup>, which allow better alternative in such situations.

### 5.1.2 Decoder library structure

As mentioned in Section 3.2.2, the first unit of RetDec core is Decoder library, which transforms Capstone IR into LLVM IR. The library design illustrates the class diagram in Figure 5.1. The library *encapsulates* design into two parts:

- **Public interface**: The library provides public headers without data members and implementation.

- **Private implementation**: The implementation of the decoder (source code and hidden headers) is hidden for the library users.

Also, the design divides library, by *inheritance*, into the two types of modules. Such library design allows simple and flexible expandability by another processor architectures.

• Generic translator: Module with common translation interface and implementation that is independent from processor architecture. It includes LLVM, Capstone, general translation and configuration related methods and data members (*Translator\_impl*, see Figure 5.1).

<sup>&</sup>lt;sup>1</sup>QEMU project: https://www.qemu.org/

<sup>&</sup>lt;sup>2</sup>McSema project: https://github.com/lifting-bits/mcsema

• Processor architecture-specific translator: It includes individual modules for each supported processor architecture by a decompiler. For example, there are specific modules for ARM, MIPS, or x86 architecture *TranslatorArm\_impl*, *TranslatorMips\_impl*, *TranslatorX86\_impl*, see Figure 5.1).

### 5.1.3 Translation process

The translation process of Capstone IR into LLVM IR work similarly for each specific processor architecture module of the decoder library. The Section demonstrates the translation process of two x86 instructions: sub eax, ebx and je 0x1000.

In the first place, decoder creates the instance of the translator module for x86 architecture. The constructor of decoder instantiation accepts an empty LLVM IR module. It initializes a Capstone engine and other internal structures. LLVM IR module initializes with the architecture-dependent environment:

• The specific global variables have been created. They represent concrete hardware registers. Listing 5.1 shows an example of generated global variables. Some registers have internally divided into bit sequences with special meaning. Such special bit is commonly called a flag. A typical example represents the EFLAG register (see [14], Chapter 2). This register consists of flags that crucially control the operation of the processor. Due to the importance of these bits, the equivalent global variables in LLVM IR are generated.

```

@_asm_program_counter = internal global i64 0

2

@eax = internal global i32 0

3

@ebx = internal global i32 0

4

5

@st0 = internal global x86_fp80 0xK0000000000000000000

6

; ...

8

@cf = internal global i1 false ; The Carry flag (CF)

9

@pf = internal global i1 false ; The Parity flag (PF)

10

@ac = internal global i1 false ; The Auxiliary Carry flag (AC)

11

@zf = internal global i1 false ; The Zero flag (ZF)

12

@sf = internal global i1 false ; The Sign flag (SF)

@of = internal global i1 false ; The Overflow flag (OF)

```

Listing 5.1: Example of the specific architecture-dependent global variables.

Special attention belongs to the global variable <code>@\_asm\_program\_counter</code> . The global variable value is updated at the beginning of each translated assembly instruction. It stores integer value that denotes an address of the current reversed assembler instruction in the program. Every sequence of LLVM IR that represents one assembly instruction begins with such a store operation. For example, instruction at address 1234 begins with the following store operation:

```

store volatile i64 1234, i64* @_asm_program_counter

```

• Except for architecture-specific global variables, the module also generates the control flow pseudo functions (see Listing 5.2). These pseudo functions represent control flow operation: function call, return from the function, branching, and conditional branching. Naturally, LLVM IR provides build-in instructions for such functionality. But this stage of decompilation cannot use them, because they accept targets only

in the form of a label. However, the labels reconstruction is subject of advanced optimization at later stages of decompilation. Currently, the library has only integer address of destination targets.

```

; address is 64-bit integer because of 64-bit architecture

declare void @__pseudo_call(i64 %addr)

declare void @__pseudo_return(i64 %addr)

declare void @__pseudo_branch(i64 %addr)

declare void @__pseudo_cond_branch(i1 %condition, i64 %addr)

```

Listing 5.2: Example of the specific architecture-dependent (x86-64) control flow pseudo functions.

- A module defines an architecture-specific data layout string that determines the format of stored data in memory. As an example, the data layout string specifies if the data lays out in big-endian, or little-endian form. It specifies the size of the memory address pointer, or it defines an alignment of various integer and floating-point types.

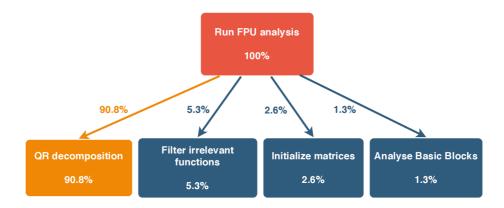

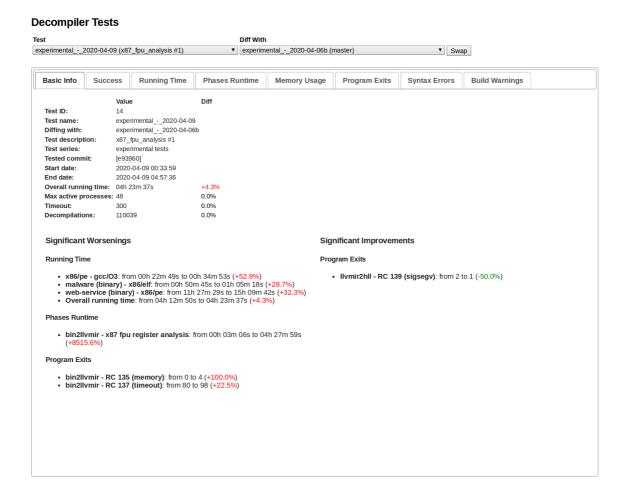

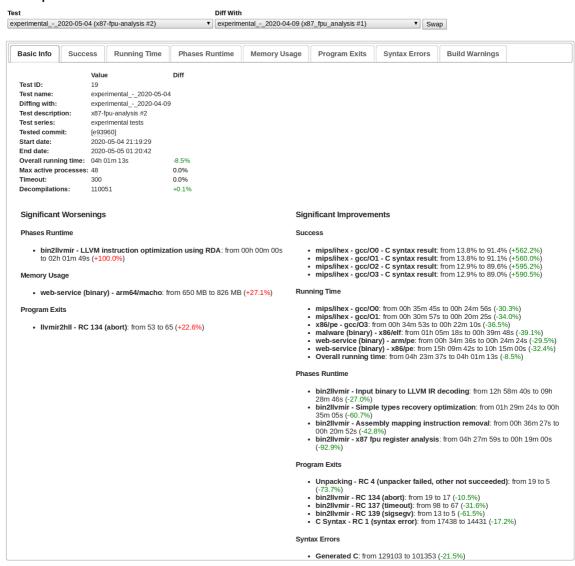

- At last, it specifies individual settings intended for particular processor functionality. For instance, the pseudo functions that manipulate FPU stack (see Section 5.2.1).