# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

### DEPARTMENT OF MICROELECTRONICS

ÚSTAV MIKROELEKTRONIKY

# ACCCELEROMETER SIGNAL PROCESSING FOR VIBRATION MEASUREMENT

ZPRACOVÁNÍ SIGNÁLU Z AKCELEROMETRU NA MĚŘENÍ VIBRACÍ

### **MASTER'S THESIS**

DIPLOMOVÁ PRÁCE

AUTHOR Bc. Peter Marčišovský

**AUTOR PRÁCE**

SUPERVISOR prof. lng. Vladislav Musil, CSc.

**VEDOUCÍ PRÁCE**

**BRNO 2020**

## Diplomová práce

magisterský navazující studijní obor Mikroelektronika

Ústav mikroelektroniky

Student:Bc. Peter MarčišovskýID: 173696Ročník:2Akademický rok: 2019/20

NÁZEV TÉMATU:

### Zpracování signálu z akcelerometru na měření vibrací

#### POKYNY PRO VYPRACOVÁNÍ:

Seznamte se s metodami monitorování stavu mechanického zařízení pomocí měření vibraci a používanými senzory. Navrhněte a realizujte precizní modul (DPS) na zpracování signálu z piezoelektrického akcelerometru, použitého na měření vibrací pro monitorování rotačního mechanického zařízení (elektromotor, turbína). Ze snímaného signálu chceme získat informaci o diagnostickém stavu stroje, např. opotřebení ložisek a vyvážení rotoru. Použijte rychlou Fourierovu transformaci (FFT) pro získání spektra signálu ze senzoru, posunutí stejnosměrné úrovně signálu (voltage level shifting) a následnou digitalizaci převodníkem ADC. Zhodnoťte dosažené výsledky.

#### DOPORUČENÁ LITERATURA:

According to recommendations of supervisor

Termín zadání: 3.2.2020 Termín odevzdání: 1.6.2020

Vedoucí práce: prof. Ing. Vladislav Musil, CSc.

doc. Ing. Lukáš Fujcik, Ph.D. předseda oborové rady

#### UPOZORNĚNÍ:

Autor diplomové práce nesmí při vytváření diplomové práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

### **Master's Thesis**

Master's study field Microelectronics

Department of Microelectronics

Student: Bc. Peter Marčišovský ID: 173696

Year of study:

Academic year: 2019/20

#### TITLE OF THESIS:

#### Accelerometer signal processing for vibration measurement

#### **INSTRUCTION:**

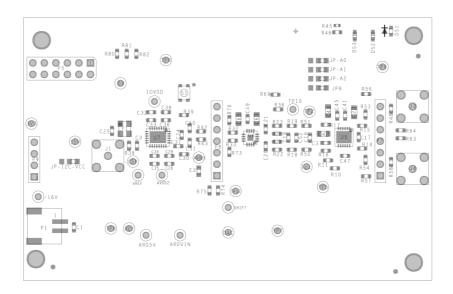

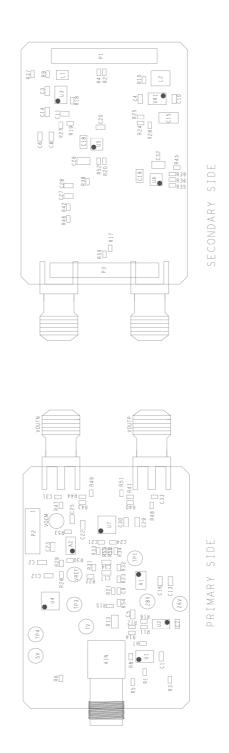

Study methods for monitoring the mechanical system performance by vibration measurement and used sensors. Design and realise the precise module (PCB) for signal processing from a piezoelectric accelerometer used for vibration measurement aimed for monitoring of a spinning machine (like electromotor, turbine). From the signal obtained we want get the diagnostic information, e.g. bearing health, or balancing of rotor. Use a so-called voltage level shifting technique to process the input signal from the sensor and prepare it for the ADC conversion and then use the Fast Fourier Transform (FFT) to calculate the signal spectrum. Evaluate obtained results.

#### **RECOMMENDED LITERATURE:**

According to recommendations of supervisor

Date of project specification: 3.2.2020

Supervisor: prof. Ing. Vladislav Musil, CSc.

Deadline for submission: 1.6.2020

doc. Ing. Lukáš Fujcik, Ph.D. Subject Council chairman

#### WARNING:

The author of the Master's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

#### **ABSTRACT**

This master thesis deals with a design of a system capable of a high precision vibration measurement using a piezoelectric accelerometer. The system is meant to be used as a machine health conditioning for investigating a health conditions mainly, of electrical machines like an electro motor or a turbine. In order to achieve a high precision and a high linearity measurement in extreme low frequency spectrum ranging even from DC levels, trough sub-hertz spectrum to tens of hertz, as well as in a higher frequency spectrum, a possibility of using a DC-coupled approach called a "voltage level shifting" technique has been required to investigate and consequently to evaluate the difference between the DC-coupled and a generally used AC-coupled approach for interfacing with piezoelectric accelerometers.

#### **KEYWORDS**

vibrations, FFT, machine health monitoring, piezoelectric accelerometer, precision ADC, sigma-delta, signal processing, voltage level shifting

#### **ABSTRAKT**

Táto diplomová práca sa zaoberá návrhom zariadenia schopného vysoko presného merania vibrácií za použitia piezoelektrického akcelerometra. Zariadenie je určené na vyhodnocovanie zdravotného stavu strojov, najmä elektrických strojov ako elektromotor, veterná turbína a iné. Za účelom dosiahnutia vysoko presného a vysoko lineárneho merania v spektre extrémne nízkych frekvencií siahajúcich až ku jednosmerným napätím, cez sub-hertzové pásma po desiatky hertzov, ale aj vo vyšších frekvenciách, bola vyžadovaná možnosť použitia prístupu s jednosmernou väzbou zvaného "posúvanie napäťovej úrovne" a následné vyhodnotenie a porovnanie prístupu so striedavou väzbou, ktorý sa bežne používa pre pripojenie piezoelektrického akcelerometra.

### KLÍČOVÁ SLOVA

vibrácie, FFT, pozorovanie zdravotného stavu stroja, piezoelektrický akcelerometer, precízny ADC, sigma-delta, spracovanie signálov, posúvanie napäťovej úrovne

MARČIŠOVSKÝ, Peter. *Accelerometer signal processing for vibration measurement*. Brno, 2020, 104 p. Master's Thesis. Brno University of Technology, Faculty of Electrical Engineering and Communication, Department of Microelectronics. Advised by prof. Ing. Vladislav Musil, CSc.

Vysázeno pomocí balíčku thesis verze 3.03; http://latex.feec.vutbr.cz

### ROZŠÍŘENÝ ABSTRAKT

Na trhu sa vyskytuje značný počet návrhových riešení, ktoré sa zaoberajú touto problematikou, avšak drvivá väčšina riešení používa vstupný člen so striedavou väzbou pre pripojenie piezoelektrického akcelerometra k meraciemu systému. Tento prístup je jednoduchý a lacný, avšak má za následok rapídne zhoršenie vlastností vo veľmi nízkom spektre frekvencií, ako aj v ostatných frekvenčných pásmach, ak sa nepoužije dostatočne kvalitný kondenzátor vo väzbe.

Spoločnosť Analog Devices, v ktorej tento projekt vznikol sa rozhodla preskúmať práve prístup s jednosmernou väzbou, pri ktorom je očakávané rapídne zlepšenie presnosti a linearity. Tento prístup využíva techniku takzvaného posúvania napäťovej úrovne, keďže všetky piezoelektrické akcelerometre majú značne vysoké predpätie, s ktorým musí byť správne naložené. Práve dokonalé zvládnutie tejto techniky je jedna z hlavných výziev pre riešenia s týmto typom väzby. Návrh hardvéru bol vedený tak, aby sa s jednoduchosťou mohlo prechádzať medzi obidvomi väzbami, za účelom porovnania ich vlastností.

Ako aktívny vstupný člen - posúvač napäťovej úrovne, bolo zvolené invertujúce zapojenie operačného zosilňovača, ktorý sa v tomto prípade chová ako sumačný zosilňovač. Na neinvertujúci vstup sa privedie pohyblivé napätie z DAC prevodníka. Na invertujúci vstup je privedené napätie zo sensora, ktoré sa ďalej spracúva. Toto napätie pozostáva z jednosmerného predpätia a striedavého napätia ktoré je už priamo úmerné vibráciám.

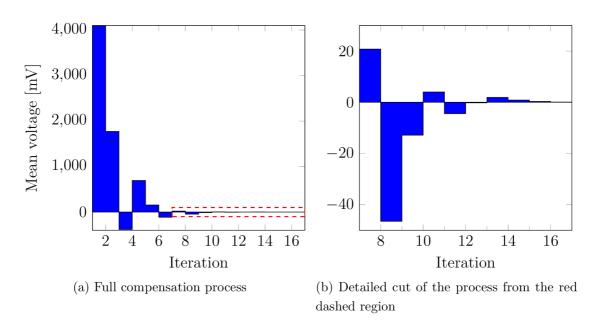

Pre posúvanie napäťovej úrovne bol zvolený DAC prevodník, ktorý umožňuje automatizáciu celého procesu. DAC prevodník vyvažuje vstupnú napäťovú asymetriu pomocou aktívnej kontrolnej slučky pozostávajúcej z ADC a DAC prevodníkov. Proces je podobný fungovaniu SAR ADC. Kdežto v tomto prípade sa nehľadá konečná hodnota neznámeho napätia ale minimalizuje sa stredné napätie pri vstupoch ADC prevodníka za účelom minimalizácie ofsetu.

Signál je navzorkovaný 24-bitovým sigma-delta ADC prevodníkom AD7768-1 s digitálnym postprocesingom. AD7768-1 bol zvolený hlavne kvôli linearite, nízkemu harmonickému skresleniu, nízkemu šumu a vhodnému frekvenčnému pásmu.

Frekvenčné pásmo, pomocou ktorého sa skúmajú defekty prístrojov, sa získa za použitia rýchlej Furiérovej transformácie FFT. Transformácia, ako aj všetky potrebné kalkulácie prebiehajú bez použitia osobného počítača, čo dodáva zariadeniu vyššiu flexibilitu. Celý dizajn ovláda mikrokontrolér s DSP modulom, na ktorom prebieha transformácia.

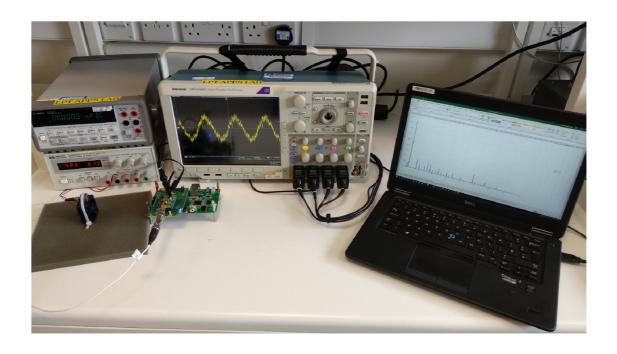

Aby sa potvrdilo, že Furiérova transformácia spolu so všetkými potrebnými kalkuláciami je správna, sada dát zachytených AD prevodníkom sa spracovala dvomi spôsobmi. Pomocou tohoto firmvéru, ktorý pracoval výhradne na mikrokontroléri

a pomocou firemného FFT jadra založeného na softvéri LabView, ponúkaného ako evaluačný softvér zákazníkom spoločnosti. Zhoda týchto dvoch spôsobov je zhrnutá v tabuľke 3.2 a dosahuje mimoriadnej presnosti ako to napríklad: rozdiel kalkulácie dynamického rozsahu je iba  $1 \, mdB$ .

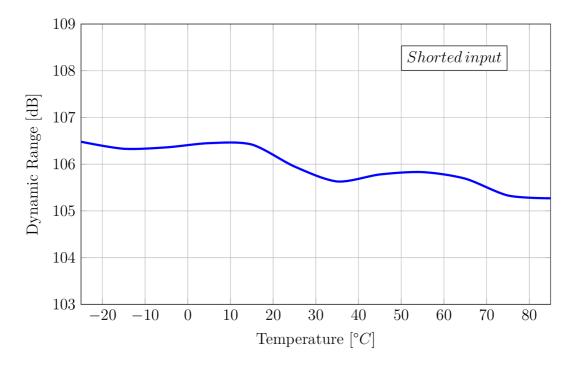

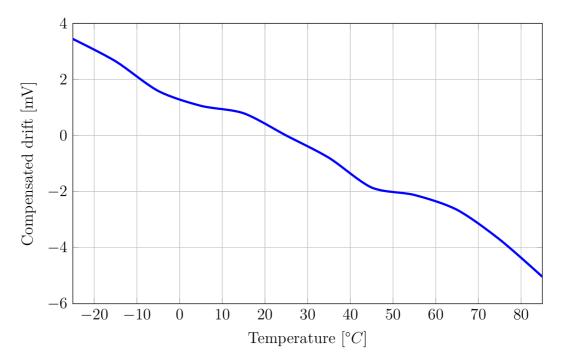

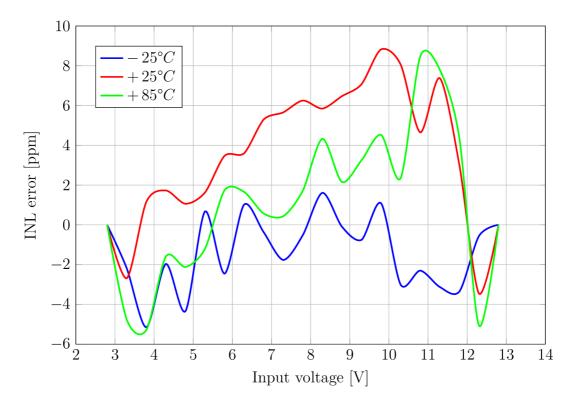

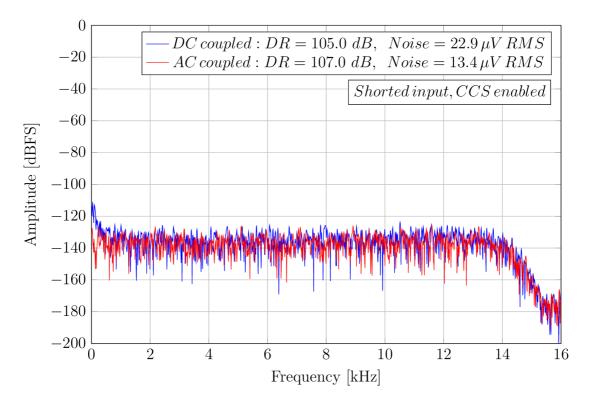

Vyhodnocovacie merania celého dizajnu naznačujú, tak ak sa očakávalo, že celkový integrovaný šum varianty s jednosmernou väzbou je vyšší. Nejde však o nejaký závratný nárast, keďže rozdiel v dynamickom rozsahu je iba  $1,7\,dB$  pre šírku pásma  $16\,kHz$  a teda celkový dynamický rozsah je lepší ako  $105,7\,dB$  pre obidve varianty na danej šírke pásma, čo je veľmi dobrý výsledok na tento pomerne zložitý analógový frontend, pričom dynamický rozsah samotného ADC so skratovanými vstupmi je podľa katalógového listu  $108,45\,dB$  pri zhodnej konfigurácii registrov. Jedná sa taktiež o meranie so skratovanými vstupmi celého riešenia.

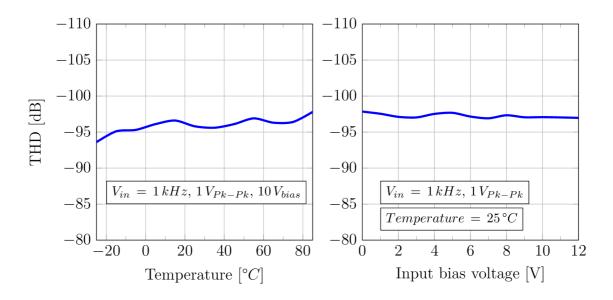

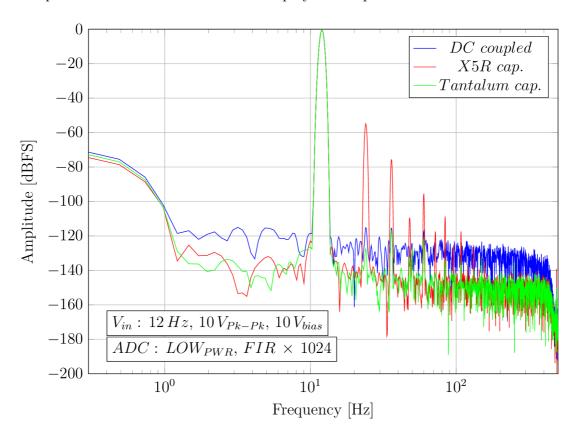

Pri meraní harmonického skreslenia sa prejavil efekt nesprávne zvoleného kondenzátora vo vstupnej striedavej väzbe, kde pri použití klasického keramického kondenzátora umiestneného v rozmerovo malom puzdre sa harmonické skreslenie zhoršilo o viac ako  $60\,dB$  oproti variante s jednosmernou väzbou, pričom frekvencia vstupného signálu bola ešte stále ďaleko v priepustnom pásme vstupného filtra.

Po výbere správneho typu kondenzátora sa úroveň harmonického skreslenia obidvoch variánt takmer vyrovnala s tým, že varianta s jednosmernou väzbou dosahovala lepšie výsledky. Spodná frekvenčná hranica použitého vstupného signálu bola limitovaná laboratórnou technikou na  $10\,Hz$  a medzná frekvencia vstupného filtru typu hornej priepuste bola experimentálne zvolená na hodnotu okolo  $1\,Hz$ . Táto konfigurácia umožňovala porovnávať rozdiely spôsobené rôznymi typmi väzieb a nie nastavením polohy medznej frekvencie. Fakt, že linearita, meraná amplitúda a šum sa znížia keď signál nebude v priepustnom pásme filtra je jasný a teda nebol ani overovaný meraním, keďže sa jedná o záležitosť nastavenia medznej frekvencie, čo nie je náplňou tejto práce.

Merania znázorňujúce detekciu defektov na zariadení boli vykonané len pre demonštráciu na malom ventilátore. Merania ukazujú dva typy defektov, a to nevyváženosť a nerovnováhu. Nerovnováha bola docielená pripevnením malého závažia na lopatku ventilátora.

#### **DECLARATION**

I declare that I have written the Master's Thesis titled "Accelerometer signal processing for vibration measurement" independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the thesis and listed in the comprehensive bibliography at the end of the thesis.

As the author I furthermore declare that, with respect to the creation of this Master's Thesis, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation  $\S 11$  of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll., Section 2, Head VI, Part 4.

| Brno | <br>               |

|------|--------------------|

|      | author's signature |

#### ACKNOWLEDGEMENT

I would like to thank Mr. prof. Ing. Vladislav Musil Ph. D. from my university: Brno University of Technology for professional guidance, consultation and suggested ideas, that helped me in the creation of this thesis.

Furthermore I would like to thank to my ex-colleagues from the company Analog Devices, where my thesis was created, with extensive assistance of those men. My special thanks belongs to Mr. Niall McGinley and to Mr. Naiqian Ren whom I owe for hours of explaining the secrets of analog circuit design and for being always happy to help me, to Mr. Sean Smith and Mr. Michael Bradley for huge support with firmware development and finally to supervisor Mr. Stuart Servis for giving me interesting job, permanent assistance, answering all my questions, explaining huge quantity of technical issues and enthusiasm for this project. I would never be able to finish my thesis and more importantly, to finish the work.

Thank you!

| Brno | <br>               |

|------|--------------------|

|      | author's signature |

# **Contents**

| In       | trodu | cion                                            |      | 16 |

|----------|-------|-------------------------------------------------|------|----|

| 1        | The   | oretical background                             |      | 17 |

|          | 1.1   | Types of defects                                |      | 17 |

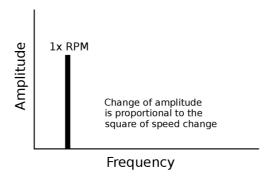

|          |       | 1.1.1 Imbalance                                 |      | 17 |

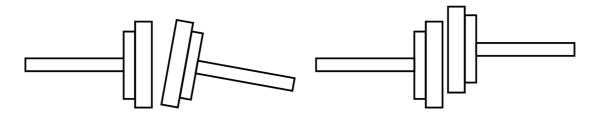

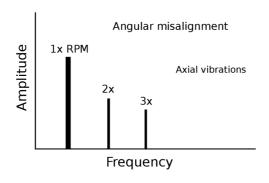

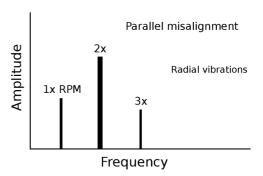

|          |       | 1.1.2 Misalignment                              |      | 18 |

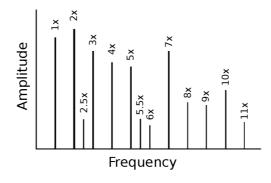

|          |       | 1.1.3 Looseness                                 |      | 19 |

|          | 1.2   | Frequency spectrum of interest                  |      | 20 |

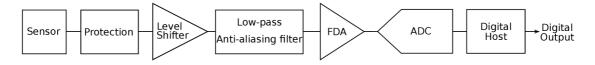

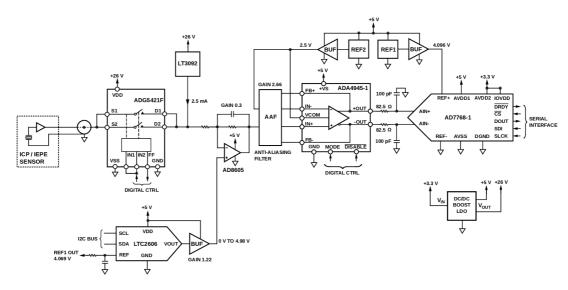

| <b>2</b> | Hare  | dware design                                    |      | 21 |

|          | 2.1   | High level design                               |      | 21 |

|          | 2.2   | The sensor                                      |      | 22 |

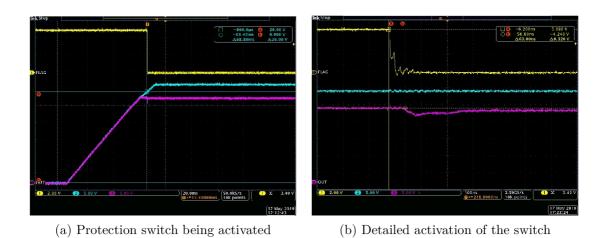

|          | 2.3   | Input protection                                |      | 24 |

|          | 2.4   | Constant current source                         |      | 25 |

|          |       | 2.4.1 Constant current source noise             |      | 26 |

|          | 2.5   | Input signal conditioning                       |      | 28 |

|          |       | 2.5.1 Coupling capacitor - AC coupling          | <br> | 28 |

|          |       | 2.5.2 Voltage level shifter - DC coupling       | <br> | 29 |

|          |       | 2.5.3 Level shifter requirements                | <br> | 29 |

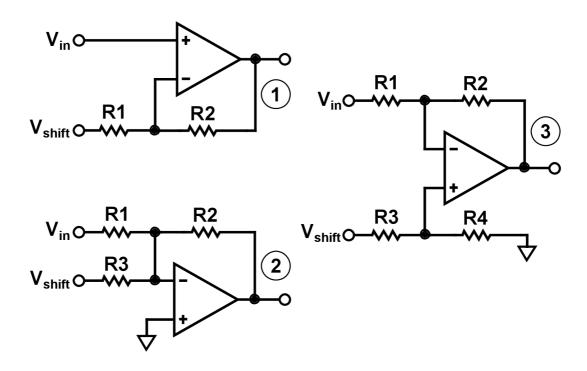

|          |       | 2.5.4 Topology of the voltage level shifter     | <br> | 30 |

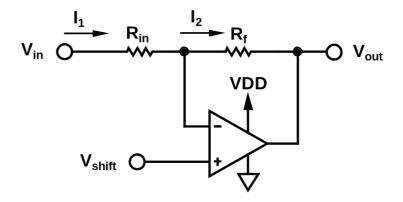

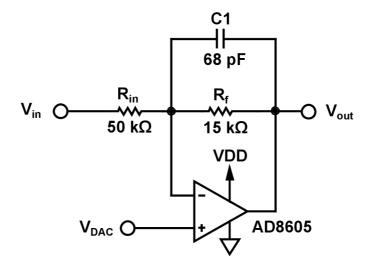

|          |       | 2.5.5 Design of the voltage level shifter       | <br> | 32 |

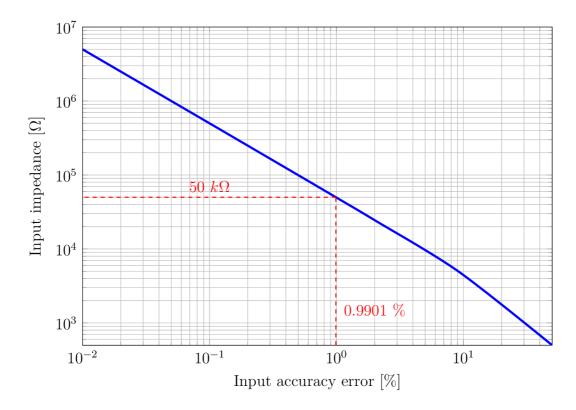

|          |       | 2.5.6 Input impedance                           | <br> | 33 |

|          |       | 2.5.7 First's stage noise calculation           | <br> | 35 |

|          |       | 2.5.8 First's stage noise bandwidth of interest | <br> | 37 |

|          |       | 2.5.9 First stage noise                         | <br> | 39 |

|          | 2.6   | Anti-aliasing filter                            | <br> | 40 |

|          | 2.7   | Level shifting DAC                              | <br> | 42 |

|          |       | 2.7.1 DAC buffer                                | <br> | 43 |

|          |       | 2.7.2 Stability of the DAC buffer               | <br> | 45 |

|          | 2.8   | Voltage reference                               | <br> | 45 |

|          | 2.9   | Analog to Digital Converter                     |      | 47 |

|          | 2.10  | Sensor bias compensating technique              |      | 48 |

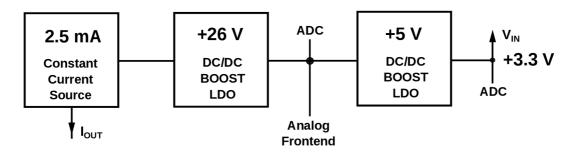

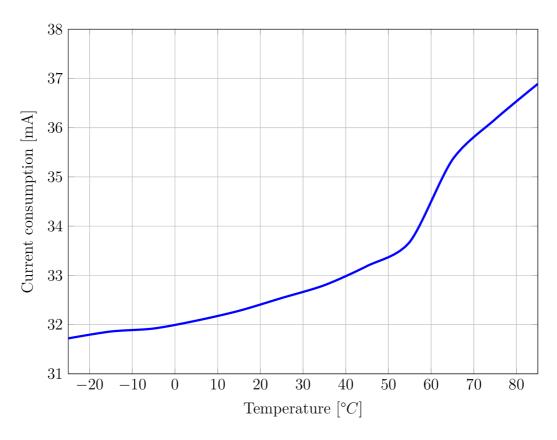

|          |       | Power supplies                                  |      | 50 |

| 3        | Firm  | nware design                                    |      | 51 |

|          | 3.1   | Frequency bin width                             |      | 51 |

|          | 3.2   | ADC data format                                 |      |    |

|   | 3.3                                                                                                              | FFT o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | n DSP                                                                                                                                                                                                                                                                                                  |      |                   |                   | 52                                                                          |

|---|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|-------------------|-----------------------------------------------------------------------------|

|   | 3.4                                                                                                              | FFT p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | re-processing                                                                                                                                                                                                                                                                                          |      |                   |                   | 53                                                                          |

|   |                                                                                                                  | 3.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Waveform statistics                                                                                                                                                                                                                                                                                    |      |                   |                   | 53                                                                          |

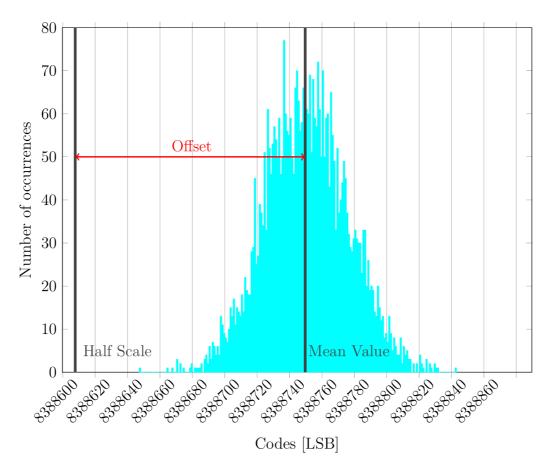

|   |                                                                                                                  | 3.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Offset of the ADC $\ \ldots \ \ldots \ \ldots \ \ldots$                                                                                                                                                                                                                                                |      |                   |                   | 54                                                                          |

|   |                                                                                                                  | 3.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Transition noise                                                                                                                                                                                                                                                                                       |      |                   |                   | 55                                                                          |

|   |                                                                                                                  | 3.4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Getting voltage from ADC codes $\dots \dots$                                                                                                                                                                                                                                                           |      |                   |                   | 55                                                                          |

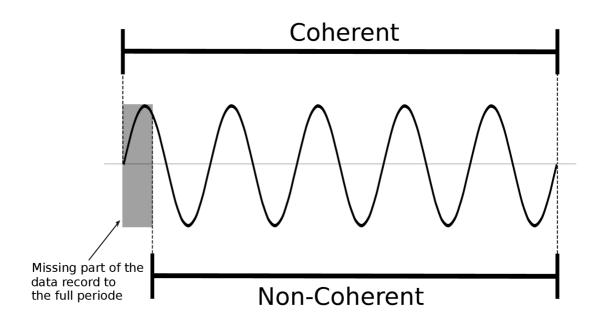

|   |                                                                                                                  | 3.4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Coherent sampling $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                 |      |                   |                   | 56                                                                          |

|   |                                                                                                                  | 3.4.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Windowing $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                           |      |                   |                   | 58                                                                          |

|   | 3.5                                                                                                              | FFT p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ost-processing                                                                                                                                                                                                                                                                                         |      |                   |                   | 61                                                                          |

|   |                                                                                                                  | 3.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Correction factor $\dots$                                                                                                                                                                                                                                                                              |      |                   |                   | 61                                                                          |

|   |                                                                                                                  | 3.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Magnitude - decibels conversion                                                                                                                                                                                                                                                                        |      |                   |                   | 62                                                                          |

|   |                                                                                                                  | 3.5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Spectral leakage correction                                                                                                                                                                                                                                                                            |      |                   |                   | <br>63                                                                      |

|   |                                                                                                                  | 3.5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Distinguishing bins                                                                                                                                                                                                                                                                                    |      |                   |                   | <br>64                                                                      |

|   |                                                                                                                  | 3.5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Picking up the fundamental frequency $\dots$                                                                                                                                                                                                                                                           |      |                   |                   | <br>65                                                                      |

|   |                                                                                                                  | 3.5.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | THD calculation                                                                                                                                                                                                                                                                                        |      |                   |                   | <br>65                                                                      |

|   |                                                                                                                  | 3.5.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Folding of the harmonics                                                                                                                                                                                                                                                                               |      |                   |                   | <br>65                                                                      |

|   |                                                                                                                  | 3.5.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Noise parameters calculation                                                                                                                                                                                                                                                                           |      |                   |                   | <br>67                                                                      |

|   | 3.6                                                                                                              | Data r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | eception                                                                                                                                                                                                                                                                                               |      |                   |                   | <br>69                                                                      |

|   | 3.7                                                                                                              | Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s evaluation                                                                                                                                                                                                                                                                                           |      |                   |                   | <br>71                                                                      |

|   |                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                        |      |                   |                   |                                                                             |

| 4 | Eval                                                                                                             | luation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | n measurements                                                                                                                                                                                                                                                                                         |      |                   |                   | 73                                                                          |

| 4 | <b>Eva</b> l 4.1                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | n measurements  noise of the signal chain                                                                                                                                                                                                                                                              | <br> |                   |                   | <br><b>73</b> 73                                                            |

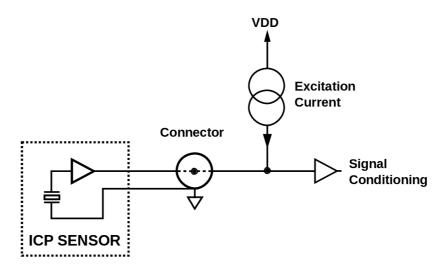

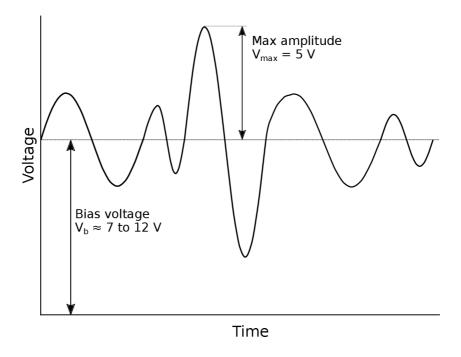

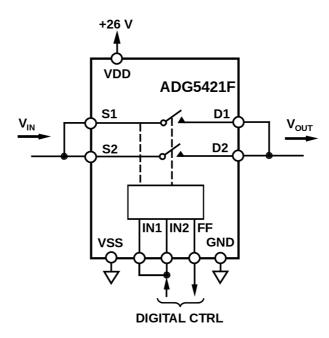

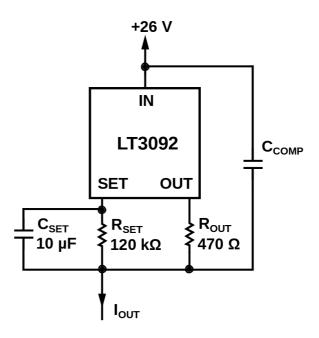

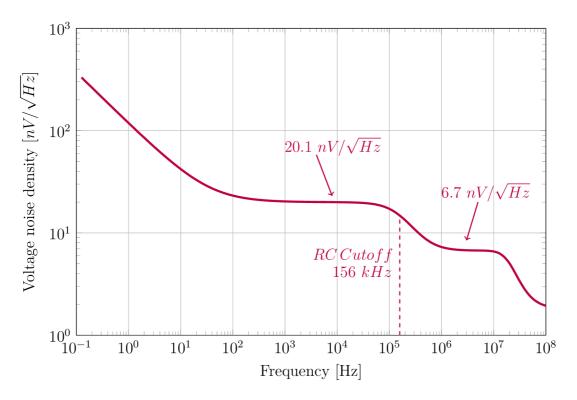

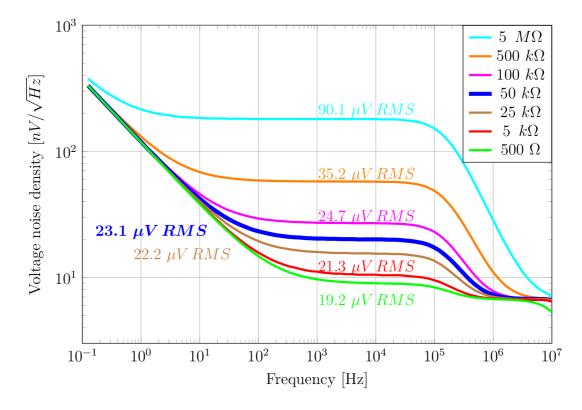

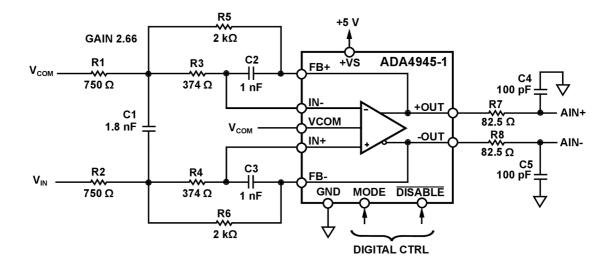

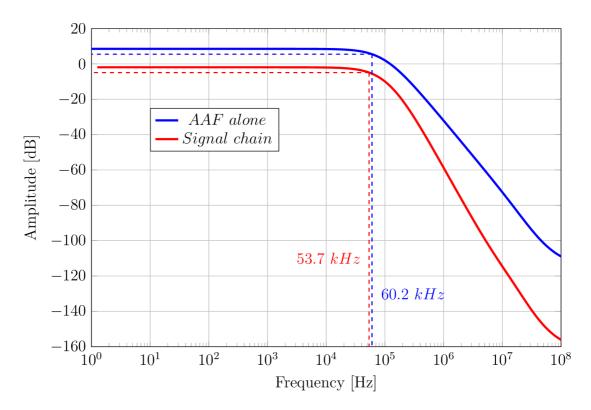

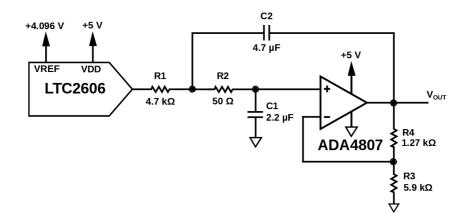

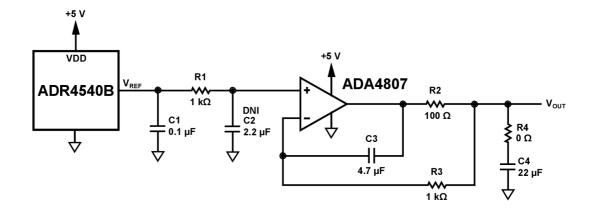

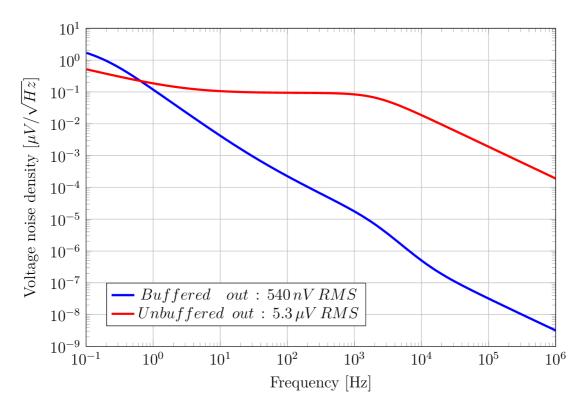

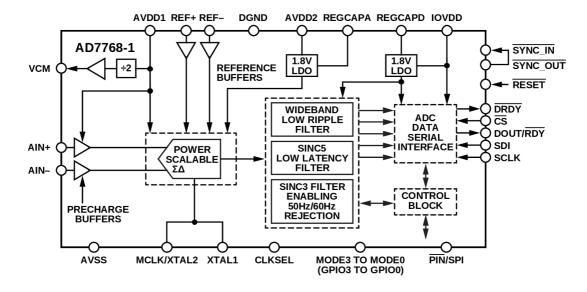

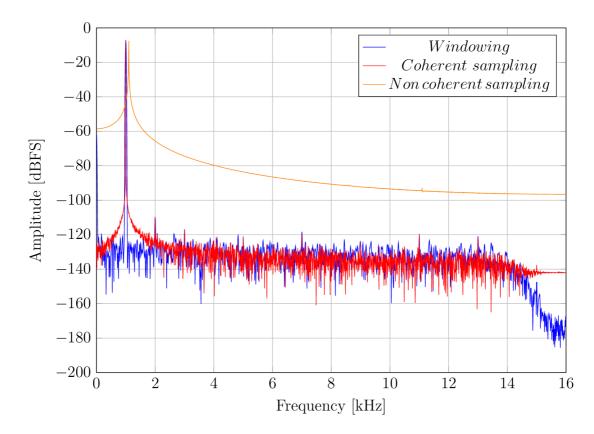

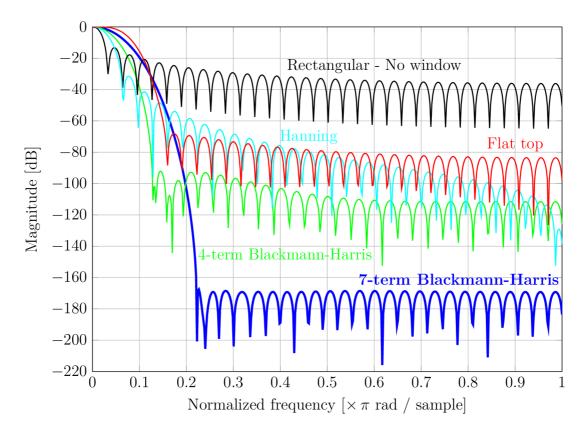

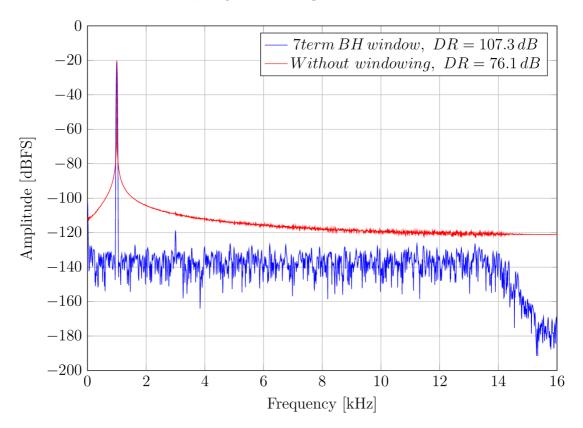

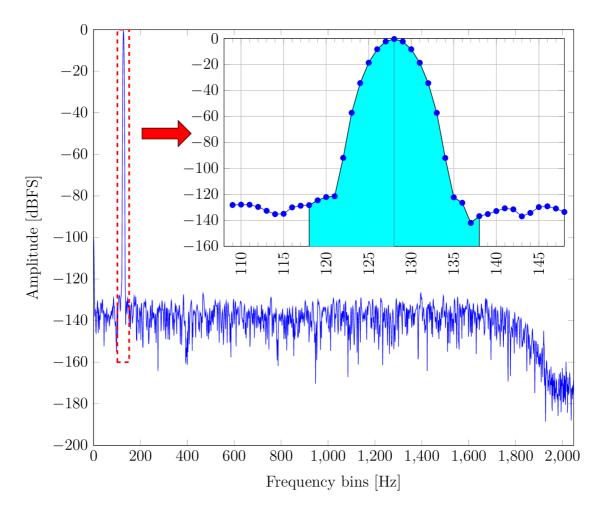

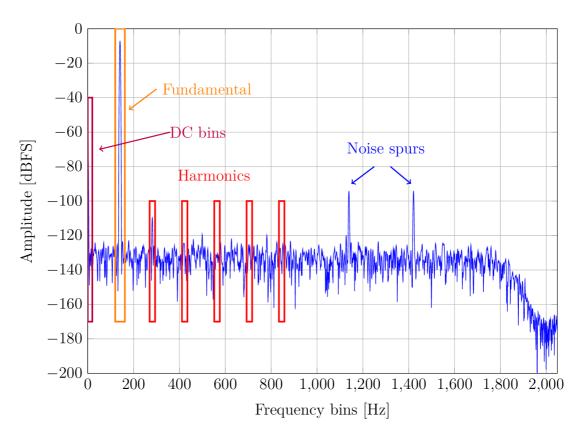

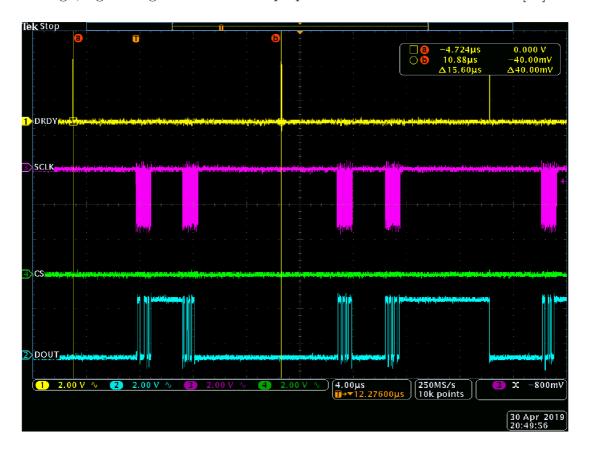

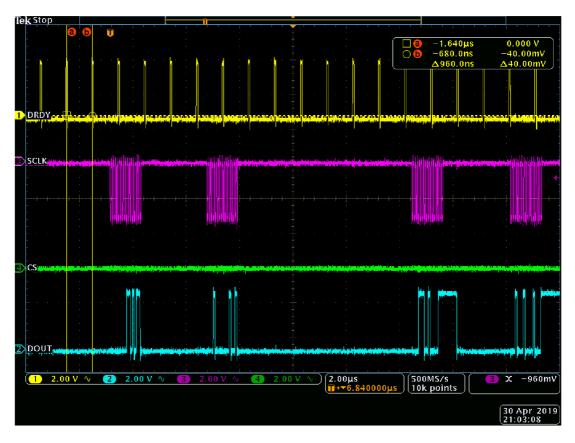

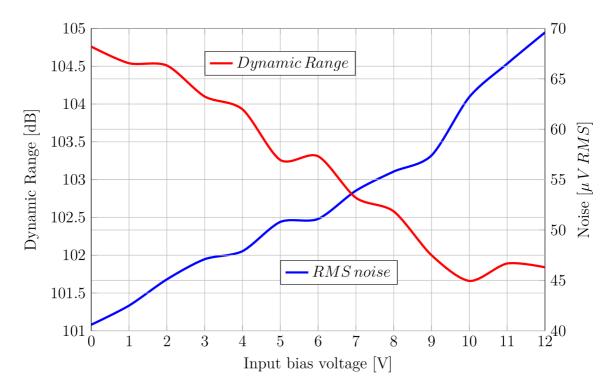

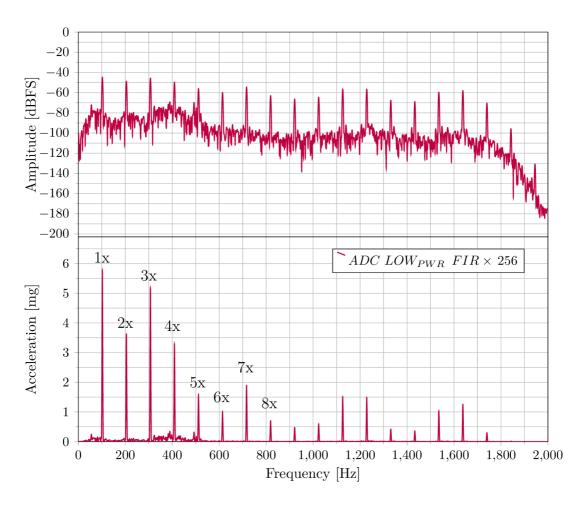

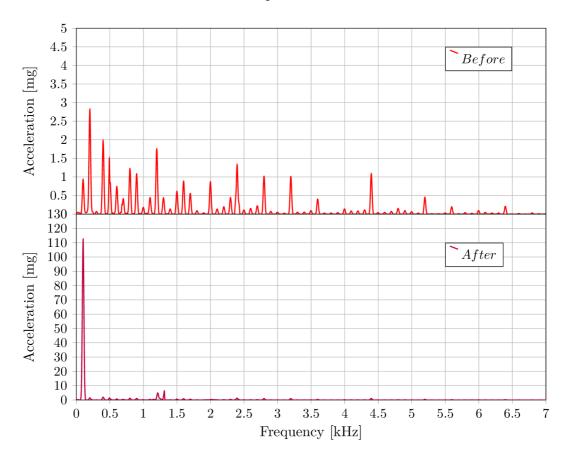

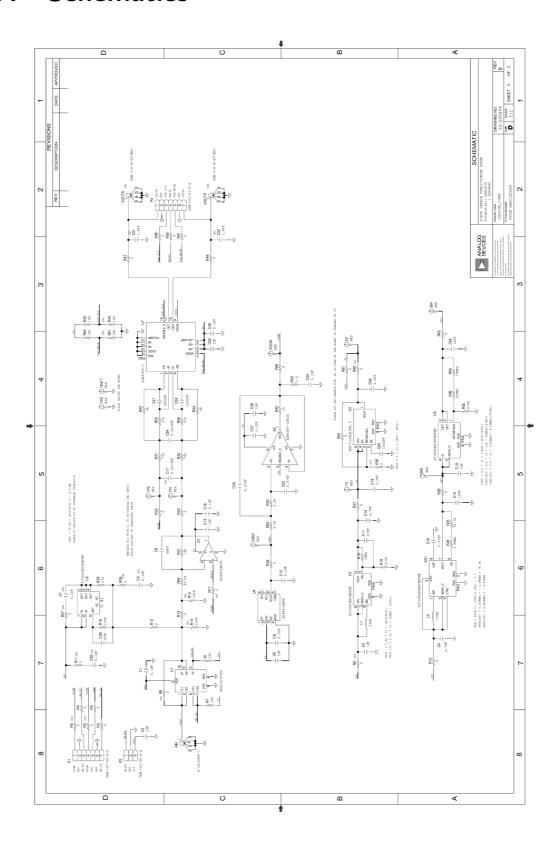

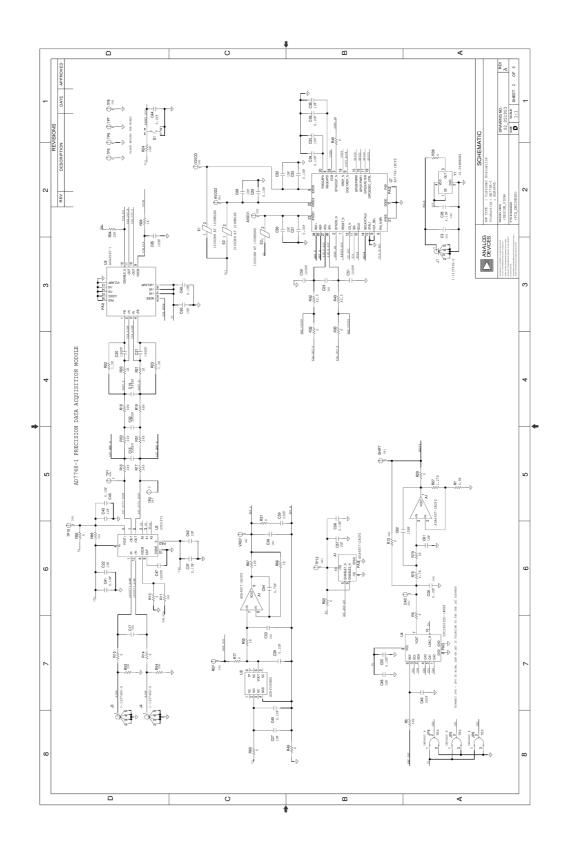

| 4 |                                                                                                                  | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | n measurements  noise of the signal chain                                                                                                                                                                                                                                                              |      |                   |                   |                                                                             |