# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

## DEPARTMENT OF RADIOENGINEERING

ÚSTAV RADIOELEKTRONIKY

# THERMAL CAMERA FOR BIOLOGICAL APPLICATIONS

TERMÁLNÍ KAMERA PRO BIOLOGICKÉ APLIKACE

#### **MASTER'S THESIS**

DIPLOMOVÁ PRÁCE

AUTHOR

**AUTOR PRÁCE**

Bc. Jáchym Macura

SUPERVISOR VEDOUCÍ PRÁCE

Ing. Michal Kubíček, Ph.D.

**BRNO 2020**

# **Master's Thesis**

#### Master's study field Electronics and Communication

Department of Radioengineering

Student: Bc. Jáchym Macura ID: 164327

Year of 2 Study: Academic year: 2019/20

**TITLE OF THESIS:**

#### Thermal camera for biological applications

#### **INSTRUCTION:**

Study properties and get acquainted with analog thermal detector BIRD17-XGA. Design a camera based on this sensor. The primary purpose of the camera is monitoring of activity of plat's stomata. The detector should be controlled using an FPGA and will utilize standard camera subsystems used within PSI company. To control the camera create suitable HDL IP cores for target FPGA. To complete the design write also basic software modules for Linux operating system, including TCP server for communication with a PC. Integrate the software into PSI company internal generic camera platform and verify its functionality.

#### **RECOMMENDED LITERATURE:**

[1] VOLLMER, Michael a Klaus-Peter MOLLMANN. Infrared thermal imaging: fundamentals, research and applications. Weinheim: Wiley-VCH, c2010. ISBN 3527407170.

[2] UNSALAN, Cem a Bora TAR. Digital system design with FPGA: implementation using Verilog and VHDL / Cem Unsaln, Yeditepe University, Bora Tar, The Ohio State University. New York, NY: McGraw-Hill Education, [2017]. ISBN 9781259837906.

Date of project specification:

3.2.2020

Deadline for submission: 28.5.2020

Supervisor: Ing. Michal Kubíček, Ph.D.

prof. Ing. Tomáš Kratochvíl, Ph.D. Subject Council chairman

#### WARNING:

The author of the Master's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

#### **ABSTRACT**

This master thesis describes the process of designing a thermal camera for biological applications. The first part describes infrared radiation, also known as thermal radiation. It goes on to describe an emissivity of objects, which plays an important role in determining the temperature of the object. The end of first chapter overviews the types of thermal detectors and their basic properties. The second chapter briefly introduces the basic hardware components of the developed camera. The last chapter describes the process of software development. This includes the development of IP cores, kernel modules and C++ libraries.

#### **KEYWORDS**

Thermal camera, VHDL, Kernel module, C++, Qt

#### **ABSTRAKT**

Diplomová práce se zabývá návrhem termální kamery pro biologické aplikace. V první části je popsáné infračervené záření, také známé jako thermální záření. Pokračuje popisem emisivity objektů, která hraje důležitou roli při stanovení teploty snímaného objektu. Dále je v první kapitole uveden přehled typů termálních detektorů a jejich základní vlastnosti. Druhá kapitola stručně seznamuje se zákládními hardwarovými komponenty vyvíjené kamery. V poslední kapitole je popsán celý proces vývoje softwaru. Ten zahrnuje vývoj IP jader, kernel modulů a C++ knihoven.

### KLÍČOVÁ SLOVA

Termální kamera, VHDL, Kernel modul, C++, Qt

MACURA, Jáchym. *Thermal camera for biological applications*. Brno, 2019/2020, 80 p. Master's Thesis. Brno University of Technology, Fakulta elektrotechniky a komunikačních technologií, Ústav radioelektroniky. Advised by Ing. Michal Kubíček, Ph.D.

Typeset by the thesis package, version 3.05; http://latex.feec.vutbr.cz

#### **DECLARATION**

I declare that I have written the Master's Thesis titled "Thermal camera for biological applications" independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the thesis and listed in the comprehensive bibliography at the end of the thesis.

As the author I furthermore declare that, with respect to the creation of this Master's Thesis, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation  $\S 11$  of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll., Section 2, Head VI, Part 4.

| Brno | <br>               |

|------|--------------------|

|      | author's signature |

# **Contents**

| IN | TRO | DDUC    | TION                                          | 11   |

|----|-----|---------|-----------------------------------------------|------|

| 1  | INF | RARI    | ED RADIATION AND THERMAL DETECTORS            | 12   |

|    | 1.1 | Infrare | ed radiation                                  | . 12 |

|    |     | 1.1.1   | Thermal Radiation                             | . 13 |

|    |     | 1.1.2   | Black-Body                                    | . 14 |

|    |     | 1.1.3   | Emissivity                                    | . 17 |

|    | 1.2 | Therm   | novision and IR Detectors                     | . 19 |

|    |     | 1.2.1   | Thermovision                                  | . 19 |

|    |     | 1.2.2   | IR Detectors                                  | . 20 |

|    |     | 1.2.3   | Photon Detectors                              | . 20 |

|    |     | 1.2.4   | Thermal Detectors                             | . 21 |

|    | 1.3 | Paran   | neters That Characterize Detector Performance | . 22 |

|    |     | 1.3.1   | Responsivity                                  | . 22 |

|    |     | 1.3.2   | NETD                                          | . 22 |

|    |     | 1.3.3   | Defective Pixels                              | . 22 |

| 2  | Har | dware   |                                               | 23   |

|    | 2.1 | Uncoc   | oled BIRD17-XGA Detector                      | . 23 |

|    | 2.2 | Zynq-   | 7000 and MicroZed board                       | . 25 |

|    |     | 2.2.1   | Processing System                             | . 25 |

|    |     | 2.2.2   | Programmable Logic                            | . 26 |

|    |     | 2.2.3   | Advanced eXtensible Interface                 | . 26 |

|    |     | 2.2.4   | MicroZed board                                | . 27 |

|    |     | 2.2.5   | LTC2387-16                                    | . 28 |

|    |     | 2.2.6   | AD7680                                        | . 28 |

| 3  | Sof | tware   |                                               | 29   |

|    | 3.1 | AXI4-   | -Stream                                       | . 30 |

|    | 3.2 | DMA     | Controller and DMAENG                         | . 31 |

|    |     | 3.2.1   | DMA Controller                                | . 31 |

|    |     | 3.2.2   | DMAENG                                        | . 32 |

|    |     | 3.2.3   | Performance test                              | . 33 |

|    | 3.3 | ADC     | Interface                                     | . 34 |

|    |     | 3.3.1   | LTC2387_v1 IP core                            | . 36 |

|    |     | 3.3.2   | ltc2387drv library                            | . 39 |

|    | 3.4 | XGA     | Interface                                     | . 40 |

|              |                         | 3.4.1 XGA Video Interface                                                                   | 40             |

|--------------|-------------------------|---------------------------------------------------------------------------------------------|----------------|

|              |                         | 3.4.2 XGA communication interface                                                           | 43             |

|              | 3.5                     | $ Temperature \ stabilization  . \ . \ . \ . \ . \ . \ . \ . \ . \ .$                       | 48             |

|              |                         | 3.5.1 Temperature reading                                                                   | 48             |

|              |                         | 3.5.2 TEC driver                                                                            | 50             |

|              |                         | 3.5.3 PID controller                                                                        | 51             |

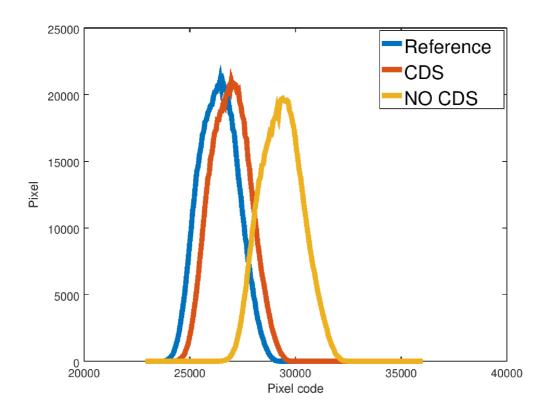

|              | 3.6                     | CDS calibration                                                                             | 53             |

|              |                         | 3.6.1 CDS_v1.0 IP core                                                                      | 53             |

|              | 3.7                     | Non-Uniform Correction                                                                      | 56             |

|              |                         | 3.7.1 NUC calibration                                                                       | 57             |

|              |                         | 3.7.2 NUC Hierarchy                                                                         | 58             |

|              | 3.8                     | Bad Pixels Replacement                                                                      | 60             |

|              |                         | 3.8.1 DeadPixel class                                                                       | 60             |

|              | 3.9                     | $XGA\_control\_app \ \ldots \ \ldots$ | 60             |

|              |                         | 3.9.1 PsiProtServer class                                                                   | 60             |

|              |                         | 3.9.2 PsiProtParser class                                                                   | 60             |

|              |                         | 3.9.3 XgaBird class                                                                         | 61             |

|              | 3.10                    | Resource utilization                                                                        | 62             |

|              | 3.11                    | Graphical User Interface                                                                    | 63             |

| Co           | onclu                   | sion                                                                                        | 64             |

| Bi           | bliog                   | graphy                                                                                      | 66             |

| Li           | st of                   | symbols, physical constants and abbreviations                                               | 69             |

| Li           | st of                   | appendices                                                                                  | 71             |

| $\mathbf{A}$ | Exa                     | mple IR images                                                                              | 72             |

| В            | Viv                     | ado block desing and test benches                                                           | 74             |

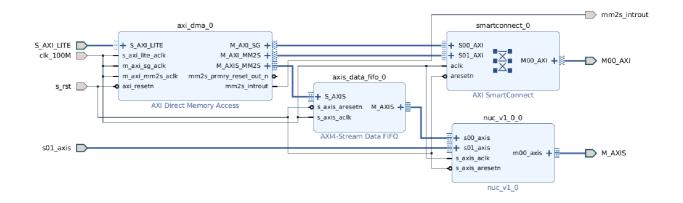

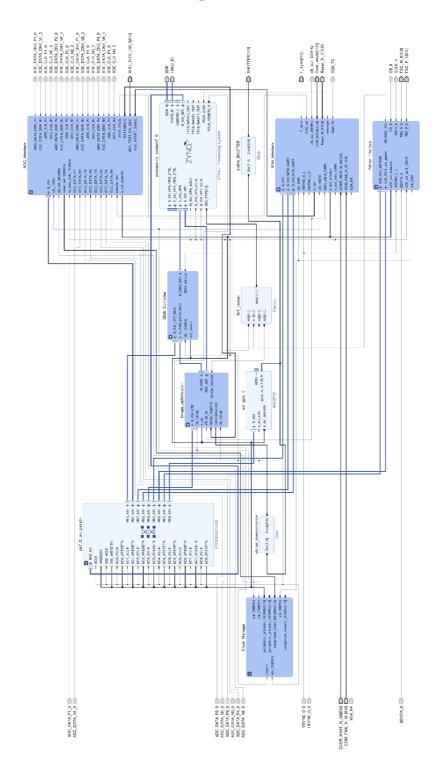

|              | B.1                     | Vivado Block Design                                                                         | 71             |

|              | D.1                     | Vivado Biodi Boligii                                                                        | 74             |

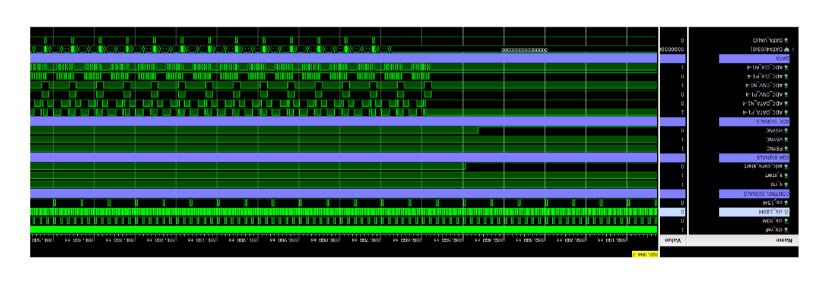

|              | B.2                     | XGA_driver_v2 + LTC2387_v1 Test Bench                                                       | 74<br>75       |

|              |                         |                                                                                             |                |

|              | B.2<br>B.3              | $XGA\_driver\_v2 + LTC2387\_v1$ Test Bench                                                  | 75             |

| $\mathbf{C}$ | B.2<br>B.3<br>B.4       | XGA_driver_v2 + LTC2387_v1 Test Bench XGA_UART_Synchronisation_v1_0 Test Bench              | 75<br>76       |

| <b>C D</b>   | B.2<br>B.3<br>B.4<br>IR | XGA_driver_v2 + LTC2387_v1 Test Bench                                                       | 75<br>76<br>77 |

# List of Figures

| 1.1  | Total radiant power                                | 13 |

|------|----------------------------------------------------|----|

| 1.2  | Radiance of the Black-Body                         | 15 |

| 1.3  | Black-Body's radiation as function of $\lambda T$  | 16 |

| 1.4  | Spectral emissivity                                | 18 |

| 1.5  | Examples of Thermovision                           | 19 |

| 2.1  | HW block schematic of IR camera                    | 23 |

| 2.2  | SCD BIRD17-XGA IR Detector                         | 24 |

| 2.3  | Wheatstone bridge and Read out circuit             | 24 |

| 2.4  | Zynq Processing System                             | 25 |

| 2.5  | MicroZed board                                     | 28 |

| 3.1  | SW block diagram                                   | 29 |

| 3.2  | AXI4-Stream diagram                                | 30 |

| 3.3  | Block diagram of the DMA Controller                | 31 |

| 3.4  | Vivado DMA test design                             | 33 |

| 3.5  | Data generator and generated pattern               | 34 |

| 3.6  | LTC2386-16 Timing diagram                          | 35 |

| 3.7  | LTC2387_v1 FSM                                     | 36 |

| 3.8  | Test bench of timing synchronization               | 37 |

| 3.9  | Captured data of the timing synchronization by ILA | 38 |

| 3.10 | ADC Interface Hierarchy                            | 39 |

| 3.11 | General frame timing                               | 40 |

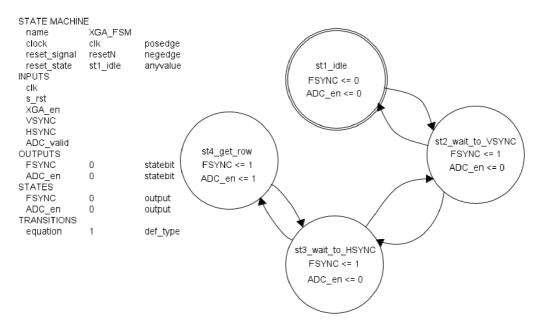

| 3.12 | XGA_driver_v2 finite state machine                 | 41 |

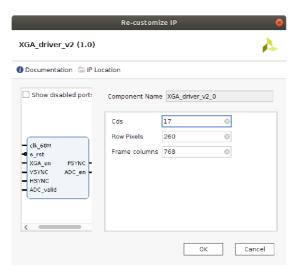

| 3.13 | Customized IP – XGA_driver_v2                      | 42 |

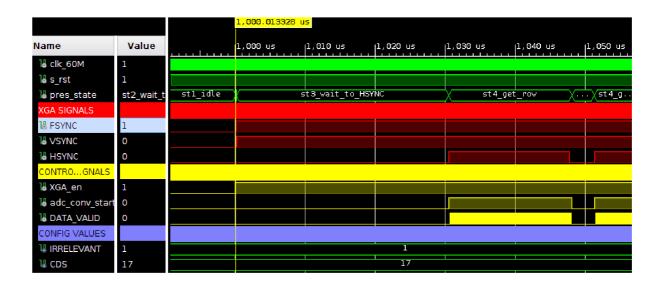

| 3.14 | Test bench of the XGA_driver_v2                    | 42 |

| 3.15 | Auto-detect flowchart                              | 44 |

| 3.16 | XGA UART Hierarchy                                 | 45 |

| 3.17 | XGA Message and Response Protocol                  | 45 |

| 3.18 | The first taken photo                              | 47 |

| 3.19 | AD7680_v1.0 IP core                                | 49 |

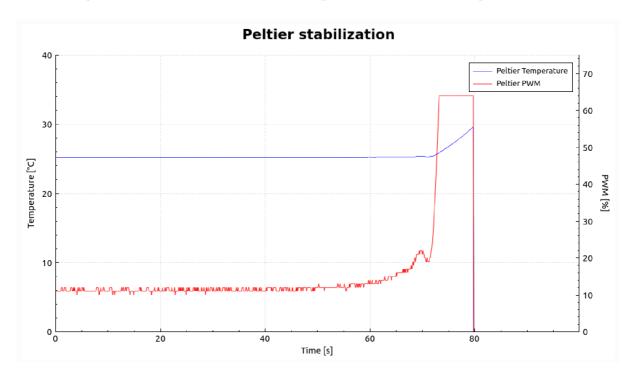

| 3.20 | TEC (Peltier) stabilization                        | 52 |

| 3.21 | ROIC amplifiers                                    | 54 |

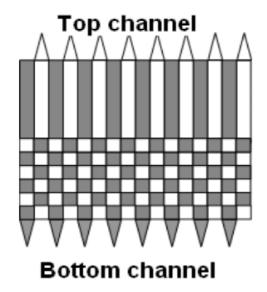

| 3.22 | CDS correction                                     | 54 |

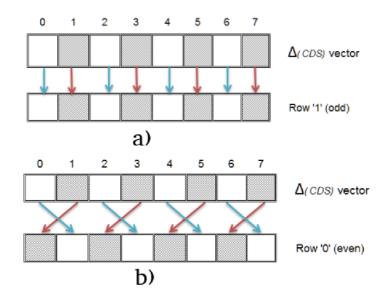

| 3.23 | CDS vs. NO CDS signal                              | 55 |

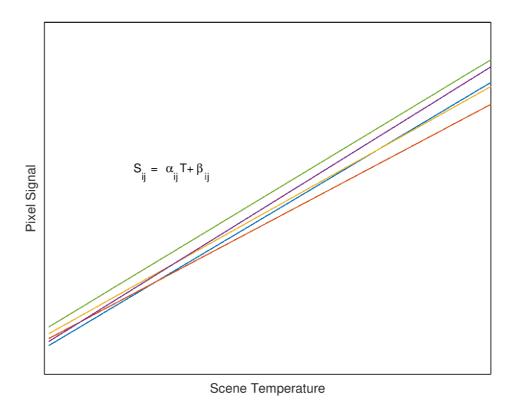

| 3.24 | Pixel Signal vs. Scene Temperature                 | 56 |

|      | NUC calibration process                            | 58 |

| 3.26 | NUC Hierarchy                                      | 59 |

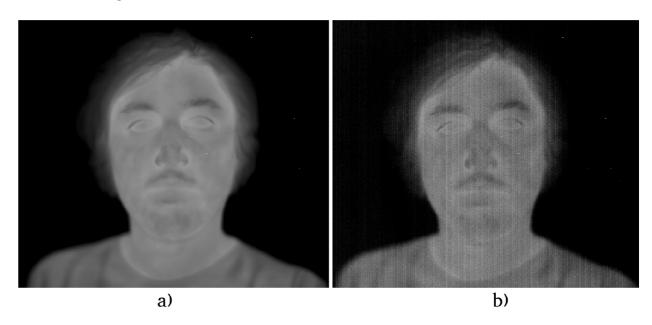

|      | Image quality improvement by NUC                   | 59 |

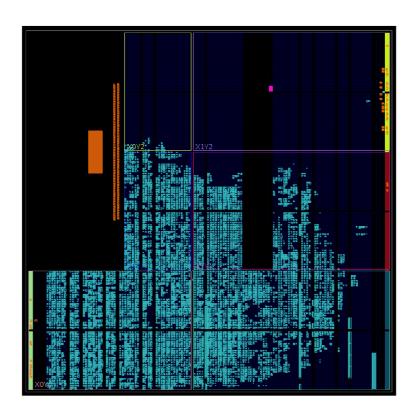

| 3.28 | FPGA floor-planning view after implementation 62 |

|------|--------------------------------------------------|

| 3.29 | GUI - IR viewer                                  |

| A.1  | IR image - flower with sick leafs (grayscale)    |

| A.2  | IR image - flower with sick leafs (colorscale)   |

| A.3  | IR image - veins (greyscale)                     |

| A.4  | IR image - veins (colorscale)                    |

| В.1  | Final Vivado Block Design                        |

| B.2  | $XGA\_driver\_v2 + LTC2387\_v1$ Test Bench       |

| В.3  | XGA_UART_Synchronisation_v1_0 Test Bench         |

| B.4  | axi_pwm_v1.0 Test Bench                          |

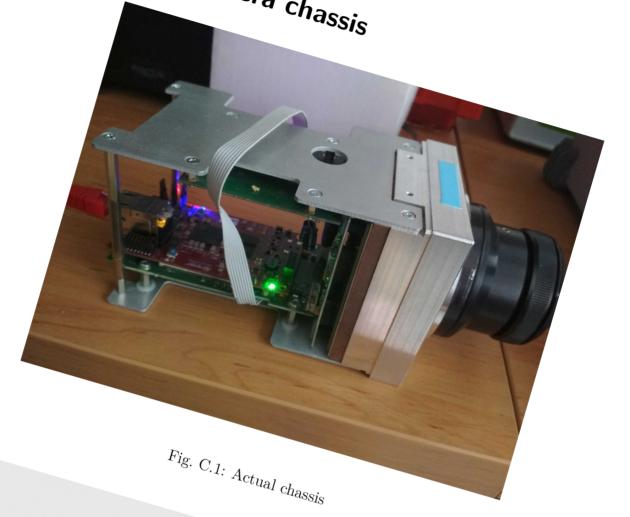

| C.1  | Actual chassis                                   |

| C.2  | Upgraded chassis                                 |

| D.1  | Black-Body                                       |

|      |                                                  |

# **List of Tables**

| 1.1 | Infrared spectral ranges         | 12 |

|-----|----------------------------------|----|

| 1.2 | Example of band emission         | 16 |

| 1.3 | Example of material emissivity   | 18 |

| 3.1 | DMA Kernel driver attributes     | 33 |

| 3.2 | XGA UART parameters              | 43 |

| 3.3 | Temperature-Diode Specifications | 48 |

| 3.4 | AD7680_v1 AXI4-Lite interface    | 49 |

| 3.5 | axi_pwm_v1.0 AXI4-Lite interface | 50 |

| 3.6 | axi_pwm_v1.0 AXI4-Lite interface | 51 |

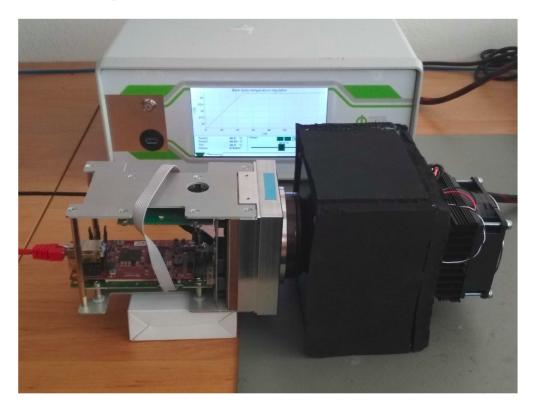

| 3.7 | Custom Black Body parameters     | 57 |

| 3.8 | FPGA resource utilization        | 62 |

# Listings

| 3.1 | XGA   | control  | app main loop |   |   |   |   |   |   |   |   |   |   |   |       |   |   |   |   |   |   |   |   | 6 | ; 1 |

|-----|-------|----------|---------------|---|---|---|---|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|---|---|-----|

| 0.1 | 11011 | COLLULOI |               | • | • | • | • | • | • | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | • |   | , , |

# INTRODUCTION

Infrared thermal imaging, also called thermography is applied in research and development such as nondestructive testing, predictive maintenance and in many more areas.

This master thesis goal is a design of a thermal camera for non-invasive measurement in biological application. First chapter of this thesis is focused on describing of the infrared radiation and detailed back-ground information about important parameters like emissivity. Next part of this chapter describes thermovision and its use in the real world. Thermovision topic also includes division and description of thermal detectors and their characteristic parameters.

The second chapter is devoted to get reader familiar with the individual electronic components of developed thermal camera. The hardware of the camera was supplied by the contracting company Photon Systems Instruments (PSI). Most attention is devoted to the heart of the camera which is XGA-Bird17 - an infrared bolometric detector and the brain, which is SoC Xilinx Zynq.

The last chapter called Software describes step by step the development of a camera control system. The chapter is divided into following parts:

- Ensuring high data throughput for video stream between Zynq programmable logic and processing system.

- Interfacing with high speed external components.

- Temperature stabilization of XGA-Bird17 detector.

- Image quality improving by Correlated Double-Sampling correction, Non-Uniformity Correction and Bad Pixels Replacement.

- Graphical User Interface for TCP communication with the camera.

# 1 INFRARED RADIATION AND THERMAL DETECTORS

This chapter describes the basics of InfraRed (IR) and thermal radiation. This chapter continues acquainting the reader with cooled and uncooled thermal detectors and their parameters.

# 1.1 Infrared radiation

IR radiation or IR light is type of an energy that is invisible to the human eyes but that can be felt as heat. IR is type of the electromagnetic (EM) radiation same as (lowest to highest wavelength) gamma-rays, X-rays, ultraviolet radiation, visible light, infrared radiation, microwaves and radio waves. Together, these types of radiation make up the electromagnetic spectrum which can be described as particles, or more common, as EM waves. The wavelength ( $\lambda$ ) of IR spectrum is in range from 0.78 µm to 1 mm. With known speed of propagation (c<sup>1</sup> = 299792458 m/s) the frequency (f) in Hertz (Hz) can be calculated using Eq.1.1.

$$f = \frac{\lambda}{c} \tag{1.1}$$

The frequency domain, boundary of IR spectrum is approximately from 300 GHz to 400 THz. From this huge bandwidth only a small range is used for thermal imaging. Typically, three spectral ranges (Tab.1.1) are defined for thermal imaging (thermography).

Tab. 1.1: Infrared spectral ranges

| Spectral range | Short | Wavelength [µm] |

|----------------|-------|-----------------|

| Short-wave     | SWIR  | 0.9 - 1.7       |

| Mid-wave       | MWIR  | 3 - 5           |

| Long-wave      | LWIR  | 8 - 14          |

<sup>&</sup>lt;sup>1</sup>Speed of propagation depends on index of refraction but in this text it is assumed as a constant.

# 1.1.1 Thermal Radiation

Every object with temperature higher than absolute zero emits thermal radiation. Radiation power that can be emitted depends on the temperature of the object and on the wavelength (Planck's law - more description in Black-Body section). The element with radiation surface dA generates total energy flux  $d\phi$ , also called radiant power M [Wm<sup>-2</sup>] (Eq.1.2).

$$M = \frac{d\phi}{dA} \tag{1.2}$$

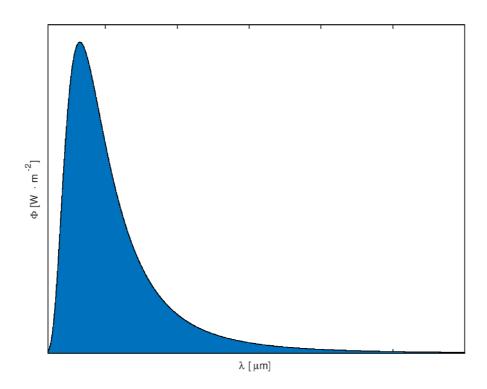

Eq.1.2 is simplified by using total derivatives of all emitted wavelengths and radiant angles. Resulting sum of all wavelength energies for Eq.1.2 is shown in Figure 1.1.

Fig. 1.1: Total radiant power

## 1.1.2 Black-Body

Black-Body is a theoretical perfect emitter of thermal radiation, that is able to emit the maximum radiant power which depends only on the body temperature. For the object to be called Black-Body, it must meet these conditions:

- Black-body has to absorb all incident radiation, regardless on wavelength or direction.

- No object can emit more radiation than Black-Body with the same temperature and wavelength.

- Emitted radiation of Black-Body depends only on wavelength but not on the direction.

#### Planck's law, Wien's law and Stefan-Boltzmann law

Planck's law describes the spectral density of EM radiation emitted by the Black-Body, when there is no net flow of energy between the body and its environment. Planck's law Eq.1.3 defines the intensity of radiation for the Black-Body as a function of temperature and wavelength.

$$M_{\lambda}(T)d\lambda = \frac{2\pi hc^2}{\lambda^5} \cdot \frac{1}{e^{hc/(\lambda kT)} - 1} d\lambda$$

(1.3)

.

where  $h = 6.626 \cdot 10^{-34}$  [J·s] is the Planck's constant, c [m/s] is the speed of light in vacuum,  $\lambda$  [m] is the wavelength of the radiation, T [K] is the absolute temperature of the Black-Body and  $k = 1.38 \cdot 10^{-23}$  [J·K<sup>-1</sup>] is the Boltzmann constant.

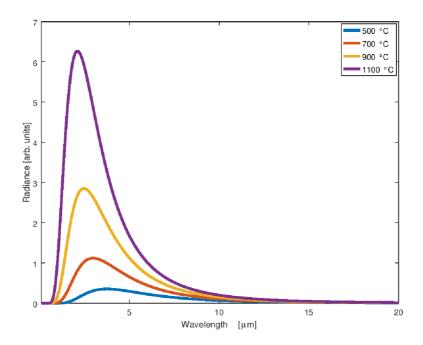

Figure 1.2 shows plot of several curves depending on the wavelength. Each curve represents the energy distribution at different temperature. Based on Fig.1.2, 2 rules can be derived:

- If temperature increases, the intensity of radiation increases.

- If the temperature of an object increases, the peak intensity moves to shorter wavelengths.

With usage of these rules, we can observe this phenomenon by slowly heating a piece of metal. At room temperature, the metal does not emit any light visible to the human eye. However, if it's heated to approximately 500°C, it begins to glow red. At 500°C, the metal emits visible light primarily in the red portion of the visible spectrum. As the temperature of the metal increases to approximately 1500°C, it begins to glow with white color. At 1500°C, the metal emits energy at all visible wavelengths. White light is the combination of all visible colors.[3]

Fig. 1.2: Radiance of the Black-Body

With condition  $dM_{\lambda}(T)/d\lambda = 0$ , it's possible to locate wavelength with maximal intensity. This leads to Wien's displacement law Eq.1.4:

$$\lambda_{peak} = \frac{b}{T} \tag{1.4}$$

Where T [K] is absolute temperature, b is Wien's displacement constant, equal to 2898  $[\mu m \cdot K]$ .

The excitance of the Black-Body source can be calculated from Eq.1.5, that is so called Stefan–Boltzmann law.

$$M(T) = \int_0^\infty M_\lambda(T) d\lambda = \sigma T^4 \tag{1.5}$$

Where  $\sigma = 5.69 \cdot 10^{-8} \ [Wm^{-2}K^{-4}]$  is the Stefan-Boltzmann constant and  $T \ [K]$  is temperature. Final emissive power is equal to the area in Fig.1.1.

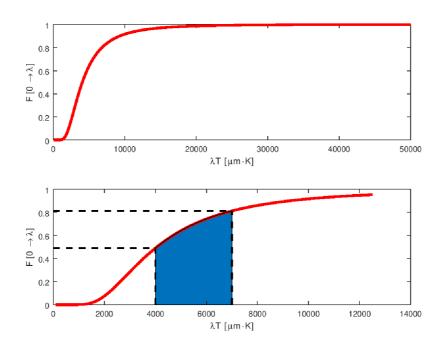

In the real world, IR imagining never detects the whole spectrum, but only predefined spectral range, which is determined by detector. The integral of Eq.1.5 doesn't have analytic solution for arbitrary values of lower and upper limits. To simplify the results, band radiation can be obtained as the fraction of the Black-Body radiation in the interval from 0 to  $\lambda$ , compared to the total emission from 0 to  $\infty$ . The mathematical analysis shows that the integral only depends on the parameter  $\lambda \cdot T$  and therefore integrals can be evaluated numerically for this parameter and

tabulated as a function of  $\lambda T$ . The Black-Body radiation in wavelength interval 0 to  $\lambda$  as function of  $\lambda T$  is in Figure 1.3a.

For quick power estimation, simple graphical method can be used: For example, if the used detector works in LWIR band  $(8 - 14 \mu m)$  and we are interested in temperature 500 Kelvin. Get values for  $8 \mu m \cdot 500 K$  and  $14 \mu m \cdot 500 K$  from the graph (dashed lines in Figure 1.3b) and then put them into Eq.1.6. The resulting value (Fig.1.3b blue area) is a very good estimation of the band energy. Table 1.2 shows result for two temperatures and all IR spectral ranges.

$$F_{(\lambda_1 \to \lambda_2)} = F_{(\lambda_0 \to \lambda_2)} - F_{(\lambda_0 \to \lambda_1)} \tag{1.6}$$

Fig. 1.3: Black-Body's radiation as function of  $\lambda T$

Tab. 1.2: Example of band emission

| Temperature [K] | SWIR [-]             | MWIR [-]             | LWIR [-]             |

|-----------------|----------------------|----------------------|----------------------|

| 500             | $4.2 \cdot 10^{-5}$  | $15.6 \cdot 10^{-2}$ | $32.1 \cdot 10^{-2}$ |

| 2000            | $37.1 \cdot 10^{-2}$ | $10.1 \cdot 10^{-2}$ | $0.92 \cdot 10^{-2}$ |

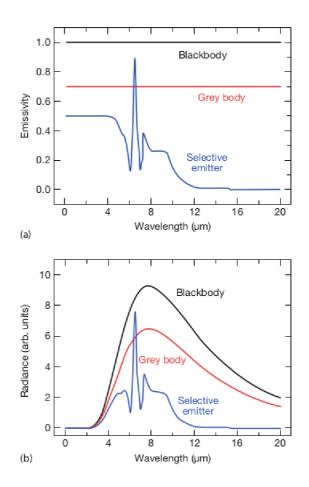

### 1.1.3 Emissivity

Real objects can't emit the maximal thermal radiation at given temperature as the Black-Body. Thermal radiation of real objects can be easily computed by multiplying the Black-Body radiation by the emissivity  $\varepsilon$ . Emissivity is a ratio of emited radiation from the surface of real objects and Black-Body radiation at the same temperature. Emissivity is influenced by wavelength, temperature and solid angle. But IR cameras work in predefined wavelength ranges with limited dynamic range temperature of the scene. In practice, averaged emissivity is mostly used over the desire wavelength and temperature range. The object with constant emissivity over all wavelengths is called Gray-Body. Emissivity can have a value between  $0 \le \varepsilon \le 1$ .

#### Kirchhoff's Law

Kirchhoff's Law expresses that the amount of radiation absorbed by any object is equal to the amount of radiation that is emitted by this object Eq.1.7.

$$\varepsilon = \alpha \tag{1.7}$$

Where  $\varepsilon$  [-] is the emissivity and  $\alpha$  [-] denotes the fraction of radiation that is either emitted or absorbed. This leads to Eq.1.8 which says: Radiation ( $\phi_0$ ) incident on any object must be sum of reflected ( $\phi_R$ ), transmitted through the object ( $\phi_T$ ) and absorbed ( $\phi_A$ ) radiation.

$$\phi_0 = \phi_R + \phi_T + \phi_A \tag{1.8}$$

Eq.1.8 may be rewritten as Eq.1.9.

$$1 = R + T + \alpha \tag{1.9}$$

Where R is reflected radiation and T transmitted radiation. For opaque solids is T = 0 and in this case combining Eqs. 1.7 and 1.9 allows to express the emissivity as Eq.1.10.

$$\varepsilon = 1 - R \tag{1.10}$$

It is important to note that R includes not only directed reflectivity as is usual for polished surface, but also diffusive reflectivity, which additionally occurs for rough surfaces. Highly polished surfaces can reduce emissivity, and on the other hand, objects with rough surface can increase emissivity. Table 1.3 lists materials and their emissivity (whole table can be found in [2]).

Tab. 1.3: Material emissivity [2]

| Material                   | Emissivity value [-] |

|----------------------------|----------------------|

| Aluminum: Polished         | 0.05 - 0.10          |

| Aluminum: Roughly polished | 0.18                 |

| Copper: Polished           | 0.02 - 0.10          |

| Copper: Rough              | 0.74                 |

| Foods                      | 0.85 - 1.00          |

| Glass: Plate               | 0.90 - 0.95          |

Fig. 1.4: (a) Spectral emissivity and (b) spectral radiation of object with different emissivity [1]

# 1.2 Thermovision and IR Detectors

#### 1.2.1 Thermovision

Thermovision is a method of non-contact detection of IR radiation. An IR camera can therefore register the thermal radiation emitted by physical bodies at temperatures of about -40 °C to about +2,000 °C. Typically, thermal imaging cameras record a range from -20 °C to +250 °C. The great advantage of the thermovision method is its lack of invasiveness. In addition, it is possible to conduct temperature measurements in hard-to-reach places. With the use of thermovision methods, one can be quickly diagnose the correct functioning of electrical and electronic components, including industrial automation systems, the uniformity of heating of objects such as machines, furnaces, etc.[9]

There are two methods for IR thermovision:

**Active** - needed source of the IR light to produce a thermal contrast between the feature of interest and the background. The active approach is necessary in many cases, given that the inspected parts are usually in equilibrium with the surroundings.

**Passive** - temperature of the object is higher or lower than temperature of the background, which naturally makes the contrast.

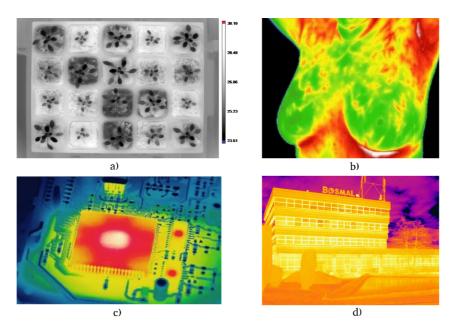

Fig. 1.5: Examples of Thermovision: a) leaf and plant temperature as indicator of water-use efficiency[10], b) breast cancer detection[11], c) PCB inspection[12], d) thermal insulation of the house[9]

#### 1.2.2 IR Detectors

Every IR detector is a transducer that converts thermal radiation into electric signals. IR detectors can be divided into two main groups. First IR detector type is called photon detector, also known as cooled detector, and second type is thermal detector, known as uncooled detector.

#### 1.2.3 Photon Detectors

Photon detectors work on the basis of an intrinsic photoelectric effect. Photon detectors are made of material which responds to IR by photon absorbing that moves material electrons to a higher energy state, which leads to voltage, conductivity or current changes. At room temperature, electrons at different energy levels and electrons in conduction band which are free to move can conduct an electrical current. Most of the electrons are found in the valence band, where they do not carry any current because they cannot move freely. If the material is cooled to low-enough temperature (operating temperature  $\approx 77$ K), the energy of the electrons may be so low that there isn't any left to move the electrons. In this state, the material is not able to carry current. Exposing this cooled material to incident photons having sufficient energy  $E = h \cdot v$  (E is photon energy, h is the constant of proportionality, v is frequency), exceeding the energy threshold ( $\Delta$  E), stimulates the electrons in the valence band, causing them to move up thru energy gap into the conduction band. Thus, the cooled IR detector can carry a photocurrent, which is proportional to the intensity of the incident radiation. There is a critical value of energy of the incident photons that will allow an electron to jump from the valence band into the conduction band. This energy is related to a certain wavelength, the cut-off wavelength. Since photon energy is inversely proportional to its wavelength, the energies are higher in the SWIR/MWIR band than in the LWIR band. Therefore, the operating temperatures for LWIR detectors are lower than for SWIR/MWIR detectors.

#### Intrinsic detectors

Photovoltaic intrinsic detectors structure is based on PN junction devices. The reflective coating on the bottom of the detector provides double chances (injection and reflection) of the photon absorption. Under IR radiation, the potential barrier of the PN junction leads to the photovoltaic effect. An incident photon with the energy greater than the energy band gap of the junction generates electron-hole pairs and the photocurrent is excited.[16]

#### Extrinsic detectors

Extrinsic detectors are similar to intrinsic detectors. However, in extrinsic detectors carriers are excited from the impurity levels and not over the bandgap of the basic materials. They have the advantage of being able to operate at much lower wavelengths than intrinsic. To overcome problems with positive holes left behind in the valence band, higher doping density is required.[16]

#### Quantum well infrared photodetector

Quantum Well Infrared Photodetector (QWIP) uses electronic intersubband transitions in quantum wells to absorb photons. In order to be used for infrared detection, the parameters of the quantum wells in the quantum well infrared photodetector are adjusted so that the energy difference between its first and second quantized states match the incoming infrared photon energy.

#### 1.2.4 Thermal Detectors

Thermal detectors convert incident EM radiation into thermal energy, which leads to changes in physical properties, that are converted into electrical signal with thermal-electric convertor. The utilized type of thermal-electric defines the uncooled detector type. Since the operation of thermal detectors involves a change in temperature, they have an inherently slow response and a relatively low sensitivity compared to photon detectors. Big advantage over photon detectors is the working temperature which is usually equal to room temperature (25 °C). But even if they are called uncooled detectors, they need some type of cooling mechanism for noise and non-uniformity reduction.

#### **Thermocouples**

Thermocouples are formed by connecting two dissimilar metals that generate voltage at the junction point. Generated voltage is proportional to the temperature of the junction.[16]

#### Pyroelectric detectors

Pyroelectric detectors consist of a polarized material which, when subjected to changes in temperature, changes the polarization. The fluctuation in the exposure to the scene generates a corresponding fluctuation in polarization and thus an alternating current that can be monitored with an external amplifier.[16]

#### **Bolometers**

Bolometers are based on the same principle as thermistors. The resistance of the elements varies with temperature changes. Unlike thermocouples or pyroelectric detectors, bolometers are passive elements and for proper function they need a source of power.[16]

# 1.3 Parameters That Characterize Detector Performance

## 1.3.1 Responsivity

The responsivity of an IR detector is defined as a ratio of the change of the received signal to to the change of the temperature scenery (Eq.1.11).

$$Responsivity_{ij} = \frac{S_{1,ij} - S_{2,ij}}{T_{1,ij} - T_{2,ij}}$$

(1.11)

where  $S_{x,ij}$  is the received signal facing the target at Tx.

#### 1.3.2 **NETD**

Noise Equivalent Temperature Difference (NETD) is the smallest detectable temperature change in the target. All temperature differences smaller than the NETD, would be smaller than the noise of the detector, thus impossible to be detected.

$$NETD = \frac{noise(T_{bb}) \cdot \Delta T_{bb}}{S_2(T_{bb} + \Delta T_{bb}/2) - S_1(T_{bb} - \Delta T_{bb}/2)}$$

(1.12)

where  $S_x$  is the received signal and  $T_{bb}$  is the Black-Body temperature.

#### 1.3.3 Defective Pixels

Defective pixels or dead pixels are pixels that fail to operate properly when excitation is applied during the video sampling. Dead pixels must be repaired and that increases computational complexity. Big clusters of dead pixels are impossible to repair using the neighbour samples.

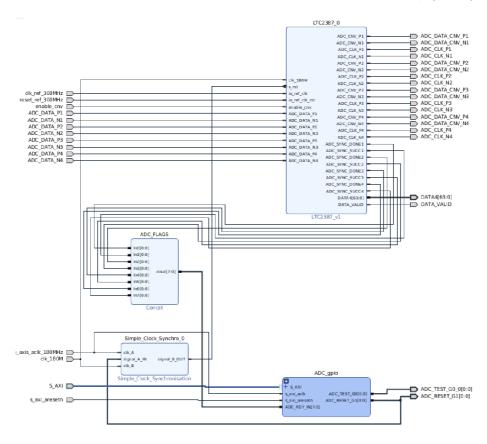

# 2 Hardware

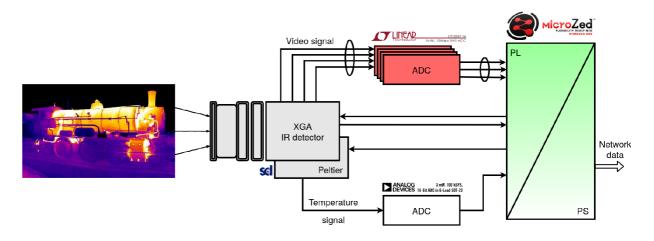

This chapter introduces the main hardware parts of the evolves thermal camera (Fig.2.1). Schematics and PCB designs are not included because it was already done with engineers of Photon Systems Instruments and it is not part of this thesis. The main part of the thermal camera is the BIRD17-XGA IR detector. This detector has 4 analog outputs for video signal, which are converted to digital signals with 4 parallel Analog-Digital-Converter (ADC) LTC2387-16 [17] (Low noise, high speed ADC with 16 bit resolution and 15 MHz sample frequency). Another ADC is AD7680 [18] which is used to digitize the analog output of the thermal diode for BIRD17-XGA temperature measurement. Digital interface and all signal and data processing is done by Zynq7000 on MicroZed board [8].

Fig. 2.1: HW block schematic of IR camera

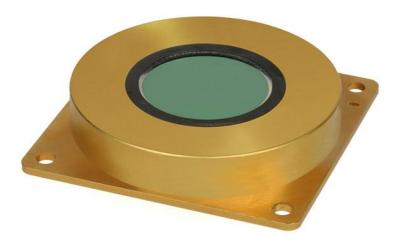

# 2.1 Uncooled BIRD17-XGA Detector

SCD BIRD17-XGA (Figure 2.2) is a high performance (60 frame per second) and high resolution (1024 x 768 pixels) IR long wavelength detector operating in the 8-14 micrometer (LWIR) spectral range. The 17 in the name of the detector stands for 17 µm pixel pitch of the focal plane array (FPA). The detector is composed of:

- A micro-bolometer detector integrated with a silicon Read-Out Integrated Circuit (ROIC)

- Ceramic substrate

- Germanium filter with anti-reflection coating

- Thermoelectric cooler (TEC)

Fig. 2.2: SCD BIRD17-XGA IR Detector

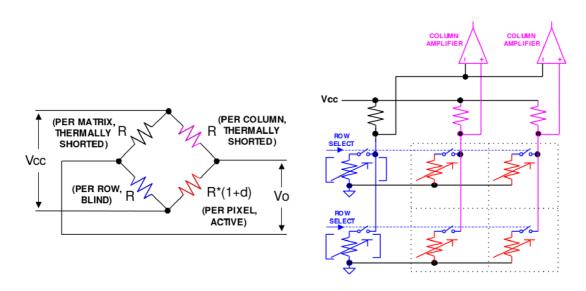

SCD bolometer detector implements a full Wheatstone bridge (Figure 2.3) which gives ability of handling small signal changes (high sensitivity). The micro-bolometer matrix readout is performed using the vertical scanning. During the row integration, each of the row bolometer is connected to the Wheatstone bridge for a predefined period (integration time). After that period, the signal is gained and read out. Output voltage span is between 0.5V and 2.5V and supported span temperature is from  $-40^{\circ}$ C to  $+80^{\circ}$ C. NETD for BIRD17-XGA is 35 mK.

Fig. 2.3: Wheatstone bridge (left) and Read out circuit (right)

BIRD17-XGA offers two possibilities for configuration interfacing, it is Universal Asynchronous Receiver-Transmitter (UART) or Serial Peripheral Interface (SPI).

# 2.2 Zynq-7000 and MicroZed board

For digital data processing, interfacing with peripherals and communication, Xilinx Zynq is used. Zynq is a System-on-Chip (SoC) which combines ARM Cortex-A9 processor with traditional Field Programmable Gate Array (FPGA) logic fabric. The part formed around ARM Cortex-A9 is called Processing System (PS) and the FPGA part is called Programmable Logic (PL). The PL section is ideal for arithmetic, high-speed interface and data flow. PS serves for application that may not be as precise but rather complex. The benefit is that Zynq supports the operating system (Linux) with easy-to-use SDK called Petalinux. Communication between the PL and PS is made using industry standard called Advanced eXtensible Interface (AXI).

# 2.2.1 Processing System

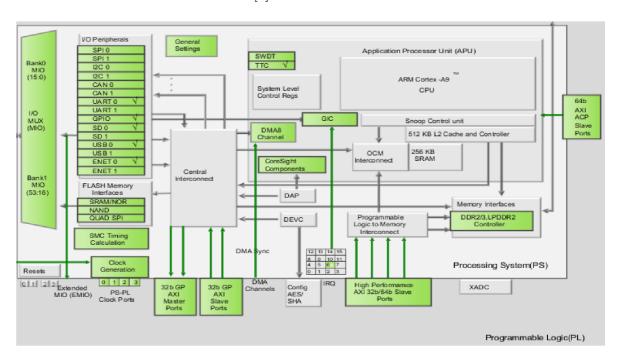

ARM Cortex-A9 processor is a hard IP core, which means it is a dedicated and optimised silicon element on the device. PS block diagram is shown in Fig.2.4. The main part is the Application Processor Unit, which comprises of one or two ARM processing cores with Floating Point Unit (FPU), Memory Management Unit (MMU), cache memory and others. The other main parts of PS are IO peripherals (USB, UART, SPI, GPIO, etc.), memory interface for DDR memory and AXI interface. More information can be found in [5].

Fig. 2.4: Zynq Processing System from Vivado

## 2.2.2 Programmable Logic

The PL part of the Zynq device is composed of general purpose FPGA logic fabric, which contains Configurable Logic Blocks (CLBs), Input/Output Blocks (IOBs) and special resources like high-speed arithmetic block DSP48E1.

#### Configurable Logic Block

Configurable Logic Block (CLB) is a small group of logic elements. Regular CLB consists of slices. Slice is small sub-unit which contains resources (Lookup tables, Flip-flops) for implementing combinatorial and sequential logic circuits.

#### Input/Output Block

IOB provides interfacing between the PL and physical device pad used to connect external devices. IOB contains some special blocks like serial to parallel converter (SERDES), I/O programmable delay primitive and BITSLIP [7].

#### 2.2.3 Advanced eXtensible Interface

AXI is described as a standard for on-chip communication. Zynq uses version AXI4, which is part of the ARM AMBA 3.0 open standard. AXI buses are used to connect the processor to the IP blocks or multiple IP blocks between each other. There are three types of AXI4 buses where each represents different protocol with its own special property. More information can be found in [6].

#### • AXI4

The AXI4 is used for memory-mapped links. This protocol reaches the highest performance. AXI4 uses address for data burst transfer of up to 256 data words.

#### • AXI4-Lite

The AXI4-Lite is a simplified AXI4 protocol. It is also memory-mapped but only single data word (no burst) is transferred on each address.

#### • AXI4-Stream

The AXI4-Stream protocol is used for applications that typically focus on data-flows, where the concept of address is not present or not required. Each stream acts as a signle unidirectional channel for a handshake data flow.

For communication between PS and PL, Zynq offers 3 types of interfaces:

#### • General Purpose AXI

There are four general purpose AXIs. It is a 32 bit data bus, which is suitable for low rate communication between PS and PL with absence of buffering. An

example is communication with AXI General Purpose Input/Output (GPIO) IP core.

• High Performance AXI

There are also four high performance AXI interfaces. This interface supports high rate communication between PS and PL with buffering. Data width can be 32 or 64 bits. This interface is mainly used for Direct Memory Access.

• Accelerator Coherency Port

Provides connection between PL and APU with unchangeable 64-bits width. The port is used to achieve coherency between the APU caches and elements within the PL.

#### 2.2.4 MicroZed board

MicroZed (Figure 2.5) is an Avnet development board based on the Xilinx Zynq SoC. The MicroZed Evaluation Kit includes standalone MicroZed that contains fully functional Zynq Processing System (PS) with peripherals as well as enabling the Zynq Programmable Logic (PL) fabric. This PS system includes DDR3 memory, Flash memory, gigabit Ethernet, USB 2.0 Host, and UART. The capabilities of the MicroZed can be enhanced by plugging it into a carrier card, which then enables up to 108 user defined I/Os. [8]

#### MicroZed Key Features:

• Processor

Zynq<sup>TM</sup>-7000 AP SoC XC7Z010-CLG400-2

• Memory

1 GB DDR3 128 Mb Quad-SPI Flash microSD card

• Communication

10/100/1000 Ethernet USB Host 2.0 and USB-UART

• Expansion connectors

2 MicroHeader connectors 108 single-ended, 48 differential pairs, Agile Mixed Signalling Digilent Pmod<sup>TM</sup> Compatible header (8 MIO)

Clocking

33.33333 MHz clock source for PS

• Configuration and Debug

Xilinx Platform Cable JTAG connector

Fig. 2.5: MicroZed board [8]

#### 2.2.5 LTC2387-16

LTC2387-16 is a high speed successive approximation register (SAR) ADC with 16-bit resolution and 15 MSps (MegaSample per second) throughput rate. The input signal must be driven differentially with common mode voltage 2.048 V and differential range  $\pm 4.096$  V. In order to support high speed operation and minimizing the number of data lines for communication, serial Low Voltage Differential Signal (LVDS) digital interface is used.

#### 2.2.6 AD7680

AD7680 is a 16-bit successive approximation register ADC with 100 kSps throughput rate. Single ended input signal can reach values from 0 V to the VDD (designed to 3.3 V). AD7680 offers high speed serial interface compatible with SPI/QSPI/ $\mu$ Wire/DSP. SPI was chosen for the purpose of this project.

# 3 Software

This chapter describes the design of the implementation in Xilinx SoC Zynq-7000 in PL and PS. Intellectual Property (IP) cores (written in VHDL) were designed in the Xilinx Vivado 2019.1. The embedded Linux solutions on the PS side was designed in Xilinx Petalinux Tools 2019.1 [13] based on Yocto project. Kernel modules (written in C) and the main control program (written in C++) were designed in Xilinx SDK 2019.1. Graphical User Interface (GUI) for data visualisation was designed in Qt with Qt Creator 4.11.1

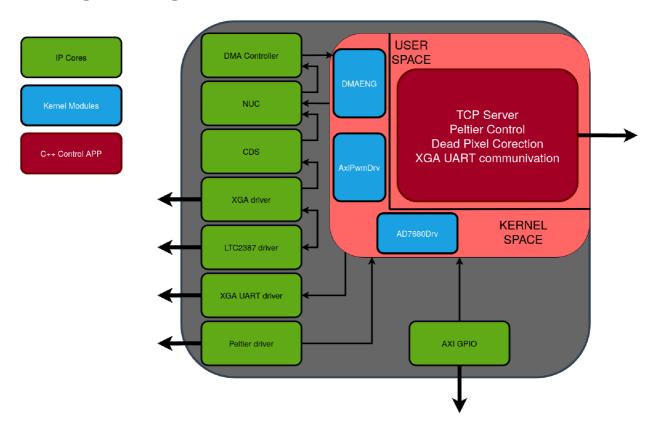

The PL part and IP cores are used for high-speed interfacing, signal processing and communication with peripherals. Linux with kernel version 4.19.0-xilinx-v2019.1 is running on the PS side. Kernel modules are pieces of code running in the kernel space. They can be imagined like communication gates with hardware, or in our case, with the PL part (IP cores). The main control program runs in the user space and it has control over communication and setting of the BIRD17-XGA, temperature stabilization, TCP server for data transmissions to PC and etc. SW block diagram is in Fig.3.1.

Fig. 3.1: SW block diagram

Designed IP cores, kernel modules and C++ libraries in this chapter were designed in the same order as listed. During development, focus was placed on the reusability of the developed IP cores, kernel modules and libraries.

## 3.1 AXI4-Stream

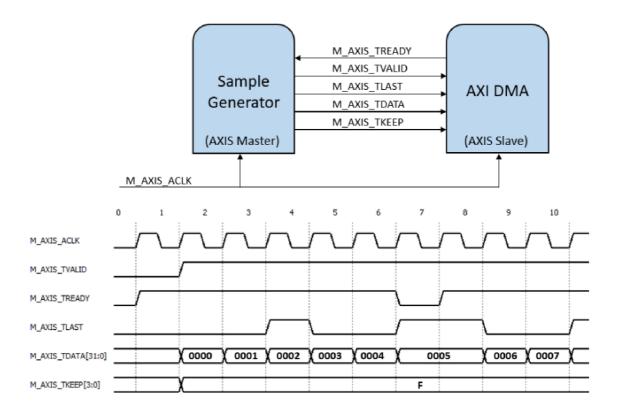

Before presentation of the designed IP cores, here are a few words about AXI4-Stream, which is used for data forwarding. AXI4-Stream is master (M\_AXIS) -> slave (S\_AXIS) interface which uses 5 communication signals: TREADY, TDATA, TVALID, TLAST and TKEEP. The TREADY signal is driven by slave and is informs the master, when data are ready to receive. After that master starts sending data through the TDATA bus. For valid data, the TVALID signal must be set (if the TVALID = '0' -> DATA are discared). The TLAST is used to inform the slave that the last data from packet are being sent. The TKEEP bus is used to indicate the amount of valid bytes in the last data transfer. AXI4-Stream diagram can be seen in Fig.3.2.

Fig. 3.2: AXI4-Stream diagram [15]

## 3.2 DMA Controller and DMAENG

DMA Controller is a name of the hierarchy block in Vivado design, which is used for transferring high amounts of data between PL and PS. For high throughput of data Xilinx offers an IP core called AXI Direct Memory Access (DMA). This IP core is able to transfer theoretically 400 MB/s with 100 MHz clock. On the PS side, there was created a kernel module called dmaeng, which receives data from the PL and saves them into the shared (user/kernel space shared buffer) ring buffer.

As it was written in chapter 2.1, resolution of the BIRD17 is  $1024 \times 768$  pixel with 60 fps. Every pixel is represented by 16 bits. These numbers allow to calculate necessary throughput from PL to PS. From Eq.3.1 calculated data throughput is equal to 94.3 MB/s.

$$Throughput_{data} = \frac{Pixels \cdot fps \cdot BitsPerPixel}{8}$$

(3.1)

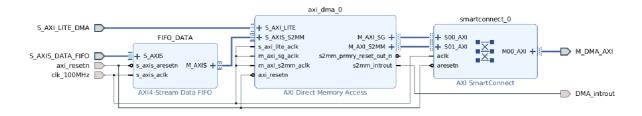

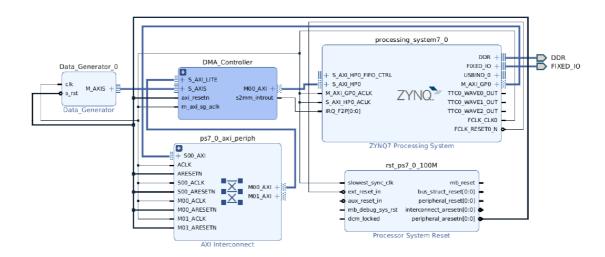

#### 3.2.1 DMA Controller

DMA controller is made from connection of three IP cores (Fig.3.3). AXI4-Stream Data FIFO is used as buffer for the case when DMA is busy. The FIFO size is set to 64 bits x 4096 words. Data from the FIFO flows into the AXI DMA block. The DMA supports two data-flow modes - stream-to-memory-mapped (S2MM) and memory-mapped-to-stream (MM2S). In this design I only used S2MM channel for transferring data to PS memory. DMA AXIS interfaces support 8/16/32/64/128/265/512/1024 bit wide TDATA busses. This IP core also supports scatter/gather functionality (necessary for cyclic transferring). AXI SmartConnect core connects one or more AXI memory-mapped master devices into one or more memory-mapped slave devices (Vivado automatically handles this connection for us). AXI SmartConnect is directly connected to HP port of the PS. The s2mm\_introut signal from the AXI DMA interfacing together with IRQ\_F2P is capable of producing interrupts into the processing system.

Fig. 3.3: Block diagram of the DMA Controller

#### 3.2.2 DMAENG

The AXI DMA core is controlled by the Linux device driver dmaengine offered by Xilinx. This driver was wrapped into custom character device driver called dmaeng. During the boot sequence, the kernel module is probed according to the configuration file. The configuration file (config.h) activates tx, rx or both DMA channels, defines board memory size and starting address of the rx/tx ring-buffer. The ring buffer is allocated in free memory. Reservation of a memory section in the DDR memory can be done by changing of the device tree. Reserved memory should be rounded to the Linux page size (in version 4.19.0 kernel it is PAGESIZE = 4096 B = 0x1000 B). The following example describes a device tree which reserves last 40960 bytes and another device tree node, which is DMA node.

```

memory {

device_type = "memory";

reg = <0x0 0x3FFF6000>;

};

axidmaeng_1: axidmaeng@1 {

compatible = "PSI,dmaeng";

dmas = <&axi_dma_0 0>;

dma-names = "rx_channel";

};

```

The most critical part of the this system is where the samples from kernel ring-buffer are copied to the user space. If copying the image data takes longer than it takes for the IR detector to generate new data, the ring-buffer will eventually fill and samples will be lost. For the zero-copy data method the POSIX standard offers mmap function (library sys/mman.h). From the manual of the function: This function creates a new mapping in the virtual address space of the calling process. In another words, the mmap function creates shared ring-buffer for the user space and kernel space and no data copying is necessary.

IOCTL (input/output control) and sysfs are two types for communication with the kernel module. IOCTL is a system call to express the unique functions of the device which are not included in standard system call. IOCTL is not usable from bash and needs sudo privileges for access. The kernel driver parameters are hidden behind ioctl numbers and accessed from application through ioctl system function. Sysfs is a newer method for communication with the kernel module through generated virtual files (called attributes). These attributes can be controlled from bash without sudo privileges. Another method of controlling the driver from application is using standard read/write system functions. For all designed modules I chose the sysfs model, because of easier debugging from console and cleaner access. Table 3.1 shows attributes for communication with the driver.

Tab. 3.1: DMA Kernel driver attributes

| startTX/RX  | X/RX DMA starts transmitting/receiving                                    |  |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|

| stopTX/RX   | DMA stops transmitting/receiving after valid data packet                  |  |  |  |  |  |  |  |

| configTX/RX | Set [(INT) number of descriptors for ring buffer, (INT) ring buffer size] |  |  |  |  |  |  |  |

C++ class was created in order to control the DMA driver from the application.

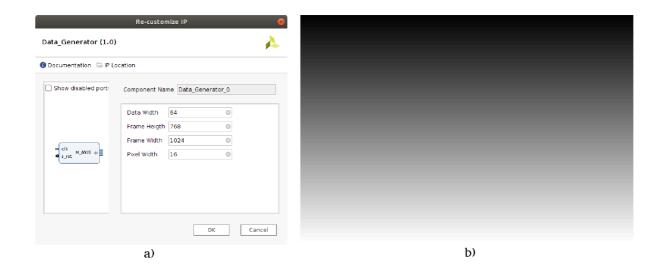

#### 3.2.3 Performance test

For verifying Vivado design, DMA driver, C++ API and finding the maximum throughput a test design was created (Fig.3.4). An IP core called Data\_Generator was built specially for testing purposes. The Data Generator (Fig.3.5) simulates the source of video data with adjustable output data width, frame height, frame width and bits per pixel. Generated data create pattern that can be used for fast visual check. Average throughput of 375 MB/s (theoretical throughput is 400 MB/s) was measured with configured XGA17-BIRD resolution. Measured throughput is sufficient and usable for the desired XGA\_throughput = 94.3 MB/s.

Fig. 3.4: DMA test design

Fig. 3.5: Data generator (a) and generated pattern (b)

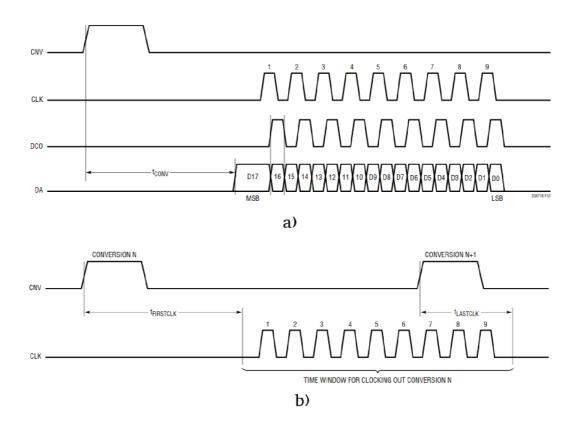

# 3.3 ADC Interface

ADC Interface hierarchy block is used for interfacing with the LTC2387-16. LTC2387-16 uses for communication interface these LVDS signals:

- Input clock (CLK)

- Data Clock Output (DCO), which is echoed version of CLK

- Conversion (CNV), which puts the internal sample-and-hold circuit into the hold mode and starts the conversion cycle all synchronized with the CNV rising edge

- Data outputs (DA/DB)

Due to lack of free pins on Microzed board, DCO and DB signals are not connected. This leads to certain limitation in interfacing. Because of unconnected DCO, the system synchronous clocking has to be used instead of source synchronous clocking. Due to unconnected DB, the two-line mode can not be used for data receiving. The power-down mode can be involved if low state is connected to control pin  $\overline{PD}$ . For setting up the correct timing and data verifying, the ADC is able to generate a test pattern after connecting the logic-high on the TESTPAT pin.

A conversion is controlled with a rising edge on CNV, which must be at least 5 ns long. When the conversion is complete ( $t_{CONV}$  - max 63 ns), the most-significant data bit is available on DA. In this moment, the data is ready to be shifted out by applying a burst of 8 clock pulses to the CLK. Data is transfer in Double Date Rate (DDR), which means data is updated with both CLK edges. The edges of DA and DCO are aligned, but DCO is not connected and can not be used to latch data. The data has to be synchronized with system clock CLK. The data must be shifted

out after the current conversion is complete and before the next conversion finishes. The timing diagram is shown in Fig.3.6.

Fig. 3.6: LTC2386-16 Timing diagram a) Single conversion and b) Valid time window for clocking out data [17]

XGA-BIRD17 generates video data with 15 MHz (66.66 ns) frequency, identical to the sampling frequency of the ADC. In the ADC datasheet [17] are listed the ADC timing characteristic. From these we can calculate Eq.3.2 the smallest working clock frequency = 158 MHz. The upper limit of the clock frequency is 400 MHz.

$$CLOCK_{PERIOD} < \frac{ADC_{SAMPLE\_PERIOD} + t_{LASTCLK} - t_{FIRSTCLK}}{8}$$

(3.2)

In the design the sampling frequency of the ADC driver is set on 180 MHz. This frequency was picked with respect to XGA-BIRD17 clock which is 60 MHz. The main benefit of this value is that Phase Lock Loop (PLL) can be used for its generation (multiplying by 3) and no clock domain crossing is necessary.

The output is in two's complement format. The ADC reference is set to 4.096 V and this results in the LSB voltage of  $62.5 \,\mu\text{V}$ .

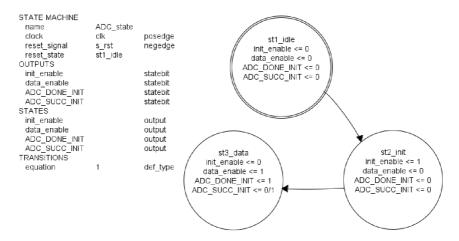

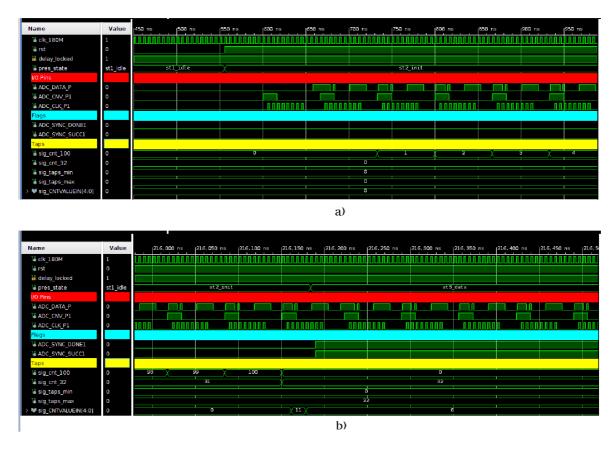

## 3.3.1 LTC2387\_v1 IP core

The LTC2387\_v1 IP core is controlled with a Finite State Machine (FSM) (Fig.3.7) which has three states:

Fig. 3.7: LTC2387\_v1 finite state machine

#### Idle - st1\_idle

Default state after power up or reset signal is the Idle state. This state serves only for waiting untill delay\_locked signal become ready. The delay\_locked signal comes from IDELAYCTRL [19] block primitive, which must be present in conjunction with the IDELAY primitive. The RDY output (connected to delay\_locked signal) of the IDELAYCTRL primitive indicates when the IDELAY module in the specific region is calibrated.

#### Init - st2\_init

The init state is used for timing synchronization with the internal clock. Because of absence of the DCO signal, variabled CLK to DA delay (0.7 ns to 2.3 ns) and static delay (PCB route) synchronization process must be done. Without the synchronization, metastability might occurs when the sampling frequency is aligned with the data change or skew and the received data might corrupt.

For finding ideal sampling windows (center of a data eye) is used a programmable delay primitive called IDELAYE2 [20]. Every I/O block contains the IDELAY and ODELAY block. IDELAYE2 has 31 taps and every tap is 58 ps long (IDELAY ranges from 0 to  $31 \cdot 58$  ps).

The synchronization starts with generation of the known ADC data pattern. Two counters are prepared. The first one is used as a tap counter named in the test bench

as sig\_cnt\_32 and the second one as a pattern counter named sig\_cnt\_100. The process starts with tap delay set to 0 ps. The pattern counter increments up to 100 and in every step it checks if the pattern was received correctly. If all received data patterns were correct, the value of the tap counter would set as the lowest working delay value in the sig\_taps\_min signal, the tap counter would be incremented, the pattern counter reset and and the process would start over again. With this method it is possible to find the lowest and highest working tap delay. The average tap of these two values is set to IDELAY2 as the optimal working delay.

Figure 3.8 shows the test bench for the synchronization process. For this test bench the internal delay of the ADC is set to 1.3 ns and the PCB path delay to 1.5 ns. The final average tap value set to IODELAY2 is 11. Figure 3.9 shows real captured data by the Integrated Logic Analyzer (ILA). From the ILA's data we get almost the same values as from the test bench. The final tap value is equal to the test bench tap value = 11.

Fig. 3.8: Test bench of timing synchronization a) start of the st2\_init state and b) end of the st2\_init state

Fig. 3.9: a) Captured data of the timing synchronization by ILA and b) detailed view

#### Data - st3\_data

After the synchronization process, the output bit ADC\_DONE\_INIT is set to high level. ADC\_SUCC\_INIT is set high if the synchronization was successful. In this moment, the ADC is ready to use. High level on the input port enable\_CNV starts the ADC conversion. The delay of the IP core is 4 clock cycles, untill the CNV signal is physically shifted out. New conversions are started when enable\_CNV stays in high level. Valid data are shifted to the DATA output port with DATA\_VALID signal set.

#### **Primitives**

For interfacing with LVDS-DDR signal coming from LTC2387-16, Zynq primitives must be used. Three primitives, connected in series, are used for the incoming data. The first one is IBUFDS for converting differential signal into single ended. The signal from IBUFDS is fed into IODELAY2 for timing synchronization. The last primitive is called IDDR and it converts signal from double date rate into single date rate. After this process, data can be latched and shifted for next processing.

For forward clock generation, ODDR primitive is used. The ODDR is able to enable or disable the output clock signal, which is very useful for ADC clock interface constraints. For single ended to differential signal conversion, OBUFDS is used. [20]

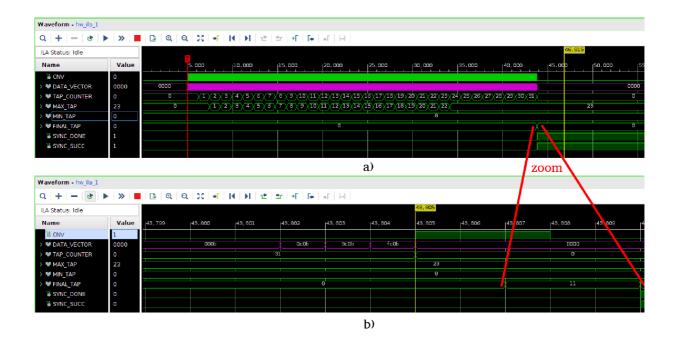

#### **ADC Interface Hierarchy**

Final version of the IP core LTC2387\_v1 has two properties, which are "Number of ADC", which configurates the number of used external LTC23787-16 chips and "Ref Clk", which is the value of the reference clock for IDELAYCTRL. This IP core is inserted into the hierarchy block (Fig.3.10) called the ADC\_Interface. Beside LTC2387\_v1, AXI\_GPIO IP core and Simple\_Clock\_Synchronisation are inserted. The AXI\_GPIO is used as a reset and LTC2387\_v1 status reading from the PS side. Because LTC2387\_v1 runs on 180 MHz and AXI\_GPIO on 100 MHz, Simple\_Clock\_Synchronisation is used for Clock Domain Crossing (CDC).

Fig. 3.10: ADC Interface Hierarchy

#### 3.3.2 ltc2387drv library

The ltc2387drv is a C++ library for controlling the LTC2387\_v1 which contains only one overloaded function. It is an initialization function which should be called at the beginning of the program. The function starts with resetting the IP core and waiting, until ADC\_SYNC\_DONE signal becomes ready. When ready, the ADC\_SYNC\_SUCC flag is read.

#### 3.4 XGA Interface

XGA Interface is a hierarchy block, which integrates communication and video interface with XGA-BIRD17. For this detector it generates the master clock with frequency of 60 MHz (clk\_out\_60MHz).

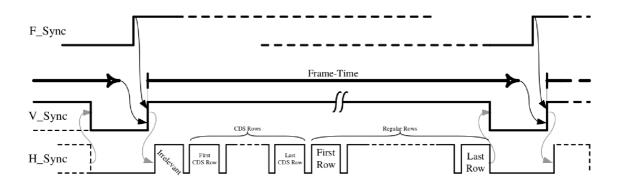

#### 3.4.1 XGA Video Interface

XGA-BIRD17 has three digital video signals which are used to synchronize events between the system (FPGA) and detector (XGA-BIRD17): Frame start synchronization (F\_Sync), Video frame indication (V\_Sync) and Video line indication (H\_Sync). All these synchronization signals are synchronous to the system output clock clk\_out\_60MHz.

The requested frame starts with assertion of the F\_Sync signal, driven by system. The detector responds with assertion of signal V\_Sync. The V\_Sync stays set during whole frame. After assertion of the V\_Sync, H\_Sync pulses are generated by the detector. Every H\_Sync pulse covers the duration of the output of the video of one row. General frame timing and the activity of digital video signals is shown in the following Fig.3.11.

Fig. 3.11: General frame timing [21]

According to F\_Sync signal, there are two video modes: System-Controlled and Free-Running.

#### **System-Controlled Operating-Mode**

In System-Controlled mode system issues F\_Sync pulse with a duration of at least one clock cycle, whenever a new frame should start. The frame duration should be constant and even number of clocks, otherwise image quality is degraded.

#### Free-Running Operating-Mode

In Free-Running mode is continuously F\_Sync = '1' and when frame time is elapsed, XGA-BIRD17 automatically starts a new frame. When F\_Sync is deasserted, the detector completes the frame in progress and stops.

For developing the camera in this master thesis, Free-Running mode was chosen, which is more suitable for video data stream and better image quality should be reached.

#### IP core XGA\_driver\_v2

IP core XGA\_driver\_v2 is controlled by FSM with 4 states (Fig.3.12).

Fig. 3.12: XGA driver v2 finite state machine

The default state is st1\_idle and for starting the video data streaming the XGA\_en signal must be asserted. When FSM comes to the second state (st2\_wait\_to\_VSYNC) F\_Sync is set (XGA-BIRD17 runs in Free-Running mode) and FSM waits for rising edge of the V\_Sync signal from XGA-BIRD17. After rising edge of the V\_Sync signal, FSM is updated to st3\_wait\_to\_HSYNC, where it waits for a rising edge of the H\_Sync signal. In the moment when H\_Sync and V\_Sync are set, FSM goes into st4\_get\_row state. In this state, output signal ADC\_en is asserted. This signal is connected to enable\_cnv of LTC2386\_v1 IP core which starts the conversion. For controlling how many pixels were already read, signal DATA\_VALID from LTC2386\_v1 is routed back to XGA\_driver\_v2.

After receiving the DATA\_VALID = Row Pixels (Row Pixels is an input variable of the XGA\_driver\_v2), FSM goes back to st3\_wait\_to\_HSYNC and waits for the next rising edge of the H\_Sync signal. When the counter of H\_Sync is equal to the frame height, FSM moves to st2\_wait\_to\_VSYNC. Depending on the XGA\_en signal, FSM stays in this state and waits for new rising edge of the V\_Sync signal or goes to st1\_idle.

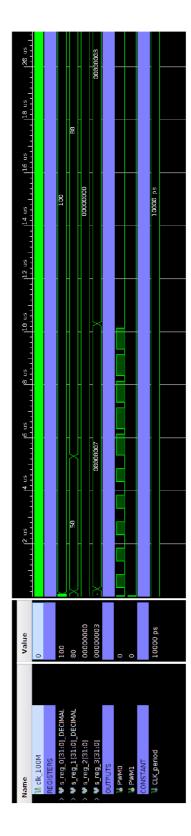

The final version of XGA\_driver\_v2 (Fig.3.13) has three customized parameters for setting the frame size. The test bench for this IP core is in Fig.3.14. Test bench in conjunction with IP core LTC2387\_v1 can be found in Appendix B.2.

Fig. 3.13: Customized IP – XGA\_driver\_v2

Fig. 3.14: Test bench of the XGA\_driver\_v2

#### 3.4.2 XGA communication interface

XGA-BIRD17 detector supports communication interfaces, which allow access to management of various detector parameters. The communication with the detector can be implemented in two modes:

- Parallel interface synchronous with CLK (similar to SPI)

- Serial interface Asynchronous, using UART

Due to routed UART on the design of the PCB, only the Serial interface will be further considered. The UART parameters are described in the following Tab.3.2:

Tab. 3.2: XGA UART parameters [21]

| Parameters  | Details                               | Comments                                        |

|-------------|---------------------------------------|-------------------------------------------------|

|             |                                       | Simple Protocol:                                |

| 8N1         | 8-bit data, no parity, 1 stop-bit     | "Message" followed by optional "Response"       |

| Half-Duplex | No simultaneous Receive and Transmit. |                                                 |

| Baud-rate   | $19.2K \div 230.4K$                   | BIRD17-XGA auto-detects<br>the System Baud-Rate |

BIRD17-XGA detector supports the communication baud rate automatic detection functionality. UART mode requires the system (FPGA) to initialize baud rate auto detection sequence prior to sending any communication message.

#### XGA\_UART Hierarchy

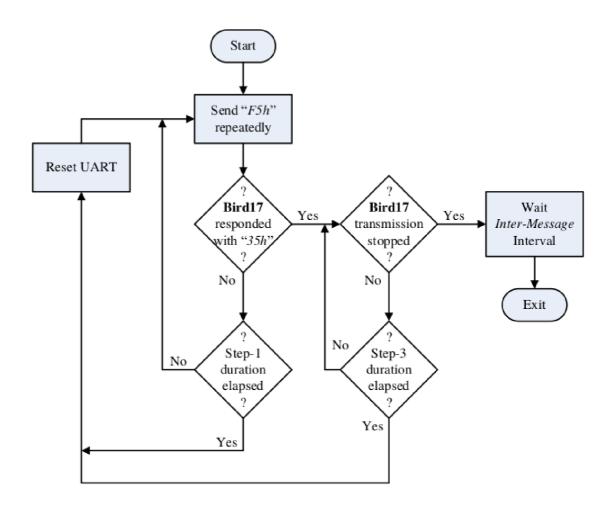

XGA-BIRD17 enters into baud-rate auto-detection in 2 cases. First is during power-on-reset sequence and second is after UART-reset. The flowchart of baud-rate auto-detect sequence is in Fig.3.15. In the first step, the system continuously transmits "0XF5" (hexadecimal) characters. XGA-BIRD17 monitors received characters and runs auto-detect algorithm in order to identify the baud-rate. After baud-rate is recognized, detector starts responding with "0x35" character repeatedly. The system stops the transmission and waits until detector stops the response. The system waits for the Inter-Message Interval (which is 24 characters long) and then the communication is prepared. The auto-detection fails when the detector doesn't receive response within 100 transmitted characters or detector responses with more than 100 characters.

Fig. 3.15: Auto-detect flowchart [21]

Linux is able to access the serial port from the user space. Unfortunately, Linux isn't real time operation system and for strict timing parameters of the auto-detection it isn't suitable. For this reason the auto-detection is moved to the PL and after the auto-detection is control over the UART handed over to the PS user space.

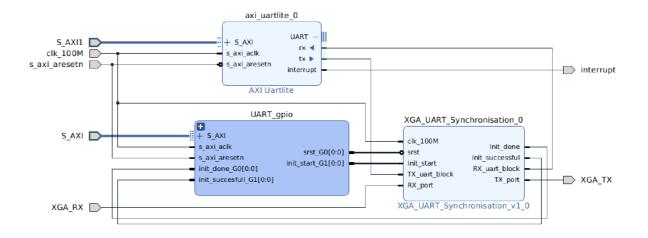

The content of hierarchy block called XGA\_UART is in Fig.3.16.

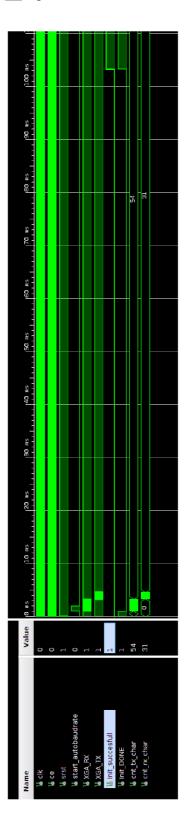

XGA\_UART\_Synchronisation\_v1 is a custom IP core used for the auto-detect phase. The start of the auto-detection is controlled from the PS via input port Init\_start connected to axi\_gpio. Signals Init\_done and Init\_successful inform the PS about the auto-detect result. If the auto-detection is successfully done then axi\_uartlite \_0 [23] takes control over the UART communication. The test bench can be found in Appendix B.3.

Fig. 3.16: XGA UART Hierarchy

#### Xgauartdrv class

From Tab.3.2 it is clear that the used UART format is of 8-bit data length, no parity and 1 stop-bit. However, the word size is 6-bit long in the communication protocol with the detector. Bit6 and bit7 of each Byte must be 0, otherwise the message is considered faulty. The system is always the initiator of communication and the detector responds with the appropriate response.

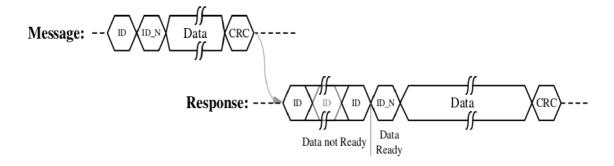

The message structure is shown in Fig.3.17. It consists of 4 parts:

- Cmd\_ID Command identification number

- Cmd\_ID\_N The inverse of Cmd\_ID (1's complement)

- Message body Data of command (one or more words)

- CRC Complement of "0x00" to the bitwise XOR of all the previous words in the whole message

$$CRC(\mathbf{i}) = XOR\{1^{st}word(\mathbf{i}), 2^{nd}word(\mathbf{i}), ..., (last - 1)word(\mathbf{i})\}$$

Fig. 3.17: Message and Response Protocol [21]

For communication via UART, Uartdrv class was written. This class contains standard functions for setting UART parameters, write and read function. From this class inherits the Xgauartdrv class, created for communication with the detector with all its communication constraints. The detector has a large number of configuration parameters, but only the most interesting are present (the rest can be found in [22]).

**Reset-Command** - This command executes the soft-reset. The soft-reset stops video processing operation, all parameters are configured to default values. [22]

**Status-Command** - This command is used for checking indication regarding various errors as well as the internal compensation process status. [22]

RRB-Select-Command - Each row of the detector contains 32 Row-Redundant-Bolometers (RRB). Each one of these bolometers can be either selected or deselected by this command. These bolometers on the left branch of the Wheatstone bridge (Fig.2.3), a.k.a "Blinds", are blocked from the scene and hence used together with the "Global" resistors as a reference to the right branch in order to measure minute changes in pixel resistance. The Global resistors are common for all the pixels in the matrix, and in order to keep the bridge balanced, the same number of Global and Blind resistors in each row must be chosen. The RRB map is unique for each detector. It is created during the factory detector characterization and supplied with the detector as a binary file with predefined format. [22]

**Initialization-Command** - This command defines detector initialization internal parameters and is rarely changed by the user. [22]

Configuration-Command - The system can configure different operation modes of the BIRD17-XGA detector. This command defines detector parameters such as timing, row and frame readout direction, overheat protection mode and other video output parameters. [22]

**Setup-Command** - This command allows the system to define the values of parameters, whose combination defines the detector gain. [22]

Compensation-Command - This command instructs the BIRD17-XGA detector to execute an internal process of compensation calculation. All the matrix pixels are required to line up around the working level (usually mid-voltage-range) after power-up by injecting "compensation" current. This action is referred to as compensation.

The compensation calculation algorithm should be processed with a shutter covering the FOV or in front of a uniform scene while the XGA-BIRD17 detector operates normally.

The compensation calculation algorithm should be processed every time the FOV temperature changes. [22]

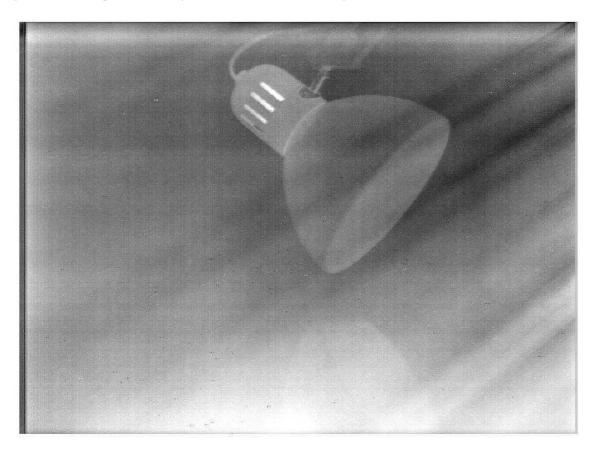

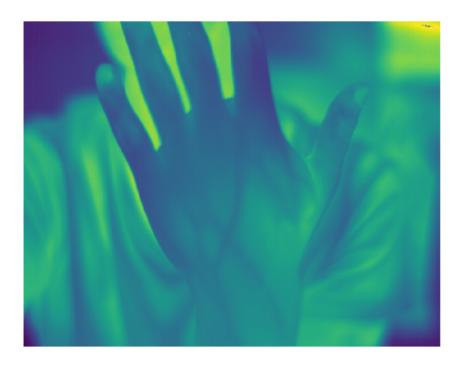

For verification of the so far designed IP cores and C++ classes, first photo from the detector was taken. Figure 3.18 shows the first taken photo. In this figure, the effect of non-uniform temperature can directly be seen as fog. Vertical noise patterns are generated by the ROIC column amplifiers.

Fig. 3.18: The first taken photo

#### 3.5 Temperature stabilization

The XGA-BIRD17 detector is equipped with a thermoelectric cooler (TEC) element which allows controlling the FPA temperature. Implementing the TEC controller allows the system to stabilize detector FPA at specific temperature which best suits the system requirements. The detector produces an image during the TEC stabilization, the image quality is deteriorated (Fig.3.18) until full stabilization is attained. [22]

Temperature of the TEC is read directly on the output pin of an internal diode for independent FPA temperature measurement. This pin is connected to ADC AD7680. The power of the TEC is driven by Pulse Width Modulation (PWM) signal. Duty cycle for the PWM is calculated by PID regulator based on the diode temperature.

Table 3.3 shows the output voltage dependent on a temperature of the temperature diode. With values from this table, equation for any temperature [°C] of FPA can be expressed as:

$$FPA_{temperature} = \frac{V_{diode} - 2.1385}{-0.01126} \tag{3.3}$$

Tab. 3.3: Temperature-Diode Specifications [21]

| FPA temperature | Min. | Typ.   | Max. |

|-----------------|------|--------|------|

| -40°C           |      |        | 2.4V |

| 25°C            |      | 1.857V |      |

| 85°C            | 1.2V |        |      |

#### 3.5.1 Temperature reading

#### IP core AD7680\_v1

IP block AD7680\_v1 was designed to interface with AD7680. AD7680 uses for communication only three pins: SDATA,  $\overline{CS}$  and SCLK.

The conversion is initiated on the falling edge of  $\overline{CS}$  and must remain low until at least 10 SCLK falling edges. If  $\overline{CS}$  is brought high at any time after the 10th SCLK falling edge, but before the 20th SCLK falling edge, the part remains powered up, but the conversion is terminated and SDATA goes back into three-state. At least 20 serial clock cycles are required to complete the conversion and access the complete conversion result. Additionally, a total of 24 SCLK cycles accesses the four trailing

zeros.  $\overline{CS}$  may remains high until the next conversion or it may remains low until  $\overline{CS}$  returns high sometime prior to the next conversion. [18]

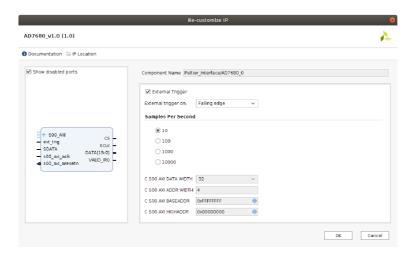

In Figure 3.19 is the designed IP core AD7680\_v1. Except for the ports used for interfacing with AD7680, it contains AXI4-Lite interface, ext\_trig, DATA and VALID\_IRQ. This IP core can work in two modes:

**Trigger mode** - The trigger mode is set if "External trigger" option is checked. In this mode *ext\_trig* port is used for triggering the new conversion. Selecting the trigger edge is done by "External trigger on:" option.

**Free-running mode** - If "External trigger" option is unchecked, then the IP core runs in the Free-running mode. In this mode "Samples Per Second" parameter is applied. Conversion is triggered automatically and periodically with respect to "Samples Per Second".

The output *DATA* port can be used for data reading if AXI4-Lite is not used. Port *VALID\_IRQ* is used as a valid signal for validation if new data are available or as an IRQ signal for the PS.

Fig. 3.19: AD7680 v1.0 IP core

ADC data are available via AXI4-Lite on the base address + offset. The IP core contains only one register for data (offset = 0x00). The register is 32-bit long, but only lower 16-bit are used (Tab.3.4).

Tab. 3.4: AD7680\_v1 AXI4-Lite interface

| Address Space Offset | Register Name | Access Type | Default Value |

|----------------------|---------------|-------------|---------------|

| 0x00000000           | ADC_DATA      | R_only      | 0x0000        |

#### Kernel module ad7680

For transmission of the ADC data from the PL to user space of the PS serves the kernel module called ad7680. The read-only attribute called read\_ADC\_reg0\_r returns the ADC value. When  $VALID\_IRQ$  pin is connected to IRQ\_vector of the PS, the module can be registered with system functions "poll" or "select" and wait for IRQ.

#### Ad7680 class

Ad7680 class is used for communication with the kernel module. This class has two public methods for get raw ADC data or already converted data to voltage values. Reference voltage of the ADC is inserted in the constructor of the class.

#### 3.5.2 TEC driver

TEC inside the XGA-BIRD17 is driven by H-bridge DRV592. DRV592 is a high-efficiency, high-current H-bridge ideal for driving a wide variety of thermoelectric cooler elements in systems. The DRV592 may be driven from any external PWM generator such as a microcontroller or an FPGA. [24]

#### IP core axi\_pwm\_v1.0

The PWM signal is generated by axi\_pwm\_v1.0 IP core. This IP core is controlled from PS via the AXI4-Lite bus. Table 3.5 shows the status/control registers.

| Address Space Offset | Register Name  | Access Type | Default Value |

|----------------------|----------------|-------------|---------------|

| 0x00000000           | PWM_PERIOD_REG | R/W         | 0x0000        |

| 0x00000004           | PWM0_REG       | R/W         | 0x0000        |

| 0x00000008           | PWM1_REG       | R/W         | 0x0000        |

| 0x000000C            | STATUS REG     | R/W         | 0x0000        |

Tab. 3.5: axi\_pwm\_v1.0 AXI4-Lite interface

**PWM\_PERIOD\_REG** - This register is 32-bits wide and is used as clock divider for the reference clock of the IP core. For example, if loaded value = 100 and clock of the IP core = 100 MHz then PWM period will be 1 MHz.

**PWM0/1\_REG** - This register is 32-bits wide and is used as a duty-cycle value. This value shouldn't be higher then the value in PWM\_PERIOD\_REG (duty cycle = 100%).

STATUS\_REG - This register is 32-bits wide but only the lowest 6 bits are used.

This register is used for turning on and off the PWM channels and watchdog. The status register is shown in table 3.6.

Tab. 3.6: axi\_pwm\_v1.0 AXI4-Lite interface

| Bits | Name              | Core Access | Reset Value | Description                                                              |

|------|-------------------|-------------|-------------|--------------------------------------------------------------------------|

| 31-6 | Reserved          | N/A         | 0           | Reserved. Set zero on read.                                              |

| 5    | Watchdog Reset    | R/W         | 0           | Rising edge resets watchdog.                                             |

| 4    | Watchdog Enable   | R/W         | 0           | $ \begin{array}{c} 1 = \text{Enable} \\ 0 = \text{Disable} \end{array} $ |

| 3    | PWM1 Enable       | R/W         | 0           | $ \begin{array}{c} 1 = \text{Enable} \\ 0 = \text{Disable} \end{array} $ |

| 2    | PWM0 Enable       | R/W         | 0           | $ \begin{array}{r} 1 = \text{Enable} \\ 0 = \text{Disable} \end{array} $ |

| 1    | PWM global Enable | R/W         | 0           | Control enable for bit 2-3.                                              |