# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

BRNO UNIVERSITY OF TECHNOLOGY

# FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

# ÚSTAV RADIOELEKTRONIKY

**DEPARTMENT OF RADIO ELECTRONICS**

# JEDNODUCHÝ PRŮMYSLOVÝ ETHERNET

INDUSTRIAL LOW COMPLEXITY ETHERNET SYSTEM

DIPLOMOVÁ PRÁCE

**MASTER'S THESIS**

**AUTOR PRÁCE**

AUTHOR

Bc. Vladimír Šustek

**VEDOUCÍ PRÁCE**

SUPERVISOR

doc. Ing. Tomáš Götthans, Ph.D.

**BRNO 2019**

# Diplomová práce

magisterský navazující studijní obor **Elektronika a sdělovací technika** Ústav radioelektroniky

Student:Bc. Vladimír ŠustekID: 164421Ročník:2Akademický rok: 2018/19

NÁZEV TÉMATU:

#### Jednoduchý průmyslový Ethernet

#### POKYNY PRO VYPRACOVÁNÍ:

Seznamte se s možnostmi implementace IwIP -- IP stacku v embedded systému architektury ARM. Navrhněte embedded systém implementující univerzální vstupně výstupní zařízení komunikující na IwIP TCP/IP vrstvě s důrazem na kompatibilitu zařízení s embedded periferiemi komunikujícími pomocí rozhraní PMOD, Arduino a standardy Analog Devices, Inc. Pro systém použijte mikrokontrolér ADI adUCm4050 a jako linkovou vrstvu neveřejný prototyp ethernetového připojení s integrovaným MAC. Dalším požadavkem tohoto modulu je univerzálnost napájení v standardních průmyslových aplikacích stejně jako napajéní v uživatelských podmínkách (USB) a navrhnutí základní ochrany bloku zdroje. Seznamte se s průmyslovými komunikačními protokoly jako například MODBUS, či OPC - UA pro další část práce.

Zajistěte výrobu hardwaru zmíněného embedded systému s dodržením zásad při použití vysokorychlostních komunikačních bloků (Ethernet). Naprogramujte a oživte vytvořený systém, zprovozněte lwIP -- IP stack. Zvolte praktickou a jednoduchou demonstrační aplikaci (například měření teploty, či tlaku vzduchu) a vyberte vhodný průmyslový protokol jako nádstavbu systému (MODBUS, OPC- UA). Daný protokol implementujte a připojte k vámi vytvořené síti založené na průmyslovém protokolu. Navrhněte grafické rozhraní pro interpretaci získaných dat. Zhodnoťte robustnost systému, zvažte, případně navrhněte možná bezpečnostní vylepšení a další rozšíření.

#### DOPORUČENÁ LITERATURA:

[1] DUNKELS, A. Design and Implementation of the IwIP TCP/IP Stack. Swedish Institute of Computer Science 2001. Online https://www.artila.com/download/RIO/RIO-2010PG/lwip.pdf

Termín zadání: 4.2.2019 Termín odevzdání: 16.5.2019

Vedoucí práce: doc. lng. Tomáš Götthans, Ph.D.

Konzultant:

prof. lng. Tomáš Kratochvíl, Ph.D. předseda oborové rady

#### UPOZORNĚNÍ:

Autor diplomové práce nesmí při vytváření diplomové práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

# **ABSTRACT**

The diploma thesis is focused on the building embedded demonstration application of the proprietary Low Complexity Ethernet module for industrial usage further called the LEN/LES 2. At the first, main used technologies such as MCU, or the lightweight IP stack is discussed, Consequently, there is detailed view on system hardware architecture proposed by hardware and software requirements. Then though part describes blocks of embedded system are in term of specific parts and hardware requirements to create universal board. Following chapters expresses first startup and known hardware bugs, LwIP implementation and MODBUS system implementation. The core of the system is the new released microcontroller an ADuCM4050 and the Low Complexity Ethernet MAC-PHY prototype block and much more dependent convenient peripherals of the MCU based application.

## **KEYWORDS**

Low Complexity Ethernet (LES), MAC-PHY, ADuCM4050, LwIP stack, SDP and Arduino interface, universal power supply, MODBUS, OPC – UA

# **ABSTRAKT**

Předmětem diplomové práce je vytvoření vestavěného neboli embedded systému za účelem demonstračního zařízení s využití neveřejného modulu Low Complexity Ethernet pro průmyslové aplikace – tedy jednoduché průmyslového ethernetu. Nejprve se dokument zabývá technologickými bloky jakožto MCU a použitým LWIP, poté se práce zaobírá detailním popisem architektury univerzálního systému podle zadaných požadavků po stránce fyzické (hardwarové) a systémové (softwarové). Další kapitoly se zabývají oživením desky, včetně vysvětlení technických závad, dále implementací LWIP stacku a nadstavěným MODBUS protokolem. Hlavními stavebními bloky jsou zmíněný Low Complexity Ethernet modul a mikrokontroler ADuCM4050 a další důležité hardwarové periferie mikroprocesoru.

# KLÍČOVÁ SLOVA

Low Complexity Ethernet (LES), MAC-PHY, ADuCM4050, LwIP stack, SDP and Arduino interface, univerzální napájecí zdroj, MODBUS, OPC – UA

# **PROHLÁŠENÍ**

Prohlašuji, že svoji diplomovou práci na téma Jednoduchý průmyslový ethernet jsem vypracoval samostatně pod vedením vedoucího diplomové práce a s použitím odborné literatury a dalších informačních zdrojů, které jsou všechny citovány v práci a uvedeny v seznamu literatury na konci práce.

Jako autor uvedené diplomové práce dále prohlašuji, že v souvislosti s vytvořením této diplomové práce jsem neporušil autorská práva třetích osob, zejména jsem nezasáhl nedovoleným způsobem do cizích autorských práv osobnostních a/nebo majetkových a jsem si plně vědom následků porušení ustanovení § 11 a následujících zákona č. 121/2000 Sb., o právu autorském, o právech souvisejících s právem autorským a o změně některých zákonů (autorský zákon), ve znění pozdějších předpisů, včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č. 40/2009 Sb.

| V Brně dne |                 |

|------------|-----------------|

|            | (podpis autora) |

# **PODĚKOVÁNÍ**

Děkuji školnímu vedoucímu diplomové práce doc. Ing. Tomáši Götthansovi, Ph.D. a externímu vedoucímu panu Ing. Michalovi Brychtovi včetně aplikačního týmu ADI, Limerick, zejména Connelu O'Sullivanovi za účinnou metodickou, pedagogickou a odbornou pomoc a další cenné rady při zpracování mé diplomové práce.

# **CONTENT**

| C  | ontent         |                                        | iv   |

|----|----------------|----------------------------------------|------|

| Li | st of pictures |                                        | vi   |

| Li | st of tables   |                                        | viii |

| 1  | Introductio    | n                                      | 9    |

| 2  | Preliminary    | y                                      | 10   |

|    | 2.1 L          | ight Weight TCP IP stack               | 10   |

|    | 2.1.1          | LWIP Stack footprint                   | 12   |

|    | 2.2 A          | ARM microcontroller introduction       | 13   |

|    | 2.2.1          | ARM M – family                         | 13   |

| 3  | System pro     | posal                                  | 15   |

|    | 3.1 P          | ower Supply unit                       | 16   |

|    | 3.1.1          | Preliminary                            | 16   |

|    | 3.1.2          | LTC3630 down converter                 | 17   |

|    | 3.1.3          | ADP7142 LDO stabilizer                 | 19   |

|    | 3.1.4          | Power supply protection circuitry      | 20   |

|    | 3.2 P          | roprietary Low Complexity Ethernet LES | 21   |

|    | 3.3 A          | ADuCM4050 Cortex M4-F microcontroller  | 22   |

|    | 3.4 S          | ystem connector interfaces             | 23   |

|    | 3.4.1          | SDP platform                           | 24   |

|    | 3.4.2          | Arduino interface                      | 25   |

|    | 3.4.3          | PMOD interface                         | 26   |

|    | 3.4.4          | USB/UART converter interface           | 27   |

|    | 3.4.5          | Auxiliary circuitry                    | 28   |

| 4  | Hardware j     | proposal and debug                     | 29   |

|    | 4.1 P          | Parts placement                        | 29   |

|    | 4.1.1          | MAC-PHY – RJ 45                        | 30   |

|    | 4.1.2          | Arduino interface                      | 30   |

|    | 4.1.3          | MCU, EEPROM                            | 30   |

|    | 411            | PMOD SPI PMOD I2C ADI SDP RE connector | 30   |

|        | 4.1.5                                                      | Buttons                                                                                                           | 30                                            |

|--------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|        | 4.1.6                                                      | Slot microSD                                                                                                      | 31                                            |

|        | 4.1.7                                                      | USB micro, J-LINK – pin                                                                                           | 31                                            |

|        | 4.1.8                                                      | LEDs                                                                                                              | 31                                            |

|        | 4.1.9                                                      | Power Source                                                                                                      | 31                                            |

|        | 4.1.10                                                     | Thermometer ADT75                                                                                                 | 31                                            |

|        | 4.1.11                                                     | The remaining components of the schematic                                                                         | 31                                            |

|        | 4.2 H                                                      | lardware getting started and hardware bugs                                                                        | 32                                            |

| 5      | LWIP Impl                                                  | ementation                                                                                                        | 35                                            |

|        | 5.1                                                        | Setting started with MAC-PHY                                                                                      | 35                                            |

|        | 5.2 L                                                      | WIP porting                                                                                                       | 38                                            |

|        | 5.2.1                                                      | Porting layer ethernetif                                                                                          | 39                                            |

|        | 5.2.2                                                      | DHCP and LWIP                                                                                                     | 43                                            |

|        |                                                            |                                                                                                                   |                                               |

| 6      | Demonstrat                                                 | tion system hardware                                                                                              | 44                                            |

| 6      |                                                            | an-based air conditioning                                                                                         |                                               |

| 6<br>7 | 6.1 F                                                      | •                                                                                                                 |                                               |

|        | 6.1 F                                                      | an-based air conditioning                                                                                         | 44<br><b>46</b>                               |

|        | 6.1 F TCP/IP Mo 7.1 N                                      | dbus APPLICATION                                                                                                  | 44<br><b>46</b><br>46                         |

|        | 6.1 F TCP/IP Mo 7.1 M 7.2 T                                | dan-based air conditioningdbus APPLICATION  1ODBUS introduction                                                   | 44<br>46<br>46<br>48                          |

|        | 6.1 F TCP/IP Mo 7.1 M 7.2 T 7.3 T                          | dbus APPLICATION  MODBUS introduction  CCP/Modbus demonstration system                                            | 44<br>46<br>46<br>48<br>48                    |

|        | 6.1 F TCP/IP Mo 7.1 M 7.2 T 7.3 T                          | dbus APPLICATION  MODBUS introduction  CCP/Modbus demonstration system  CCP/Modbus master (client) implementation | 44<br>46<br>46<br>48<br>48                    |

| 7      | 6.1 F TCP/IP Mo 7.1 M 7.2 T 7.3 T 7.4 T                    | dbus APPLICATION  MODBUS introduction  CCP/Modbus demonstration system  CCP/Modbus master (client) implementation | 44<br>46<br>46<br>48<br>48<br>50              |

| 7      | 6.1 F TCP/IP Mo 7.1 N 7.2 T 7.3 T 7.4 T Conclusion Sources | dbus APPLICATION  MODBUS introduction  CCP/Modbus demonstration system  CCP/Modbus master (client) implementation | 44<br>46<br>46<br>48<br>48<br>50<br><b>54</b> |

# LIST OF PICTURES

| Figure 1 Division between TCP/IP and Application              | 11 |

|---------------------------------------------------------------|----|

| Figure 2 General PBUF_RAM packet chained with PBUF_ROM packet | 11 |

| Figure 3 ARM-M Cores Overview                                 | 13 |

| Figure 4 ARM-M operation states and modes                     | 14 |

| Figure 5 Hardware architecture overview                       | 15 |

| Figure 6 LES power consumption measurement                    | 16 |

| Figure 7 Schematic of the LTC3630 power supply                | 18 |

| Figure 8 Recommended inductor value graph, assumed from [8]   | 18 |

| Figure 9 Schematic of the ADP7142 power supply                | 19 |

| Figure 10 Schematic of power protection circuit               | 20 |

| Figure 11 USB power and signal protection circuit             | 21 |

| Figure 12 Proprietary MAC-PHY prototype illustration          | 21 |

| Figure 13 Block diagram of the SDP system                     | 24 |

| Figure 14 The Arduino interface header sorting                | 25 |

| Figure 15 SPI Type 2A, I2C PMOD connectors                    | 27 |

| Figure 16 Schematic of USB/UART converter                     | 28 |

| Figure 17 LEN/LES 2 board                                     | 29 |

| Figure 18 LEN/LES 2 board                                     | 32 |

| Figure 19 Wrong LED orientation                               | 32 |

| Figure 20 3V3 and 3V3 MAC-PHY misconnection                   | 33 |

| Figure 21 Wrong P13 pinout                                    | 33 |

| Figure 22 LEN/LES 2 board normal consumption                  | 34 |

| Figure 23 Wireshark Syslog frame receiving                    | 35 |

| Figure 24 Frame Syslog payload received by LEN/LES 2 receiver | 36 |

| Figure 25 Calling ping command (no other task processed)      | 42 |

| Figure 26 DHCP LWIP client                                    | 43 |

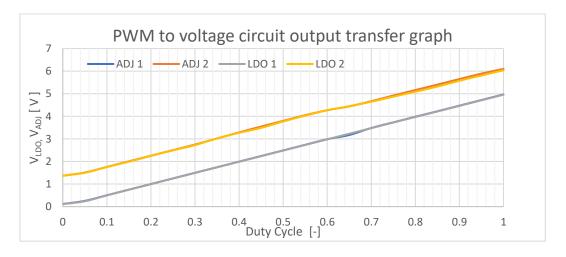

| Figure 27 Fan control circuit                                 | 45 |

| Figure 28 Fan circuit voltage                                 | 45 |

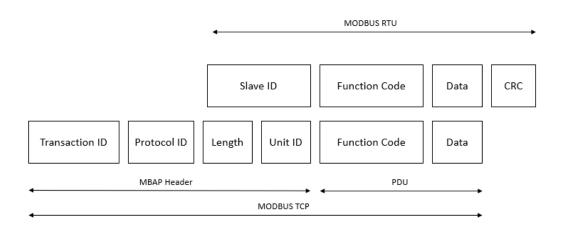

| Figure 29 Modbus RTU vs TCP/MODBUS                            | 46 |

| Figure 30 TCP/Modbus commands                                 | 47 |

| Figure 31 TCP/Modbus example transaction read coil (ON-state) | 47 |

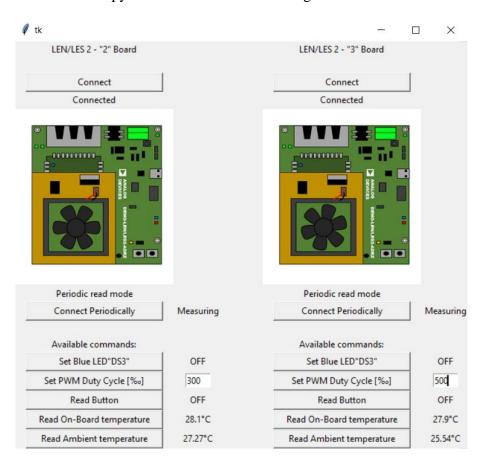

| Figure 32 The master TCP/Modbus GUI                    | . 49 |

|--------------------------------------------------------|------|

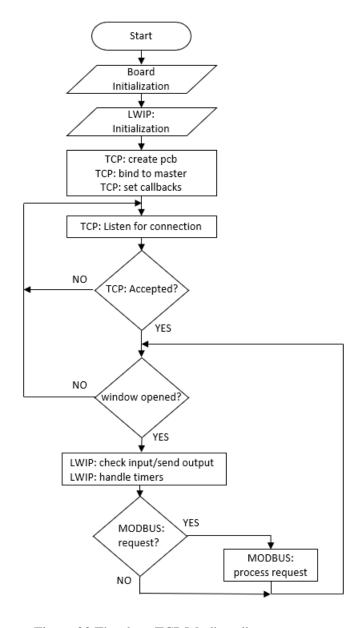

| Figure 33 The slave TCP/Modbus diagram                 | . 50 |

| Figure 34 Low Complexity Ethernet Demonstration System | . 52 |

| Figure 35 TCP/Modbus master-slave communication        | . 53 |

# LIST OF TABLES

| Table 1 Dunkels's LwIP footprint             | 12 |

|----------------------------------------------|----|

| Table 2 STM32F4xx HTTP server demo footprint | 12 |

| Table 3 Arduino interface pinout             | 26 |

| Table 4 PMOD SPI Type 2A, I2C pinout         | 27 |

# 1 INTRODUCTION

Over the last few years, interest in mutually connected computer-based devices has greatly increased. These devices are becoming more available because of prices have dropped and so can be used in various areas such as healthcare, industrial production, safety, transportation etc. Originally the army project named ARPANET emerged in highly developed Internet technology for different purposes with often hard requirements such as safety, high speed, data rate. This document aims into Low Complexity Ethernet module which collect data from essential communication protocol on the one side (SPI, I2C, UART etc.), encapsulates data to convenient ethernet frames and consequently sends for general processing on the other side. This chapter aims into the fundaments of the proposed system.

Recently, Analog Devices (ADI) designed the FPGA based low complexity prototype with two ETH - PHYs and I2C + SPI access interfaces. This block is proprietary, and its content is not point of this diploma thesis. This prototype is called as the LEN/LES (switchable Low complexity Ethernet Node/ Low complexity Ethernet Switch) can be understood yet not released product providing MAC service. In the further text is this block called as the MAC-PHY. This document aims only into to LES mode system implementation. Further implementation (up to application layer) is subject of this document. The main point of this assignment is to create demonstration application board with the MAC-PHY included (further called LEN/LES 2 board). Demonstration board should highlight potential of the project and it is pre – iteration for final intended SoC (System on Chip) implementation of the whole described system. The MAC-PHY requires host MCU for control – intended part of the final SoC. Final system should use one of the convenient industrial protocol such MODBUS, OPC - UA. Note that of the main corporal requirements is to use new released ARM MCU the ADuCM4050 (M-4F Cortex) with enhanced power management and convenient peripherals to prove its performance.

However, there are some constrains during Ethernet implementation in the miniaturized embedded system – available space memory and computing performance. Therefore, a LwIP stack is discussed as the first – special variant of a TCP/IP stack for embedded. The LwIP familiarization is followed by brief introduction to used ARM microcontrollers. Consequently, the fundaments of the system are described as was mentioned in the abstract. Finally, last chapters express hardware debug, LwIP implementation and MODBUS implementation.

# 2 PRELIMINARY

This chapter is dedicated for brief LWIP stack introduction such as reason of usage in embedded system or light view on the architecture. Secondly, the basic features of the ARM MCUs are discussed.

# 2.1 Light Weight TCP IP stack

The miniaturized computer-based devices such as sensors must be inexpensive and small, the implemented Internet Protocol must be optimized as well. For these purposes LwP TCP/IP stack by Adam Dunkles was developed (From the Swedish institute of computer science) [1]. The ordinary TCP/IP stack provides and IP, ICMP, UDP and a TCP protocol [3]. The application layer is highly hardware abstract, that entry point of the convenient stack is in file I/O fashion, especially because of fundamental elements implementation in the system kernel. The TCP/IP is designed as a layered system, whereas layers are strictly divided and only entry points are exposed for interfacing. Since the stand-alone layered architecture has advantages such as safety (no other layer can access resources of neighbor layer except interfacing with dedicated entry points), there is a disadvantage of performance and memory requirements. For layer division, it is needed to copy all used data buffers through the stack, therefore significant amount of the memory and computing time is occupied by system.

However, the typical embedded application has very limited memory resources, so compromise is needed especially in the buffering. The main goal of LwIP (light weight TCP/IP stack) is the sharing buffer through the layers, what is violation of strictly divided layers in the original intended stack. The memory sharing can be easily supervised because of native the C – language stack implementation. Except supported protocols (IP, ICMP, UDP, TCP) LwIP needs a few support modules such:

- Emulation layer only implementation dependent part of stack, includes timers, process synchronization, message passing etc.

- Buffer and management subsystem care about memory for processes

- Network Interface functions the end low layer driver function

- Internet Checksum functions packet checksum calculation

- Abstraction API for global stack interfacing

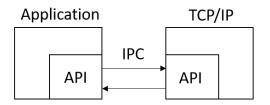

In term of process model, LwIP is intended to operate as the single process, whereas user is interfacing stack API (Application Programming Interface) accessing this single process, or stack is divided into the two process in mutual collaboration comprised from the API and the TCP/IP process. In case of the divided API and TCP/IP, both process communication using an inter-process communication (IPC) using software semaphores, message passing and memory sharing.

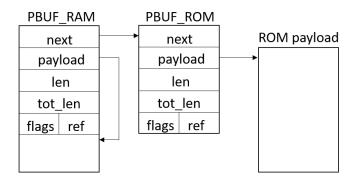

The memory management uses chained structures with necessary variables and pointers to the payloads. For example, the packets are represented as a structure as well as the network driver structure, which represents the certain mapped network devices.

Figure 1 Division between TCP/IP and Application

The memory manager splits memory into the small chunks and places small structure with flag used/unused there. This allows to maintain memory and prevent fragmentation. Also, the manager maintains only dedicated part of the memory so cannot occupy room of other blocks

The packet buffers are example of the chained structure instances. The packet may reside in a *PBUF\_RAM*, *PBUF\_ROM* or might be stored in the fastest way to the pre-located static *PBUF\_POOL* memory. The *PBUF\_ROM* memory is suitable for constant data to be sent, *PBUF\_RAM* data are used to send packet and *PBUF\_POOL* for its fast access is used for incoming packets. Note that in the MCU is available only the RAM and the FLASH memory for protentional data, so packet of the ROM character is both read/write accessible. The *PBUF* structure contains following parts such pointer of the next *PBUF* instance pbuf, pointer of packet payload, length of packet, length chained packets, flags and reference bits. The data of payload pointer are stored in the though frame of pbuf as the last member of structure. In term of size is the biggest *PBUF\_POOL*, because of incoming packet size (huge amount of received payload data). Figure 2 express chained packets of types PBUF\_RAM and PBUF\_ROM, whereas PBUF\_ROM has external payload storage.

Figure 2 General PBUF\_RAM packet chained with PBUF\_ROM packet

Network interfaces are also handled using chained structure defined as *netif*. Structure contains pointer for chaining, name of interface, interface number, IP address, netmask, gateway field and state flag, but especially contain two function pointers for low layer packet handling during receiving and transmitting. IP and UDP protocols are presented as structures as well.

## 2.1.1 LWIP Stack footprint

The Adam Dunkels's proposal of the LwIP was tested only for the program RO (Read Only) memory usage (data, instruction). Also, reached results are old – fashioned in term of the implementation (compiled for x86 and 6502), note that reference document was issued in the year 2001. Dunkels's original stack takes 23kB of the flash memory and there is not specified application of usage.

In point of view from LwIP original proposal, the STM recently issued document of the LwIP stack for its ARM M-4 Cortex microcontrollers STM32F4xx (year 2013) [4]. STM compiled LwIP in result of 98kB used FLASH (RO data and RO program), and 33kB of the RAM usage in case of the HTTP 1.0. Note that the STM uses the hardware abstract functions and the used microcontroller is much more advanced in compare to 6502 used by Dunkels (STMF4xx family represents 32 – bit ARM M-4 Cortex MCU).

Table 1 Dunkels's LWIP footprint

| Module            | Size [B] |

|-------------------|----------|

| TCP               | 11461    |

| Support functions | 4149     |

| API               | 3847     |

| UDP               | 1264     |

| IP                | 1211     |

| ICMP              | 714      |

| Total             | 22646    |

Table 2 STM32F4xx HTTP server demo footprint

| Module                                      | RO code<br>FLASH<br>[B] | RO data<br>FLASH<br>[B] | RW data<br>SRAM [B] |

|---------------------------------------------|-------------------------|-------------------------|---------------------|

| Ethernet driver and interface               | 2828                    | 0                       | 9360                |

| LwIP memory management and IP modules       | 18634                   | 20                      | 19978               |

| Application Modules: general initialization | 6988                    | 52385                   | 1581                |

| STM Peripheral drivers and board support    | 3720                    | 5                       | 16                  |

| Others (stack, heap, ect.)                  | 8456                    | 4573                    | 32                  |

| Total                                       | 40626                   | 57091                   | 32770               |

Regards to the footprint of the  $_{LW}IP$  stack is mandatory to mention the  $\mu IP$  stack developed for the 8-bit microcontrollers with the footprint < 1kB of FLASH and <100B of the RAM, also by Adam Dunkels [2]. Constraints caused by footprints will be discussed in the MCU related chapter 4.

#### 2.2 ARM microcontroller introduction

It may be said with exaggeration that the ARM based 32-bit MCUs rule the world. The Advanced RISC Machines are used not only in the miniaturized embedded solution, but also in the devices with high computing performance [5].

Although the RISC (Reduced Instruction Set Computing) is part of the name abbreviation, most of the used instruction is CISC (Complex Instruction Set Computing). ARM company does provide only the IP core for the silicon vendors which produce MCU with their customized peripherals.

Once of the main advantage is a core native debug interface standard JTAG/SWD, what is also only direct entry point to the core. Consequently, the core provides ethe entry high performance AXI and simpler APB bus for interfacing with other important block of MCU such as clock section, memories (SRAM, FLASH), etc. ARM is designed for ARM - 32b instructions, but also provides option of the THUMB2 16/32b instruction set. The ARM microcontrollers are marked as the Harvard architecture devices, because data and program can be accessed simultaneously. This device processes with virtualize memory, so even if FLASH and RAM is content from different HW memories, user accesses them in linear order.

ARM cores are divided into:

- ARM A: High performance devices such as mobile phones, tablets and small

computers. This type of core supports 7 modes of operation with its own

processing necessary registers. Only this core uses full scale of ARM instructions.

ARM instruction might be used as very powerful using Assembler fashion

programming.

- ARM R: Devices with the highest timing requirements. This core is used in application, whereas is needed timing accuracy (e.g. during ISR routines) such as very precise motor control.

- ARM M: Brief description in following subchapter.

## 2.2.1 **ARM M – family**

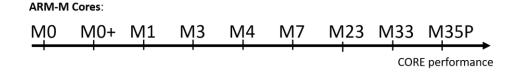

The ARMv7M architecture of ARM-M devices was developed to offer better industrial leading-edge system performance, support natively C/C++ coding, deterministic instruction and interrupts timings [6]. M – family requirement was to allow producing enhanced low-cost miniaturized applications, whereas full performance of core may be needed. The ARM company market offers a few M-cores sorted in increasing order of performance and complexity.

Figure 3 ARM-M Cores Overview

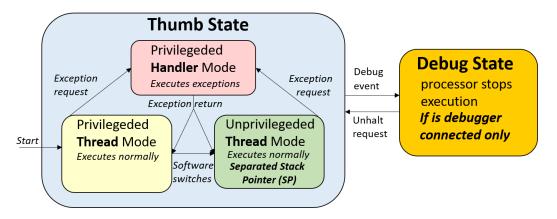

The devices support two (three) operational modes in frame of the Thumb State [5]. The number of modes is very limited in compare to "A" and "R" ARM devices. There is the privileged handler mode for exception (interrupt) processing and privileged/unprivileged thread mode for normal instruction execution. The unprivileged thread mode prevents from accessing sensitive parts of the MCU such memory or peripherals and uses its own stack pointer — ensures advanced reliability of the system. However, the unprivileged mode does not have to be used at all, especially in the simple applications.

Figure 4 ARM-M operation states and modes

The register bank is composed from 16 registers of 32-bit width, whereas first 12 of them are for general purposes. The 13<sup>th</sup> register is Stack Pointer and can be MSP (Main SP) or PSP (Process SP) according to the current state of operation. Then, there is a register to hold return address, program counter. The ARMs have a few of status registers a xPSR (Application, Execution, Interrupt), what also ensures higher reliability of the system.

One of the most mentioned feature of the ARM high performance is the three-stage pipeline. The three-stage pipeline is implementation begins in M3 family and then in the better cores. The pipelining allows fetch-execute-store fashion of execution, what allows to process most of the instruction in one clock cycle such multiplication. Note that clock the frequency may exceed 100 MHz up to 200 MHz [5].

# 3 SYSTEM PROPOSAL

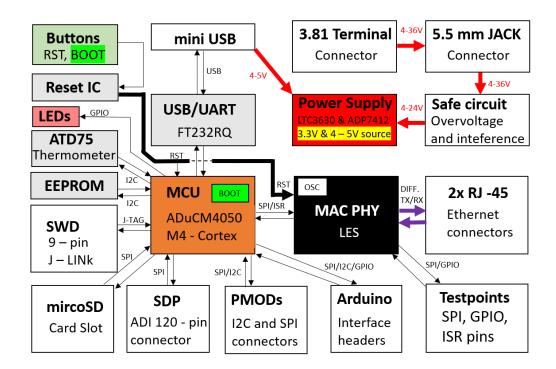

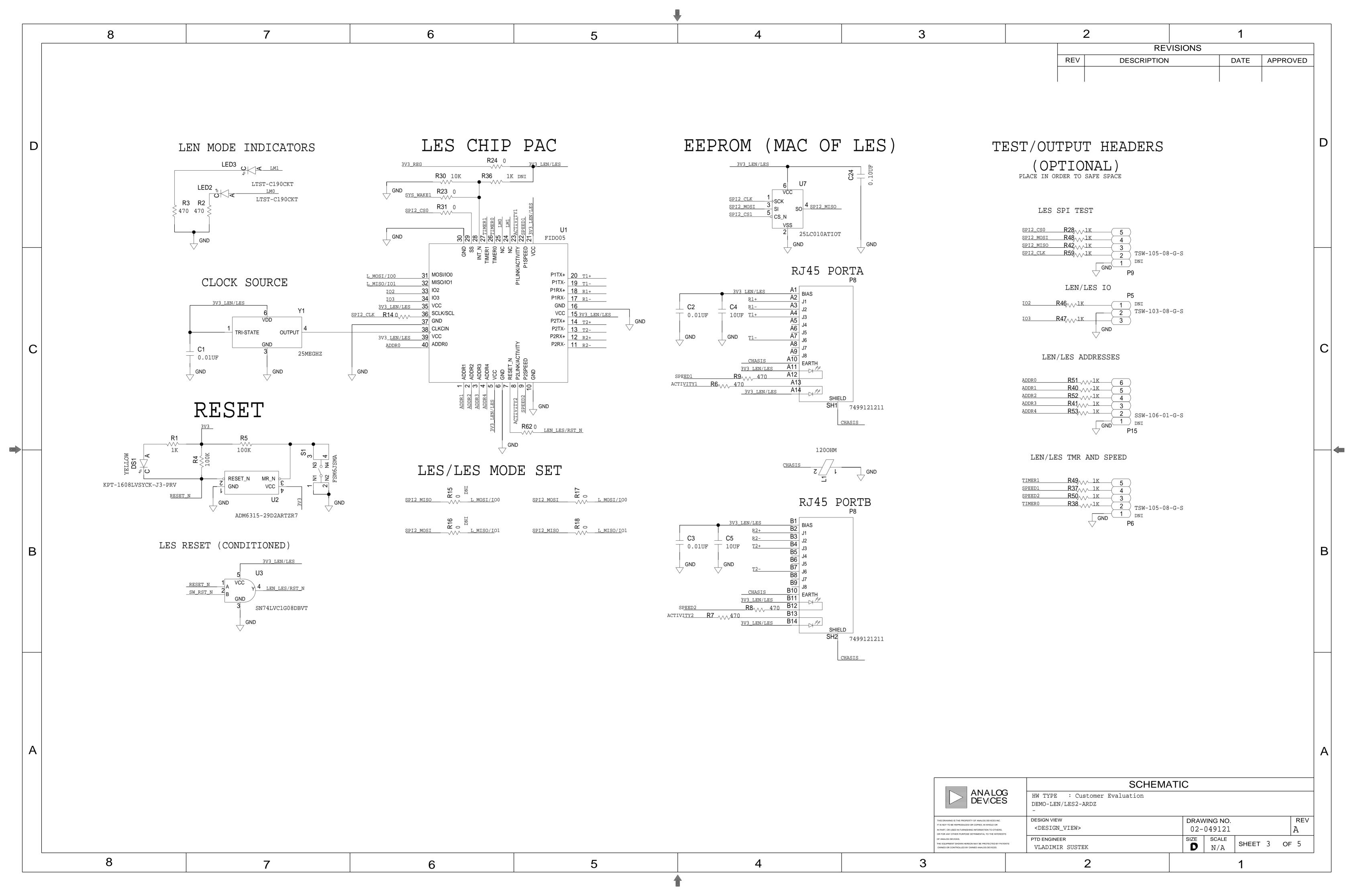

This chapter discusses important hardware blocks used in the LEN/LES 2 board. At the first is discussed power supply unit, secondly there is brief introduction to the proprietary MAC-PHY block. The third part expresses properties of the used MCU ADuCM4050 application. Consequently, there are subchapters about universal interfacing units – such as USB/UART interface and connectors. The detailed view on the embedded system is Figure 5. Schematic of the proposed system is enclosed as the appendix.

Figure 5 Hardware architecture overview

The Hardware architecture depicts blocks and its signal and external power connections. The white blocks represent passive mechanical connectors for board interfacing – note that there are only around the core. The core of the architecture is MAC-PHY block and MCU (brown and black). The light blue color marks ICs used for auxiliary functions such as reset circuit, USB to UART etc. The red block contains power supply circuitry and provides power supply 3.3V to the system. Note that whole system is powered by 3.3V except the USB/UART – internally powered by the LDO. There is 4-5V power source stabilized by the 5V LDO ADP7412, the usage is only for the SDP interface connector. The green block is composed from two buttons, first for reset circuit, the second for the BOOT pin of the MCU, note that signal connection between BOOT and MCU is not drawn – expressed only by distinct green color. For signalization there are a few LEDs dedicated (pink).

The simple thin arrows are used for SPI/I2C/GPIO/ISR connections. The thick black arrow leads between MCU and MAC-PHY block of external reset requirement. The uncomplete thick red arrow should outline power supply options.

## 3.1 Power Supply unit

## 3.1.1 Preliminary

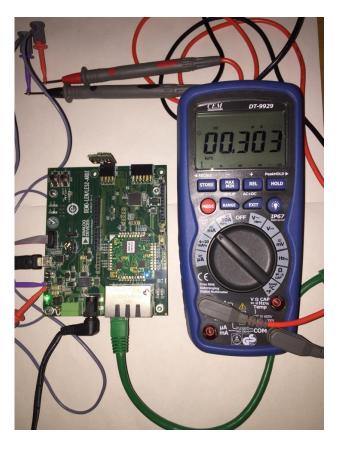

One of the typical features of the miniaturized devices is range of power supply voltage and low power requirements. Because of the used MAC-PHY PFGA-based block (discussed in the next chapter), the low power requirements may be abandoned. During the pre-iteration of the Low Complexity Ethernet system was measured consumption of the whole system including MCU around 300 mA (Figure 5).

Figure 6 LES power consumption measurement

Auxiliary consumption measurement is depicted in figure 5. There is voltmeter on the left, ammeter in the middle and the very first LES device with the hosting ADuCM4050 board ADZS - ADuCM4050 EZKIT – the universal MCU evaluation board [7]. The EZKIT ensured up to 500mA current at 3.3V for hosted application. During the measurement, the LES was linked with the PC (processed packet on the ARP layer – traffic load). The current consumption reached approximately 300mA, what did not vary across adjusting traffic significantly. Note that the EZKIT was supplied using its USB interface by desktop PC - DELL OPTIPLEX.

However, ADI (Analog Devices International) stopped production of EZKIT and started to produce more practical and economic replacement EV-COG-AD4050 [14]. Replacement board though does not have enough power supply unit because of its purpose – evaluating microcontroller ADuCM4050 in lower power efficient applications. The result was that MAC-PHY block was kept in brown-out state so reliable system with ADuCM4050 and MAC-PHY module in collaboration is needed – the diploma thesis assignment.

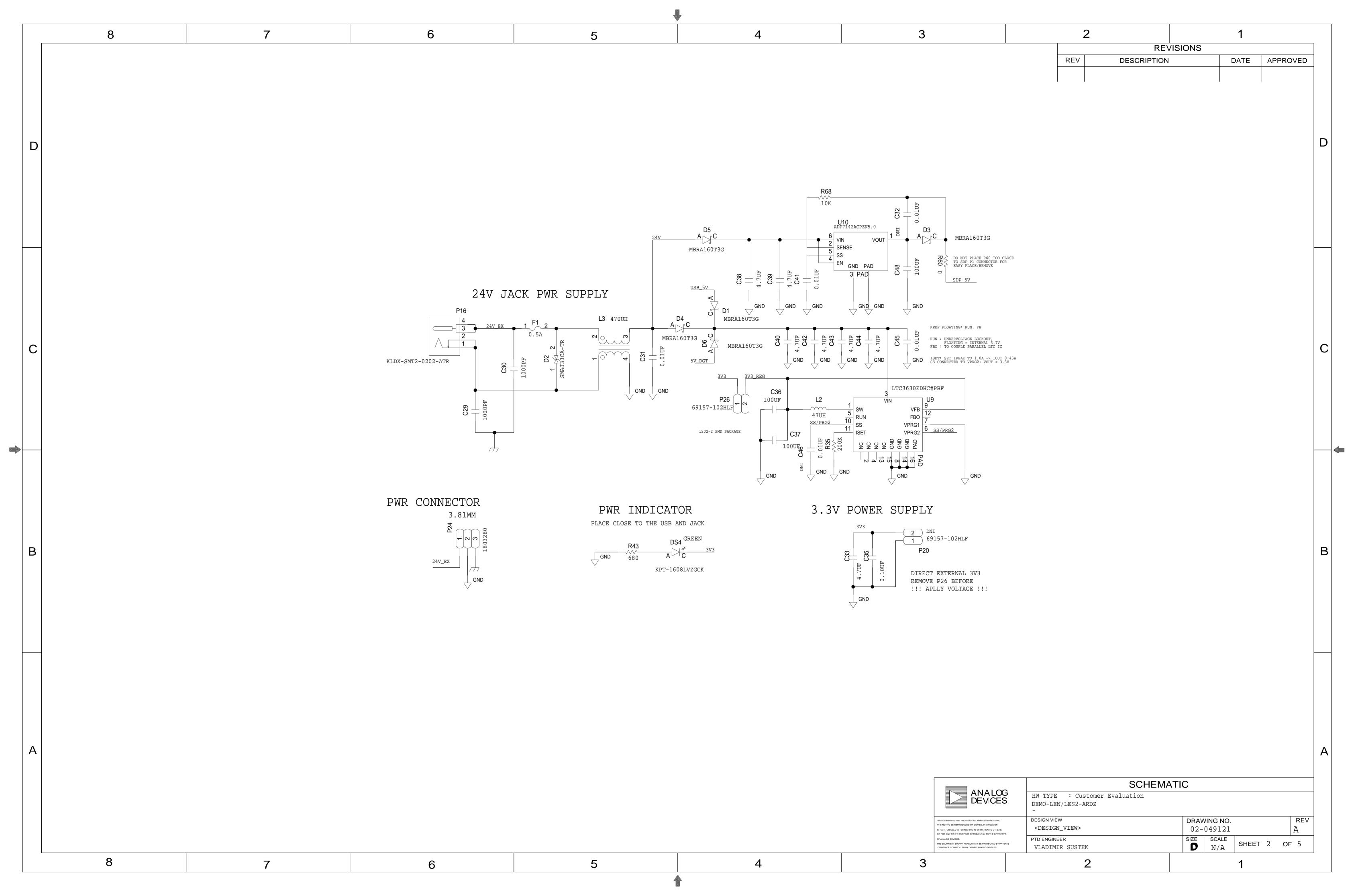

#### 3.1.2 LTC3630 down converter

The Analog Devices acquired Linear Technology (year 2017) and became company with wide offer of power supply converters or stabilizers. Logically, usage of corporal IC for power supply is required. Described circuit is part of the red block in figure 5.

Global power supply requirements of the system:

- 5V for SDP requirement and 3.3V for LES, MCU and related circuits

- USB V<sub>BUS</sub> 5V power supply source (down to 4.2V in worst case)

- Industrial 24VDC  $\pm 10$ V source, overvoltage and interference safe circuits

- Direct 3.3V voltage power supply source exceptional, debug purposes

- Provide 500mA at 3.3V, voltage cannot decrease down to 3.20V

- Provide 5V for SDP purposes and 3.3V for MCU and LES (next subchapter)

LTC3630 was chosen as an appropriate down converter due to following properties [8]:

- Operating range 4 65VDC

- Adjustable 50 500mA output current

- All-in including switch, only external inductor working point passives needed

- Low dropout in case of  $V_{IN} \approx V_{OUT}$ , switch  $R_{DSON}$  1.9 $\Omega$  at 100% duty cycle

- Low profile footprint 3.5mm x 5mm with thermal pad

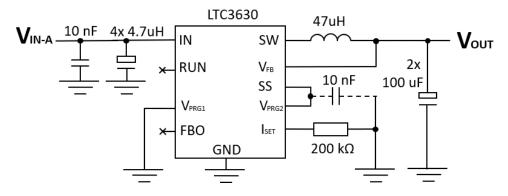

There are a few evaluated typical applications in the official LTC3630 datasheet [8]. The best suits "4V to 65V Input to 3.3V Output, 500mA Step-Down Converter" from the first page. Because LTC3630 contains optional pins (unused in mentioned application), the original schematic was enhanced (Figure 6). Especially, there is a pin for output current settings, which is originally left floated  $\approx$  maximal current.

The output current I<sub>OUT</sub> (500mA) is set by switched I<sub>PEAK</sub> which are related as:

$$I_{OUT} = I_{PEAK} \div 2 \rightarrow I_{PEAK} = 2 \times I_{OUT} \rightarrow I_{PEAK} = 1.0A \tag{3.1}$$

$$R_{I_{SET}} = I_{PEAK} \times 0.2 \times 10^6 = 1 \times 0.2 \times 10^6 = 200k\Omega$$

(3.2)

The equation 3.2 calculates value of  $200k\Omega$  resistor which is connected to the I<sub>SET</sub> pin.

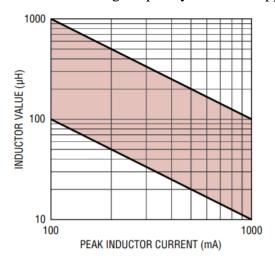

Figure 7 Schematic of the LTC3630 power supply

The value  $47\mu H$  of the switching inductor at the terminal SW was obtained from the graph of figure 7. Value  $47\mu H$  is on in the optimal center of the recommended inductance graph. As it is recommended in the datasheet, quality MSS – 1048 family inductor by Coilcraft vendor was chosen. Estimated switching frequency should be approx. 80kHz.

Figure 8 Recommended inductor value graph, assumed from [8]

Although there are formulas for the output and input capacitor calculation, vendor recommend increased values of mentioned discrete parts. However, by experienced colleagues in application department was recommended to use greater value of capacity in  $V_{OUT}$  pin represented by cascade of the recommended capacitors. The 4x 4.7 $\mu$ F and 10nF were placed in the input in order to bypass it appropriately. The output stage of the converter is bypassed by vendor recommended 2x 100 $\mu$ F capacitors. Note that type of chosen capacitor is X5R and X7R (material of the dielectric - stable capacity across voltage). There is not sketched connection of thermal PAD in the schematic – connected to GND.

Terminals RUN, and FB were left floating, because FB (Feedback) takes its place only in the application of LTC3630 cascade. The RUN pin is dedicated for voltage lockout, floating RUN sets input voltage lockout to internal 3.5V ÷ 3.7V of input voltage.

#### 3.1.3 ADP7142 LDO stabilizer

The main source voltage 3.3V is provided by LTC3630 described upper. However, for ADI SDP purposes, also 5V voltage is required. Due to economy drive, just the LDO was used. There may be occur problem with providing 5V, if input voltage is lower than 5V – output voltage of the LDO is never higher than input. The ADP7412 is originally ADI LDO circuit and there is fixed 5V instance - ADP7142ACPZN5.0 – figure 9.

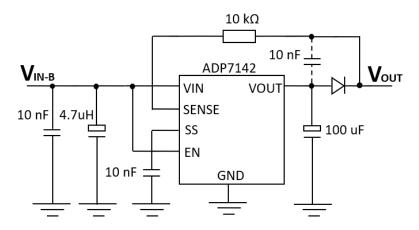

Figure 9 Schematic of the ADP7142 power supply

The input and output of the IC are bypassed by capacitors (recommend values are  $2.2 \mu F$  in the input and output [9]). However, greater capacitors were placed at the terminals. The Pin SS controls soft start of the IC, whereas tied capacitor of the value 10 nF corresponds with calculated time:

$$SS_{TIME} = t_{STARTUP(0pF)} + (0.6 \times C_{SS}) \div I_{SS}$$

(3.3)

Whereas the  $t_{STARTUP(0pF)}$  is constant of value 380µs as well as the bias  $I_{SS} = 1.15\mu A$

The calculate time is:

$$SS_{TIME} = 380 \times 10^{-6} + (0.6 \times 10^{-8}) \div 1.15 \times 10^{-6} = 5.5 ms$$

(3.4)

The feedback composed from the  $10k\Omega$  resistor and optional the 10nF capacitor causes stabilized 5V output voltage (SS adjusts loop gain if VIN is not equal to VOUT), whereas capacitor may prevent circuit oscillations. EN pin connected to VIN permanently enables LDO function. The diode at the output stage prevents reverse current flow – discussed in the subchapter of protection circuitry. Note that the input capacitors are quality X7R/X7S (stable capacity across work voltage range).

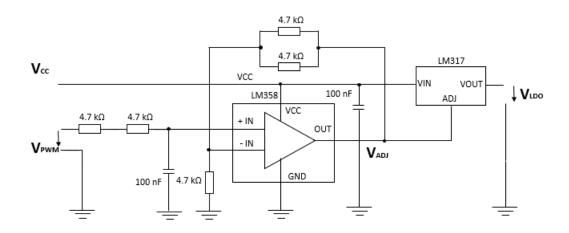

## 3.1.4 Power supply protection circuitry

Refers to the previous subchapter, a few protective discrete parts were used. The main requirement was to prevent overvoltage passed to the power supply terminal damage the circuitry. Generally, digital circuits need interference suppression, thus filters were implemented as well.

Figure 10 Schematic of power protection circuit

The figure 10 depicts the noise suppression and the overvoltage safe circuit. Note that the enclosed external power supply may be used as positive V<sub>SUPPLY</sub> + ground (negative) V<sub>SUPPLY</sub> GND and optional V<sub>SUPPLY</sub> EARTH for enhanced noise suppression. From the input point of view, the input current goes through the PTC – based resettable 0.5A poly-fuse [11], which increase its resistance in case of higher than nominal current, because of semiconductor current heating. Also, there are symmetrically tied 100 pF capacitors to the earth potential. The current through the fuse may be increased by 33V transil, which vice versa decrease its resistance in case of higher than nominal voltage [10].

Consequently, 470uH common mode choke suppresses symmetrical and unsymmetrical interference. The inductor works as the serial inductance in the first mode and suppresses usual high frequency signals. The second mode of operation is, when there is some interference noise in both input lines. The common mode choke produces magnetic flux in its the core, which causes signal subtraction in the magnetic domain – therefore also in signal domain. Choke output is bypassed by additional 10 nF capacitor.

Then, there is a few of power Schottky diodes to block reverse current flow in case of multiply connected power sources [12]. Basically, the diodes prevent to force voltages  $V_{USB\_5V}$  and  $V_{5V\_DGT}$  in case of used  $V_{SUPPLY+}$  and vice versa in another 2 combinations (the three diodes connected to the  $V_{IN-A}$  node). The diode of the  $V_{IN-B}$  and diode of figure 9 may prevent reverse current in case of used SDP daughterboard with external power supply. The 100pF capacitors contains C0G dielectric (very stable) and the rest of capacitors are of X7R dielectric type.

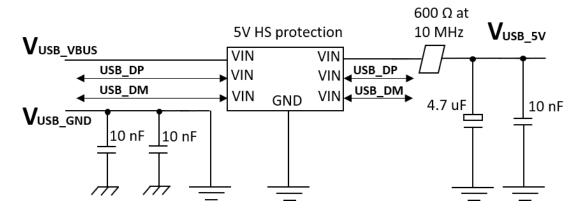

Figure 11 USB power and signal protection circuit

Figure 11 illustrates the USB overvoltage (might never take place) and signal interference protection. All the lines are protected against increased voltage by protective circuit IC [13]. Additionally, there is placed a ferrite bead with convenient  $600\Omega$  at 10 MHz value. Power supply line is also bypassed by two capacitors connected to the  $V_{\text{USB\_5V}}$  node. Also, as in the previous cases the chosen capacitor were used with the X7R dielectric.

The chapter 3.1 and proposed circuits are based on the results of the currently produced EV-COG-AD4050 [14] and its ancestor ADZS - ADuCM4050 EZKIT [7].

# 3.2 Proprietary Low Complexity Ethernet LES

Following chapter is intended to sketch necessary properties of the unreleased – secret prototype with MAC – PHY service implemented. As was mentioned previously in the power supply articles, the FPGA based device has significant consumption depicted in figure 6 (300 mA at normal network traffic).

To describe MAC-PHY as a black box is necessary to say, that in this application is interfaced by host processor using the SPI and a few optional GPIO pins (ISR). Another user part of interface – network interface is supporting convenient double socket "RJ – 45" with internal transformers. In the block are implemented the 10/100-BASE Ethernet domains. Currently is prototype continually developed and would result in the complex SoC chip.

Figure 12 Proprietary MAC-PHY prototype illustration

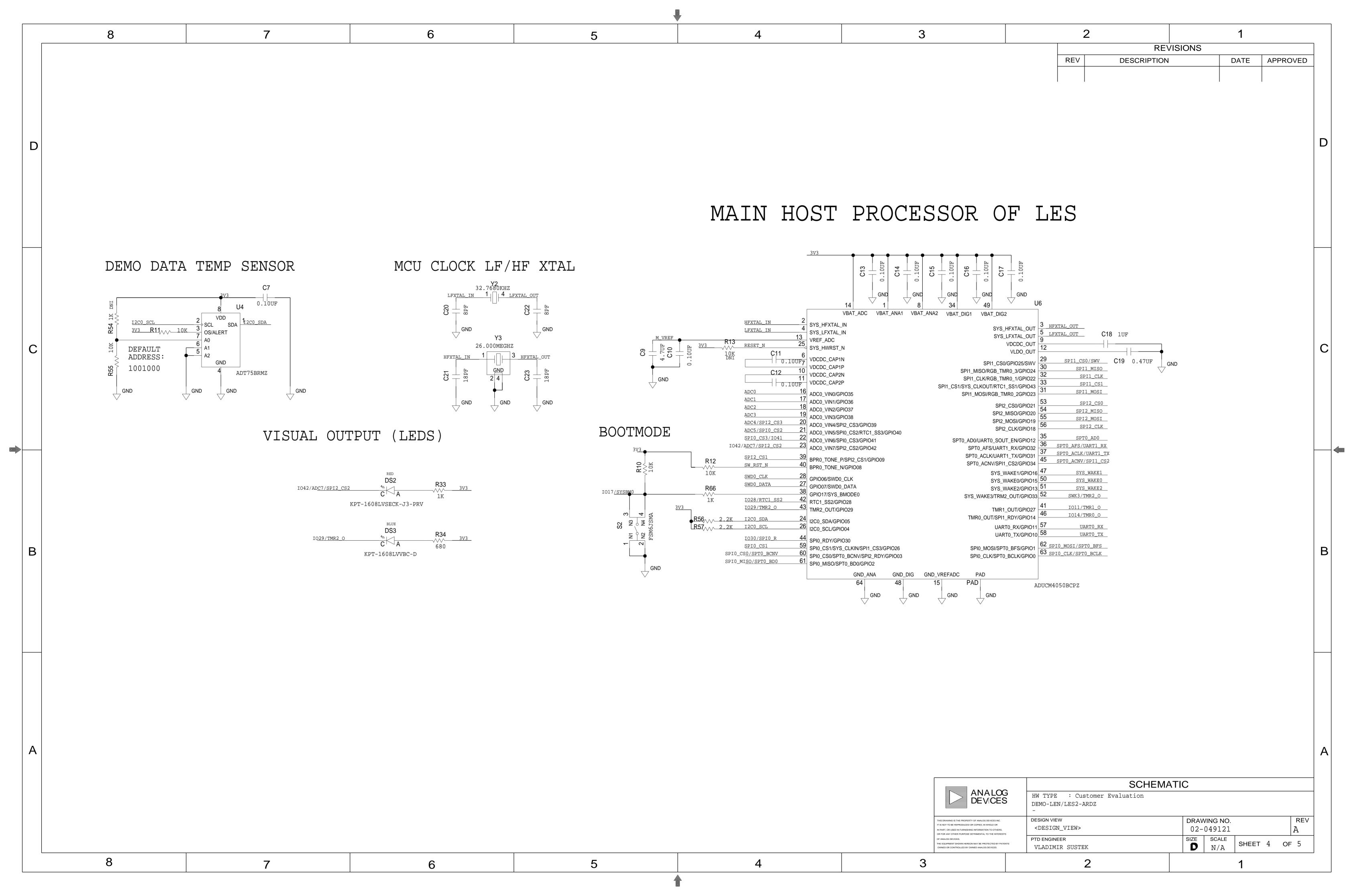

#### 3.3 ADuCM4050 Cortex M4-F microcontroller

The ARM cores are sold and implemented by a lot of silicon vendors. Typically, certain vendor uses convenient core such as M3 or M4, adds its specific peripherals what results in microcontroller for specific usage – see chapter 2.2 and related sources.

The ADuCM4050 might be highlighted for its integrated power management – field of the application in low power sensors for medical, industrial, agricultural and other low power sensor-based applications [15]. The power management offers 3 sleep modes with various depth of system hibernation and support fast wake – up. The deepest sleep mode guarantees consumption around 40 nA and the MCU may be woken using 4 various interrupts. Typical consumption in active mode is 400 μA/MHz [16].

For the general IoT purposes is the ADuCM4050 equipped with up to 128 kB SRAM and 512 kB flash memory. The SRAM could be divided into 32 kB partitions and part of SRAM is optional 4 kB cache for efficient processing. The "F" letter in the M4-F designation expresses the floating-point unit with various support to floating computing. The rest of the features such peripherals might be marked as convenient.

However, in this application the power management will not be used due to significant LES consumption (see 3.1.1). The exact model of the used MCU is the ADUCM4050BCPZ-U2 in the 64 - LCSFP package (9x9x0.75mm).

Following hardware peripherals are used (corresponds to figure 5):

SPI (Serial peripheral Interface):

- SPI 0 ADI SDP

- SPI 1 SPI PMOD socket, microSD slot, SPI/I2C Arduino header

- SPI 2 (highest performance [16]) MAC-PHY module, EEPROM

I2C (Inter Integrated Circuit – Two Wire Interface):

• I2C 0 – I2C PMOD socket, ADI SDP, SPI/I2C Arduino header, Thermometer ADT75

UART (Universal Asynchronous Receiver and Transmitter):

- UART 0 via USB/UART connected to USB

- UART 1 UART/GPIO Arduino header, ADI SDP

SPORT (Serial PORT – parallel SPI):

• SPT 0 – ADI SDP

WAKE External Interrupts:

- WAKE 0 Arduino UART/GPIO header, PMOD SPI

- WAKE 1 MAC-PHY module

- WAKE 2 Arduino UART/GPIO header, SDP

- WAKE 3 Arduino UART/GPIO header

ADC (Analog to Digital Converter) channels:

- ADC 0 Arduino ADC header, SDP

- ADC 1 Arduino ADC header, SDP

- ADC 2 Arduino ADC header, SDP

- ADC 3 Arduino ADC header, SDP

- ADC 4 Arduino ADC header

- ADC 5 Arduino ADC header, SDP

- ADC 6 SDP

- ADC 7 not used

The ADuCM4050 allows (LF) low frequency and (HF) high frequency external clock sources, both instances were implemented – LF using 32.7680 kHz and HF using 26 MHz XTAL.

Then, there are features such as GPIO, Timer, BOOT or various VCC and GND pins, which detailed view is not in range of the thesis – see attached schematic and datasheets [15] [16].

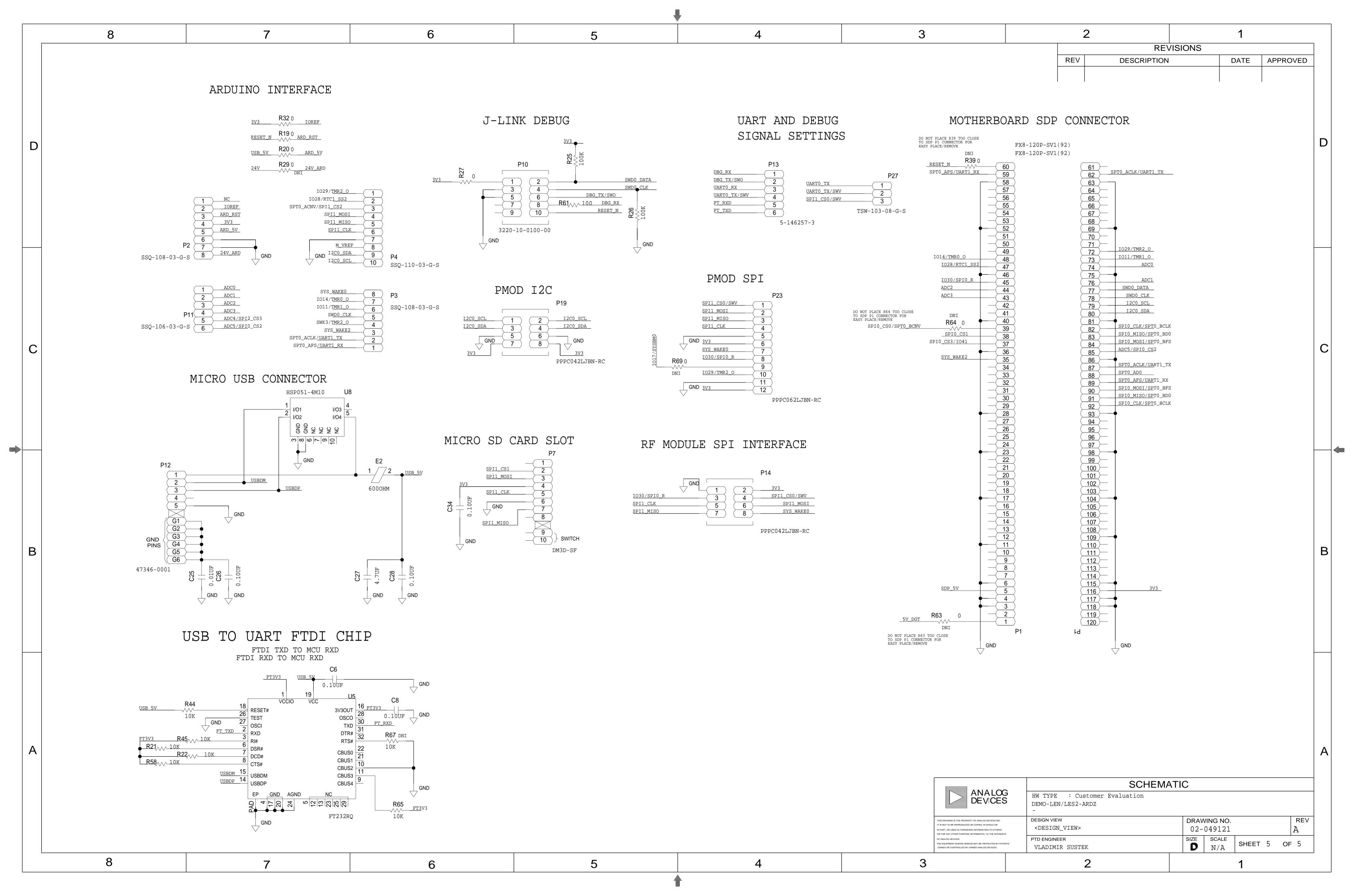

## 3.4 System connector interfaces

One of the main aspects for useful universal embedded system is synoptically sorted interfacing. For development purposes is important to raise enough number of available peripherals and feature - in the best case all of them. However, problems caused by extended wiring may occur (especially in ADC or high-speed digital communication).

Following connectors are required:

- SDP platform 120-pin interface with GPIO, TIMER pins, UART, SPI, I2C, ADC, SPORT and WAKE peripheral

- Arduino interface 4 female 2.54mm headers. In this document divided to Power header, ADC header, SPI/I2C header and UART/GPIO header.

- PMOD interface two row 90° 2.54mm female header according to the Digilent specification, implemented SPI and I2C.

- microSD slot SPI based slot for removable flash microSD card storage

- RJ 45 (double) network connectivity with the system (MAC-PHY)

- J link (9 pin) for ARM debugging/flashing interface

- Power supply 5.5mm jack barrel for powering using conventional connectors

- Socket 3.81mm terminal for powering in industrial conditions

- microUSB for UART interfacing, used USB/UART FT232RQ converter

## 3.4.1 SDP platform

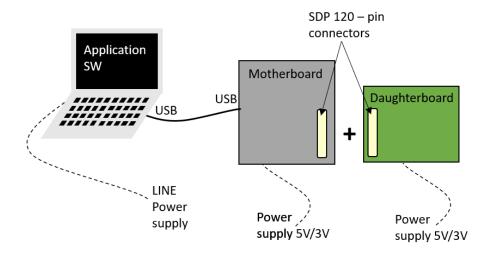

The SDP platform was found by the ADI in order to reuse central elements in system demonstration [17]. Basically, the SDP demonstration system comprises from (figure 13):

- Motherboard The FPGA/MCU based universal board, with 120 pin connectors to interface up to 2 SDP daughterboard devices. Motherboard has USB connector for PC interfacing. Motherboard usually powers daughterboard. There are supported interfaces such an ADC, SPORT, UART, SPI, GPIO/WAKE various parallel ports and I2C (for daughterboard identifying).

- PC convenient desktop or laptop, running application software

- Daughterboard demonstrated module or system board. Daughterboard may sink power supply current from motherboard, but in high consumption cases may be used its external power source. Each daughterboard should have EEPROM with stored ID (accessed via I2C). Kind of protocol to access demonstrated circuit is optional.

This proposed system may be understood as motherboard instance. However, function is very limited in compare to dedicated universal motherboard devices. For more information see attached schematic – page 5 or source [17] and its related.

Figure 13 Block diagram of the SDP system

#### 3.4.2 Arduino interface

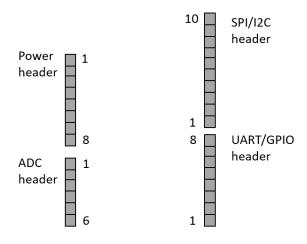

The Arduino standard is one of the most popular standards for amateur technics and programmers. The Arduino is open-source platform based on easy to use software and hardware. From the embedded point of view, The Arduino board may be understood as universal development board with certain implemented MCU. The most famous is the UNO board with 8 – bit Atmel ATmega328 [18]. Although 8 – bit processor board might be mark as insufficient for high performance application, the UNO Arduino contains one important interface - special female 2.54m headers sorting known as the Arduino interface. Figure 14 illustrates sorting of 4 headers. There is power header, ADC header, SPI/I2C header and UART/GPIO header. Nowadays exist a lot of Arduino shields – daughterboard of Arduino, which are hosted by motherboard MCU board and became helpful for easy development in professional embedded field.

Figure 14 The Arduino interface header sorting

In the LEN/LES 2 board was attempted to follow Arduino interface pinout as much as possible. Following chart expresses matches and differences. Note that some requirements could not be follow (missing ATmega timer-related output, the ADuCM4050 provides complex timer outputs).

Table 3 Arduino interface pinout

|   |          |         |         |    | Original            | LEN/LES 2 demo    |

|---|----------|---------|---------|----|---------------------|-------------------|

|   |          |         |         | 10 | ADC5/IC2_SCL        | GPIO/I2C_SCL      |

|   |          |         |         | 9  | ADC4/IC2_SDA        | GPIO/I2C_SDA      |

|   | Original | LEN/LES | S2 demo | 8  | AREF                | M_REF             |

| 1 | NC       | NC      |         | 7  | GND                 | GND               |

| 2 | IOREF    | IOREF   |         | 6  | GPIO/SPI_SCK        | GPIO/SPI_SCK      |

| 3 | RESET    | RESET   |         | 5  | GPIO/SPI_MISO       | GPIO/SPI_MISO     |

| 4 | 3.3V     | 3.3V    |         | 4  | GPIO/OC2A/SXPI_MOSI | GPIO/SXPI_MOSI    |

| 5 | 5V       | 5V      |         | 3  | GPIO/OC1B/SPI_CS    | GPIO/SPI_CS       |

| 6 | GND      | GND     |         | 2  | GPIO/OC1A           | GPIO/RTC1_SS2     |

| 7 | GND      | GND     |         | 1  | GPIO/CLKO/ICP1      | GPIO/TMR2_0       |

| 8 | VIN      | VIN     |         |    |                     |                   |

|   | ,        |         | •       | 8  | GPIO/AIN1           | GPIO/WAKE0        |

|   |          |         |         | 7  | GPIO/AINO/OCOA      | GPIO/TMR2_0       |

| 1 | ADC0     | ADC0    |         | 6  | GPIO/XCK/T1/OC0B    | GPIO/TMR1_0       |

| 2 | ADC1     | ADC1    |         | 5  | GPIO/XCK/T0         | GPIO              |

| 3 | ADC2     | ADC2    |         | 4  | GPIO/WAKE1/OC2B     | GPIO/WAKE3/TMR2_0 |

| 4 | ADC3     | ADC3    |         | 3  | GPIO/WAKE0          | GPIO/WAKE2        |

| 5 | ADC4/I2C | ADC4    |         | 2  | GPIO/UART_TX        | GPIO/UART_TX      |

| 6 | ADC5/I2C | ADC5    |         | 1  | GPIO/UART_RX        | GPIO/UART_TX      |

Table 3 represents pinout and deviation table of the Arduino Headers. Red color highlights deviation in function in compare to original Arduino. Originally, ATmega MCU were used and contains timers with various output functions such Output Compare etc. (OCXY).

ADuCM4050 does not support this fashion of timer output – there is a few universal timer outputs instead. The ADC header deviated in pins 5 and 6 where ADuCM4050 does not support multiplexing with I2C stage. In the UART/GPIO header are deviated pins 8-5. The 8-7 deviates, because ADuCM4050 does not support analog comparator on used pins and 6-7 because of external timer clocks (also not supported). The same problem occurred in the SPI/I2C header pins 4-1 and because ADuCM4050 does not multiplex ADC in the I2C stage (pins 10-9).

Anyway, important features such external interrupt or wake interrupt are followed. Also SPI, I2C, UART and ADC stages are connected to Arduino convenient headers.

#### 3.4.3 PMOD interface

The PMOD is originally Digilent output standard for low frequency interfacing [19]. PMOD is intended for devices of 3V or 5V logic and currents appropriate to digital circuits (at least 2 mA). Logically, the current should not exceed low values of usual digital processing. Nowadays exist a lot of pluggable modules using PMOD interface

such as UART/USB converter, RTC module and various wireless modules, PMOD currently specifies 6 kind of interface and some interface has A and B extinguishing. In the LEN/LES 2 board are used I2C PMOD and SPI type 2 PMOD. Note that PMOD is usually 2.54mm two-row socket with 12 - 24 pins with  $90^{\circ}$  angle.

Figure 15 SPI Type 2A, I2C PMOD connectors

Table 4 PMOD SPI Type 2A, I2C pinout

| PMOD SPI Type 2A |    |   |   |     |      |     |

|------------------|----|---|---|-----|------|-----|

|                  | DV | ഹ | ח | CDI | Typa | 2 / |

|    | <b></b> , | , P.O. —, . |     |     |     |     |       |     |     |     |     |

|----|-----------|-------------|-----|-----|-----|-----|-------|-----|-----|-----|-----|

| SS | MOSI      | MISO        | SCK | GND | VCC | INT | RESET | N/S | N/S | GND | VCC |

| 1  | 2         | 3           | 4   | 5   | 6   | 7   | 8     | 9   | 10  | 11  | 12  |

|    |           | PMOD I      | 2C  |     |     |     |       |     |     | _   |     |

|    |           | SCL         | SCL | SDA | SDA | GND | GND   | VCC | VCC |     |     |

|    |           | 1           | 2   | 3   | 4   | 5   | 6     | 7   | 8   |     |     |

As it is shown at Figure 15 and Table 4, there are more than data lines in case of SPI Type 2A. The INT pin is dedicated for interrupt purposes and is connected to WAKE0 – the highest priority interrupt of the ADuCM4050. The RESET pin may be output pin for slave reset. N/S (Not Specified) are connected to GPIO (see schematic page 5).

#### 3.4.4 USB/UART converter interface

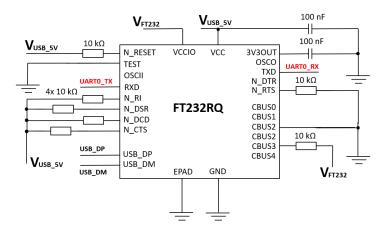

The ADuCM4050 does not support USB stage, so converter for universal PC interfacing is needed. The FTDI USB/UART converter FT232RQ is quite mostly used IC in embedded application [20]. The USB differential signal passed to the input of FT232 is processed and converted to UART protocol. Note that PC, which is sending USB signal requires installed and supported virtual COM ports.

Anyway, the FT232RQ supports conversion of another protocols such RS232 or RS485, thus more than UART RX and UART TX is required in term of the IC pinout. The mentioned chip is used only as USB/UART converter and the rest of the input pins is terminated using 10 k $\Omega$ . Using internal LDO is whole active chip powered by 3.3V, so UART is in the 3.3V LOGIC mode (ADuCM4050 supports only this mode). The outputs are left floating except N RTS (Request to Send) – may be used for flow control with N\_CTS cooperation. Note that UART RX and UART TX signals must swapped when connecting to the MCU UART stage.

Figure 16 Schematic of USB/UART converter

#### 3.4.5 Auxiliary circuitry

The scope of the diploma thesis is limited, so following chapter is only brief comment to the rest of used IC is the design.

Reset Circuit ADM6315-29D2ARTZR7 [21] supervises power voltage and generates reset signal, when voltage drops below its trip-point 2.93V to prevent brown out of the MAC-PHY module at the first (ADuCM4050 operates at much lower voltage level). The reset signal is then connected to the NAND gate, so MAC-PHY can be reset by MCU GPIO signal or by reset circuit (page 3 of schematic).

The ADT75 is 1° C precision thermometer with the I2C output and its address is set by external resistor [22]. Thermometer should be placed further from the MAC-PHY and MCU otherwise will measure its power dissipation.

To distinguish more LEN/LES 2 boards according to the MAC addresses, there is used EEPROM 25LC01A of the storage size 128kB with lock (read-only) capability [28].

It is planned to use a few LEDs for signalizing POWER, RESET, and 2 GPIO LEDs. For boot and reset options, the RESET and BOOT button is intended (pull upped to VCC).

# 4 HARDWARE PROPOSAL AND DEBUG

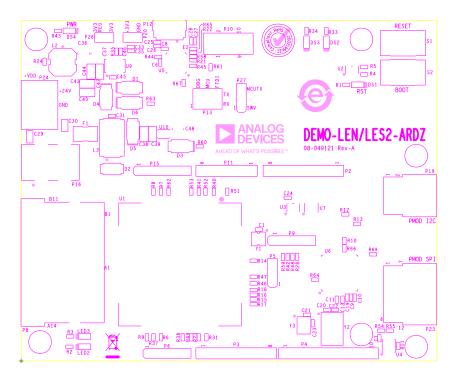

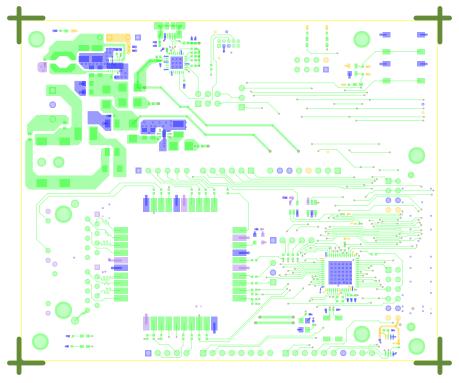

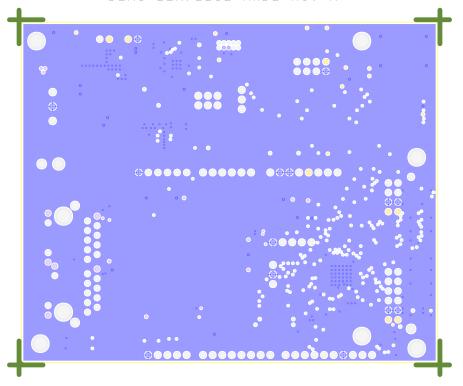

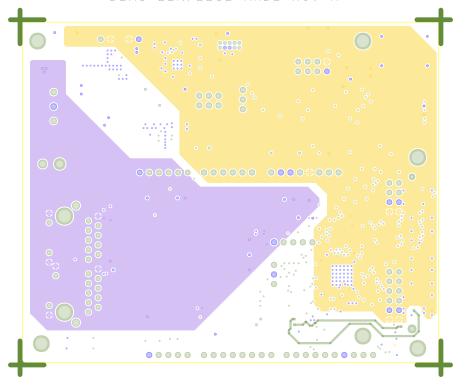

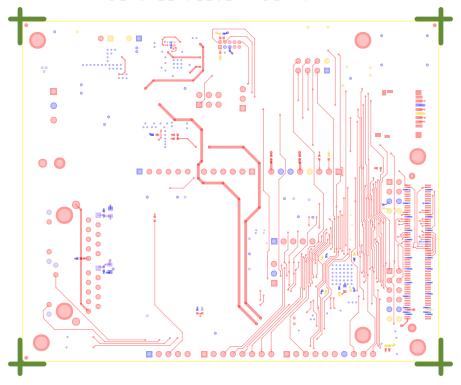

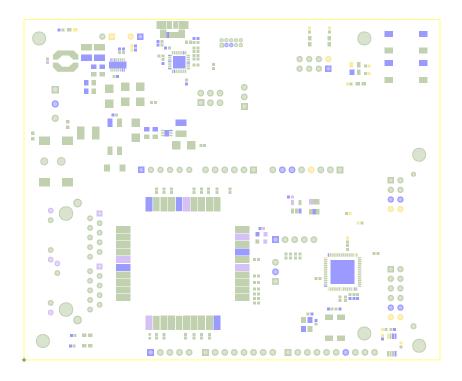

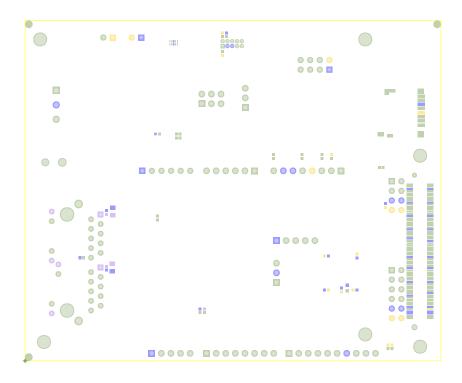

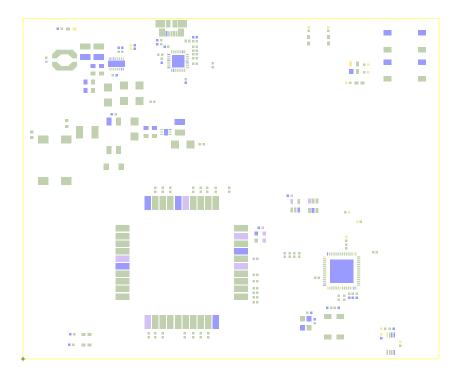

This chapter focuses on the hardware PCB parts placement and PCB layout. The placement of the parts had been done by writer of the thesis, however layout services such as routing and layering had been done by ADI layout specialist – Pat Sheahan (internal ADI regulation). The precise hardware layout is included in appendix (the end of the document). Note that board is 4 - layer.

## 4.1 Parts placement

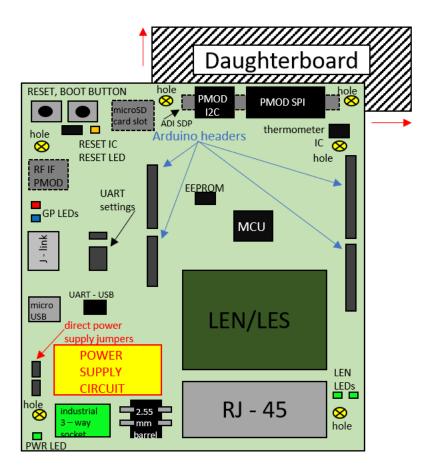

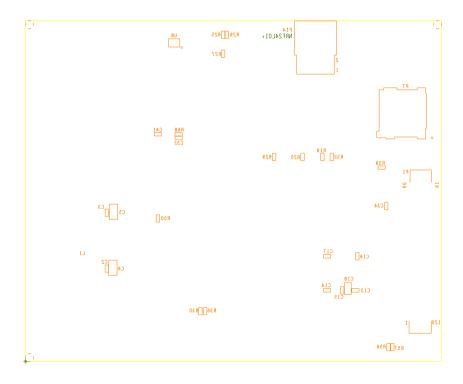

Refer to chapter 4, there is needed a few restrictions during the parts placement. For example, the Arduino interface requires specific placement of all 4 connectors regards to coordinates. Also, the MAC-PHY block should be placed as close as possible to its Ethernet connector. Generally, useful components such interface connectors should be placed to correct places for comfortable usage and debug by user/developer. The result of placement discussion is following placement proposal of figure 17. The scale of the picture approx. corresponds with real intended dimensions (if page size is A4).

Figure 17 LEN/LES 2 board

#### 4.1.1 MAC-PHY – RJ 45

The most important trace connection is between MAC-PHY and RJ-45 connector, so both parts are placed close to each other, and its interfacing differential signals +Tn, – Tn and +Rn, -Rn are routed with the same length using meander trace (n is port number: 1, 2). In case of not matched traces could occur errors during delayed signal of any ethernet line. Note that the MAC-PHY block requires 25MHz oscillator, which must be placed close as well.

#### 4.1.2 Arduino interface

As it is explained in the chapter 3 (Arduino section), the correct sorting and placement for Arduino shield compatibility is needed [18]. The Arduino top orientation of figure 17 is portrait, so upper left connectors contains power signals. Also, between the Arduino interface and RJ-45 connector should be leave at least 2-3cm place, because the Arduino shields are often bigger than dimensions of the connector interface.

## 4.1.3 MCU, EEPROM

Regards to intended high speed SPI communication (up to 2.5Mbps) between MCU and the MAC-PHY port, the distance between them should be small and no sources of interference should be located around. On the other hand, the EEPROM shall be used only during startup to read MAC address bytes, so its placement has no special restrictions.

#### 4.1.4 PMOD SPI, PMOD I2C, ADI SDP, RF connector

PMOD connectors usually lay on the PCB (axial connector orientation), so the best location in any PCB edge, that's why are both PMODs placed to the top edge of the board. Also, at least centimeter clearance between them may improve connector's accessibility. The ADI SDP motherboard connector shall be placed at the bottom side of the board (because daughterboard connector is on the top) and except holes for bolting has special requirement. To explain this requirement, see Figure 17 and the hatched daughterboard. The red arrow shows that daughterboard could be arbitrarily high and wide of the arrow directions, but the left bottom corner of the daughterboard (from the point of view Figure 17) must be aligned as depicted. This fact limits placing dimensional components and stand-offs around the SDP connector such. The RF connector is 8-pins two row connector of nRF24L01+ transmitter/receiver and shall be placed to the edge for compatibility.

#### **4.1.5 Buttons**

As the conventional buttons are by finger accessible almost everywhere, they should be placed to the corner of the LEN/LES 2 board. RESET button capability only resets whole system (drives reset circuit), but BOOT button except boot functionality of the MCU may be used as GPIO button of the microcontroller.

#### 4.1.6 Slot microSD

The slot for the microSD card is usually placed at the bottom of the boards, so this board shall not be exception. Also, placing to the edge of the board improves accessibility

## 4.1.7 USB micro, J-LINK – pin

For device connectivity, it is necessary to place USB connector to the any edge of the board. J-LINK debug/flash port shall be placed to the edge as well for better connectivity. For flawless communication between USB and MCU the USB-UART FDTI converter shall be placed close to the USB connector. Note that J-LINK connector P10 is only way to debug/flash MCU (except UART0 in the boot mode [7][16]).

#### 4.1.8 LEDs

There are four LEDs indicating LEN/LES 2 system. The orange LED placed in the upleft corner will be used when is the system in reset state (RESET button pressed or reset IC triggered undervoltage). The green LED is placed in the left-down corner shall light when the board is powered (3.3V power source supplies voltage). Two general purpose LEDs of red and blue color located on the left-upside are connected via pull-ups to 3.3V and MCU.

#### 4.1.9 Power Source

Many times, placement of the switched power source is tricky task. However, in this design there is no sensitive device, as the ethernet PHY communicates on the much higher frequency than LTC3630 switches (estimated frequency according to the current and load is 80kHz [8]). For better accessibility, the source circuitry will be placed to the separate part of the (left-down corner) as well as its connector (DC barrel and three-way terminal).

#### 4.1.10 Thermometer ADT75

The thermometer is placed as far as possible from the MAC-PHY (expected increased temperature around this block) to measure approximate average temperature of the board (left up).

#### 4.1.11 The remaining components of the schematic

In the schematic (included in attachments in the end of this document) there are a few DNI connectors for debugging, especially of MAC-PHY block (e.g. SPI), as well as direct connector for 3.3V supply (in case of main power source failure) and most of the crucial traces is connected by  $0\Omega$  resistors (some of the also DNI) for disconnections or probe accessibility. Thus, resistor, which may be changed were not placed to the plastic parts such as header female connector (to do not damage plastic by heat). The crystals for MCU and protection diodes were placed to the related components.

# 4.2 Hardware getting started and hardware bugs

The LEN/LES 2 board had been manufactured by analog device PCB vendor, so no manual soldering or placement was needed. The real board photograph is following picture (figure 18). For a first time, board was powered using power source with current limit and no fatal shortcut was detected.

Figure 18 LEN/LES 2 board

However, the first bug was found as the green LED DS4 is placed in reverse mode. To debug this is needed only remove and rotate appropriately DS4.

# PWR INDICATOR PLACE CLOSE TO THE USB AND JACK R43 GND GND GND GND KPT-1608LVZGCK

Figure 19 Wrong LED orientation

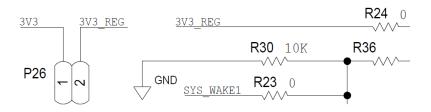

Originally intended capability to disconnect completely power supply is not possible during misconnection of 3V3 and 3V3\_REG. Figure 20 depicts problem, whereas R24 must be removed and wire placed between 3V3 and right side of resistor (MAC-PHY power supply). This problem is not fatal, and board can work normally, but if P26 jumper is removed, MAC-PHY is still powered.

Figure 20 3V3 and 3V3 MAC-PHY misconnection

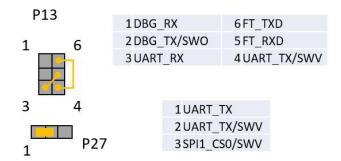

The third found bug is misunderstanding when choosing two-row male pin header P13. The jumper purpose was to set up to 4 different UART settings using two jumpers. All of parts used in the system are in ADI corporal library and this header was there as well. However, header in the library has pinout not usual to header, but pinout as integrated circuit. That is why is not possible to use 2 jumpers as originally intended. To fix this bug is needed to use wires terminated by female header or create female matching reduction. To understand this problem more, see schematic included in the appendix.

Connect at P13: 6 and 5 for FT232RQ loopback test

Figure 21 Wrong P13 pinout

Of course, the firmware development and creating external equipment was done gradually, however to approve system consumption in usual mode following figure 22 depicts measurement of current consumption during TCP bidirectional traffic (LWIP TCP-layer firmware is running and exchanges string messages with the PC).

Figure 22 LEN/LES 2 board normal consumption

Figure 22 shows, that during normal operation (with  $_{LW}IP$  stack and TCP bidirectional communication with 0.3s period, payload > 50 bytes) and whole system takes 303 mA at voltage 3.034V provided by on board power source. Note that the same system with powered off MAC-PHY takes 8.3 mA (estimated MCU consumption running on the frequency 26 MHz is  $\approx 1.5$  mA [15]).

Arduino interface, RF (nRF24L01+) interface, PMODs and SDP was tested successfully as well as buttons and LEDs. The most important part MAC-PHY also communicates with the MCU and basic firmware of static frame send/receive approved that system is ready to implement main assigned goals (for more see following chapter).

All of three currently known bugs do not prevent normal operational of the MCU and MAC-PHY (if developer does not fix them).

#### 5 LWIP IMPLEMENTATION

There is a lot of customized LwIP implementation available under free license. As was mentioned in chapter 2, originally LwIP is based on Adam Dunkel's stack. In fact, the basic LwIP implementation to custom system may include only porting layer implementation and system settings definition file. This chapter may be helpful for someone who attempts implement LwIP for a first time (always is needed device such as MAC-PHY).

### 5.1 Getting started with MAC-PHY

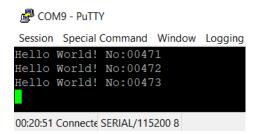

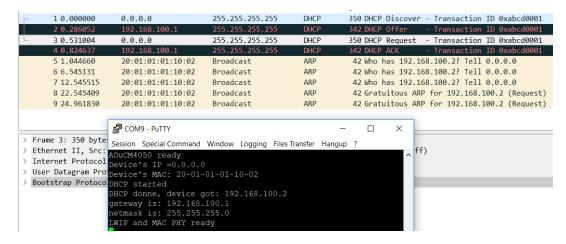

To use the MAC-PHY with LwIP, necessary functionalities had to be tested and defined. To keep the proprietary driver of MAC-PHY secret, wrapper layer MAC\_PHY has been implemented and lower than this layer is not published in this document. The first firmware functionality is UDP Syslog frame send and receive with string payload of the common first call "Hello World" with MAC address of device and frame number. Syslog is UDP based protocol intended for debug messages, so it's useful for test purposes [25].

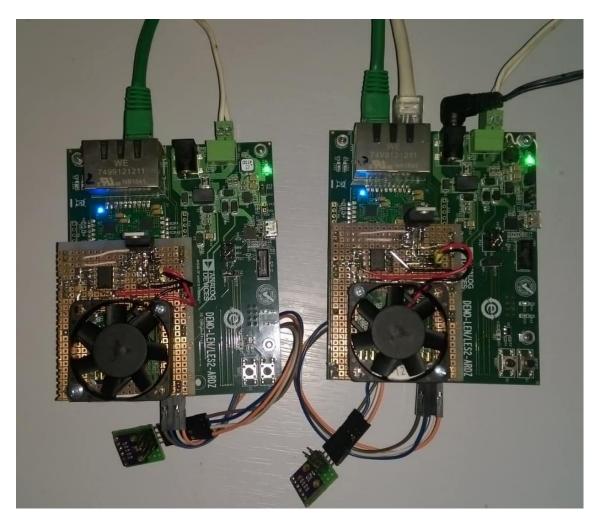

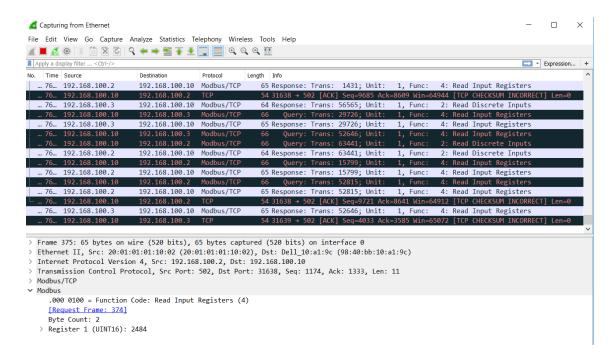

For the test, two LEN/LES 2 were used. First board worked as the Syslog transmitter, meanwhile the second as the receiver. Transmitter worked on its own with periodically triggered frame sending with no logging and receiver's firmware sent all received valid frames to the UART console (logged on the PC via putty terminal). However, for illustration, following Figure 23 depicts caught frames by WireShark (transmitter connected to the PC), Figure 24 mentioned communication of two LEN/LES 2 boards.

```

3092 554.714511

192.168.100.2

192.168.100.10

66 KERN.DEBUG: Hello World! No:00115

Svslog

66 KERN.DEBUG: Hello World! No:00116

3093 554.814775

192.168.100.2

192.168.100.10

Syslog

3094 554.915044

66 KERN.DEBUG: Hello World! No:00117

192.168.100.2

192.168.100.10

Syslog

3095 555.015307

192.168.100.2

192.168.100.10

Syslog

66 KERN.DEBUG: Hello World! No:00118

> Frame 3093: 66 bytes on wire (528 bits), 66 bytes captured (528 bits) on interface 0

Ethernet II, Src: 02:00:00:00:10:01 (02:00:00:00:10:01), Dst: IPv4mcast 01 (01:00:5e:00:00:01)

Internet Protocol Version 4, Src: 192.168.100.2, Dst: 192.168.100.10

User Datagram Protocol, Src Port: 1024, Dst Port: 514

> Syslog message: KERN.DEBUG: Hello World! No:00116

9999

0010

0040

```

Figure 23 Wireshark Syslog frame receiving

Figure 24 Frame Syslog payload received by LEN/LES 2 receiver

```

1. #define MAC_LNG (uint32_t)(6)

2. #define FRAME_LNG (uint32_t)(66)

3. #define PLD OFFSET (uint32 t) (45)

4.

5. //#define RX 1 /* When receiver should be flashed */

6. //#define TX 1 /* When transmitter should be flashed */

7

8. #ifdef TX

9

10. uint8 t device mac[MAC LNG] = \{0x2, 0x0, 0x0, a\}

11.

0 \times 0, 0 \times 10, 0 \times 1;

12.

13. uint8 t multicast mac[MAC LNG] = \{0x1, 0x0, 0x5e,

14.

0 \times 0, 0 \times 0, 0 \times 1;

15.

16. uint8 t udpframe[FRAME LNG] = {

17.

0x01, 0x00, 0x5e, 0x00, 0x00, 0x01, /* Multicast address */

18.

0x02, 0x00, 0x00, 0x00, 0x10, 0x01, /* Device MAC */

19.

0x08, 0x00,

/* IP Ethertype (0x0800) */

20.

/* IP Header */

21.

22.

0x45,

/* IP V4 -- header length 20 bytes */

23.

0x00,

/* differentiated services field */

/* total length (length of ASCII + 31)*/

24.

0 \times 00, 0 \times 34,

25.

0 \times 00, 0 \times 07,

/* identification */

/* flags/fragment offset */

26.

0x00, 0x00,

27.

/* time-to-live 255*/

0xFF,

/* protocol -- UDP */

28.

0x11,

/* header checksum */

0 \times 00, 0 \times 00,

29.

192u, 168u, 100, 2u, /* Receiver's IP */

30.

192u, 168u, 100, 10u,/* Transmitter's IP */

31.

32.

33.

/* UDP Header */

34.

0 \times 04, 0 \times 00,

/* UDP source port 1024 */

0x02, 0x02,

/* UDP destination port 514 Syslog */

35.

/* length (total 20, ASCII + 11) */

36.

0 \times 00, 0 \times 20,

/* UDP checksum (0 = don't check) */

37.

0 \times 00, 0 \times 00,

38.

/* Syslog Message */

39.

/* KERNAL DEBUG message */

0x3C, 0x37, 0x3e,

40.

/* message contents (ASCII) */

41.

42.

/* Prepared 21 space characters for further payload*/

43.

44.

45.

46.

47.

```

```

48. #elif RX

49. uint8_t *p_frame = NULL;

50. uint32_t rx lng = 0;

0x0, 0x10, 0x2;

52.

uint8_t multicast mac[MAC LNG] = \{0x1, 0x0, 0x5e,

53.

54.

0x0, 0x0, 0x1;

55.

56.

#endif

57. int main(int argc, char *argv[]) {

58.

59.

uint16 t frame num = 0;

60.

/* IDE generated pin multiplex */

61.

adi initComponents();

62.

/*Initialize ADuCM4050 LEN/LES 2 board peripherals */

63.

platform len les2 init();

64.

/* Initialize MAC-PHY */

65.

MAC PHY start up();

66.

/* Set device's MAC address */

67.

MAC PHY static mac add (device mac);

68. #ifdef TX

69.

/* Calculate necessary IPv4 checksum */

70.

Ipv4 CalcOutGoingChecksum(udpframe);

71.

72.

73.

while(1){

74.

/* Send frame and wait 100 ms and increment frame

75.

number*/

76.

MAC PHY send frame (udpframe, FRAME LNG);

77.

sprintf((char*)udpframe + PLD OFFSET,

"Hello World! No: %05d", frame num);

78.

79.

frame num++;

80.

tim delay ms(100);

81.

82.

#elif RX

83.

MAC PHY static mac add(multicast mac);

84.

85.

while(1) {

86.

87.

/* Poll for receive frame (non-blocking request)*/

MAC PHY receive frame();

88.

89.

/* Get the frame */

90.

p_frame = MAC_PHY_get_buff(&rx_lng);

91.

If valid frame received, print its number, content

92.

* and clear receiving buffer */

93.

if(rx lng != 0) {

94.

print frame(p frame + PLD OFFSET,

95.

FRAME LNG, frame num);

96.

frame num++;

97.

MAC PHY clear buff();

98.

99.

100. #endif

101.

102.}

```

The code snipped mentioned here may be helpful for beginners implementing ethernet system with different MAC-PHY, especially pre-generated *udpframe* array with filled

multicast MAC address. Note that many MAC-PHYs does not have it included. Be careful, the IPv4 header checksum must be calculated.

Important is after initializing MAC-PHY fill the MAC address table with expected addresses (line 67, 83). For example, current MAC-PHY was not capable to receive multicast packet without adding multicast MAC (line 83).

#### 5.2 LWIP porting

According to the [26] and [27] (getting started sections), only four files of whole LwIP stack may be edited to customize stack for specific MAC-PHY (Ethernet periphery). So, for a first time (of the LwIP implementation) is the best way to download free LwIP available at [26] and only override settings of foreign customization. The first is *lwipopts.h*, which contains definitions customizing default LwIP stack settings such service enabling (e.g. whether DHCP, UDP, TCP ... are enabled). Then very important definitions are whether LwIP runs with or without RTOS (this LwIP runs without) and the settings of checksum calculation. MAC-PHY used in the LEN/LES 2 board does not calculate frame checksums on its own, so software calculations are needed (so defined to be set in *lwipopts.h*). Following code snippet of the *lwipopts.h* includes mentioned definitions of NO\_RTOS – NO\_SYS LwIP with software checksum calculations and disables RTOS LwIP related modules etc. Note that memory alignment for 32-bit MCU shall be 4.

```

#ifndef __LWIPOPTS_

1.

2.

#define LWIPOPTS H

3.

#ifdef __cplusplus

extern "C" {

4.

5.

#endif

6

7.

8.

9

10. #define WITH RTOS

0

11. #define NO SYS

1

12. #define CHECKSUM BY HARDWARE

0

13. #define SYS LIGHTWEIGHT PROT

0

14. #define MEM ALIGNMENT

4

15. #define LWIP ETHERNET

1

16. #define LWIP DNS SECURE

7

17. #define TCP SND QUEUELEN

9

18. #define TCP SNDLOWAT

1071

19. #define TCP SNDQUEUELOWAT

5

20. #define LWIP NETCONN

0

21. #define LWIP SOCKET

0

22. #define RECV BUFSIZE DEFAULT

2000000000

23. #define LWIP STATS

24. #define LWIP CHECKSUM CTRL PER NETIF

25.

26.

#endif

```

The second file and the most important is *ethernetif* module adapting representing layer between LwIP and custom MAC-PHY (ethernet periphery). The *ethernetif* will be discussed later. To be precise, required files to be change are also *cc.h* and *sys\_arch.h*. The *cc.h* includes definitions of the data types (LwIP is not written using stdint.h library, so e.g. instead of uint8\_t type is used u8\_t etc.) The sys\_arch.c includes mainly necessities for RTOS based LwIP, so both may be simply reused in this case.

#### **5.2.1** Porting layer ethernetif

As was discussed upper, this module is the most necessary to be customized. This module interfaces input/output of used ethernet hardware and the module quality and reliability will be shared and inherited across whole LWIP. Also, it is recommended to attempt override any *ethernetif* then bare metal development.

In total, 7 functions are implemented in this layer including initialization, input, output and system time management (LwIP counts with 1ms timer). This means, that except input/output driver for customized MAC-PHY is needed to implement also reliable source of the 1 millisecond ticks. Initialization function is easiest and concerns only simple ethernet interface initialization, eventually storing static MAC address table. Then very important settings of the *netif* structure such an ARP setting, hardware address settings and set the flag signalizing link up [26][27]. The *netif* structure is passed through whole LwIP and includes also device IP address etc.

```

1. static void low level init(struct netif *netif) {

2.

3.

uint8 t mac addr[6] = { 0 };

/* Start MAC-PHY, read MAC address (from EEPROM)

4.

5.

and store to the device*/

MAC PHY start up();

6.

MAC PHY read MAC (mac addr);

7.

8.

MAC PHY static mac add (mac addr);

9

10.

netif->flags |= NETIF FLAG LINK UP;

11. #if LWIP ARP || LWIP ETHERNET

/* set MAC hardware address length */

12.

13.

netif->hwaddr len = ETH HWADDR LEN;

14.

/* set MAC hardware address */

15.

netif->hwaddr[0] = mac addr[0];

16.

netif->hwaddr[1] = mac addr[1];

17.

netif->hwaddr[2] = mac addr[2];

18.

netif->hwaddr[3] = mac addr[3];

19.

netif->hwaddr[4] = mac addr[4];

20.

netif->hwaddr[5] = mac addr[5];

21.

/* maximum transfer unit */

22.

netif->mtu = 1500;

23. #if LWIP ARP

24.

netif->flags |= NETIF FLAG BROADCAST | NETIF FLAG ETHARP;

25. #else

26.

netif->flags |= NETIF FLAG BROADCAST;

27. #endif

28. #endif

29.

```

The output function simple assembles packet content in pbuf chained structures (see chapter 3) and sends.

```

1. static err t

2. low level output(struct netif *netif, struct pbuf *p) {

3.

4.

err_t errval = 0;

5.

struct pbuf *q;

6.

uint8_t buffer[1024];

7.

uint32 t bufferoffset = 0;

8.

for (q = p; q != NULL; q = q->next) {

9.

10.

memcpy(buffer + bufferoffset, q->payload, q->len);

11.

bufferoffset += q->len;

12.

13.

errval = MAC PHY send frame(buffer, bufferoffset);

14.

15.

return errval;

16. }

```