Návrh jádra procesoru architektury RISC-V v FPGA – Jaroslav Körner

Jaroslav Körner

Bachelor's thesis

Návrh jádra procesoru architektury RISC-V v FPGA

RISC-V architecture based processor core in an FPGA

Abstract:

Tato bakalářská práce se zabývá návrhem jedno jádrového procesoru architektury RISC-V32I, tedy procesoru s 32 bitovou adresací paměti pracující nad datovým typem integer. Návrh byl omezen na neprivilegovaný instrukční soubor. Jádro procesoru je navrženo v jazyce VHDL. Tento návrh byl následně otestován pomocí simulace v prostředí Xilinx Vivado. Celková funkčnost je předvedena jednoduchým demonstračním …moreAbstract:

This bachelor thesis deals with a design of a single-core processor of the RISC-V32I architecture, i.e. a processor with 32-bit memory addressing and working over the integer data type. The design was limited to unprivileged instruction set. The processor core is designed in the VHDL language. This finished design has been tested using simulation in Xilinx Vivado environment. The overall functionality …more

Language used: Czech

Date on which the thesis was submitted / produced: 22. 5. 2023

Thesis defence

- Supervisor: Ing. Martin Rozkovec, Ph.D.

Citation record

ISO 690-compliant citation record:

KÖRNER, Jaroslav. \textit{Návrh jádra procesoru architektury RISC-V v FPGA}. Online. Bachelor's thesis. Liberec: Technical University of Liberec, Faculty of Mechatronics, Informatics and Interdisciplinary Studies. 2023. Available from: https://theses.cz/id/qkjnfb/.

The right form of listing the thesis as a source quoted

Körner, Jaroslav. Návrh jádra procesoru architektury RISC-V v FPGA. Liberec, 2023. bakalářská práce (Bc.). Technická univerzita v Liberci. Fakulta mechatroniky, informatiky a mezioborových studií

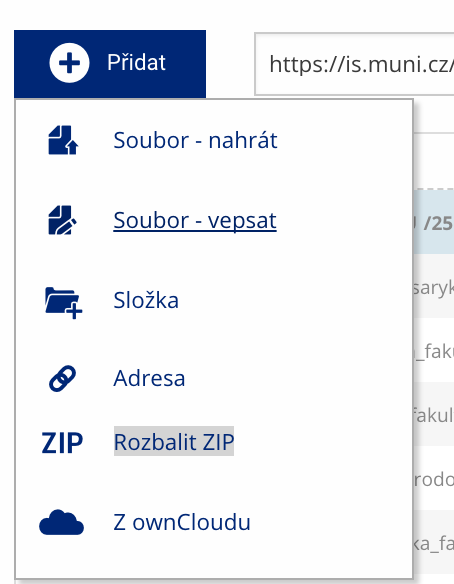

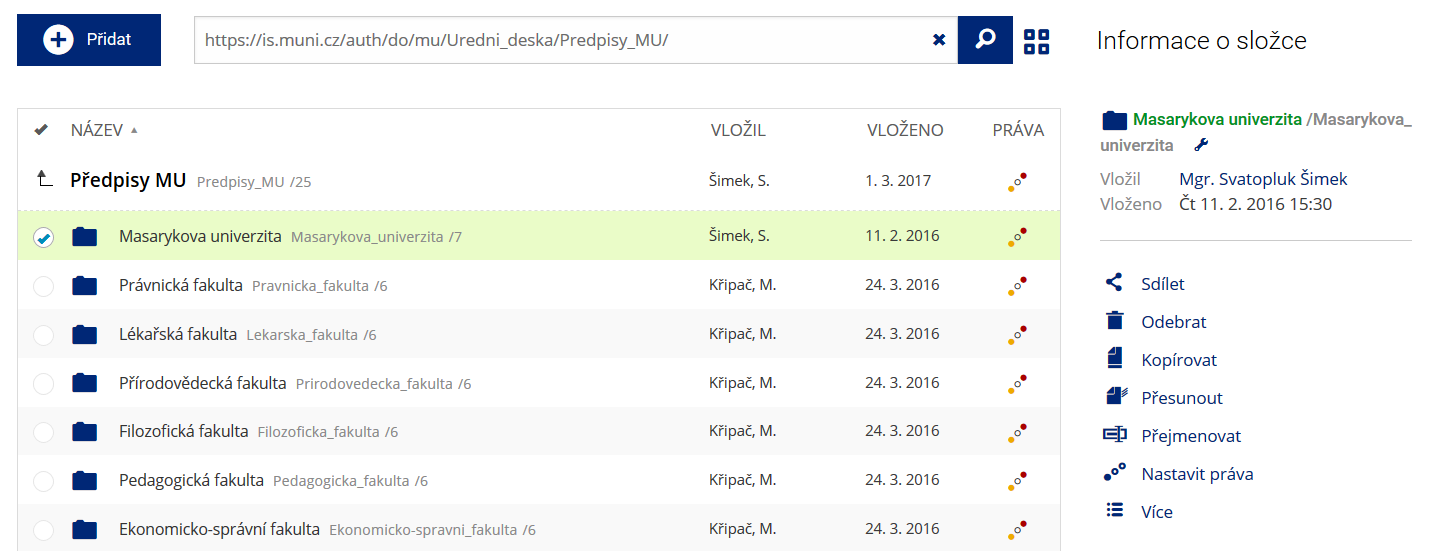

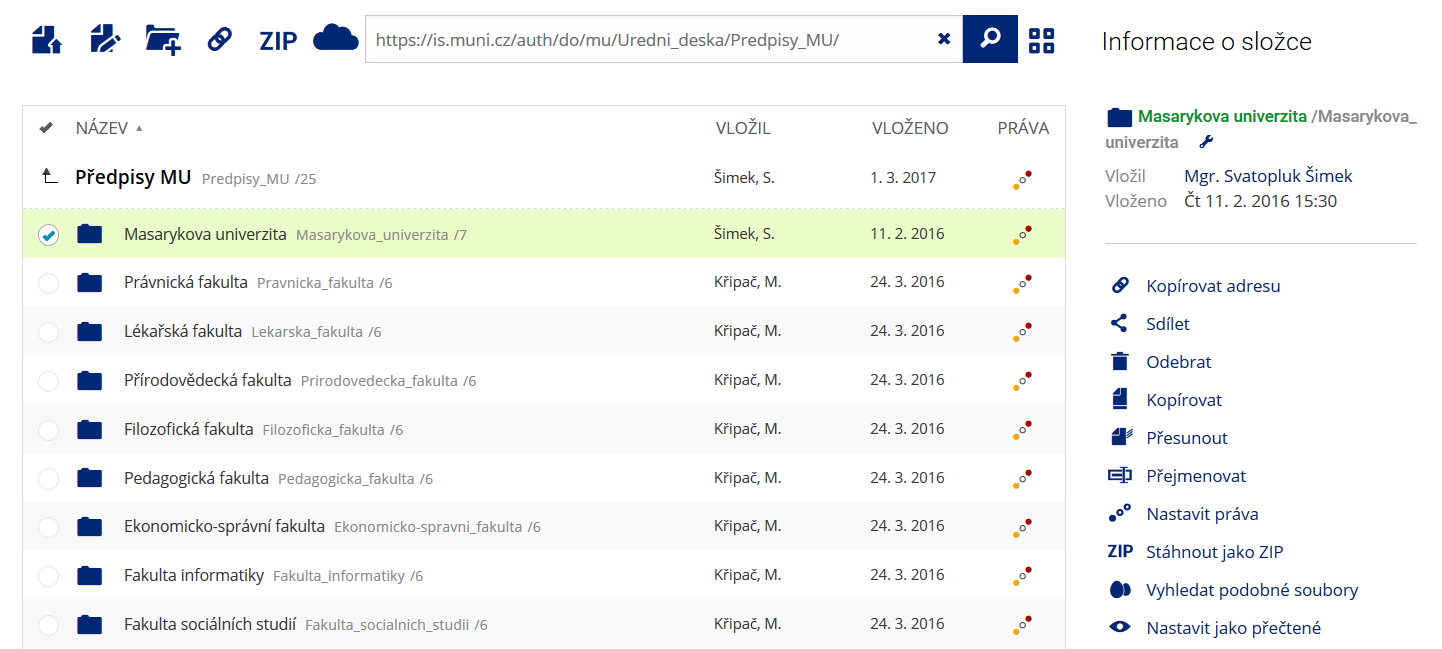

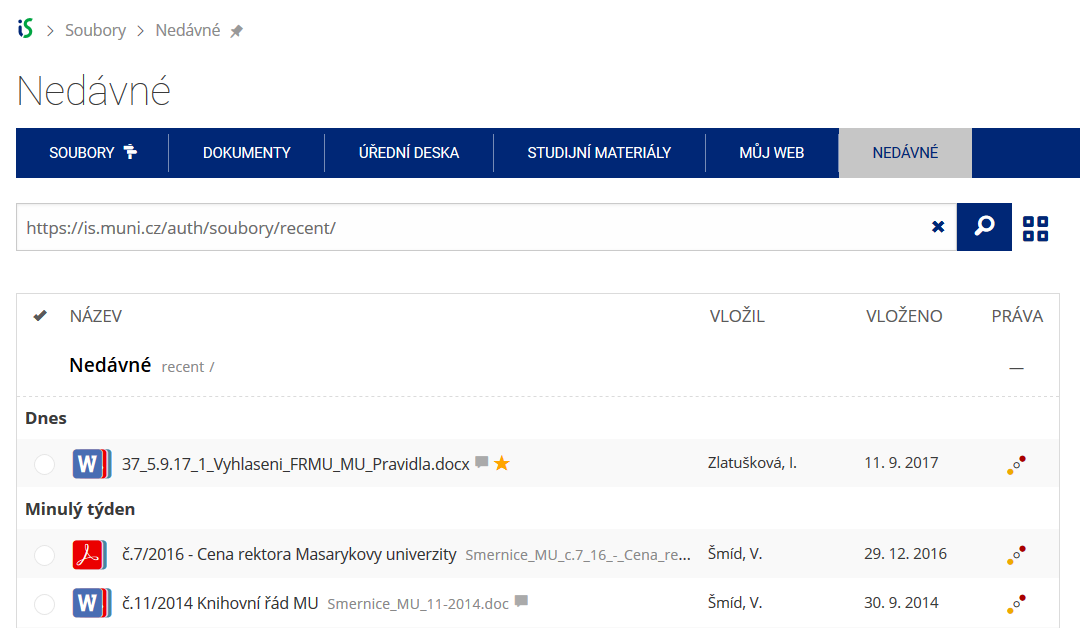

Full text of thesis

Contents of on-line thesis archive

Published in Theses:- světu

Other ways of accessing the text

Institution archiving the thesis and making it accessible: Technická univerzita v Liberci, Fakulta mechatroniky, informatiky a mezioborových studiíTechnical University of Liberec

Faculty of Mechatronics, Informatics and Interdisciplinary StudiesBachelor programme / field:

Information Technology / Inteligentní systémy

Theses on a related topic

-

Implementace šifrovacích algoritmů v jazyce VHDL

Lukáš Fruněk -

Zabezpečovací systém s logováním na SD kartu vytvořený z přípravku Nexys4 v jazyce VHDL

Bohdan Jůza -

Návrh pokročilé architektury procesoru v jazyce VHDL

Daniel Slavík -

Implementace šifrovacích algoritmů v jazyku VHDL

Petr Kožený -

Návrh rozhraní základních sběrnic v jazyce VHDL

Petr Toman -

Aplikační rozhraní pro podporu grafiky v jazyce VHDL

Petr Vlček -

Simulácia a testovanie kombinačných obvodov vo VHDL

Jozef Bernát -

Bezztrátové komprese obrazu v embedded zařízeních

David Ulman

Name

Posted by

Uploaded/Created

Rights