## FACULTY OF MECHATRONICS, INFORMATICS AND INTERDISCIPLINARY STUDIES $\underline{TUL}$

#### **Master Thesis**

# Implementation of real-time digital signal processing algorithms using STM32F7xx series microcontrollers

Study programme: N0714A150003 Mechatronics Author: **Muhammed Çagri Küçükalp** Ing. Miroslav Holada, Ph.D.

Institute of Information Technology and Electronics

Liberec 2024

### **Master Thesis Assignment Form**

## Implementation of real-time digital signal processing algorithms using STM32F7xx series microcontrollers

Name and surname: Muhammed Çagri Küçükalp

Identification number: M21000195

Study programme: N0714A150003 Mechatronics

Assigning department: Institute of Information Technology and Electronics

Academic year: 2022/2023

#### **Rules for Elaboration:**

- 1. Familiarize yourself with the STM32F7xx microcontroller. Focus on hardware support for digital signal processing computations.

- 2. Design firmware that will process the digital signal from the ADC in real time and write the results to the DA converter or send them to a higher-level system via a communication line.

- 3. Functionalities to be performed by this firmware are digital filtering (FIR and IIR filters), spectrum calculation, and simple recognition algorithms (DTMF detection).

- 4. Create a Matlab application that will be used as a graphical user interface for this firmware. Its purpose will be to compute the parameters of data processing algorithms according to the user specification and send them to the STM board via USB (CDC Virtual COM port) interface. It will also display the data resulting from data processing performed by firmware.

- Test the developed firmware and analyze its performance limits (maximum sampling and data processing speeds). Make sure that your firmware fully utilizes the capabilities of the processor used.

Scope of Graphic Work: as needed by documentation

Scope of Report: 40-50 pages

Thesis Form: printed/electronic

Thesis Language: english

#### **List of Specialised Literature:**

- [1] Chassaing R.: Digital Signal Processing and Applications with the TMS320C6713 and TMS320C6416 DSK, Wiley-IEEE Press, ISBN-13: 978-0470138663, 2008.

- [2] Porat B.: A Course in Digital Signal Processing', John Wiley & Sons, 1997.

- [3] Norris D.: Programming with Stm32 Getting Started with the Nucleo, McGraw-Hill Education, ISBN: 978-1-26-003132-4, 2018

Thesis Supervisors: Ing. Miroslav Holada, Ph.D.

Institute of Information Technology and Electronics

Date of Thesis Assignment: January 26, 2023 Date of Thesis Submission: May 15, 2024

L.S.

prof. Ing. Zdeněk Plíva, Ph.D. Dean

doc. Dr. Ing. Jaroslav Hlava study programme guarantor

Liberec January 26, 2023

### **Declaration**

I hereby certify, I, myself, have written my master thesis as an original and primary work using the literature listed below and consulting it with my thesis supervisor and my thesis counsellor.

I acknowledge that my master thesis is fully governed by Act No. 121/2000 Coll., the Copyright Act, in particular Article 60 – School Work.

I acknowledge that the Technical University of Liberec does not infringe my copyrights by using my master thesis for internal purposes of the Technical University of Liberec.

I am aware of my obligation to inform the Technical University of Liberec on having used or granted license to use the results of my master thesis; in such a case the Technical University of Liberec may require reimbursement of the costs incurred for creating the result up to their actual amount.

At the same time, I honestly declare that the text of the printed version of my master thesis is identical with the text of the electronic version uploaded into the IS/STAG.

I acknowledge that the Technical University of Liberec will make my master thesis public in accordance with paragraph 47b of Act No. 111/1998 Coll., on Higher Education Institutions and on Amendment to Other Acts (the Higher Education Act), as amended.

I am aware of the consequences which may under the Higher Education Act result from a breach of this declaration.

#### ACKNOWLEDGEMENT

I would like to express my sincere gratitude and appreciation to the individuals and institutions who have played a significant role in completing my thesis. Their support and contributions have been invaluable throughout this journey.

I am grateful to the numerous authors, researchers, and scholars whose work I have referenced and consulted as part of my literature review. Their contributions have provided valuable insights and knowledge that have shaped the foundation of my thesis. I express my sincere appreciation to these individuals and the sources they have published.

Furthermore, I would like to thank **TUL** – **Technical University of Liberec, specifically the Faculty of Mechatronics, Informatics, and Interdisciplinary Studies Informatics**. I am grateful to the respected Dean, the Head of the Department, and all the staff for providing the necessary resources and knowledge. The academic environment and the learning opportunities everyone offers have been instrumental in my growth and development as a student.

I want to extend my heartfelt thanks to my parents, Recep Küçükalp and İlknur Küçükalp, for their unwavering love and encouragement. I also extend my gratitude to my sister, Elif Küçükalp, my grandmother, Nermin Yılmaz, and my friend, Ing. Elçin Tören, for their constant support and motivation. Their belief in my abilities has been the driving force behind my accomplishments.

Last but certainly not least, I am deeply indebted to my guiding professor and thesis supervisor, **Ing. Miroslav Holada, Ph.D.**, for their unwavering support, continuous guidance, and invaluable mentorship throughout my thesis journey. Their expertise, patience, and constant encouragement have been pivotal in shaping the outcome of my research. I am truly grateful to all the individuals and institutions mentioned above who have significantly completed my thesis. Their contributions, whether big or small, have impacted my academic and personal growth.

#### **ABSTRACT**

This thesis details the design and implementation of firmware tailored for the STM32F7 series microcontroller, focusing on efficiently processing digital signals acquired from an ADC (Analog-to-Digital Converter). The firmware's primary objective is to process these signals in real-time, either outputting them to a DA converter or transmitting them to a higher-level system via various communication methods, including USB (Universal Serial Bus) CDC (Communications Device Class) Virtual COM port. This work includes the development of digital filtering techniques using FIR (Finite Impulse Response) and IIR (Infinite Impulse Response) filters, execution of FFT (Fast Fourier Transform) for spectrum analysis, and implementation of simple recognition algorithms such as DTMF (Dual-Tone Multi-Frequency) detection.

A MATLAB-based graphical user interface is also developed to interact seamlessly with the STM32 microcontroller via a USB CDC Virtual COM port, enabling real-time configuration and visualization of signal processing parameters and results. The firmware architecture supports comprehensive testing and performance analysis, providing insights into the microcontroller's operational limits, efficiency, and scalability in handling real-world signal processing tasks. These analyses demonstrate the capability of the STM32F7 microcontroller to meet the demands of embedded DSP applications.

**Keywords**: Embedded DSP Firmware, STM32F7 Microcontroller, Real-Time Signal Processing, USB CDC Virtual COM port.

#### **ABSTRAKT**

Tato diplomová práce popisuje návrh a implementaci firmwaru přizpůsobeného pro mikrokontroléry řady STM32F7, se zaměřením na efektivní zpracování digitálních signálů získaných z ADC (převodníku analogového signálu na digitální). Hlavním cílem firmwaru je zpracování těchto signálů v reálném čase, buď jejich výstupem na DA převodník nebo jejich přenosem do vyššího systému prostřednictvím různých komunikačních metod, včetně USB (Univerzální Sériové Magistrály) CDC (Třída Zařízení Komunikace) Virtuálního COM portu. Tato práce zahrnuje vývoj technik digitálního filtrování pomocí FIR (konečné impulzní odezvy) a IIR (nekonečné impulzní odezvy) filtrů, provádění FFT (rychlé Fourierovy transformace) pro analýzu spektra a implementaci jednoduchých algoritmů rozpoznávání, jako je detekce DTMF (dvoutónové vícefrekvenční).

Také bylo vyvinuto grafické uživatelské rozhraní založené na MATLABu pro bezproblémovou interakci s mikrokontrolérem STM32 prostřednictvím USB CDC virtuálního COM portu, které umožňuje konfiguraci a vizualizaci parametrů zpracování signálu v reálném čase a výsledků. Architektura firmwaru podporuje komplexní testování a analýzu výkonu, která poskytuje přehled o operačních limitech, efektivitě a škálovatelnosti mikrokontroléru při zvládání úkolů zpracování signálů v reálném světě. Tyto analýzy demonstrují schopnost mikrokontroléru STM32F7 splnit požadavky vestavěných DSP aplikací.

**Klíčová slova:** Firmware vestavěného DSP, Mikrokontrolér STM32F7, Zpracování signálů v reálném čase, USB CDC virtuální COM port.

## LIST OF CONTENTS

| 1. | OBJECTIVE                                                             | 1  |

|----|-----------------------------------------------------------------------|----|

|    | 1.1 Motivation And Scope                                              | 1  |

|    | 1.1.1 Motivation                                                      | 1  |

|    | 1.1.2 Scope                                                           | 2  |

| 2. | LITERATURE REVIEW                                                     | 4  |

| 3. | THEORETICAL BACKGROUND                                                | 5  |

|    | 3.1. Overview of STM32F7 Series Microcontroller                       |    |

|    | 3.2. Principles of Analog to Digital Conversion (ADC)                 |    |

|    | 3.3. Digital Filtering Techniques: FIR                                |    |

|    | 3.3.1. STM32 Implementation of FIR Filters                            | 10 |

|    | 3.4. Digital Filtering Techniques: IIR                                | 12 |

|    | 3.4.1. STM32 Implementation of IIR Filters                            | 13 |

|    | 3.5 Fast Fourier Transform (FFT) in Signal Analysis                   | 14 |

|    | 3.5.1. STM32 Implementation of FFT                                    |    |

|    | 3.6. Real-Time Processing of DTMF Signals                             | 18 |

|    | 3.6.1. STM32 Implementation of DTMF                                   |    |

| _  | NETWOOD OF OCK AND CHEET AND ENGINE ATTOM                             |    |

| 4. | METHODOLOGY AND SYSTEM IMPLEMENTATION                                 |    |

|    | 4.1. System Architecture and Design                                   |    |

|    | 4.3. Hardware Setup and Firmware Integration                          |    |

|    | 4.4. System Interface and Data Analysis                               |    |

|    | 4.4.1. Serial Communication Protocol and Data Format                  |    |

|    | 4.4.2. MATLAB Data Handling and Real-Time Analysis                    | 32 |

|    | 4.4.3. Visualization and Performance Metrics                          | 32 |

|    | 4.4.2. Data Visualization and Analysis                                | 33 |

| 5  | RESULTS AND DISCUSSION                                                | 37 |

| ٠. | 5.1. Performance of Digital Filters                                   |    |

|    | 5.1.1. Efficacy of Infinite Impulse Response (FIR) Filters            |    |

|    | 5.1.2. Efficacy of Infinite Impulse Response (IIR) Filters            |    |

|    | 5.2 Efficacy of FFT Analysis                                          | 43 |

|    | 5.3 Real-Time DTMF Algorithm Performance                              | 45 |

|    | 5.4. Performance Analysis of DSP Algorithms on STM32 Microcontrollers |    |

|    | 5.4.1. Detailed Metrics and Comparisons                               | 49 |

|    | 5.4.2. Discussion on Cycle Counts and Execution Times                 | 52 |

| 6  | REFERENCES                                                            | 53 |

|    |                                                                       |    |

## LIST OF FIGURES

| Figure 1. NUCLEO-144 Board with STM32 Microcontroller and interface connectors.[2]       | .5 |

|------------------------------------------------------------------------------------------|----|

| Figure 2. PMOD Audio Module [6]                                                          | .7 |

| Figure 3. Schematic of Audio Signal Processing Circuit with ADC and DAC [10]             | .8 |

| Figure 4. Fast Fourier Transform (FFT) Computational Graph.[18]                          | 15 |

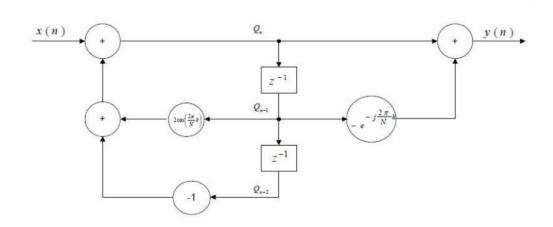

| Figure 5. Block Diagram of the Goertzel Algorithm [21]                                   | 19 |

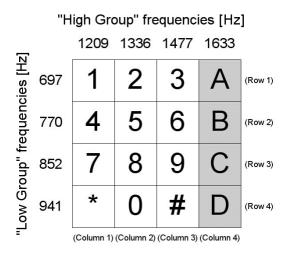

| Figure 6. DTMF Frequency Table for Keypad Tones.[23]                                     | 20 |

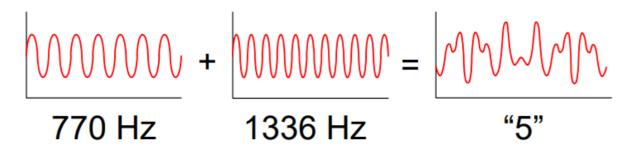

| Figure 7. Generation of the DTMF Tone for the Digit "5" Using 770 Hz and 1336 H          | Ηz |

| Frequencies.[18]                                                                         | 21 |

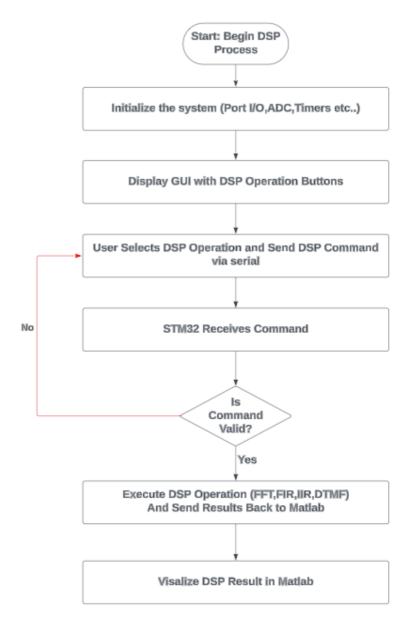

| Figure 8. Workflow diagram of Matlab and STM32 DSP Operations                            | 24 |

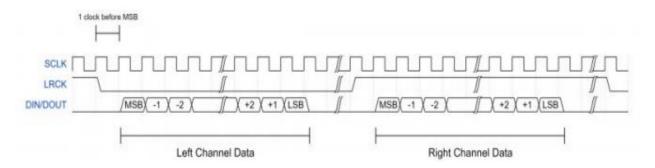

| Figure 9. I2S Data Transmission Format Showing Left and Right Channel Bit Alignment.[14] | 25 |

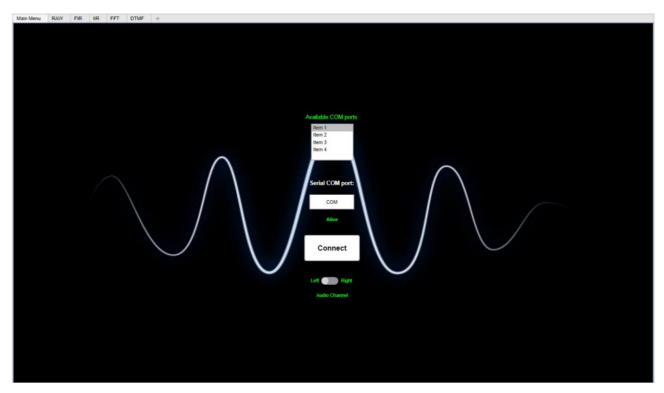

| Figure 10. Graphical User Interface for DSP Application with Serial COM Port Connection  | 26 |

| Figure 11. Graphical User Interface for DSP Application                                  | 27 |

| Figure 12. SAI Configuration on STM                                                      | 29 |

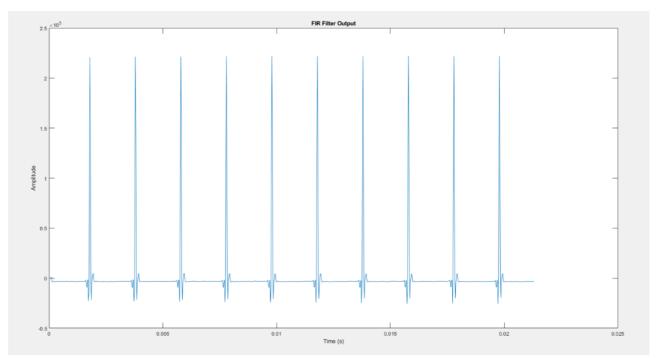

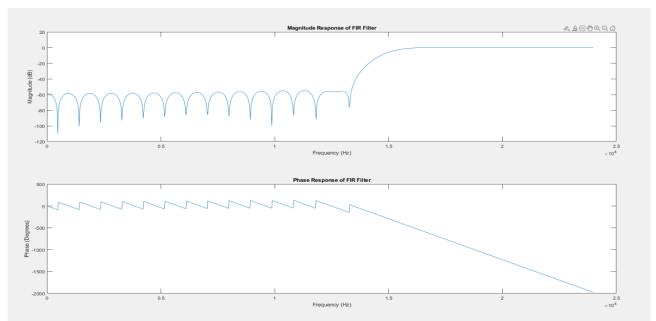

| Figure 13.FIR Filter Output Graph                                                        | 39 |

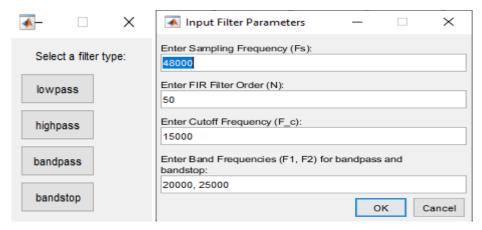

| Figure 14. Filter Design Application                                                     | 40 |

| Figure 15.Magnitude And Phase Response of FIR Filter                                     | 40 |

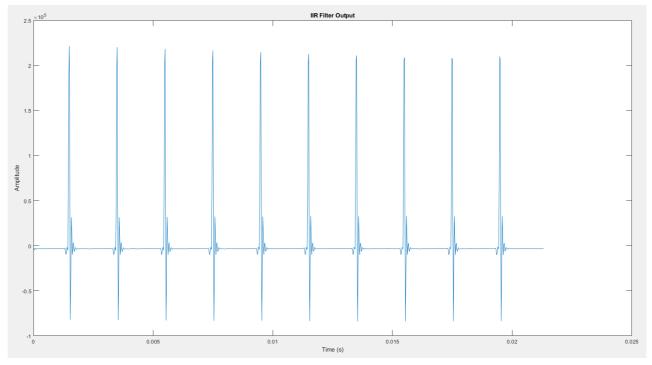

| Figure 16.IIR Filter Output Graph                                                        | 41 |

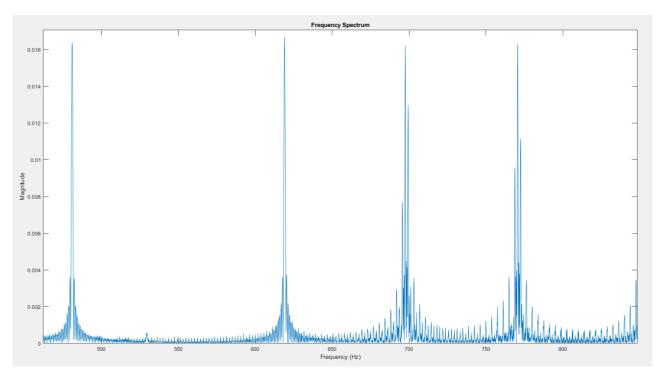

| Figure 17.FFT Magnitude Spectrum Graph                                                   | 44 |

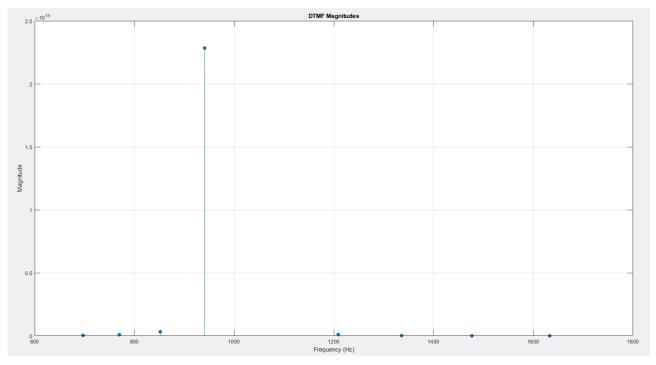

| Figure 18. DTMF Magnitudes Graph                                                         | 45 |

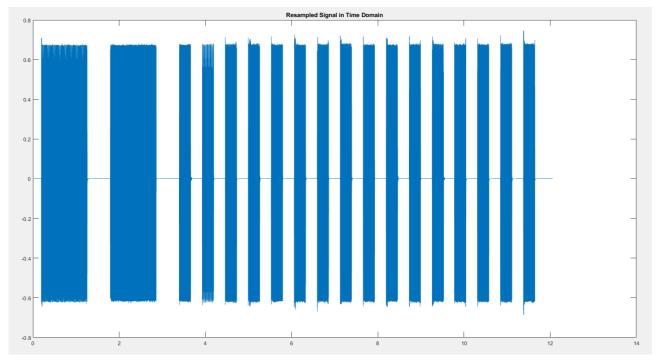

| Figure 19. Time Domain Representation of a Resampled Digital Signal                      | 46 |

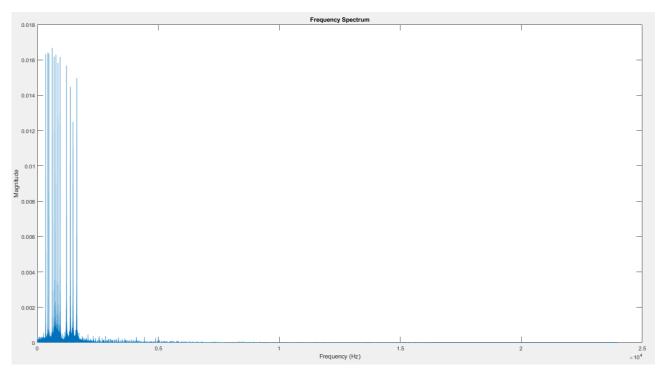

| Figure 20. Frequency Spectrum                                                            | 47 |

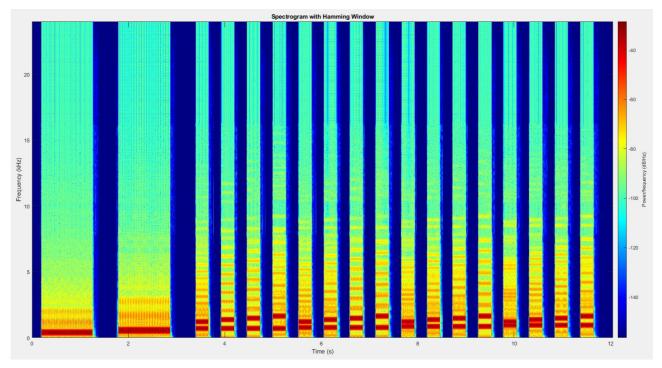

| Figure 21. Spectrogram with Hamming Window                                               | 47 |

## LIST OF TABLES

| Table 1. Comparison of Computational Complexity between DFT and FFT for I | Different Sample |

|---------------------------------------------------------------------------|------------------|

| Sizes [16]                                                                | 14               |

| Table 2. DTMF Tone Coefficients [22]                                      | 20               |

| Table 3. FFT Performance Analysis                                         | 50               |

## LIST OF SOURCE CODES

| Source Code 1. STM FIR Filter Processing by CIMSIS-Library (Courtesy: STM script)     | 11    |

|---------------------------------------------------------------------------------------|-------|

| Source Code 2. arm_fir_f32 function by CIMSIS-Library (Courtesy: STM script)          | 11    |

| Source Code 3. STM IIR Filter Processing by CIMSIS-Library (Courtesy: STM script)     | 13    |

| Source Code 4. STM FFT Processing by CIMSIS-Library (Courtesy: STM script)            | 16    |

| Source Code 5. STM DTMF Processing by CIMSIS-Library (Courtesy: STM script)           | 23    |

| Source Code 6. STM Data transmit function from STM to Matlab (Courtesy: STM script)   | 34    |

| Source Code 7. Matlab Data receive callback function from STM to Matlab (Courtesy: MA | ATLAB |

| script)                                                                               | 34    |

| Source Code 8. Matlab Read Data function (Courtesy: MATLAB script)                    | 35    |

#### 1. OBJECTIVE

This thesis is dedicated to designing and developing advanced firmware for real-time digital signal processing (DSP) using the STM32F767ZI microcontroller, known for its robust digital signal computation capabilities. The core goal is to engineer firmware that efficiently processes signals from an Analog to Digital Converter (ADC), transforming them into formats that can be transmitted to higher-level systems. This involves implementing sophisticated digital filtering techniques, including Finite Impulse Response (FIR) and Infinite Impulse Response (IIR) filters, and exploring the integration of simple recognition algorithms such as DTFM (Dual-Tone Multi-Frequency) detection.

A critical component of this project is to establish an interactive interface between the STM32 microcontroller and a personal computer, utilizing MATLAB. This interface will leverage the USB CDC (Communications Device Class) Virtual COM port to provide user-friendly access for configuring DSP parameters, enhancing the system's adaptability and responsiveness to diverse operational conditions.

Comprehensive testing and evaluation of the firmware are essential for this research, mainly focusing on the STM32F767ZI microcontroller's configuration limits. This phase aims to optimize the firmware according to the microcontroller's specifications and assess performance under these constraints. This evaluation is crucial for providing insights into the system's efficacy in real-time applications.

The foundational STM code, central to this thesis, manages UART (Universal Asynchronous Receiver/Transmitter), interrupts, and processes MATLAB commands, which are vital for developing the firmware. It covers essential aspects of digital signal processing, such as digital filtering, gain control, and interactions with the SAI (Serial Audio Interface) for audio data management. Interaction with the SAI (Serial Audio Interface) for audio data management.

#### 1.1 Motivation And Scope

#### 1.1.1 Motivation

In an era of rapid technological advancements, DSP emerges as a pivotal field, influencing various sectors such as communications, control systems, multimedia, and consumer electronics. The essence of DSP lies in its ability to manipulate vast streams of real-time data, highlighting the need for robust and efficient microcontrollers. The STM32F7 series stands out among various options due to its formidable processing capabilities and specialized support for DSP operations.

This research is driven by the transformative impact of DSP in practical scenarios and the untapped potential of the STM32F767ZI microcontroller series. The primary aim is to exploit the full capabilities of this microcontroller in DSP applications. The envisioned outcome is a comprehensive firmware that processes digital signals in real-time and seamlessly relays processed data to more complex systems, enhancing functionality and performance.

The implications of this research extend beyond its immediate Scope, offering benefits to various groups:

- 1. **Researchers**: As a platform for testing theoretical DSP concepts or as a foundation for developing more advanced systems.

- 2. **Audio Engineers**: Providing valuable tools for sound manipulation and analysis, which are crucial in music production, broadcast engineering, and acoustics.

- 3. **Software Developers**: Facilitating the incorporation of DSP methodologies into diverse software applications.

- 4. **Educators in Related Fields**: Assisting instructors in illustrating key computational concepts through practical DSP applications.

Additionally, as envisioned by my supervisor, this program's application in an educational setting underscores its importance. It introduces an innovative teaching methodology where students can engage with DSP systems in real-time, effectively bridging the gap between theoretical understanding and practical application. This hands-on experience is invaluable for students and educators, enhancing comprehension of DSP and its relevance in various technological domains. This thesis transcends the boundaries of a mere academic endeavor. It is a gateway to innovation, education, and practical implementation in numerous fields. The development of this firmware and its accompanying tools are set to contribute significantly to DSP and microcontroller technology, paving new paths for research, development, and education.

#### **1.1.2 Scope**

The Scope of this thesis encompasses developing and implementing a real-time digital signal processing (DSP) system using the STM32F767ZI microcontroller series. This endeavor aims to explore and demonstrate the capabilities of this microcontroller in processing complex DSP tasks. The focus areas and objectives of this research are outlined as follows:

- 1. **Understanding the STM32F767ZI Microcontroller**: The initial phase involves an in-depth study of the STM32F767ZI microcontroller. This includes examining its architecture, processing capabilities, and specific features that support DSP operations. A comprehensive understanding of the hardware is crucial for optimizing the firmware design and implementation.

- 2. **Designing and Implementing DSP Firmware**: This research aims to design firmware capable of real-time processing digital signals from an Analog-to-Digital Converter (ADC). The firmware will also be able to transmit the processed data to a Digital-to-Analog Converter (DA) or a higher-level system through a communication interface. This includes implementing functionalities like digital filtering (using FIR and IIR filters), spectrum analysis, and basic signal recognition algorithms like dual-ton multi-frequency (DTMF) detection.

- 3. **Developing a MATLAB Interface**: A significant part of this project involves creating a MATLAB application to serve as a graphical user interface. This application will compute DSP algorithm parameters based on user specifications and facilitate the communication of these parameters to the STM32 board via a USB interface. Additionally, it will display data resulting from the DSP operations performed by the firmware.

- 4. **Performance Analysis and Optimization**: Testing the developed firmware's performance limits is integral to this research. This includes determining the maximum achievable sampling and data processing speeds and ensuring that the firmware leverages the full potential of the STM32 microcontroller's processing capabilities.

- 5. **Real-world Applications and Educational Use**: Identifying potential real-world applications for the developed system is crucial. Additionally, the project aims to demonstrate how this system can be utilized in an educational context, providing a practical tool for teaching DSP concepts.

This thesis, therefore, not only focuses on the technical aspects of DSP implementation but also considers its practical applications and educational value. The project is designed to contribute to the microcontroller-based DSP field and the broader technological education and application context.

#### 2. LITERATURE REVIEW

As I embark on my thesis journey, a foundational step is the comprehensive review of existing literature and references. This process is crucial in shaping the research trajectory, providing validation and insight into the complexities of Digital Signal Processing (DSP) with a focus on MATLAB applications and STM32 microcontrollers. The subsequent literature review addresses pivotal questions and challenges inherent in the field, offering a structured approach to the research objectives.

#### Key Questions and Challenges:

- **DSP Algorithm Implementation:** What are the optimal algorithms for effective DSP, and how can they be efficiently implemented using MATLAB and STM32 microcontrollers?

- MATLAB's Integration in DSP: How does MATLAB facilitate DSP applications, particularly in algorithm development and data analysis?

- **Utilization of STM32 Microcontrollers:** What role do STM32 microcontrollers play in DSP, and what are their capabilities and limitations?

- **Real-Time Processing Challenges:** How can real-time signal processing be achieved, and what are its associated challenges?

- **Hardware and Software Synchronization:** How can the synchronization between hardware (STM32) and software (MATLAB) effectively manage for optimal DSP performance?

#### 3. THEORETICAL BACKGROUND

#### 3.1. Overview of STM32F7 Series Microcontroller

The STM32F7 series represents a robust family of microcontrollers developed by STMicroelectronics, a leader in the semiconductor industry. This series, distinguished by its high-performance ARM Cortex-M7 cores, offers an unparalleled balance of efficiency and power. Engineered to meet the demanding requirements of sophisticated digital signal processing (DSP) applications, the STM32F7 series is an exemplary choice for a wide range of embedded systems [1].

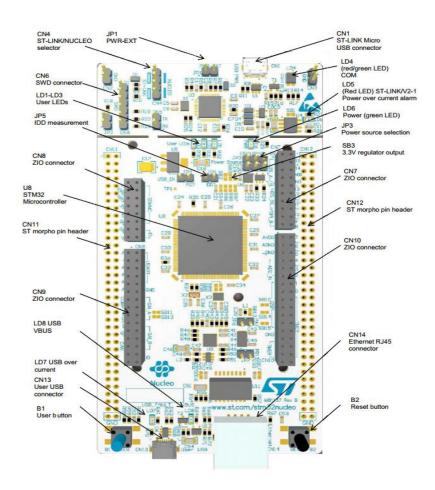

Figure 1. NUCLEO-144 Board with STM32 Microcontroller and interface connectors.[2]

**Key Features and Architecture:** The STM32F7 series is renowned for its ARM Cortex-M7 processor, which operates at speeds up to 216 MHz. This core is notable for its high-performance and low-power operation, enabled by its advanced architecture and adaptive real-time ART Accelerator<sup>TM</sup> [3]. The Cortex-M7 core features a floating-point unit (FPU), enhancing the microcontroller's capability to handle complex mathematical operations and DSP tasks, as depicted in Figure 1. [2].

**Memory and Storage:** The STM32F7 series has up to 2 MB of flash memory and 512 KB of SRAM, facilitating extensive code storage and high-speed data processing. This series also supports external memory interfaces, which enhances system design flexibility and scalability [4].

Connectivity and I/O Interfaces: The STM32F7 series excels in connectivity, incorporating diverse communication interfaces such as UART/USART, SPI, I2C, CAN, and USB OTG with full-speed and high-speed capabilities. The series is also well-equipped with extensive I/O ports and peripherals, including ADCs, DACs, timers, and GPIOs, addressing the varied needs of applications across different domains [4].

**Energy Efficiency and Power Management:** Energy efficiency is paramount in the STM32F7 series, featuring multiple power-saving modes, including Sleep, Stop, and Standby. These modes are designed to optimize power consumption without compromising system responsiveness, which is crucial for applications requiring prolonged operational periods [4].

**Development and Tool Support:** STMicroelectronics provides comprehensive development support for the STM32F7 series through tools like the STM32Cube software ecosystem. This includes the Hardware Abstraction Layer (HAL) libraries, middleware components, and numerous software examples. For this thesis, the STM32Cube's DSP library, optimized explicitly for the STM32F7 series, plays a vital role in enhancing the efficiency of digital signal processing. This library facilitates seamless integration from initial development stages to final deployment, offering a collection of optimized DSP functions and algorithms. These resources prove indispensable in streamlining the development of DSP applications, demonstrating practical effectiveness in DSP tasks [4].

#### 3.2. Principles of Analog to Digital Conversion (ADC)

In digital signal processing, particularly in systems that integrate STM32 microcontrollers with peripheral modules like PMOD I2S2, the Analog Digital Conversion (ADC) process plays a pivotal role. This process involves converting analog signals, such as audio inputs, into their digital counterparts, effectively bridging the gap between analog and digital realms. The STM32F7 series demonstrates proficiency in handling this conversion, utilizing the I2S interface to ensure a high-quality data transfer from analog to digital format [5].

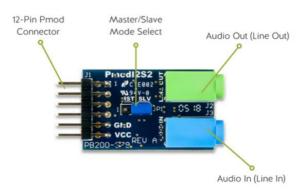

The ADC process within this system involves a well-coordinated interaction between the STM32F767 microcontroller and the PMOD module. The PMOD I2S2, featuring the Cirrus CS5343

AD and CS4344 DA converters, is critical in this context (Figure 2) [6] Audio signals are captured by the microcontroller through the I2S RX line and undergo digital processing. They are then output via the I2S TX line, thus completing their journey from the analog to the digital domain and back [7].

Figure 2. PMOD Audio Module [6]

A critical aspect of this process is understanding the electrical characteristics of the AD and DA converters. Recognizing their different full-scale voltage ranges is essential, as this affects the amplitude of the output signal relative to the input, particularly in a passthrough configuration. This gain, a byproduct of the voltage range differences, is quantified through precise calculations, highlighting the intricate nature of signal conversion in this system [8].

The ADC's capability to accurately capture input voltages, considering elements like voltage dividers on the PMOD board, is validated through comprehensive testing. These tests ensure adherence to datasheet specifications, confirming that the ADC avoids exceeding its clipping threshold and maintains signal integrity within its 24-bit dynamic range. MATLAB visualizations further support these tests, offering a graphical representation of the signal's amplitude range and showcasing the ADC's precision [9].

The full-scale analog voltage range of the AD and DA converters on the PMOD board differs, affecting the output amplitude in a passthrough configuration. The CS5343 AD converter has a full-scale input peak-to-peak range of 0.568 times Vcc, while the CS4344 DA converter has an output peak-to-peak range of 0.65 times Vcc. This variance results in a conversion gain. For instance, an AD converter sampling at 0.5Vcc will produce a digital value of approximately 4922289 ((0.5\*(30.568))\*(2^24-1)). When passed through the DA converter, this value is converted back into an analog signal, completing the digital-to-analog signal conversion cycle and illustrating the amplitude difference due to the converters' varying voltage ranges.

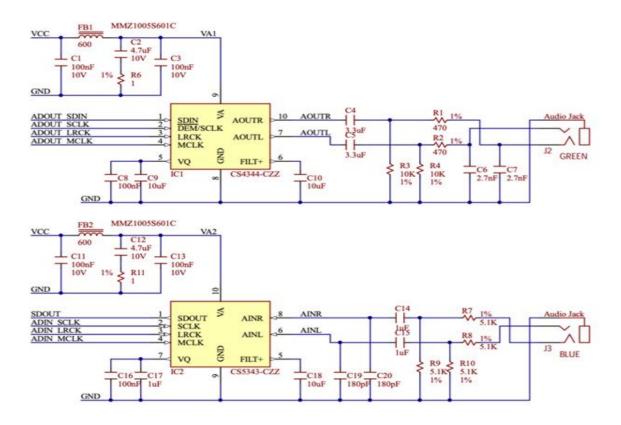

Figure 3. Schematic of Audio Signal Processing Circuit with ADC and DAC [10]

The schematic provided (Figure 3) [10] delineates the CS5343 analog-to-digital converter (ADC) interface connected to an STM32 microcontroller, a crucial component in the digital signal processing chain explored in this thesis. This ADC is instrumental in transducing the analog audio input from the blue jack into a digital representation, employing an I2S interface for high-fidelity data transfer. The schematic incorporates passive components that condition the audio signal, ensuring a clean, noise-free conversion. The precision of this ADC, with its 24-bit resolution, is central to capturing the nuanced acoustic information necessary for high-quality audio processing tasks performed by the STM32. Considering the voltage divider on the PMOD board, the A/D converter perceives the input voltage as halved. Tests with a precise 3.3V supply from the Analog Discovery 2 USB multitool showed that a 2V amplitude input signal (4V peak-to-peak) is the maximum before clipping occurs in the A/D converter. These findings align with the datasheet specifications for the A/D converter's full-scale input range, confirming the system's ability to handle input signals up to 2V in amplitude without clipping. MATLAB plots of passthrough sample data for unclipped and clipped signals reveal the effective utilization of the 24-bit sample range, further substantiating the system's adeptness in ADC [6,10].

#### 3.3. Digital Filtering Techniques: FIR

In digital signal processing (DSP), Finite Impulse Response (FIR) filters are highly regarded for their stability and linear phase characteristics. Unlike Infinite Impulse Response (IIR) filters, FIR filters rely solely on present and past inputs, devoid of feedback mechanisms. This section delves into implementing FIR filters within DSP frameworks, focusing on STM32F7 series microcontrollers.

FIR filters are pivotal in DSP for isolating specific frequency bands and mitigating noise from signals. Their digital nature allows for greater flexibility and configurability compared to analog filters, facilitating adjustments in filter characteristics without needing physical component changes.

The shift towards digital filters, such as FIR, significantly reduces reliance on external hardware components like resistors and capacitors, cutting manufacturing costs and boosting reliability. Unaffected by environmental changes that impact analog filters, digital filters offer consistent performance, making them a more stable and reliable choice for signal processing tasks.

The digital filter equations are based on the following essential transfer function shown in the z domain [11]:

$$Y(z) = H(z)X(z), \tag{1}$$

Where Y(z) is the filter output, X(z) is the filter input, and H(z) is the transfer function of the filter. H(z) can be expanded as follows [11]:

$$Y(z) = \frac{b(1) + b(2)z^{1} + \dots + b(n+1)z^{n}}{a(1) + a(2)z^{-1} + \dots + a(n+1)z^{-n}} X(z)$$

(2)

A and b are coefficient sets, and z is a delay element. Differing fundamentally from its counterparts with feedback mechanisms, the Finite Impulse Response (FIR) filter operates without relying on feedback. This aspect can be understood by examining its transfer function, which, at its core, is derived similarly to other filters. A notable distinction in the FIR filter's formulation is the simplification of its coefficients, particularly with the 'a' coefficient being singular and assigned a value of one (a(1) = 1). This simplification is evident when the output equation, y(t), is formulated in the context of an FIR filter [11]:

$$y(t) = (z) = \frac{b(1)x(k) + b(2)x(k-1) + \dots + b(n+1)x(k-n)}{a(1)}$$

(3)

For the FIR algorithm, the current output is generated based only on the current and previous inputs. In effect, an FIR is a weighted sum operation. FIR filters have several advantages and drawbacks. One of the main advantages is that FIR filters are inherently stable. This characteristic makes

designing FIR filters easier than designing IIR filters. In addition, FIR filters can provide linear phase response, which may be necessary for some applications. Another essential advantage of FIR filters is that they are more resistant to quantization noise in their coefficients. Replacing a(1)=1 and C for the b constants, the equation for the FIR filter is as follows [11]:

$$y(n) = C0x(n) + C1x(n-1) + C2x(n-2) + C3x(n-3) + ...,$$

(4)

Y (n) is the most recent filter output, and x(n) is the most recent filter input. The filter does rely on previous inputs, as shown by the terms x(n-1), x(n-2), etc. The Cx constants determine the filter response and can be derived using many different algorithms, yielding different characteristics. The first input, x(1), is multiplied by C0. The output y(1) is as follows [11]:

$$y(1) = C0x(1)$$

(5)

The x(1) input is saved for the next pass through the FIR algorithm. The second input, x(2), is multiplied by C0, and the previous input, x(1), is multiplied by C1. The output y(2) is as follows [11]:

$$y(2) = C0x(2) + C1x(1)$$

(6)

x(1) The and x(2) inputs are saved for the following input, x(3), and so on. The order of an FIR filter is equal to one less than the number of constants and indicates the degree of complexity and the number of input samples that need to be stored. The higher the order, the better the characteristics of the filter (sharper curve and flatter response in the non-attenuation region) [11,12].

#### 3.3.1. STM32 Implementation of FIR Filters

A pivotal component of implementing Finite Impulse Response (FIR) filters in digital signal processing (DSP) within the STM32 microcontroller environment is the arm\_fir\_f32 function. This function, integral to the CMSIS (Cortex Microcontroller Software Interface Standard) DSP library, is specifically tailored for the ARM Cortex-M processor series. This section delineates the role and functionality of the arm\_fir\_f32 function as it is applied in the FIR filter implementation on an STM32F7 series microcontroller [13].

void PerformFIR() {

static float32 t firOutput[BLOCK SIZE];

```

float32_t *inputSignal;

inputSignal = (selectedChannel == 0) ? sample_L : sample_R; // Channel selection

arm_fir_f32(&S_FIR, inputSignal, firOutput, BLOCK_SIZE);

SendData2MTLB(ID_FIR, (uint8_t*)firOutput, BLOCK_SIZE);

}

```

Source Code 1. STM FIR Filter Processing by CIMSIS-Library

The arm\_fir\_f32 function is a processing function for the floating-point FIR filter. It is designed to apply an FIR filter to an input data block and produce a corresponding output data block. The function signature is as follows:

```

void arm_fir_f32(const arm_fir_instance_f32 *S,

const float32_t *pSrc,

float32_t *pDst,

uint32_t blockSize);

Source Code 2. arm_fir_f32 function by CIMSIS-Library

```

#### Parameters and Functionality[13]:

- **S**: This parameter points to an instance of the floating-point FIR filter structure. This structure contains information about the filter's order, coefficients, and state buffer.

- **pSrc**: This represents the pointer to the block of input data. In a typical DSP application, this could be a segment of a signal, such as an audio waveform or sensor data, that needs to be processed.

- **pDst**: This is the pointer to the block of output data. It stores the filtered signal after the application of the FIR filter.

- **blockSize**: This parameter specifies the number of samples to process. It determines the size of the input and output data blocks.

The firOutput is an array where the filtered signal will be stored and input-signal points to the current input data. The function applies the FIR filter defined by S\_FIR to the input signal and stores the result in firOutput. In the provided source code, firOutput is an array storing the filtered signal. The input-signal variable points to the current input data, and the function applies the FIR filter defined by S\_FIR to this input, storing the result in firOutput.

The arm\_fir\_f32 function is indispensable for DSP applications that demand fast and efficient

signal processing. Its capability to handle floating-point operations renders it particularly suitable for precision-critical applications, such as audio signal processing and other real-time DSP tasks. The use of floating-point arithmetic ensures a broad dynamic range and mitigates common issues associated with fixed-point processing, like quantization errors and overflow, thereby enhancing the fidelity and reliability of the DSP applications.

#### 3.4. Digital Filtering Techniques: IIR

The IIR topology extends directly from this equation by moving the denominator of the expanded H(z) to the left side of the equation [14,15]:

$$(a(1)+a(2)z-1+...+a(n+1)z-n)Y(z) = (b(1)+b(2)z-1+...+b(n+1)z-n)X(z)$$

(7)

In the time domain, this equation appears as follows [14,15]:

$$a(1)y(k) + a(2)y(k-1) + \dots + a(n+1)y(k-n) = b(1)x(k) + b(2)x(k-1) + \dots + b(n+1)x(k-n)$$

(8)

where y(k) represents the current filter output, x(k) represents the current input, y(k-1) represents the previous output, x(k-1) represents the previous input, and so on. If this equation is solved for y(k) [14,15]:

$$y(k) = \frac{b(1)x(k) + b(2)x(k-1) + ... + b(n+1)x(k-n) - a(2)y(k-1) - ... - a(n+1)y(k-n)}{a(1)}$$

(9)

This equation shows that the IIR filter is a feedback system that generates the current output based on the current and previous inputs and outputs. The IIR structure has unique advantages and drawbacks. The main advantage of the IIR structure is that it provides a frequency response comparable to an FIR filter of a higher order. This results in fewer calculations necessary to implement the filter. IIR filters can suffer from instability because they rely on feedback. As a result, they are more challenging to design, and special care must be taken to prevent an unstable system. IIR filters may also have a non-linear phase response, making them inappropriate for some applications where a linear phase is necessary. Finally, because they rely on past outputs, they tend to be more sensitive to quantization noise, making them difficult to implement with 16-bit fixed point hardware. Generally, 32-bit hardware is necessary for an IIR filter implementation. Digital IIR filters reduce dependence on external components like resistors and capacitors, lowering production costs and enhancing reliability. Unlike analog filters, whose performance might be impacted by environmental changes, digital IIR filters maintain consistent functionality due to their algorithmic basis. IIR filters are integral in DSP due to their recursive nature, which employs current and past inputs and outputs. This characteristic enables IIR filters to replicate the behavior of analog filters

efficiently while retaining the advantages of digital processing. They are precious in scenarios where filter stability and computational efficiency are paramount [15].

#### 3.4.1. STM32 Implementation of IIR Filters

In the STM32 platform, the implementation of IIR filters involves initializing and processing the filter structure and parameters through dedicated CMSIS library functions. The following conceptual overview provides insight into how IIR filters can be integrated into STM32 applications:

**Initialization of the Filter Structure**: This step involves setting up the IIR filter's parameters, including the order, coefficients, and state buffer. The initialization ensures the filter is correctly configured to process the incoming signal according to the desired specifications.

**Processing the Input Signal**: Once the filter is initialized, the input signal is processed through the filter. This process involves manipulating the input data based on the filter's characteristics, producing an output that reflects the desired frequency response.

**Handling the Filtered Output**: The IIR filter process output is typically used for further processing or analysis within the application. Depending on the application's specific requirements, this could include data visualization, transmission, or storage tasks.

The STM32 microcontroller environment utilizes functions like arm\_biquad\_cascade\_df1\_f32 for IIR filter implementation, part of the CMSIS DSP library designed for ARM Cortex-M processors. Here is a sample implementation of an IIR filter in STM32:

```

void PerformIIR() {

float32_t *inputSignal = (selectedChannel == 0) ? sample_L : sample_R;

float32_t iirOutput[BLOCK_SIZE];

arm_biquad_cascade_df1_init_f32(&S_IIR, IIR_ORDER, iirCoeffs, iirState);

arm_biquad_cascade_df1_f32(&S_IIR, inputSignal, iirOutput, BLOCK_SIZE);

SendData2MTLB(ID_IIR, (uint8_t*)iirOutput, BLOCK_SIZE);

}

Source Code 3. STM IIR Filter Processing by CIMSIS-Library

```

In this implementation, arm\_biquad\_cascade\_df1\_f32 processes the input signal using the IIR filter defined by S\_IIR and stores the result in iirOutput.

Functionality of arm\_biquad\_cascade\_df1\_f32

- S: This parameter refers to an instance of the floating-point IIR filter structure containing information about the filter's stages, coefficients, and state buffer.

- **pSrc**: Represents the pointer to the block of input data.

- **pDst**: Points to the output data block where the filtered signal is stored.

- **blockSize**: Specifies the number of samples to process per block.

The IIR filter's output is determined by its order and the coefficients defining its frequency response.

#### 3.5 Fast Fourier Transform (FFT) in Signal Analysis

The Fourier Transform, a fundamental concept in signal processing, interprets a signal in the continuous time domain to discern its frequency composition. In practical applications, especially those involving Analog-to-Digital Converters (ADC), signals exist discretely, necessitating the Discrete Fourier Transform (DFT). The Fast Fourier Transform (FFT), an algorithmic advancement, mirrors the DFT's functionality but achieves the results with greater computational efficiency.

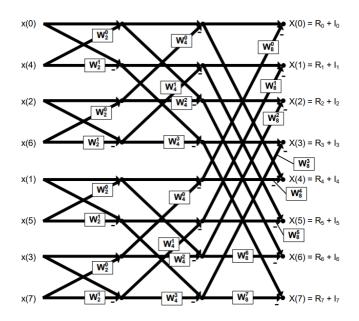

The operational essence of the FFT lies in its methodical breakdown of the input data array. It systematically halves the data, progressing recursively until it attains a pair-wise format. Commencing with these pairs, the FFT executes a 2-point transformation, employing these initial results to advance to a 4-point FFT. This process iterates, utilizing the outcomes of each step (2-point, 4-point, etc.) to progress to the subsequent 8-point FFT, continuing in this manner until the N-point FFT is accomplished [16]:

Contrasting the computational demands, the DFT typically requires  $N^2$  complex calculations to output N data points. The FFT, however, streamlines this process significantly, requiring only  $(N/2) \times \log_2(N)$  complex calculations. This optimized calculation requirement of the FFT becomes increasingly advantageous as the number of input points (N) escalates, solidifying its efficiency over the traditional DFT, particularly for large datasets [16]:

| N (number of input samples) | 8  | 256   | 1024    |

|-----------------------------|----|-------|---------|

| DFT (complex calculations)  | 64 | 65536 | 1048576 |

| FFT (complex calculations)  | 12 | 1024  | 5120    |

Table 1. Comparison of Computational Complexity between DFT and FFT for Different Sample Sizes [16]

The FFT allows for frequency analysis in a system and is an essential tool for any digital signal processing (DSP) system. Traditionally implemented on dedicated DSP hardware, FFT functionality is also available in DSP-enabled Microcontroller Units (MCUs). These advanced MCUs blend the specialized capabilities of DSPs with the adaptability of general-purpose programmable microcontrollers, allowing embedded systems to perform FFT operations efficiently. This integration provides a versatile platform for a wide range of applications, leveraging the power of FFT in more

flexible and integrated environments [16,17]:

Figure 4. Fast Fourier Transform (FFT) Computational Graph.[18]

In each phase of the FFT process, the count of complex data points remains consistent, illustrating the intensive computational nature of this algorithm. For instance, whether it is a 2-point stage or a 4-point stage, the algorithm handles 32 data points in each. This characteristic of the FFT underscores its computational intensity, particularly as the value of N, representing the number of data points, increases. Moreover, the precision of calculations in the initial stages of the FFT is crucial, as any inaccuracies or errors tend to amplify as the process progresses through subsequent stages. Therefore, ensuring high accuracy in the early calculations is paramount for the optimal performance of the FFT algorithm. This aspect highlights the need for meticulous implementation and execution of the FFT, especially in applications involving large datasets [18]:

#### 3.5.1. STM32 Implementation of FFT

In the digital signal processing domain (DSP) within the STM32 microcontroller framework, the Fast Fourier Transform (FFT) is pivotal in analyzing signal frequency components. Implementing FFT on STM32 microcontrollers, mainly using the CMSIS DSP software library, exemplifies leveraging advanced computational techniques in embedded systems. The following provides an insight into how FFT is implemented in the STM32 environment, as demonstrated by the specific code utilized in the application.

```

void PerformFFT() {

// Create the Hamming window

```

```

float32_t window[FFT_LENGTH];

createHammingWindow(window, FFT_LENGTH);

// Apply the window to the input signal

float32_t windowedSignal[FFT_LENGTH];

float32_t *input signal;

// Determine the input signal to process based on the selected channel

if (selectedChannel == 0) {

inputSignal = sample_L; // Left channel

} else {

inputSignal = sample_R; // Right channel

}

// Windowing the signal to be processed

for(int i = 0; i < FFT\_LENGTH; i++) {

windowedSignal[i] = (float32_t)inputSignal[i] * window[i];

// Initialize the FFT instance

arm_rfft_fast_init_f32(&S, FFT_LENGTH);

// Perform the FFT operation on the windowed signal

arm_rfft_fast_f32(&S, windowedSignal, fftOutput, 0);

// Calculate the magnitude of the FFT

arm_cmplx_mag_f32(fftOutput, fftMagnitude, FFT_LENGTH / 2);

// Send the FFT magnitude data back to MATLAB

SendData2MTLB(ID_FFT, (uint8_t*)fftMagnitude, FFT_LENGTH / 2);

}

```

Source Code 4. STM FFT Processing by CIMSIS-Library

Code Breakdown and Explanation:

#### 1. Window Creation and Application:

- The **PerformFFT**() function initiates by creating a Hamming window, a method used to reduce spectral leakage in FFT analysis. The window is generated by createHammingWindow(window, FFT\_LENGTH); where FFT\_LENGTH defines the size of the data set.

- The generated window is then applied to the input signal. This process involves multiplying each data point in the input signal with the corresponding window

function value to minimize edge effects in the FFT analysis.

#### 2. Signal Processing and FFT Execution:

- The function determines the input signal (sample\_L for the left channel or sample\_R for the right channel) based on the selected channel (selectedChannel).

- Windowed signal data is prepared by applying the Hamming window to the input signal.

- The arm\_rfft\_fast\_init\_f32(&S, FFT\_LENGTH); call initializes the FFT process, configuring the FFT length and setting up internal structures necessary for the computation.

- The actual FFT computation on the windowed signal is performed by arm\_rfft\_fast\_f32(&S, windowedSignal, fftOutput, 0);, where the third parameter indicates that a regular FFT (not inverse FFT) is to be computed.

#### 3. Magnitude Calculation and Data Transmission:

- Post-FFT, the magnitude of each frequency component is calculated using arm\_cmplx\_mag\_f32(fftOutput, fftMagnitude, FFT\_LENGTH / 2);. This step converts the complex FFT output into a real-valued magnitude spectrum.

- Finally, the FFT magnitude data is sent back to MATLAB for further analysis or visualization, facilitated by SendData2MTLB(ID\_FFT, (uint8\_t\*)fftMagnitude, FFT\_LENGTH / 2);.

#### **Understanding CMSIS DSP Library Functions:**

> arm\_rfft\_fast\_init\_f32(): This function initializes the FFT algorithm instance, setting up internal buffers and variables required for FFT computation. It considers the length of the FFT to be processed, thereby optimizing subsequent computations.

#### Parameters:

- **S** (in/out): A pointer to the **arm\_rfft\_fast\_instance\_f32** structure will hold the FFT process configuration.

- **fftLen (in)**: The length of the real sequence for which the FFT is computed. This parameter determines the size of the FFT computation and should be one of the supported lengths (32, 64, 128, 256, 512, 1024, 2048, 4096).

- > arm\_rfft\_fast\_f32(): The core function for performing the FFT. It takes the initialized FFT instance the input data buffer, and computes the FFT, placing the output in the specified buffer. The ifftFlag parameter determines whether a forward or inverse FFT is performed.

Flag to specify the operation type. A value of 0 indicates RFFT, and 1 indicates RIFFT.

#### Parameters:

- **S** (in): A pointer to the initialized arm\_rfft\_fast\_instance\_f32 structure containing the configuration for the FFT.

- **p** (in): Pointer to the signal data input buffer.

- **pOut (out)**: Pointer to the output buffer where the FFT result (IFFT, if specified) will be stored.

- **ifftFlag (in)**: Flag to specify the operation type. A value of 0 indicates RFFT, and 1 indicates RIFFT.

- > arm\_cmplx\_mag\_f32(): After the FFT is performed, this function calculates the magnitude of the complex FFT output, which is essential for analyzing the frequency spectrum of the input signal.

#### Parameters:

- **pSrc** (in): Pointer to the input vector containing complex numbers (real and imaginary parts interleaved).

- **pDst** (**out**): Pointer to the output vector where the magnitudes of the complex numbers will be stored.

- **numSamples (in)**: Number of complex samples in the input vector.

#### 3.6. Real-Time Processing of DTMF Signals

In embedded systems, where the interest often lies in identifying specific frequencies within an input signal, the Goertzel Algorithm emerges as an instrumental tool. This algorithm excels in scenarios where the frequencies of interest are predetermined, offering a streamlined and focused approach to frequency detection [19,20].

At its core, the Goertzel Algorithm is designed to detect the presence of a singular frequency component within a signal. Its operational foundation can be likened to a two-pole IIR filter. However, its theoretical underpinnings are closely tied to the principles of a single-bin output from the Discrete Fourier Transform (DFT). This relationship with DFT allows the Goertzel Algorithm to isolate and analyze a specified frequency within a signal efficiently [17].

The Mathematical Formulation of the Goertzel Algorithm

Figure 5. Block Diagram of the Goertzel Algorithm [21]

1. Calculation of Qn: Qn = x(n) + 2cos

$$(\frac{2\pi k}{N})$$

.  $Q_{n-1}$  -  $Q_{n-2}$

Where:

- x(n) represents the current input signal at time n.

- Qn is the output of the algorithm at time n.

- *k* is a constant determined by the targeted frequency.

- *N* is the total number of samples.

2. **Magnitude Calculation**:

$$|y_k(N)| = Q^2(N) + Q^2(N-1) - 2\cos(\frac{2\pi k}{N})$$

.  $Q(N) \cdot Q(N-1)$

This equation calculates the magnitude of the frequency component at the target frequency, k, after processing N samples.

In the above equation, if N is set to 205[1], then the value of k needs to be determined. The value of this constant k also determines the tone we are trying to detect and is given by [18]:

$$k = N * ftone / fs$$

(10)

Where: ftone = frequency of the tone

fs = sampling frequency.

Now we can calculate the value of the coefficient and obtain Table 2. [18]

$$2\cos(2\pi k/N) \tag{11}$$

A distinctive feature of the Goertzel Algorithm is its output validity, which is contingent on processing a complete set of input samples. The output becomes meaningful and accurate only after the algorithm processes N input samples, where N denotes the total count of inputs utilized [21].

.

This characteristic underscores the algorithm's efficacy in the real-time processing of a predetermined number of required samples.

| Frequency | K  | Coefficient |

|-----------|----|-------------|

| 697       | 18 | 1.703275    |

| 770       | 20 | 1.635585    |

| 852       | 22 | 1.562297    |

| 941       | 24 | 1.482867    |

| 1209      | 31 | 1.163138    |

| 1336      | 34 | 1.008835    |

| 1477      | 38 | 0.790074    |

| 1633      | 42 | 0.559454    |

Table 2. DTMF Tone Coefficients [22]

The Goertzel Algorithm's focused frequency detection makes it particularly suitable for embedded systems that require real-time analysis of specific frequency components. Its ability to isolate individual frequencies from a composite signal allows for efficient processing in applications such as DTMF decoding, signal monitoring, and targeted frequency analysis in various industrial and communication systems.

For instance, integrating the Goertzel Algorithm into STM32-based systems leverages the microcontroller's DSP capabilities to perform precise and real-time frequency analysis. This integration is critical in applications that demand high accuracy and efficiency in frequency detection, such as in telecommunication systems and signal processing modules.

Figure 6. DTMF Frequency Table for Keypad Tones.[23]

DTMF tone generation is an easy problem that can be solved by stepping through constant SINE

tables and adding the tones together. For example, the "5" tone combines the Row 2 tone of 770 Hz and the Column 2 tone of 1336 Hz, as shown.

Figure 7. Generation of the DTMF Tone for the Digit "5" Using 770 Hz and 1336 Hz Frequencies.[18]

Detecting DTMF signals necessitates a system's capability to discern both a row and a column tone, distinguishing between actual DTMF tones and voice. The Goertzel Algorithm is a suitable method for DTMF signal recognition due to its computational efficiency and non-reliance on historical input data. This algorithm is adept at isolating specific frequencies, facilitating the decoding of DTMF signals with promptness and accuracy.

These equations are tailored explicitly to detect DTMF signals. They should be included in the signal processing logic of the firmware, especially in systems utilizing STM32 microcontrollers, to handle real-time audio signal processing efficiently [24].

#### 3.6.1. STM32 Implementation of DTMF

In signal processing within embedded systems, the STM32 microcontroller series is a potent platform for implementing real-time Dual-Tone Multi-Frequency (DTMF) detection algorithms. The STM32's processing power and internal architecture, complemented by its digital signal processing (DSP) capabilities, make it an ideal candidate for executing computationally intensive tasks, such as DTMF detection using the Goertzel Algorithm.

```

void detect DTMF(uint32_t blockSize) {

// Define a pointer to the input signal array

float32_t *input signal;

// Select the appropriate input signal based on the selected channel

inputSignal = (selectedChannel == 0) ? sample_L : sample_R;

// Compute the Goertzel coefficients for the DTMF frequencies

for (int i = 0; i < DTMF_NUM_FREQS; i++) {

float32_t k = (0.5f + ((blockSize * dtmfFreqs[i]) / Fs));</pre>

```

```

goertzelCoeff[i] = 2 * arm_cos_f32((2 * M_PI * k) / blockSize);

// Loop over each DTMF frequency to compute its power

for (int i = 0; i < DTMF_NUM_FREQS; i++) {

// Initialize variables for the Goertzel algorithm

float32_t prev1 = 0.0f, prev2 = 0.0f, total power = 0.0f;

// Apply the Goertzel algorithm to the signal block

for (int j = 0; j < blockSize; j++) {

float32_t y = inputSignal[j] + goertzelCoeff[i] * prev1 - prev2;

prev2 = prev1;

prev1 = y;

// Calculate the total power of this frequency

totalPower = prev1 * prev1 + prev2 * prev2 - goertzelCoeff[i] * prev1 * prev2;

// Compare the power to a predefined threshold

if (totalPower > THRESHOLD) {

// DTMF frequency detected, perform the necessary action

}

// Store the power values for further processing or transmission

dtmfPower[i] = totalPower;

}

// Use the DTMF power values for transmission to MATLAB or another system

SendData2MTLB(ID_DTMF_DETECTED, (uint8_t*)dtmfPower, DTMF_NUM_FREQS);

}

```

Source Code 5. STM DTMF Processing by CIMSIS-Library

The Goertzel Algorithm, a DSP technique, is particularly effective in detecting specific frequency components within a signal. It is commonly employed in DTMF detection due to its efficiency and lower computational overhead than the Fast Fourier Transform (FFT). The STM32 series, with its comprehensive suite of peripherals and hardware accelerators, allows for the seamless integration of such algorithms to process and analyze audio signals in real-time.

The code snippet presented for detecting the DTMF function illustrates a practical approach to DTMF detection on an STM32 microcontroller. This function is crafted to compute the power of predefined DTMF frequencies within a signal block and identify the presence of DTMF tones based on a threshold comparison.

The function delineates several vital steps:

- 1. Initialization begins by defining a pointer to an array holding the input signal. This pointer is assigned to the appropriate channel data (sample\_L or sample\_R) based on user selection.

- Coefficient Calculation: Utilizing a loop, the function calculates the Goertzel coefficients for each frequency of interest. The coefficient calculation involves an iterative computation of the cosine function, arm\_cos\_f32, which is efficiently executed thanks to the STM32's floating-point unit (FPU).

- 3. Power Computation: The function then enters another loop to apply the Goertzel Algorithm to the signal block. It initializes the variables **prev1** and **prev2** to store the intermediate values required for the Goertzel calculation. Each input signal sample within this loop contributes to computing the power for the current DTMF frequency.

- 4. Threshold Comparison: After computing the power for a frequency, the function compares it against a predefined threshold. If the power exceeds this threshold, it suggests detecting a DTMF tone, triggering the appropriate response within the system.

- 5. Data Storage and Transmission: The computed power values are stored for further analysis or communication with other systems, such as MATLAB, for visualization or additional processing.

#### 4. METHODOLOGY AND SYSTEM IMPLEMENTATION

#### 4.1. System Architecture and Design

The architecture delineated in this thesis is specifically engineered for digital signal processing (DSP) applications, utilizing STM32 microcontrollers combined with a MATLAB interface to ensure optimal performance, flexibility, and real-time processing capabilities. This system architecture includes essential components such as the STM32 microcontroller and peripheral devices like Analog-to-Digital Converters (ADCs). These are augmented by a MATLAB-based graphical user interface (GUI) that enhances control and data visualization, as detailed in Figure 8.

Figure 8. Workflow diagram of Matlab and STM32 DSP Operations

Central to the system is the STM32 microcontroller, particularly chosen for its superior performance traits within the STM32F7 series. This series is strategically selected for its exceptional high-performance characteristics, crucial for meeting real-time DSP applications' rigorous demands. Integrating a Floating-Point Unit (FPU) within the STM32F7 series significantly augments the efficiency of executing complex DSP algorithms. The STM32F7 series, equipped with the Cortex-M7 processor, is renowned for its robust processing capabilities at a core clock frequency of 216 MHz. This processor's speed and advanced architectural features make it exceptionally well-suited for demanding DSP tasks. The ADCs play a pivotal role in the system, converting analog signals into a digital format for subsequent processing. These converters' meticulous configuration and proficient utilization are paramount to maintaining signal integrity and achieving the desired real-time performance.

In embedded audio processing, the system's architecture is meticulously orchestrated to align with the Integrated Just-In-Time Sound (I-JITS) protocol, ensuring high-fidelity sound reproduction. The configuration employs the STM32 microcontroller that operates at a core clock frequency of 216 MHz, independent of the I2S interface's Master Clock (MCLK). The MCLK serves as the cornerstone for audio signal synchronization, typically derived from an external crystal oscillator or a phase-locked loop (PLL) circuit to meet the precise requirements of the analog-to-digital converters (ADCs) within the audio codec.

Figure 9. I2S Data Transmission Format Showing Left and Right Channel Bit Alignment.[14]

The MCLK is set distinctly from the microcontroller's operating frequency, tailored to facilitate a sampling rate of 48 kHz, a standard in professional audio applications. This rate is achieved by calibrating the MCLK to a suitable frequency that, when divided down through the I2S clock management system, provides the exact bit clock (SCLK) and word select (LRCK) rates necessary for seamless stereo audio streaming. A 2.8224 MHz MCLK in this implementation would be inappropriate, as it aligns with the 44.1 kHz sampling rate commonly used for CD-quality audio.

Figure 10. Graphical User Interface for DSP Application with Serial COM Port Connection.

Figure 10 illustrates the MATLAB-based GUI, which enables the user's ability to connect to the device by selecting from available COM ports, toggle between audio channels, and monitor the results of DSP processes in a visual format. This interface empowers the user to interact with the system dynamically, offering an enhanced user experience in real-time system management.

The MATLAB interface is further extended to include dedicated tabs for Finite Impulse Response (FIR), Infinite Impulse Response (IIR), Dual-Tone Multi-Frequency (DTMF) signaling, and Fast Fourier Transform (FFT) analysis, each facilitating specialized signal processing functions. The FIR tab, for instance, provides tools for generating and applying filter coefficients, visualizing magnitude and phase responses, and sending filter configurations to the STM32 microcontroller. Similarly, the IIR segment allows intricate filter design and real-time response observation. DTMF and FFT tabs offer user-friendly interfaces for tone generation, detection, and spectral analysis, contributing to a comprehensive DSP toolkit. The GUI's modular design ensures a seamless workflow, enabling users to navigate between different DSP operations efficiently, enhancing the interactive experience, and promoting practical exploration of DSP concepts.

Figure 11. Graphical User Interface for DSP Application

Figure 11 depicts the GUI's additional segments, showcasing the user's ability to interact with various DSP functionalities. These include generating filter coefficients, transmitting filter data to the hardware, and real-time audio loopback testing. This level of interaction exemplifies the GUI's role as an essential facilitator in applying complex DSP algorithms within an educational or research context.

## 4.2. Firmware and Software Development

In embedded systems, integrating firmware development for the STM32 microcontroller with a MATLAB Graphical User Interface (GUI) establishes a cohesive platform for executing real-time digital signal processing (DSP). This section explores the complexities of developing firmware that equips the STM32F7 series with sophisticated DSP functionalities, including digital filtering, spectral analysis, and signal recognition.

The firmware capitalizes on the robust processing power of the STM32F7 series to efficiently perform a range of DSP functions. A notable innovation in the firmware design is the protocol for identifying incoming data types. This is facilitated by an identifier (ID), where IDs greater than 215,215 denote floating-point numbers, and lower values represent 32-bit unsigned integers. This identification strategy optimizes handling varied data types, aligning them with the specific computational demands of DSP operations.

A standardized block size for data packets has been adopted to improve system performance.

This measure addresses previous challenges associated with variable data sizes, which have led to performance degradation and occasional system failures. Standardizing data packet size has enhanced system stability and mitigated negative impacts on processing performance during increases in sampling rates.

Concurrently, a MATLAB GUI has been meticulously designed to manipulate and configure the DSP algorithms executed on the microcontroller. Via the USB CDC virtual COM port, the GUI facilitates dynamic adjustments to DSP parameters that directly influence the microcontroller's real-time processing activities. The MATLAB script's **readDataSTM32** function exemplifies this interaction, efficiently sorting and classifying data based on the ID. Additionally, the **isReady** utility verifies data availability within the serial buffer, ensuring consistent and dependable data acquisition.

To further augment system performance, the firmware development incorporated the use of the CMSIS DSP library. This strategic choice was influenced by empirical evidence demonstrating its advantages in efficiency. Previous endeavors without this library had experienced noticeable performance declines, particularly under conditions involving extensive buffer sizes, leading to significant computational delays. The CMSIS DSP library, specifically optimized for the ARM Cortex processor series, provides a suite of highly optimized signal processing functions that markedly enhance DSP operations on the STM32 microcontroller. The adoption of this specialized DSP library has proven essential for achieving the requisite performance levels in real-time signal processing tasks.

## 4.3. Hardware Setup and Firmware Integration

In this thesis's development, the clock system's configuration in STM32 microcontrollers is meticulously outlined, underscoring its critical role in ensuring optimal microcontroller operations across various digital signal processing (DSP) tasks. This setup is paramount for achieving accurate signal sampling, processing, and analysis, and it is pivotal in applications involving audio signal modulation, data conversion, and real-time signal analysis.

The STM32's clock system configuration involves defining multiple clock sources and adjusting various multiplexers and dividers to tailor the operational frequencies for different peripherals. This process begins by selecting an appropriate external high-speed clock (HSE) source, set at 8 MHz, serving as the reference for the Phase-Locked Loop (PLL), which multiplies the HSE to achieve the higher frequencies required by the system

| SAI A                              |                    |  |

|------------------------------------|--------------------|--|

| Synchronization Inputs             | Asynchronous       |  |

| Basic Parameters                   |                    |  |

| Audio Mode                         | Master Transmit    |  |

| Output Mode                        | Stereo             |  |

| Companding Mode                    | No companding mode |  |

| SAI SD Line Output Mode            | Driven             |  |

| Protocol Parameters                |                    |  |

| Protocol                           | I2S Standard       |  |

| Data Size                          | 24 Bits            |  |

| Number of Slots (only Even Values) | 2                  |  |

| Clock Parameters                   |                    |  |

| Master Clock Divider               | Enabled            |  |

| Audio Frequency                    | 48 KHz             |  |

| Real Audio Frequency               | 48.0 KHz           |  |

| Error between Selected             | 0.0 %              |  |

| Advanced Parameters                |                    |  |

| Fifo Threshold                     | Empty              |  |

| Output Drive                       | Disabled           |  |

| SALB                               |                    |  |

| Synchronization Inputs             | Asynchronous       |  |

| Basic Parameters                   | ,                  |  |

| Audio Mode                         | Master Receive     |  |

| Output Mode                        | Stereo             |  |

| Companding Mode                    | No companding mode |  |

| Protocol Parameters                |                    |  |

| Protocol                           | I2S Standard       |  |

| Data Size                          | 24 Bits            |  |

| Number of Slots (only Even Values) | 2                  |  |

| Clock Parameters                   |                    |  |

| Master Clock Divider               | Enabled            |  |

| Audio Frequency                    | 48 KHz             |  |

| Real Audio Frequency               | 48.0 KHz           |  |

| Error between Selected             | 0.0 %              |  |

| Advanced Parameters                |                    |  |

| Fifo Threshold                     | Empty              |  |

| Output Drive                       | Disabled           |  |

Figure 12. SAI Configuration on STM

Accurate configuration of the Phase-Locked Loop (PLL) is essential as it determines the core operating frequency of the microcontroller. Specific multipliers (N), prescalers (P), and dividers (Q and R) are carefully selected to produce the required internal clock speeds. The output of the PLL, referred to as PLLCLK, drives the SYSCLK at 216 MHz, providing the necessary operational speed for high-performance tasks.

This meticulous clock configuration for the I2S peripheral, which handles audio data, is crucial. The I2S\_CKIN, derived from the PLLI2S, is adjusted to closely match the standard audio rate of 48 kHz. Given the precision of modern digital systems and thorough calibration, the audio frequency precision targets the standard 48 kHz, ensuring optimal audio processing without any deviations.

The accurately configured clock frequencies are essential for data acquisition and processing in real-time DSP applications. For example, the correct setup of I2S\_CKIN ensures that the audio data is

sampled and processed at the intended rate, which is crucial for maintaining audio integrity and quality. The absence of frequency variation confirms the system's capability to handle precise audio processing tasks, meeting the stringent performance and accuracy requirements in digital audio applications. Moreover, integrating a meticulously configured hardware setup and specialized firmware development is vital in effectively deploying embedded systems for real-time digital signal processing. This section explores the nuanced processes involved in setting up the hardware and integrating firmware that supports the execution of DSP algorithms, mainly focusing on enhancing the functionality of Analog-to-Digital Converters (ADCs) and optimizing real-time processing tasks such as Dual-Tone Multi-Frequency (DTMF) detection. The hardware configuration is vital in preparing the microcontroller environment for precise operation. An essential aspect of this setup is configuring the timers, which serve as the heartbeat for tasks requiring strict timing, such as sampling signals for DSP.

- 1. **Prescaler (PSC 16-bit value)**: The prescaler value is pivotal in scaling the input clock frequency (f\_clk) to a more manageable timer clock frequency. **Timer Clock Frequency** = **f\_clk / (PSC + 1)** utilizes the prescaler value to divide the clock frequency. The subtraction by one accounts for the zero-based counting nature of the hardware timers. For instance, with an f\_clk of 21.6 MHz and a PSC of 21600, the resultant timer clock frequency would be 1 Hz, derived from 21.6 MHz / (21600 + 1).

- 2. **Counter Mode**: This setting dictates the count sequence of the timer. An 'Up' configuration signifies an ascending count from 0, instrumental in standard timing operations.

- 3. **Counter Period (AutoReload Register ARR)**: The counter period is crucial in defining the upper limit of the timer count. Upon reaching this predefined value, the timer can trigger a designated event or reset, creating a consistent time base for various operations. An ARR setting of 10000-1 implies a counting sequence up to 10000 before initiating the subsequent action.

- 4. **Auto-reload preload**: This functionality allows a buffer register for the ARR, with 'Disable' indicating a direct application of the ARR value, facilitating immediate changes to the timer's behavior without needing a buffer phase.

- 5. **Trigger Output (TRGO) Parameters**: These parameters determine the specific event that prompts the timer to emit a trigger signal. The 'Reset (UG bit from TIMx\_EGR)' configuration suggests the trigger is linked to the update generation event, typically utilized for counter resets or register updates.

Calculating the Timer Overflow Time: The timer overflow time represents the duration for a full count cycle, from 0 to the ARR value. The formula for calculating this time interval is  $(PSC + 1) \times (ARR + 1) / f_{clk}$ . Applying the given values, with an f\_clk of 21.6 MHz, we get  $(21600 + 1) \times (10000 + 1) / 21.6 \times 10^{6}$ . This calculation is essential for synchronizing the embedded system's operations with the required precision for DSP tasks.

$$Duration = \frac{(TimerPrescaler+1)(TimerPeriod+1)}{TimerClock}$$

(12)

## 4.4. System Interface and Data Analysis

This segment elucidates the interface intricacies between MATLAB and STM32 microcontroller, which underpins the robust digital signal processing (DSP) framework delineated herein. The intercommunication is facilitated by a high-throughput serial communication channel, operating at an expedited baud rate of 2\*115200. This rate is meticulously selected to accommodate the high-bandwidth requirements essential for real-time DSP while maintaining the integrity and fidelity of the data exchange.

#### 4.4.1. Serial Communication Protocol and Data Format

The strategic implementation of the communication protocol is a testament to the system's efficiency. **SendData2MTLB** within the STM32 firmware stands as a paradigm of this, adeptly packaging data alongside its corresponding identifier before dispatching it over the CDC protocol via a micro-USB connection. The data format is judiciously determined by the iD, which predicates the subsequent processing routine, typically utilizing single floating-point precision to accommodate the rigorous demands of DSP computations.