# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

# DEPARTMENT OF ELECTRICAL AND ELECTRONIC TECHNOLOGY

ÚSTAV ELEKTROTECHNOLOGIE

# RS-FEC LAYER IMPLEMENTATION FOR 400GB/S ETHERNET

**RS-FEC LAYER IMPLEMENTATION FOR 400GB/S ETHERNET**

MASTER'S THESIS DIPLOMOVÁ PRÁCE

AUTHOR AUTOR PRÁCE Bc. Patrik Zahálka

SUPERVISOR VEDOUCÍ PRÁCE

Ing. Petr Vyroubal, Ph.D.

**BRNO 2020**

# **Master's Thesis**

Master's study field Electrical Manufacturing and Materials Engineering

Department of Electrical and Electronic Technology

Student: Bc. Patrik Zahálka Year of study: ID: 173783

Academic year: 2019/20

TITLE OF THESIS:

### **RS-FEC** layer implementation for 400Gb/s ethernet

#### **INSTRUCTION:**

Learn about the Intel Stratix 10 DX FPGA chips and describe the principles of Reed-Solomon correction coding and its use in the Ethernet protocol. Design an RS-FEC layer architecture for 400 Gb / S Ethernet on an Intel Stratix 10 DX FPGA chip. Implement the proposed architecture and verify its functionality in simulations. Evaluate the results and discuss the possibilities for further expansion.

#### **RECOMMENDED LITERATURE:**

Podle pokynů vedoucího diplomové práce.

Date of project 3.2.2020 specification:

Deadline for submission: 19.5.2020

Supervisor: Ing. Petr Vyroubal, Ph.D.

**doc. Ing. Petr Bača, Ph.D.** Subject Council chairman

#### WARNING:

The author of the Master's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

Faculty of Electrical Engineering and Communication, Brno University of Technology / Technická 3058/10 / 616 00 / Brno

# Diplomová práce

magisterský navazující studijní obor Elektrotechnická výroba a materiálové inženýrství

Ústav elektrotechnologie

Student: Bc. Patrik Zahálka Ročník: 2

*ID:* 173783 *Akademický rok:* 2019/20

#### NÁZEV TÉMATU:

### Implementace vrstvy RS-FEC pro 400 Gb/s Ethernet

#### POKYNY PRO VYPRACOVÁNÍ:

Seznamte se s FPGA čipy Intel Stratix 10 DX a popište principy opravného kódování Reed-Solomon a jeho použitím v rámci protokolu Ethernet. Navrhněte architekturu vrstvy RS-FEC pro 400 Gb/S Ethernet na FPGA čipu Intel Stratix 10 DX. Navrženou architekturu implementujte a ověřte její funkčnost v simulacích. Zhodnoťte dosažené výsledky a diskutujte možnosti dalšího rozšíření.

#### DOPORUČENÁ LITERATURA:

Podle pokynů vedoucího diplomové práce.

Termín zadání: 3.2.2020

Vedoucí práce: Ing. Petr Vyroubal, Ph.D.

Termín odevzdání: 3.6.2020

doc. Ing. Petr Bača, Ph.D. předseda oborové rady

#### UPOZORNĚNÍ:

Autor diplomové práce nesmí při vytváření diplomové práce porušit autorská práva třetích osob, zejména nesmí zasahovat nedovoleným způsobem do cizích autorských práv osobnostních a musí si být plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení části druhé, hlavy VI. díl 4 Trestního zákoníku č.40/2009 Sb.

Fakulta elektrotechniky a komunikačních technologií, Vysoké učení technické v Brně / Technická 3058/10 / 616 00 / Brno

### ABSTRACT

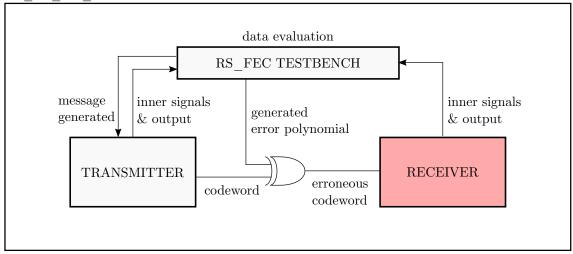

This Master's thesis deals with RS-FEC layer implementation using VLSI hardware description for 400 GE (Gigabit Ethernet) in the FPGA Intel® Stratix® 10 DX 2100. In the theoretical part of this work, current state of Ethernet speeds and context of RS-FEC layer within Ethernet protocol is described including PLD fabrication process and mathematical aspects of RS-FEC self-correction algorithm. In the practical part, parametrizable RS-FEC system is described including evaluation of the first results achieved and future scope of this project is discussed.

### **KEYWORDS**

Reed-Solomon Error Correction Codes, Forward Error Correction, 400 Gbps Ethernet, FPGA

### ABSTRAKT

Tato diplomová práce se věnuje problematice VLSI návrhu a implementaci vrstvy RS-FEC pro 400 Gb/s Ethernet do FPGA Intel® Stratix® 10 DX 2100. V práci je charakterizován současný stav rychlostí Ethernetu, význam a kontext samoopravných kódů v rámci protokolu Ethernet. Dále je popsána výroba PLD čipů i matematická podstata RS samoopravných kódů. V části praktické je představen návrh řešení systému RS-FEC, který byl realizován genericky pomocí jazyka VHDL. Zároveň byly jeho komponenty implementovány a v závěrečné diskusi je popsáno jeho řešení, dosažené výsledky včetně jeho budoucího rozšíření.

# KLÍČOVÁ SLOVA

Reed-Solomonovy samoopravné kódy, 400 Gb/s Ethernet, FPGA

ZAHÁLKA, Patrik. *RS-FEC layer implementation for 400 Gb/s Ethernet*. Brno, 2020, 77 p. Master's Thesis. Brno University of Technology, Fakulta elektrotechniky a komunikačních technologií, Ústav elektrotechnologie. Advised by Ing. Petr Vyroubal, Ph.D.

Typeset by the thesis package, version 3.05; http://latex.feec.vutbr.cz

### ROZŠÍŘENÝ ABSTRAKT

V dnešní době nám možná připadá přirozené, že poskytovatelé datových služeb přichází čas od času s novými produkty i vyššími rychlostmi datových přenosů. Dříve bylo standardní praxí počkat si na to, až se nám s připojením přes telefonní linku načte obrázek a netrpělivě jsme sledovali každou jeho načtenou část. Dnes však na tuto skutečnost pomalu zapomínáme. Navíc i vzhledem k tomu, že se do sítě připojuje stále více nových zařízení, stávají se internetové služby populárním a nepostradatelným médiem pro dnešní společnost [1]. Nároky uživatelů internetu ruku v ruce s technologickým pokrokem však dovedly maximální přenosové rychlosti od jednotek kilobitů po stovky gigabitů za sekundu, a meta zde rozhodně nekončí. V současné době existují experimantální vysokorychlostní ethernetové platformy, které operují bezmála na jednotkách terabitů za sekundu. Rychlejší přenos dat neznamená pouze nějaké vyšší číslo či kratší dobu čekání na odeslání souboru. Stojí za tím obrovské úsilí celého elektrotechnického průmsylu od inovací v kabeláži, elektrotechnické i elektronické výrobě po inovace v informačních a síťových technologiích. Každý takový pokrok umožní posun v jiných odvětvích, například ve zdravotním průmyslu pro vývoj nových léků a vakcín, předpovědích klimatu, finančních službách, genetickém inženýrství atp.

Vzhledem k tomu, že jsou obecně přenosová média vystavena faktorům rušení, stává se běžně, že se někdy přenesená zpráva poškodí a přijímač ji proto poté chybně vyhodnotí (či vůbec). Toto se stává tím častěji, čím rychlejší platforma je a čím méně je ošetřena proti rušení. Tomu lze však předejít několika způsoby. Jedním z nich je např. použití kroucené dvojlinky, která je však tématem pro nižší přenosové rychlosti, až 1 Gbit/s [2]. Jiný způsob, než použití kabeláže, je implementace samoopravných algoritmů pro rekonstrukci přenášené zprávy navzdory tomu, že je z části poškozena. Jedná se o algoritmy, které lze implementovat do hradlových polí FPGA jako firmware. V této diplomové práci je řešen aspekt implementace Reed-Solomonových kódu pomocí návrhu VLSI pro hradlová pole Intel<sup>®</sup> Stratix<sup>®</sup> 10 DX pro projekt NDK - Netcope Development Kit.

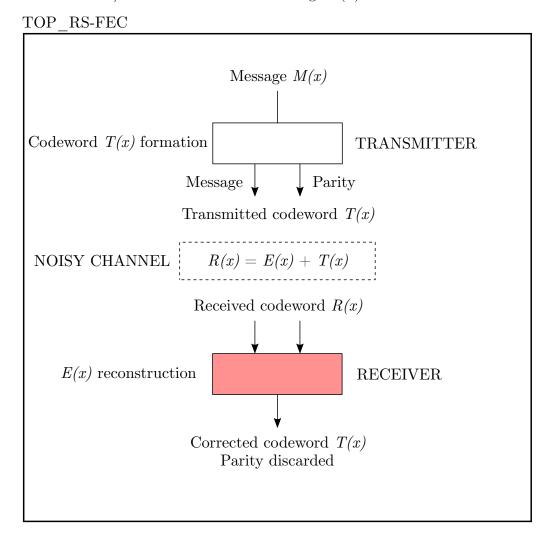

Reed-Solomonovy kódy byly doporučeny jako vhodné řešení pro dosažení rychlostí 100 Gb/s ve standardu IEEE Std.  $802.3bm^{\rm TM}$  z roku 2015. Důvodem je hlavně to, že jsou celkově dobře prostudovány a jejich vývoj sice stojí úsilí, ale dodá potřebnou kapacitu pro opravování chyb a lze je v rozumném měřítku implementovat do hradlových polí FPGA. Základní koncept pro opravu chyb pomocí Reed-Solomonových kódů spočívá v tom, že se připojí redundantní část o určitém počtu symbolů ke zprávě, kterou chceme poslat, tzv. parita. Tím se vytvoří unikátní a validní datový "balík", tzv. kódové slovo, které je výstupem vysílací strany systému RS-FEC. Pokud se kódové slovo poškodí, přijímací strana chybu detekuje a vytvoří polynom, který se dále dešifruje následujícími komponentami, které dokáží

najít pozice chyb a jejich velikosti na těchto pozicích. Toto "poškození" lze chápat tak, že se k původnímu nepoškozenému kódovému slovu přičetl určitý chybový polynom, který právě reprezentuje vzniklý šum. Systém tedy hledá přesně tento polynom, který způsobil chybu při přenosu, tzv. chybový polynom E(x). Nalezením tohoto polynomu a jeho přičtením k přijatému "poškozenému" kódovému slovu se docílí rekonstrukce, ideálně původního validního kódového slova. Reed-Solomonovy kódy se obecně značí RS(n, k), kde n specifikuje počet prvků celého kódového slova a k počet prvků zprávy.

Tato diplomová práce se tedy zabývá touto problematikou, implementací RS(544, 514) pro 400 Gb/s Ethernet. Předpokládá se, že čtenář nemá předchozí zkušenosti s touto problematikou, a proto je v práci Reed-Solomonův samoopravný algoritmus detailně shrnut. Teoretická část dále obsahuje kapitolu o síťových technologiích, výrobě mikročipů a informace o použité technologii. V praktické části je uveden návrh řešení systému pro 400GE (Gigabit Ethernet), podrobný rozbor navržených komponent a prozatimní dosažené výsledky úspěšné implementace. Dále jsou v tomto textu shrnuty výsledky a také je konstruktivně okomentováno další rozšíření tohoto systému. Samotný proces Reed-Solomonových samoopravných kódů je detailně popsán v [3] včetně jeho hardwarové podoby, a proto se tato diplomová práce z velké části odkazuje právě na tento zdroj.

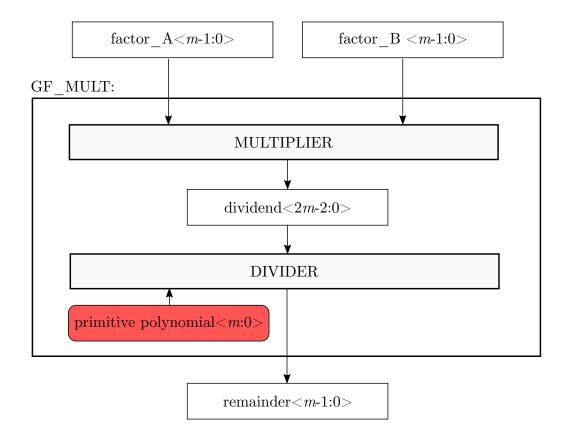

Reed-Solomonovy kódy operují nad tzv. Galoisově konečným tělesem. To ve výsledku znamená, že celý samoopravný algoritmus provádí výpočty s (m-1)-bitovými symboly, přičemž každý takový symbol je jedním z celkem jeho  $2^m - 1$  uspořádaných členů. V rámci systému RS-FEC pro 400GE se výpočet provádí s desetibitovými symboly, proto m = 10. Prvky Galoisova tělesa jsou určeny i uspořádány podle toho, jaký tzv. primitivní polynom p(x) řádu m (v binární podobě) toto těleso vytváří. Zajímavou vlastností konečných těles je to, že pokud se budeme snažit vytvořit  $(2^m + 1)$  prvek, výsledkem bude znovu prvek první,  $(2^m + 2)$  prvek je znovu prvek druhý atd. V Galoisově tělese platí také odlišná algebra, a to taková, že při provádění algebraických operací nedochází ke změně řádů (přetékání bitů). Operace sčítání a odčítání je jedna a ta samá operace, která se provádí pomocí hradla XOR. Systém tedy nevyžaduje použití žádných sčítaček ani odčítaček, a tudíž nelze využít DSP bloky v čipu FPGA. V práci byla tedy zvolena varianta implementace systému do Look-up tabulek hradlového pole včetně jejich použití jako paměti ROM. Jak je obecně známo, logické operátory XOR jsou sobě komutativní a výsledný návrh lze optimalizovat, což provádí syntézní nástroje, v této práci Intel Quartus Prime Pro [4]. Operace násobení se také liší a provádí se ve dvou fázích. Vstupy do násobičky nad  $GF(2^m)$  chápeme jako polynomy řádu m-1 a provádíme klasické násobení mnohočlenu mnohočlenem. Výsledek tohoto násobení však překračuje řád prvků  $GF(2^m)$  a je tedy nutné jej do tohoto řádu "vrátit" pomocí operace modulo

m vydělením tím samým primitivním polynomem p(x), který generuje celé Galoisovo těleso  $GF(2^m)$ . Implementace dělení v Galoisově poli je komplikovanější a vyžaduje využití velkého množství logických zdrojů. Vzhledem k tomu, že se v systému RS-FEC násobičky vyskytují ve velkém množství, jedná se o komponentu velmi náročnou na využití zdrojů v FPGA, zejména Look-up tabulek. Dělení bylo provedeno tak, že po nalezení inverzního prvku dělitele (jmenovatel) se tento prvek vynásobil s dělencem (čitatel). V komponentách, kde se provádí dělení nad  $GF(2^m)$ , se proto musely nejdříve najít tyto inverzní prvky, seřadit vzestupně dle jejich základní hodnoty a pro dosažení vysoké datové propustnosti implementovat do Look-up tabulek charakteru ROM. Toto provádí navržený VHDL podprogram, který dokáže vytvořit GF inverze pro kterákoliv požadovaná  $GF(2^m)$  bez nutnosti spouštět externí skripty. Tyto vektory však zabírají velké množství logických zdrojů a bylo potřeba jich v systému generovat co nejméně. I když je systém syntetizovatelný, výsledný návrh vyžaduje pro finální implementaci z důvodu přílišného využití dostupných zdrojů v FPGA odpovídající optimalizace. To se také projevuje dlouhou dobou fáze hledání vhodného propojení logických buněk (Route). V návrhu bylo tedy nutné vhodně určit, kdy použít konstanty a kdy násobičky. Pro samoopravný algoritmus bylo také potřeba najít čtverce a vyšší řády Galoisova tělesa. Vhodným řešením bylo použití operace násobení nežli generování konstanty navzdory tomu, že prvotní návrh počítal s pravým opakem, a to z důvodu využití co nejmenšího množství násobiček v GF pro zkrácení kritické cesty ze vstupu na výstup komponent.

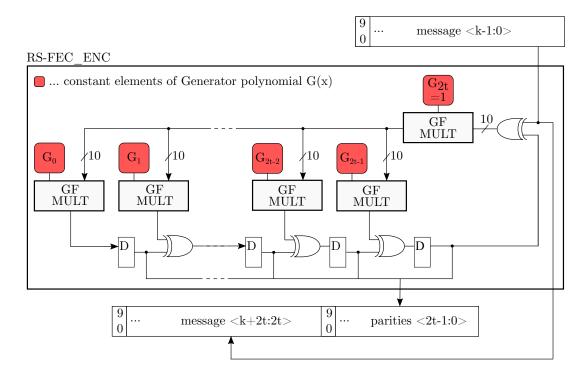

Vrstva RS-FEC je součástí podvrstvy PCS (Physical Coding Sublayer) fyzické vrstvy Ethernetu PHY. Komponenta systému RS-FEC, která přijímá data z PCS vrstvy na vysílací straně, se nazývá RS-FEC Enkodér, který provádí tzv. skramblování. To je takový rekurzivní proces, který provádí dělení mnohočlenu mnohočlenem, tedy celé zprávy M(x) tzv. Generačním polynomem G(x), který definuje norma IEEE Std 802.3bs<sup>TM</sup> 2017. Jeho úkolem je vytvořit tzv. *paritu*, což je zbytek po tomto rekurzivním procesu dělení. V praxi se při implementaci RS-FEC Enkodéru ukázalo, že syntézní nástroje nedokáží plně optimalizovat komplexní zapojení této funkce pro potřebnou datovou propustnost, což je z velké části dáno návrhem násobiček. Zjistilo se, že dva různé parametrizovatelné návrhy násobiček v RS-FEC Enkodéru vyústily ve dva různé, avšak zanedbatelně rozdílné, výsledky ve smyslu využití zdrojů, a proto je potřeba hledět na procesy skramblování a deskramblování jinak, než udává obecné schéma pro provádění této operace.

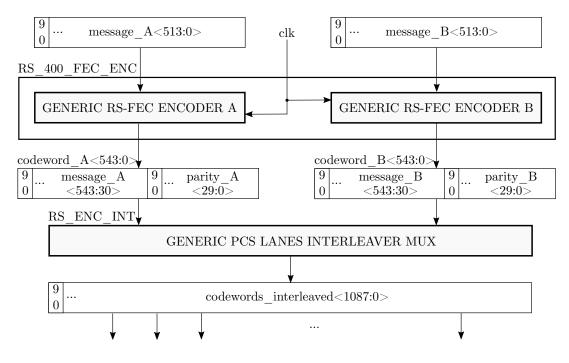

Vysílací strana dále také provádí distribuci jednotlivých symbolů zprávy mezi jednotlivé linky PCS. Vzhledem ke standardu IEEE Std 802.3 bs<sup>TM</sup> 2017 distribuci provádí MUX mezi 16 PCS linek, přičemž navržený systém nabízí funkci volby počtu linek pomocí generických patametrů, a tudíž lze navržený systém použít i pro 200GE

či budoucí rychlosti Ethernetu, pro které v současnosti ještě neexistuje normovaná verze.

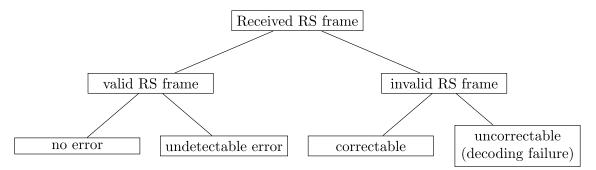

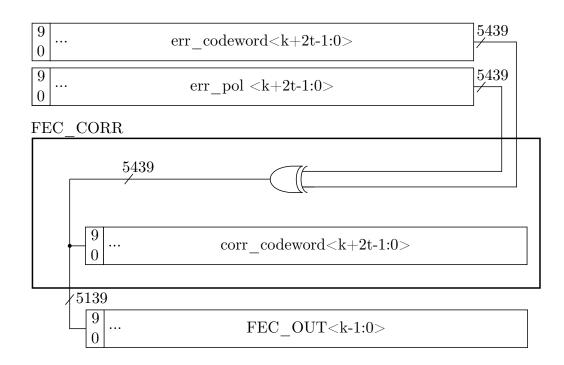

Druhou částí systému RS-FEC je část přijímací, která dekóduje dvě kódová slova. Pro provedení opravy zprávy musí přijímací strana nejprve vrátit proložené symboly zprávy do stavu před proložením. Poté se provede tzv. deskramblování, a to každého přijatého kódového slova. To je obdobný proces jako skramblování, avšak se v tomto případě dělení provádí pouze jedním elementem Galoisova tělesa, resp. kořenem generačního polynomu G(x), poté jeho následujícím elementem, atp. Dělení se provede tedy celkem 2t-krát, přičemž v FPGA lze toto dělení provádět paralelně. Nutno podotknout, že opravnou kapacitu Reed-Solomonova samoopravného algoritmu t určuje jeho tzv. Hamingova vzdálenost, která je dána počtem paritních symbolů, v tomto případě algoritmus opraví až 15 symbolů. Deskramblováním lze zjistit, zda jsou přijatá kódová slova dělitelná beze zbytku kořeny Generačního polynomu G(x). Tím se ověří, zda při přenosu k nějaké chybě došlo, čili zda je na vstupu dekodéru validní kódové slovo či nikoliv. Pokud je výsledek nulový, systém RS-FEC opravu provádět nebude. Pokud ne, deskrambler vytvořil takový polynom, který je nutno dále dešifrovat za účelem zpětného vytvoření validního kódového slova. Takový vytvořený polynom se nazývá syndrom S(x) a přímo charakterizuje chybový vektor E(x). Operace pro výpočet syndromů S(x) lze také chápat jako provádění rychlé Fourierovy transformace nad konečným Galoisovo tělesem, CFFT (Cyclotomic Fast Fourier Transform).

Díky nalezeným syndromům S(x) lze najít pozice a velikosti chyb na těchto pozicích ve třech komponentách. Děšifrování tedy pokračuje hledáním dvou polynomů, a to polynomu pro lokalizaci chyb  $\Lambda(x)$ , tzv. lokátoru chyb, a vektoru vyhodnocujícího velikosti chyb  $\Omega(x)$ . Pro jejich nalezení byl použit rozšířený Euklidův algoritmus, který obecně provádí hledání největšího společného dělitele (NSD) dvou polynomů  $S(x), x^{2t}$ . V procesu dekódování je Euklidův algoritmus použit pro řešení tzv. klíčové rovnice (anglicky Key equation), která řeší polynom  $\Omega(x)$ . Tuto tzv. Klíčovou rovnici lze upravit do tvaru pro Euklidův procesor, čili  $S(x) \times \Lambda(x) +$  $F(x) \times x^{2t} = \Omega(x)$ . Cílem Euklidova procesoru však není nalezení NSD, nýbrž přímo polynomů  $\Omega(x)$  a  $\Lambda(x)$ , což je jeho hlavní výhoda. Euklidův procesor se sestává z celkem t vrstev, přičemž každá vrstva se skládá ze strany pro polynomiální dělení a násobení. Při výpočtu se v jeho každé následující vrstvě snižuje stupeň mezivýsledku polynomu  $\Omega(x)$ , zatímco se zvyšuje řád  $\Lambda(x)$ , což reflektuje počet vzniklých chyb. Euklidův algoritmus se "zastaví", jakmile splní podmínku stupně mezivýsledku  $\Omega(x) < t$ . V tomto bodě lze polynom  $\Lambda(x)$  vyřešit v kompoentě Chien search a signál  $\Omega(x)$  přivést na vstup komponenty Forneyho algoritmu.

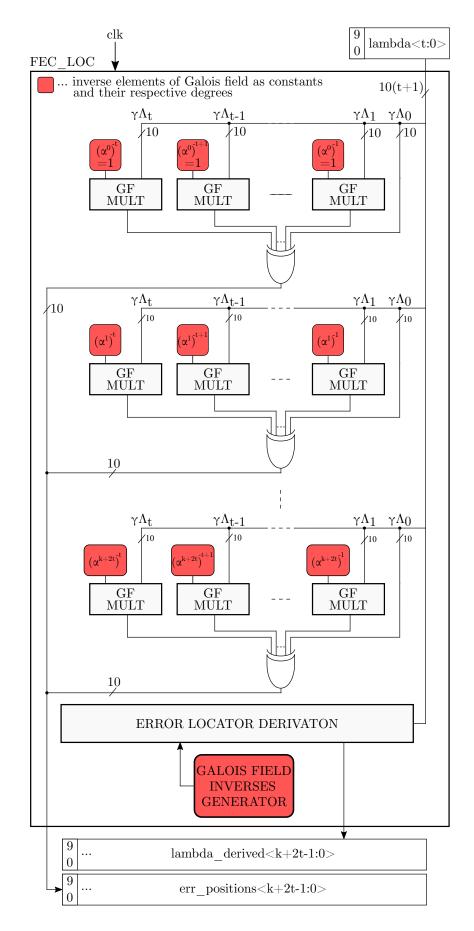

Komponenta Chien search řeší výpočet lokátoru chyb hrubou silou. A to tak, že dosazuje jednotlivé primitivní elementy Galoisova tělesa reprezentující jednotlivé pozice chybového polynomu E(x) a tím hledá, na kterých se bude  $\Lambda(x)$  rovnat nule. Výsledný polynom má tedy stejnou šířku, jako kódové slovo. Komponenta dále počítá derivaci tohoto polynomu  $\Lambda'(x)$ .

Vstupy pro Forneyho algoritmus jsou tyto dva polynomy z Chien search včetně polynomu  $\Omega(x)$  z Euklidova procesoru. Úkolem této komponenty je výpočet zlomku, přičemž v čitateli je  $\Omega(x)$  a ve jmenovateli  $\Lambda'(x)$ , což vyžaduje pro polynom stupně n-1 využití velkého množství logických zdrojů v FPGA. A dále součin s náležitým inverzním prvkem Galoisova tělesa. V první implementaci funkční verze Forneyho algoritmu se ukázalo, že uložení různých stupňů inverzních prvků Galoisova tělesa do ROM vyústilo v dlouhou dobu fáze propojování (anglicky fáze Route), a proto bylo nutné provádět výpočet těchto mocnin přímo v hardwaru.

Jelikož navržené komponenty splňují požadavky pro časování, avšak využívají velké množství logiky, práce se bude v budoucnu orientovat směrem ke snížení využití logických zdrojů v FPGA, zejména Look-up tabulek plnící funkci paměti ROM, které jsou kritickým bodem v současného návrhu. Řešení by mohl přinést přístup sdílení jak konstantních elementů ROM paměti mezi komponentami systému RS-FEC, tak registrů, zejména v Euklidově procesoru. Vhodným řešením pro minimalizaci využití zdrojů ve Forneyho algoritmu může také přinést přístup selekce jednotlivých t chybových pozic v komponentě Chien search, čímž se Forneyho vzorec použije místo n-krát pouze t-krát. Toto však bude vyžadovat vytvoření odpovídající logiky a zpoždění výpočtu o jeden hodinový takt.

### DECLARATION

I declare that I have written the Master's Thesis titled "RS-FEC layer implementation for 400 Gb/s Ethernet" independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the thesis and listed in the comprehensive bibliography at the end of the thesis.

As the author I furthermore declare that, with respect to the creation of this Master's Thesis I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation  $\S$  11 of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll., Section 2, Head VI, Part 4.

Brno .....

author's signature

### ACKNOWLEDGEMENTS

I would like to express my gratitude to the thesis supervisor *Ing. Petr Vyroubal, Ph.D.* at the Faculty of Electrical Engineering and Communication at the Brno University of Technology (BUT) for his availability and leadership in the right direction. The key contribution to the existence of this thesis is thanks to *Ing. Jîří Matoušek, Ph.D.* at the Faculty of Information Technology BUT for his trust and assigning this topic to me which evoked a constant enthusiasm in me. I also want to thank to my thesis advisor *Ing. Štěpán FriedI* at the academical institution Cesnet s. z. p. o. for his professional guidance and his availability.

Finally, I am also very grateful for the support of my dear family and my dear friends, especially to *Bc. David Houška*, for providing me support and encouragement through the process of development, research and writing this paper. Thank you for such a wonderful contribution.

# Contents

| In       | Introduction 17 |         |                                                           |    |

|----------|-----------------|---------|-----------------------------------------------------------|----|

| 1        | The             | eoretic | al Part                                                   | 18 |

|          | 1.1             | Brief   | History of Ethernet                                       | 18 |

|          | 1.2             | OSI R   | Reference Model                                           | 19 |

|          | 1.3             | Forwa   | ard Error Correction and Current State of Ethernet Speeds | 21 |

|          | 1.4             | Progra  | ammable Logic Devices Fabrication                         | 23 |

|          | 1.5             | Field   | Programmable Gate Arrays                                  | 26 |

|          |                 | 1.5.1   | Pipelining                                                | 28 |

|          |                 | 1.5.2   | Typical Applications                                      | 31 |

|          | 1.6             | Intel®  | Stratix <sup>®</sup> 10                                   | 32 |

|          | 1.7             | Reed-   | Solomon Error Correction Codes                            | 33 |

|          |                 | 1.7.1   | Galois Field                                              | 34 |

|          |                 | 1.7.2   | Galois Field Mathematics                                  | 34 |

|          |                 | 1.7.3   | The Code Generator Polynomial                             | 36 |

|          | 1.8             | Reed-   | Solomon Encoder                                           | 36 |

|          | 1.9             |         | Solomon Decoder                                           |    |

|          |                 | 1.9.1   | The Syndromes                                             | 38 |

|          |                 | 1.9.2   | The Set of Syndrome Equations                             | 39 |

|          |                 | 1.9.3   | The Error Locator Polynomial                              | 39 |

|          |                 | 1.9.4   | The Euclidean Algorithm                                   | 40 |

|          |                 | 1.9.5   | Chien Search                                              | 41 |

|          |                 | 1.9.6   | Forney's Equation                                         |    |

|          |                 | 1.9.7   | RS-FEC Error Correction Capability                        | 42 |

| <b>2</b> | Pra             | ctical  | Part                                                      | 44 |

|          | 2.1             | Motiv   | ation                                                     | 44 |

|          | 2.2             | RS-FI   | EC Layer Concept and Galois Field Construction            | 44 |

|          |                 | 2.2.1   | Reed-Solomon Encoder                                      | 48 |

|          |                 | 2.2.2   | Symbols Distribution                                      | 49 |

|          |                 | 2.2.3   | Reed-Solomon Decoder                                      | 52 |

|          |                 | 2.2.4   | Testing                                                   | 64 |

|          |                 | 2.2.5   | Implementation                                            | 65 |

|          | 2.3             | Discus  | ssion and Reflection                                      | 71 |

| Sι       | ımm             | ary     |                                                           | 72 |

| Bi       | ibliog          | graphy  |                                                           | 73 |

# List of Figures

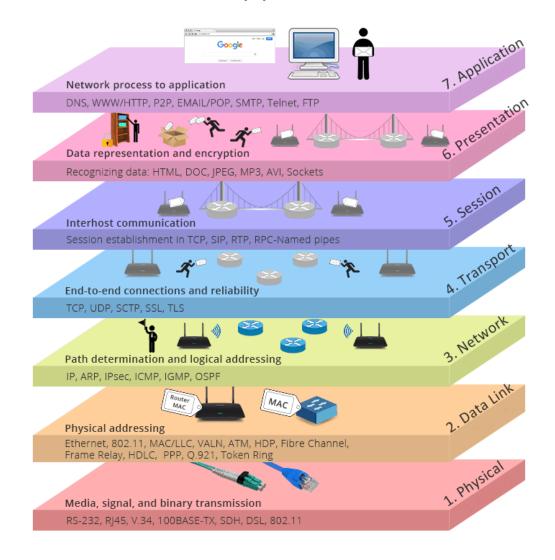

| 1.1  | Seven layers of OSI Reference model (taken from [5])                                                                                        | 19 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

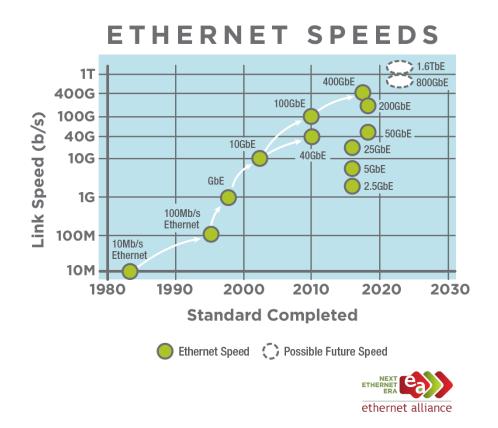

| 1.2  | Graph of current state and future projections of Ethernet speeds                                                                            |    |

|      | $(taken from [6]) \dots \dots$        | 21 |

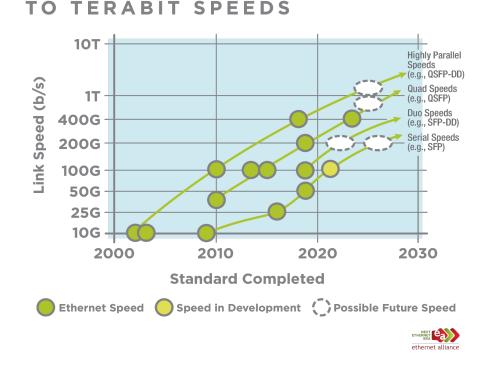

| 1.3  | Current state and future projections of standards completion for var-                                                                       |    |

|      | ious forms of Ethernet (taken from [6])                                                                                                     | 22 |

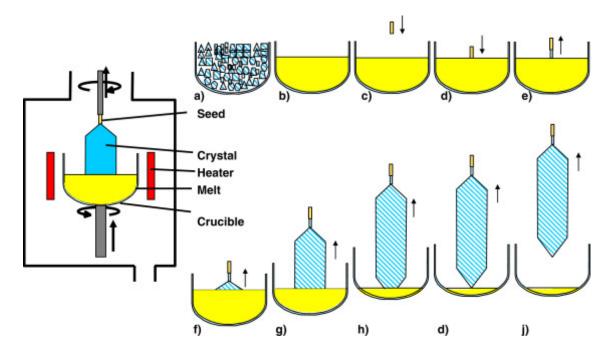

| 1.4  | Process of Czochralski crystal pulling: (a) melted polycrystalline sil-                                                                     |    |

|      | icon (b) in a crucible. (c, d) Seeding procedure: The seed crystal                                                                          |    |

|      | dipped into the melt, followed by Dash necking (e), shouldering (f),                                                                        |    |

|      | cylindrical growth (g), growth of end cone (h), lift off (i), cooling and                                                                   |    |

|      | removing the crystal (j) (taken from [7])                                                                                                   | 23 |

| 1.5  | Illustration of the process of Chemical Vapour Deposition (CVD)                                                                             |    |

|      | (taken from [8])                                                                                                                            | 24 |

| 1.6  | Process of transferring a pattern onto a substrate. (a) Coating the                                                                         |    |

|      | substrate with a photosensitive material; (b) alignment of the mask                                                                         |    |

|      | and exposure to the UV light source; (c) spraying the photoresist                                                                           |    |

|      | to remove the extra photoresist defined by the mask patterns (taken                                                                         |    |

|      | from $[9]$ )                                                                                                                                | 25 |

| 1.7  | Structure of the typical SRAM-based FPGA (taken from [10])                                                                                  | 27 |

| 1.8  | High-level structure of the typical SRAM-based FPGA (taken from                                                                             |    |

|      | [10]).                                                                                                                                      | 27 |

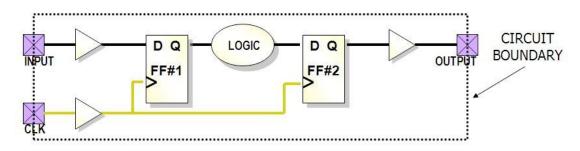

| 1.9  | Basic concept of a sequential circuit (taken from $[11]$ )                                                                                  | 29 |

| 1.10 | Structure of Tri-gate 3D Fin-Fet by Intel <sup>®</sup> (taken from [[12]]) $\ldots$                                                         | 32 |

| 1.11 | RS code definitions (taken from $[3]$ )                                                                                                     | 34 |

| 1.12 | RS-FEC error correction capability breakdown (taken from $[13])$                                                                            | 42 |

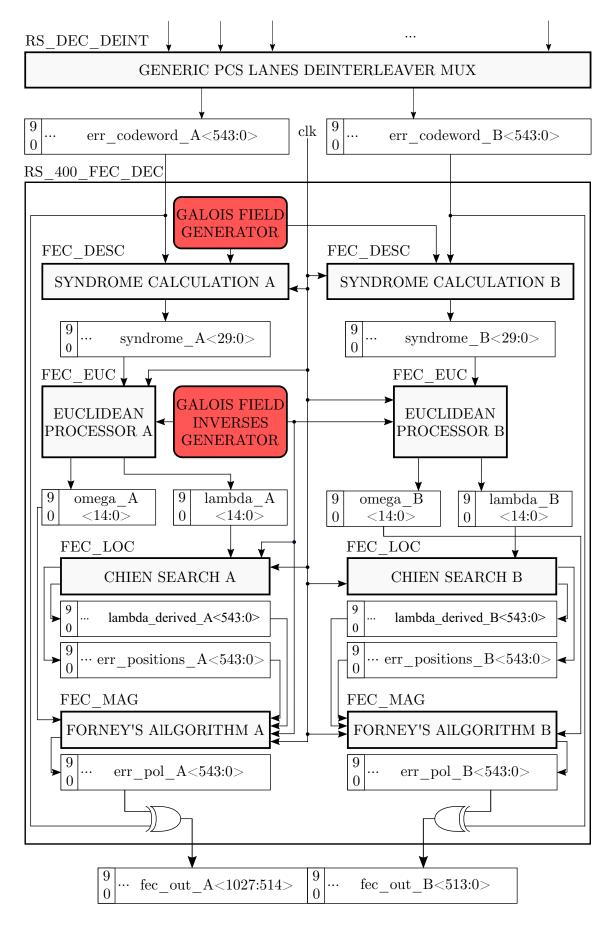

| 2.1  | Diagram of RS-FEC concept                                                                                                                   | 45 |

| 2.2  | Galois field multiplier                                                                                                                     | 47 |

| 2.3  | Numerical representation of RS-FEC Encoder operation (taken from                                                                            |    |

|      | $[3]) \ldots \ldots$ | 49 |

| 2.4  | RS-FEC Encoder hardware diagram for polynomial division $\ . \ . \ .$                                                                       | 50 |

| 2.5  | RS-FEC Transmitter diagram for 400GBASE                                                                                                     | 50 |

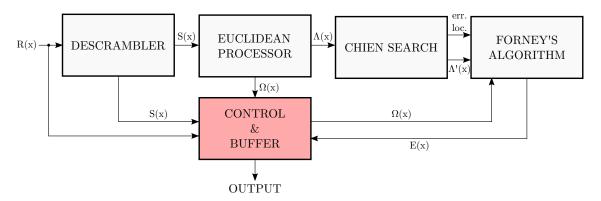

| 2.6  | Diagram of the RS-FEC Decoder                                                                                                               | 53 |

| 2.7  | Sequential solution for a single RS-FEC decoder $\hdots$                                                                                    | 54 |

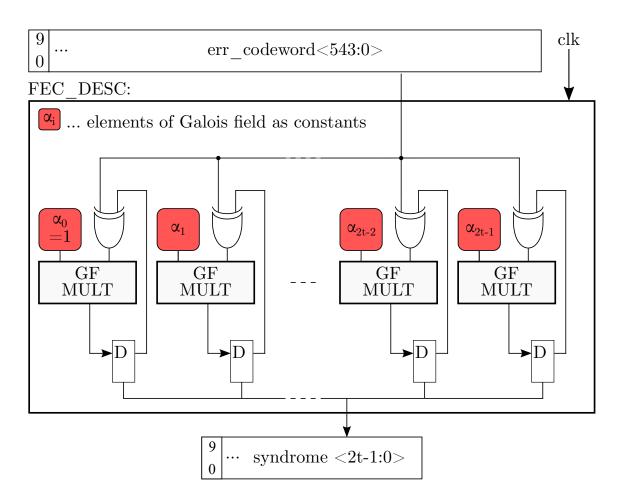

| 2.8  | Hardware of descrambler for syndromes calculation $\ldots \ldots \ldots \ldots$                                                             | 55 |

| 2.9  | Numerical representation of syndrome calculation operation $\ldots \ldots$                                                                  | 56 |

| 2.10 | Eample of first layer of Euclidean processor operation $[3]$                                                                                | 57 |

| 2.11 | Example of remaining layers of Euclidean processor operation $[3]$                                                                          | 58 |

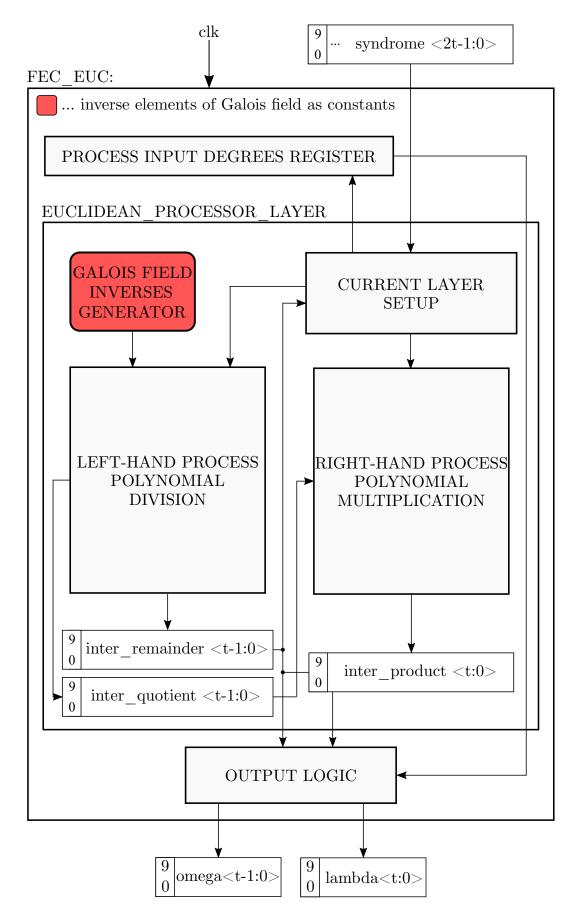

| 2.12 | Diagram of Euclidean processor unit for RS-FEC                                                                                              | 59 |

| 2.13 | Diagram of Chien search as the unit for error positions determination    | 61 |

|------|--------------------------------------------------------------------------|----|

| 2.14 | Diagram of Forney's algorithm as a unit for error polynomial calculation | 63 |

| 2.15 | Hardware for error correction                                            | 64 |

| 2.16 | Testing of the RS-FEC system                                             | 65 |

# List of Tables

| 1.1  | RS-FEC (544, 514) for $200 \text{GE}/400 \text{GE}$ Specifications (taken from [14])     | 22 |

|------|------------------------------------------------------------------------------------------|----|

| 1.2  | Positives and downsides of FPGAs (taken from [15])                                       | 30 |

| 1.3  | Applications of FPGAs for High Performance Servers (taken from [16])                     | 31 |

| 1.4  | Applications of FPGAs for High Performance Embedded Computers                            |    |

|      | (taken from $[16]$ )                                                                     | 32 |

| 2.1  | Example of primitive elements and inverses of $GF(2^m)$ where $m=4$                      |    |

|      | (taken from [3]) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 46 |

| 2.2  | Coefficients of the generator polynomial $G_i$ (taken from [17])                         | 48 |

| 2.3  | Duration of compilation stages of RS-FEC Encoder for $RS(544,514)$ .                     | 67 |

| 2.4  | Duration of compilation stages of RS-FEC Descrambler for $RS(544,514)$                   | 67 |

| 2.5  | Results of synthesis and implementation of time-constrained sequen-                      |    |

|      | tial RS-FEC Encoder for 400GE                                                            | 68 |

| 2.6  | Results of synthesis and implementation of time-constrained sequen-                      |    |

|      | tial RS-FEC Descrambler for 400GE                                                        | 68 |

| 2.7  | Duration of single stages of compilation of both components of Eu-                       |    |

|      | clidean processor                                                                        | 68 |

| 2.8  | Results of synthesis and implementation of a single sequential com-                      |    |

|      | ponent RS-EUC for 400GE                                                                  | 69 |

| 2.9  | Duration of single stages of compilation of both components for find-                    |    |

|      | ing error locations                                                                      | 69 |

| 2.10 | Results of synthesis and implementation of both components RS-CHS                        |    |

|      | for 400GE                                                                                | 69 |

| 2.11 | Duration of compilation stages of a single entity of RS-FOR conduct-                     |    |

|      | ing Forney's algorithm                                                                   | 70 |

| 2.12 | Results of synthesis and implementation of a single time-constrained                     |    |

|      | sequential entity RS-FOR for 400GE                                                       | 70 |

# Introduction

In recent decades, since the communication technologies have become widespread, all the industry sectors and businesses require increasing amount of data to remain agile and innovative. Technologies ensuring real-time data processing and fast data transferring became an essential part of the world today. On the other hand, while talking about large data transferring, such changing dynamics of public demands requires also high stability of data transfer. Therefore, one of the the main purposes of Reed Solomon Forward Error Correction (RS-FEC) algorithm is to ensure error-free digital data transfer. Thanks to the RS-FEC layer, balance between high performance, efficiency and reliability of digital data transfer can be achieved to reduce noise effects not only in high-speed Ethernet platforms [18, 19]. In particular, this system will be employed within a new NDK platform (Netcope Development Kit) which is currently in development at the academic organisation Cesnet, z. s. p. o.

Error correction methods are used on daily basis by all of us. For instance, by putting emphasis on whether an information sent has been successfully received and processed, simply by repeating the message over and over again. This repetition is a form of the error correction encoding. The principle is similar in RS-FEC, based on attaching redundant parity-check symbols to the message sent to the encoder part of the error correction system. Therefore, the system uses this redundancy for erroneous data correction at the error correction decoder. The purpose of adding the decoder part (the error correction capability) is also to avoid decoding some other message [19]. The principle of error correction coding within the RS-FEC layer is based on attaching parity-check symbols as a redundant part to the message received instead of repeating the whole message again. Subsequently, the decoder, the unit ensuring the confidence level of the system, correctly extracts the original source signal out of the corrupted data on the input of the decoder [19].

Employing RS-FEC layer seemed to be an effective solution for reaching 100 Gbps rates, however, its full error correction capability has still not been fully exploited yet, even for the new 400GE. In terms of the RS-FEC system, the main difference between these two standards is that the new 200/400 Gbps rates operate with two codewords in parallel compared to only single one for 100 Gbps rates. Therefore, the most challenging aspect for successful implementation of this system is to balance and minimize logic resources utilization. The main reason for RS-FEC system implementation into an FPGA as firmware is clearly the capability of conducting hardware operations in an FPGA concurrently enabling high-speed computations, possibly at 400 Gbps rate which is the main topic of this paper [19, 11]. In addition, VLSI design enables its development in a generic form for faster development of future platforms and creating different variants of the system.

# **1** Theoretical Part

In the theoretical part of this work, FPGA technology is briefly described, PLD (Programmable Logic Devices) manufacturing and RS error correction codes is characterized. Also, one chapter dealing with Galois field algebra is included and RS error correction flow from the mathematical point of view is described.

### **1.1 Brief History of Ethernet**

Since its introduction in the early 1980s, Ethernet has become a dominant and popular protocol for Local-Area-Networks (LANs), used mostly in offices. Over the following years, demands for higher data-rates of Ethernet began to rise enormously. The first experimental 2,94 Mbps shared bus-based system was able to transmit with only one station at a time. So called Medium Access Control (MAC) protocol detecting collisions controls the use of the shared bus. Each station is free to transmit MAC frames but if a collision occurs during transmission, it stops for certain amount of time and tries again if the channel is free for transmitting. The first commercially available standards were bus-based systems capable of 10 Mbps operation. There were no changes to the MAC protocol or MAC frame format. But, the innovation was that Ethernet was configured in a star topology which enabled traffic to go through a central hub, however, again with transmission limited through the hub. The need for faster data-rates resulted in the central hub replacement by a switch allowing full-duplex operation. Thanks to this, with the switch and MAC format protocol unchanged, collision detection is no longer needed. Further enhancements to the MAC layer were added through time to improve data rate requirements, such as provision for larger frame size. Ethernet quickly achieved widespread attention and acceptance and became a dominant technology. Not only for LANs, but also Metropolitan-Area Networks (MANs) and spread also to a wide range of applications and environments due to its extraordinary adaptability[20].

The same MAC protocol and frame format are used at all data rates. The main differences among various standardizations for different data transfer speeds are at physical layer in the definition of signal transmission medium of Ethernet [20].

Historical perspective of the first Ethernet platforms did help in the initiation higher speeds of Ethernet development beyond 100GE. The bandwidth explosion was (and still is) driven by increasing number of users, increased access methodologies, access rates and increased number of services (such as social media, video on demand, etc.). From 2000 to 2019 around 3.1 billion individual users were connected to the Internet. [1]. Nowadays, the most data-intensive sectors with the most significant growth rates of data traffic are financial, data-intensive science and peering. Slower growth rates have been estimated for cable users and end-stations, such as IP traffic and servers I/O. [21].

## 1.2 OSI Reference Model

The very first primary definition of modern networking was approved by the International Organisation for Standardisation in 1984. The OSI (Open Systems Interconnection) Reference model can be perceived as a core of serial networking technologies, including industrial Ethernet. It is a layered description of data transfer among devices within a network [22].

Fig. 1.1: Seven layers of OSI Reference model (taken from [5])

The uppermost layer, number 7, is called *Application Layer* and is the closest to end users. It directly interacts with users' software applications to provide desired communication functions [22].

Layer 6 is called *Presentation Layer* which provides end user data translation to network format so that lower layers can accept the data [22].

Session Layer is the fifth layer which manages connections between respective remote and local computers and also terminates connections between them. It also conducts data verification procedures if data have been delivered correctly or not [22].

Layer 4 is called *Transport Layer* ensuring complete delivery of data usually by using error correction functions or by other means. Sequences of data from are being transferred from a source to a destination host via network [22].

Layer 3, *Network Layer*, creates logical paths using switching functions for data transmission from node to node so that network can be formed from the node of the transmitter side to the address node of the desired destination. [22].

Layer 2, so called *Data Link Layer* (DLL) allows direct node-to-node data transfer. On this level, data are packed into frames based on Point-to-Point Protocol and encoded into single bits and further unpacked. The layer is divided into two sublayers: *MediaAccessControl* (MAC) controls which device in a network will be permitted to transmit data to a media. The second sublayer is *LogicalLinkControl* (LLC) conducting frame synchronization, network layer protocols identification. LLC is also used to control data flow and checks for errors [22].

The very bottom layer is *Physical* (PHY) which is responsible for conveying unstructured raw data bitstream at the electrical level and defines the physical specifications of the data connection, such as optical fibre specifications, operation voltages of an electrical fibre, layout pins of the connector etc. PHY and MAC layers are interconnected via MII interface [22].

Conventional Ethernet PHY consists of three additional sublayers: Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA) and Physical Media Dependent (PMD) sublayer. PCS is responsible for interfacing to the higher layer MAC through MMI (Media-Independent Interface) interface. PMD sublayer specifies optoelectronic components and, if required, implements digital signal processing on the transmitted and/or received signal. PMA sublayer conducts multiplexing of n physical lanes to x PCS lanes and backwards [17, 23].

# 1.3 Forward Error Correction and Current State of Ethernet Speeds

The very first implementations of RS (Reed-Solomon) error correction algorithms were first available since the Voyager deep space communication system in the 1977. [19, 11]. Nowadays, RS codes can be found in various applications, such as radio and television transmissions, disk storage, high-speed computer memory I/O and data communication technologies. For instance, high-speed Ethernet. FEC was first introduced for backplane and then, to deliver more economical optical transceivers and cable technologies, for a few front-panel use, such as copper cabling for 100GE, 50GE and 25GE for the purpose of error-free data transmissions, however, for the penalty of carrying additional bits for the FEC mechanism to encode, transmit, decode and correct the data packet re-transmissions [14].

Fig. 1.2: Graph of current state and future projections of Ethernet speeds (taken from [6])

In recent years, Ethernet protocol is undergoing significant development. It is capable of achieving 100GE, 200GE and 400GE speeds. Trends of current speeds of Ethernet are shown in figures 1.2 and 1.3 [14, 6].

Fig. 1.3: Current state and future projections of standards completion for various forms of Ethernet (taken from [6])

The FEC system is required for such high throughput because optical transceivers, electrical interfaces and cables are noisy signalling environments. So the bit error rate (BER) which these electronics generate itself require an algorithm-based error-correction method. RS-FEC uses an approach of finite-sized block of bits known as a block code. In Ethernet it is called a message. RS-FEC is a cyclic type of FEC despite it works as a linear code, meaning with fixed block of bits where a FEC symbol is 10 bits in size. It is known also as RS 544 FEC. In the following table 1.1, details of RS-FEC for Ethernet implementations are summarized [14]:

| Symbols                | Explanation                                                  |

|------------------------|--------------------------------------------------------------|

| 514                    | Total number of symbols in a codeword                        |

| $514 \cdot 10 = 5,440$ | Bits in the codeword or block                                |

| 544 - 514 = 30         | Number of check symbols per codeword or block                |

| $514 \cdot 10 = 5,140$ | Number of bits referring to the size of the information bits |

| $514 \cdot 10 = 5,140$ | per block                                                    |

| (544-514)              | Maximum number of symbols which can be corrected in          |

| 2                      | a codeword or in a block                                     |

Tab. 1.1: RS-FEC (544, 514) for 200GE/400GE Specifications (taken from [14])

# 1.4 Programmable Logic Devices Fabrication

FPGA chips belong to the family of active semiconductor devices. Such devices require extremely pure silicon and germanium in lesser extent. Intrinsic silicon is much more difficult to prepare than intrinsic germanium. The pure form of silicon needs about  $1.5 \cdot 10^{10}$  of intrinsic carriers per cm<sup>3</sup> and  $2.4 \cdot 10^{13}$  per cm<sup>3</sup> for germanium. Silicon is obtained from silicon dioxide or silicon tetrachloride by normal metallurgical processes and needs to be further purified until the number of foreign atoms is less than 1 in  $1 \cdot 10^{10}$  per cm<sup>3</sup> to create silicon pure enough for semiconductor devices. The most frequent method is the Czochralski crystal pulling, shown in figure 1.4 [7]. This method is based on seed crystal insertion into a bath of molten silicon.

Fig. 1.4: Process of Czochralski crystal pulling: (a) melted polycrystalline silicon (b) in a crucible. (c, d) Seeding procedure: The seed crystal dipped into the melt, followed by Dash necking (e), shouldering (f), cylindrical growth (g), growth of end cone (h), lift off (i), cooling and removing the crystal (j) (taken from [7])

A single silicon crystal of 10 to 15 cm with required impurities can be obtained by being withdrawn from the molten bath. In the next step the cooled crystal is being divided into 1 mm thick slices along the crystallographic direction of the crystal in order to avoid internal structure disruption of the crystal. Resulting slice is approximately 0,2 mm thick after the etching and polishing procedures removing surface damage after the step of slicing. This is the key step for further epitaxial layer growth with the same orientation on to the underlying sliced silicon surface [24]. In the next step, ion implantation to the pure silicon crystal lattice with impurities is performed. In this step, the energy of accelerated ion implants up to 300 keV, determining the depth of implanting, are bombarded into the silicon substrate [24].

Next and the most important stage of the integrated circuit fabrication process is epitaxial deposition. It involves an epitaxial layer growth on the slice of the silicon dioxide. The layer is grown in the atmosphere of silicon tetrachloride and hydrogen respectively with strictly controlled conditions. A perfect crystal is the key requirement for correct outputs of subsequent stages [24].

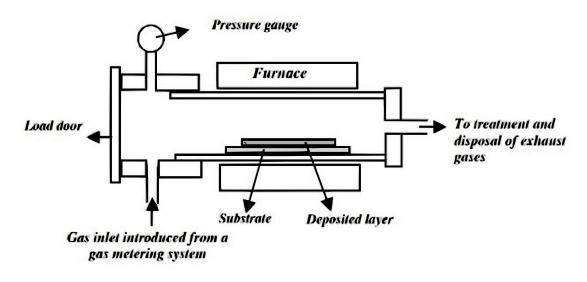

The first stage after the epitaxial deposition is oxidization which is used two or three times in order to create a mask for the impurity atoms diffusion after selective etching. One method of oxidization used for oxide layer creation of high quality physical properties is based on passing oxygen over the surface of silicon slice at a temperature of 1200 °C, as illustrated in 1.5. As the result, passivizing layer with uniform thickness of  $5 \cdot 10^{-7}$  m is created. Oxide layers have been used also as elements in active and passive devices and silicon functional blocks. Oxide layer becomes important especially during planar and epitaxial planar transistors manufacturing. The reason is very low leakage currents currents due to the junctions formed under A layer of silicon oxide. In this way, 10 silicon slices with 200 monolithic circuits in each would be produced [24]. Next step is photo-engraving process

# Uniform coating layer Thickness: 2–100 µm

Fig. 1.5: Illustration of the process of Chemical Vapour Deposition (CVD) (taken from [8])

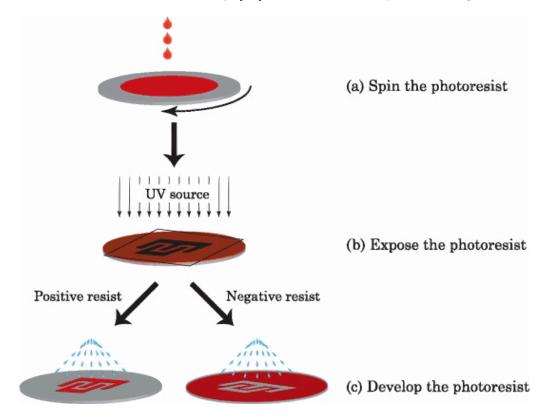

which involves two operations: photographic mask preparation and the etching of the

silicon dioxide. The purpose of this step is to cut off windows allowing the diffusion of subsequent stages to take place. Next step is the photographic mask production. Each one comprises of large number of identical elements, each of which is the original mask layout. Due to the photographic equipment limitations, sequence of stages for reduction are required. A typical sequence involves artwork originals preparation, photographic reduction, step-by-step contact printing and rephotographing. Subsequently, when the photographic mask has been prepared, with photo etching the processing of the slice may be started, illustrated in figure 1.6. The former part, the centrifugal force spreads the liquid photoresist dropped on a rotating surface of the slice at 800 rpm and subsequently is let to dry in an oven. In the latter part, as the photoresist is placed in the exact position required and subsequently exposed to UV (Ultraviolet) light. The UV light causes the photoresist to polymerize with the opaque layer. The rest of the photoresist forms a layer resistant to hydrofluoric acid used to etch the silicon base away [24]. The further step of of integrated circuit

Fig. 1.6: Process of transferring a pattern onto a substrate. (a) Coating the substrate with a photosensitive material; (b) alignment of the mask and exposure to the UV light source; (c) spraying the photoresist to remove the extra photoresist defined by the mask patterns (taken from [9]).

fabrication is diffusion which consists of combination of epitaxial deposition and

diffusion. The diffusion process takes place within the holes etched in the silicon dioxide. During the process of diffusion the time and concentration of the impurities must be accurately controlled in order to obtain specific diffusion depths according to the required transistor design. The choice of an element of diffusant must meet the requirement for easy diffusion into the intrinsic silicon but not into the silicon dioxide. For instance, boron and phosphorus are the usual diffusants. The next step, the process of evaporation is to be conducted which is important for ohmic contact production and interconnections realization. This process takes place in vacuum with golden, nickel or also aluminium rods being evaporated. As the result, a thin layer over the entire surface is produced. The main issue of the process is to avoid changing the desired nature of the semiconductors when alumina is added. Therefore, with masking and etching only the desired alumina configuration remains to form the contacts and interconnections [24].

As a slice of semiconductor has been developed, the very last step is cutting into individual circuits and packaging. Cutting can be performed by using a diamondtipped tool by drawing it across the edge of the surface of the slice. Subsequently, by breaking each part separate chips are produced. Individual chips are ready for mounting and encapsulation [24].

### 1.5 Field Programmable Gate Arrays

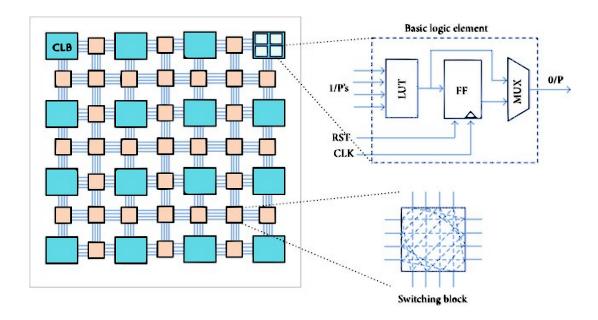

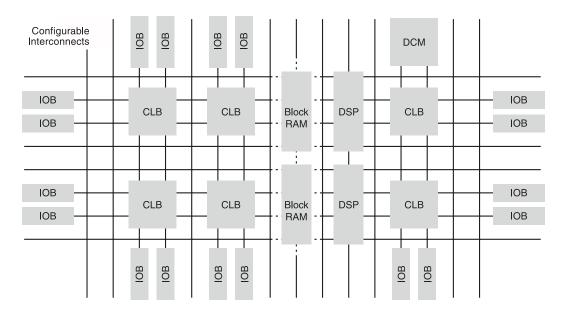

Typical hierarchical structure of modern FPGA chips consists of programmable logic blocks further containing pool of combinatorial logic blocks and flip-flops to be used in an intended design. These logic elements are often combined with memory, typically with various amount of SRAM (Static Random Access Memory) inside an FPGA chip. This typical architecture is shown in the figure 1.7 which contains so called CLB (Configurable Logic Block) units interconnected within a matrix-like grid and surrounded by programmable interconnect. Each CLB typically consists of a set of so called BLE (Basic Logic Element) units. Inside a single BLE there is an element allowing logical function implementation called LUT (Look-up table) [11, 10, 25].

More detailed view on a typical high-level hierarchical structure of an FPGA is shown in figure 1.8. CLBs form a large array including BRAMs (Block RAMs) and DSP (Digital Signal Processing) blocks, similar to arithmetic logic units (ALU) of a processor which can be programmed accordingly to perform arithmetic logic operations, such as add, multiply, subtract, compare, etc. Depending on the type of operators required, both CLBs and DSPs can perform integer, floating point or/and bitwise operations. Results of these operations are stored in registers present in

Fig. 1.7: Structure of the typical SRAM-based FPGA (taken from [10]).

CLBs, DSPs or/and BRAMs. These blocks can be connected via flexible configurable interconnects which are based on user design. The output of one operator can directly flow into the input of the next operator [16].

Fig. 1.8: High-level structure of the typical SRAM-based FPGA (taken from [10]).

The architecture then enables to create a massive array of application-specific ALUs which allow both instruction and data-level parallelism. Compared to processor units, there are no inefficiencies, such as processor cache, but data within an FPGA can be directly streamed between operators. These operators can be configured to have point-to-point dedicated interconnects, thereby setting them to pipelined configuration. For instance, throughput on integer operations are in order of Tera-operations per second, on floating point operations in order of gigaflops per second [16].

Another great advantage of FPGAs is that they can be easily interfaced to other chips or external signals by so called input/output blocks (IOBs) (see figure 1.8) behind the chip pads. So that each pad can serve as an input or an output or both. In particular, IOBs are designed to support various memory and processorinterface standards, such as support of multiple DDR3 (Double Data Rate Type 3), DDR4 (Double Data Rate Type 4) and more memory controllers, various generations of PCI Express<sup>®</sup> (Peripheral Component Interface), Intel's Front Side Bus (FSB), Quick Path Interconnect (QPI) protocols. Support for these processor interfaces and protocols enables computing applications running on FPGAs to interact with processor and accelerate the desired applications [16].

FPGA vendors also include hardwired IP (Intellectual Property) nonprogrammable cores inside the chips supporting commons recurrent functions in many designs[11]. These include general-purpose processors, high-speed serial interfaces, arithmetic blocks and Ethernet MAC (Medium Access Control) [11].

### 1.5.1 Pipelining

Clock conditioning has become also a common feature in FPGAs. Digital circuits can be also supplied by a clock signal which is, ideally, a simple square wave oscillating at a certain fixed frequency. The most basic concept of a sequential system in an FPGA chip contains number of combinatorial logic blocks in between arrays of clocksensitive components called flip-flops where current state of outputs of combinatorial blocks depends on current state of inputs to these combinatorial blocks. These are generally made of all logic functions with any level of intended complexity realized by logic gates including interconnection among them. This involves also multiplexors, encoders and decoders [11].

For instance, a D-type flip-flop (DFF). Every time there is a rising edge of the clock signal, it allows desired signals to propagate from its input D to its output Q. In this particular moment the input D is connected to the output Q in a single DFF. However, apart from this specific time D is disconnected from Q [11].

An important requirement for the resultant sequential system is that signals between the output Q of the first flip-flop and the input D of the next one must remain stable by the time the next clock cycle rising edge. It is therefore required to ensure the worst case propagation delay between these delay elements of the design. This also applies for all subsequent DFFs. Nowadays, this timing check is automated so that the designer needs to be concerned with the specification of the logic behaviour of the circuit [11].

Fig. 1.9: Basic concept of a sequential circuit (taken from [11])

This technique is generally known as pipelining. Data throughput is one of the most important parameters not only in this work. The purpose of pipelining is to satisfy throughput requirements also with minimum resource penalty. Algorithms which can be performed in parallel with sequential delay elements (such as DFFs) result in higher throughput, such as in digital processing (DSP) applications, multicore CPU (Central Processing Unit) parallel platforms, many-core GPU (Graphics Processing Unit) and FPGAs compared to traditional single-core systems. Among all these parallel platforms, FPGA-based systems allow the highest flexibility for programming parallel cores. This can be achieved thanks to the high-level synthesis which significantly increases productivity, reduces time-to-market window and helps to implement efficient parallel hardware of complex register transfer level (RTL) designs. The objective of the synthesis is to find a suitable performance solution for a design with given available resources [26].

Pipeline optimization strategy is based on partitioning this large scale designs into smaller data processing elements connected in series while each element (combinatorial block) executes its operation in parallel in a time-sliced mode. This requires some buffer storage (pipeline registers). The registered output of one element becomes the input of the next one. The time between each clock signal is set to be greater than the longest delay between pipeline stages, so that when the registers are clocked data written to the following registers are results of the previous stage of the pipeline. Pipelined systems also requires more resources then the combinatorial logic elements because each pipeline stage cannot reuse resources of other stages [26].

The key pipeline parameters are number of pipeline stages, latency, clock cycle time, delay, throughput and turnaround time. A pipeline synthesis can be constrained by resources or time, or combination of both. A resource-constraint synthesis pipeline limits the area on chip or available number of functional units on target device. A time-constraint pipeline synthesis puts more effort to required throughput and turnaround time. Finding a solution which consumes minimum resources is the task for the so called scheduler [26]. Reasons why FPGAs are chosen as promising platforms for high-performance data-intensive applications are summarized in table 1.2 including their drawbacks [15, 16]. Compared to GPUs and other multicores which consume power in hundreds of watts, FPGAs power consumption lies in the range of tens of watts [27] [16].

| Advantages                                                                                                                                                                                                                | Disadvantages                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Massive parallelism of compute opera-<br>tions which can be put to more optimal<br>configurations                                                                                                                         | Processing data with constrained cost and resources.                                                                                                                                    |

| Flexibility in terms of involvement of<br>different kinds of components (hard<br>cores, IP, memory, LUT structure of<br>the programmable fabric). Second,<br>ability to field reprogram parts or the<br>entire FPGA chip. | Not clear what should stay as soft-<br>ware part and what hardware part of<br>a desired complex system. Interfacing<br>between these two approaches requires<br>additional development. |

| Flexibility in terms of an ability to field<br>reprogram parts or the entire FPGA<br>chip.                                                                                                                                | Low efficiency of data movement around the chip.                                                                                                                                        |

| Small amount of distributed mem-<br>ory incorporated into the fabric which<br>brings the memory closer to the pro-<br>cessing                                                                                             | IP library is required for FPGA-based systems development.                                                                                                                              |

| Low power solution enabling more pro-<br>cessing than GPUs for quarter of power<br>required                                                                                                                               | Design entry methodology is lacking<br>more restricted approach to harness the<br>flexibility of the hardware.                                                                          |

| Scalability in terms of creating a chain<br>of FPGA chips together while the algo-<br>rithm is larger than the single one.                                                                                                | Strict rules of what is synthetizable and<br>what is not.                                                                                                                               |

| Nowadays, custom chips deliver more<br>data throughput per dollar.                                                                                                                                                        | Innovation is required in the area<br>of high-performance interfacing to get<br>large amount of data onto the chip.                                                                     |

Tab. 1.2: Positives and downsides of FPGAs (taken from [15])

The major reason for lower power consumption in FPGAs is that these devices operate in range of 100-300 MHz compared to processors executing operations usually between 2-3 GHz. Recently, in terms of high-end FPGA devices such as Intel<sup>®</sup> Stratix<sup>®</sup> DX, programmable clock-tree performance reaches around 1GHz [27] [16].

### 1.5.2 Typical Applications

In the mid-2000s the high performance computing industry (HPC) demand caused course of General-purpose CPU vendors to shift from single-core CPU-based systems orientation to multicore architectures to meet high-performance demands of the industry. The reason for this is that if frequency of single-core processors increases, power dissipation rises to impractical levels. The result of this is that it enables to exploit CPU performance by adopting parallel designs enabling previously unattainable performance levels [16].

There is a broad spectrum of applications where FPGAs embedded inside equipment or forming a massive compute server farms play major role. In table 1.3 applications for High Performance Servers are shown. These applications are in constant need of compute power. The greater the computation power, the more complex algorithms can be implemented to produce more accurate results [16]. In table 1.4

| Industry                     | Sample Applications                                  |

|------------------------------|------------------------------------------------------|

|                              | Climate modelling, nuclear waste simulation, war-    |

| Government labs              | fare modelling, disease modelling and research, air- |

|                              | craft and spacecraft modelling                       |

|                              | Video, audio, data mining, analysis for threat       |

| Defense                      | monitoring, pattern matching, image analysis for     |

|                              | target recognition                                   |

| Financial services           | Options valuation, risk analysis of assets           |

| Geo-sciences and engineering | Seismic modelling and analysis, reservoir simula-    |

| Geo-sciences and engineering | tion                                                 |

| Life sciences                | Gene encoding and matching, drug modelling and       |

| Life sciences                | discovery                                            |

Tab. 1.3: Applications of FPGAs for High Performance Servers (taken from [16])

sample applications for High-Performance Embedded Computers are shown. All industries mentioned require certain specific equipment for compute-intensive and data-intensive tasks. In the past, these systems were based on custom integrated circuits designed for high memory rates and to handle data-intensive processing [16].

| Industry             | Sample Applications                                      |

|----------------------|----------------------------------------------------------|

| Defense              | Beam forming in radar                                    |

| Airborne Electronics | Image compression and analysis in payload                |

| Communications       | Encryption in network routers                            |

| Medical Imaging      | Image rendering                                          |

| Financial Services   | Low latency and high throughput data processing in trad- |

| T mancial Services   | ing solutions                                            |

Tab. 1.4: Applications of FPGAs for High Performance Embedded Computers (taken from [16])

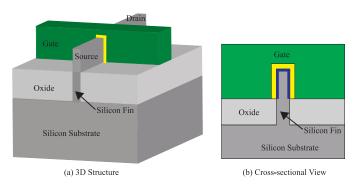

### 1.6 Intel<sup>®</sup> Stratix<sup>®</sup> 10

Since the task of this work is to implement the system RS-FEC into FPGA Intel<sup>®</sup> Stratix<sup>®</sup> 10 DX 2100, this chapter therefore deals with the technology present in Intel<sup>®</sup> Stratix<sup>®</sup> 10 family.

SoC (System on Chip) devices of this family dispose of the Intel HyperFlex FPGA Architecture combined with 14 nm Tri-Gate (3D) process technology (see the structure in the figure 1.10) which replaced the conventional 2D planar MOS-FET transistors so that geometries have been reduced below 20 nm. It contains so called Hyper-Registers present all over the functional blocks within the chip. The advantage of this technology is that all the conventional blocks such as Adaptable Logic Modules ALMs, embedded memory (M20K) and digital signal processing allow to select the optimal register location automatically after place-and-route to maximize core performance without additional changes or added complexity after the place-and-route step of the design process. The next advantage is that such registers reduce routing congestion [25]. Another useful feature of the chip is the

Fig. 1.10: Structure of Tri-gate 3D Fin-Fet by Intel<sup>®</sup> (taken from [[12]])

programmable clock tree synthesis. It reduces timing and skew uncertainty to reach the maximum core clock performance. This feature enables its entire architecture to double its performance compared to its predecessors Stratix V FPGAs. Core clocking also uses intelligent branch which allows to reduce dynamic power dissipation in the clock networks [25].

The Hyper-Aware design flow includes a Fast Forward Compile tool which enables performance exploration and guides the designer to the maximum performance of his solution. A Hyper-Retimer step near the end of the design offers further optimization after place-and-route step. An enhanced synthesis and place-and-route algorithms which use the Hyper-Registers. In the end, it uses 70 % less power than Stratix V FPGAs predcessors. There is an embedded quad-core 64-bit ARM Cortex-A53 processor system included and also components DRAM (Dynamic Random Access Memory), SRAM (Static Random Access Memory) and ASICs in a single package [25].

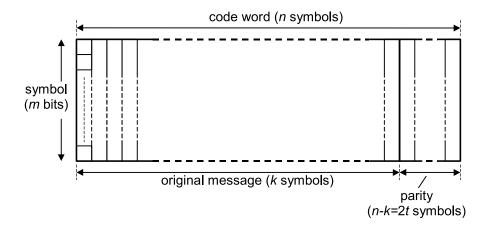

### 1.7 Reed-Solomon Error Correction Codes

Reed-Solomon codes belong to the category of block codes. This means that a message to be transmitted to the divider of n symbols is divided into separate block of data called codeword. The former part of a single codeword is an original message consisting of k information symbols in a message to be transmitted.

In the latter part a parity protection of (n - k) = 2t symbols is added to the original message. The error-correction capability of RS codes is determined by its Hamming distance which is determined by number of parities. For RS codes, its Hamming distance is 2t + 1 and the overall error-correcting capability is [13]:

$$error-correcting \ capability = \frac{Hamming \ distance}{2} \tag{1.1}$$

The variable t specifies the number of symbols the algorithm is able to correct in a block of n symbols of the codeword. This is illustrated in the figure 1.11 [3]. So that each block of information symbols has its own parity protection added as a separate part of the codeword.

In addition, RS code is also a linear code. This means that sum of any two codewords is still a valid codeword [13]. It is also a cyclic code meaning that cyclically shifting the symbols of a codeword produces another one. RS code can be therefore described as an (n, k) code. Different parameters for a code provides different levels of protection and complexity of the implementation changes respectively [3].

There is a significant advantage of RS code. It enables having all bits of a symbol of m in error and it counts as only one symbol error in terms of the correction capacity of the code [3].

Fig. 1.11: RS code definitions (taken from [3])

### 1.7.1 Galois Field

Galois field belongs to the family of finite fields and named after the French mathematician Évariste Galois. A Galois field consists of a set of elements based on a primitive element  $\alpha$  which takes values  $\alpha, \alpha^0, \alpha^1, \alpha^2, \ldots, \alpha^{N-1}$  to form a set of  $2^m$ elements where  $N = 2^m - 1$ . Galois fields are then marked as  $GF(2^m)$ . Each field element can be also represented by polynomial expression [3]:

$$a_{m-1}x^{m-1} + \ldots + a_1x^0, (1.2)$$

where coefficients  $\alpha_{m-1}$  to  $\alpha_0$  take values of 0 or 1. Therefore, it is possible to describe a single field element by the binary number  $\alpha_{m-1}, \ldots, \alpha_1, \alpha_0$ . There is in total  $2^m$  combinations of the m- bit number [3].

### 1.7.2 Galois Field Mathematics

Arithmetic operations with finite field elements differ from conventional mathematics with normal integers, especially while multiplying in a Galois field. Galois field arithmetical operations are addition, subtraction, multiplication and division. The difference is that any arithmetical operation of two field elements always produces another field element [3].

#### Addition and Subtraction

While adding two Galois field elements, two polynomials are added in this form [3]:

$$(a_{m-1}x^{m-1} + \ldots + a_1x^0) + (b_{m-1}x^{m-1} + \ldots + b_1x^0) = c_{m-1}x^{m-1} + \ldots + c_1x^0 \quad (1.3)$$

This operation  $a_i + b_i = c_i$  applies for degrees  $0 \le i \le m - 1$ . The coefficients can only take the values 0 and 1. If  $a_i = b_i$ , then  $c_i$  produces 0. Respectively, if

$a_i \neq b_i$ , then  $c_i$  produces 1. This signifies that addition of two Galois field elements is accomplished by modulo-two addition of their respective coefficients. In binary form, addition is realized by the exclusive-OR function of two binary numbers. Therefore, addition of two identical Galois field elements produces zero. It also implies that any result of subtraction of two Galois field elements from each other is exactly the same as addition. In the end, minus sign can be replaced with plus sign. In other words, if a positive element in an equation is needed to be expressed on the other side of the equation, the sign stands the same [3].

#### **Multiplication and Division**

There is a significant difference between multiplication with standard integers and multiplication in a Galois field. The main difference is that if polynomials of degree m-1 are multiplied, the result is a product polynomial of degree 2m-2 which is not a valid element of  $GF(2^m)$ . With the same approach as with subtraction, for a result of multiplication product modulo is required. In Galois field, the valid field element is obtained by dividing the product product polynomial by a field generator polynomial p(x) in order to "return" the value of the straightforward multiplication of the polynomial back to a valid Galois field element [3].

Division of two field elements of the Galois field is accomplished by multiplying the inverse of the divisor. The inverse element is defined as when the element value is multiplied by the inverse field element, value of 1 is produced [3].

#### The Field Generator Polynomial

The field generator polynomial or primitive polynomial p(x) of degree m defines a specific finite field bound to it. When a different generator polynomial or primitive polynomial is selected, it produces different results. Therefore, one generator polynomial or primitive polynomial must be selected for a single Galois field. The next requirement for a generator polynomial or a primitive polynomial is that it must be irreducible (with no factors of the GF) [3].

Based on the primitive element  $\alpha$  as a root of the field generator polynomial the all non-zero values of Galois field can be generated. So that to obtain the complete field, it means that [3]:

$$p(\alpha) = 0 \tag{1.4}$$

To determine the repeating sequence of the field elements, it is needed to express the highest degree of the primitive polynomial. First, since a GF element is written in the index form, for instance  $\alpha^0$ , it is possible to get next value  $\alpha^1$  by multiplying its entire polynomial  $\alpha^0$  in its polynomial form by  $\alpha$ . Then, the next Galois field value is obtained. It is also important to mention that if the highest degree of the generator polynomial p(x) has been reached this way, it is needed for any member of the polynomial form to substitute this member by the expression of the highest degree of the generator polynomial. In this manner, all  $2^m$  Galois field elements can be obtained by starting with an element with index 0 up to the element  $(2^m - 2)$ . It is also important to highlight that the decimal form of an element is a representation of the respective polynomial form, meaning binary form. For instance, polynomial  $\alpha^2 + 1$  is equal to the representation of bits  $x^2$  and  $x^0$  in log. 1 giving 0101 in the 4-bit binary form. Next important characteristics of the Galois field is that if the maximum is exceeded, it can be found that the index form, for instance for the first element beyond the last one which is  $\alpha^{(2^m-1)}$ , is equal to element  $\alpha^0$ , the next one equals to  $\alpha^1$  and so on and all these values remain valid within the desired Galois field [3].

### 1.7.3 The Code Generator Polynomial

While constructing an RS code, the values of the message parity symbols must be elements of a Galois field. An (n, k) RS code is constructed by the code generator polynomial G(x) involving (n - k = 2t) factors, the roots of consecutive elements of the Galois field. For a code based on m-bit symbols, the Galois field consists of  $2^m$  elements [3]:

$$g(x) = (x + \alpha^{b})(x + \alpha^{b+1})\dots(x + \alpha^{b+2t-1}), \qquad (1.5)$$

where b specifies at which degree the Galois field roots begin.

### 1.8 Reed-Solomon Encoder

The output of the encoding process comprises of two data blocks. The first block is formed by k information symbols and is represented by the message polynomial M(x) of order k-1. This polynomial of information symbols to be encoded can be written as follows [3]:

$$M(x) = M_{k-1}x^{k-1} + \ldots + M_1x + M_0,$$

(1.6)

where k is the number of symbols in a message to be transmitted,  $M_{k-1}$  is the first symbol of the message and each one  $M_{k-1}, \ldots, M_1, M_0$  is an m-bit message symbol, an element of  $GF(2^m)$  [3].