BRNO UNIVERSITY OF TECHNOLOGY

Faculty of Information Technology

# PHD THESIS

Brno, 2017

Ing. Lukáš Mičulka

# BRNO UNIVERSITY OF TECHNOLOGY

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

DEPARTMENT OF COMPUTER SYSTEMS ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

## METHODOLOGY FOR FAULT TOLERANT SYSTEMS DESIGN INTO LIMITED IMPLEMENTATION AREA IN FPGA

METODIKA NÁVRHU SYSTÉMŮ ODOLNÝCH PROTI PORUCHÁM DO OMEZENÉHO IMPLEMENTAČNÍHO PROSTORU NA BÁZI FPGA

PHD THESIS DISERTAČNÍ PRÁCE

AUTHOR AUTOR PRÁCE Ing. LUKÁŠ MIČULKA

SUPERVISOR ŠKOLITEL Doc. Ing. ZDENĚK KOTÁSEK, CSc.

**BRNO 2017**

### Abstract

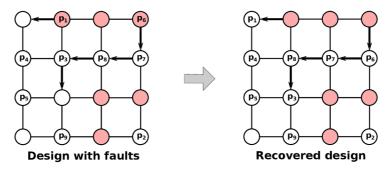

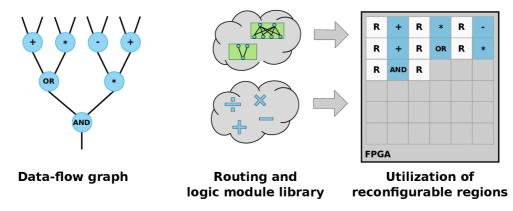

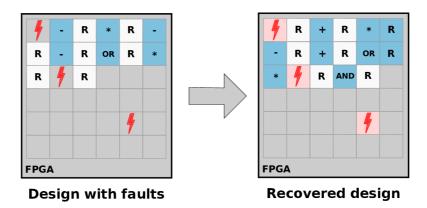

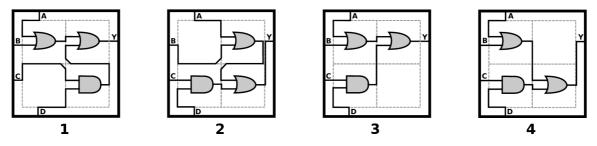

The work presents a methodology of fault tolerant system design into an FPGA with the ability of the transient fault and the permanent fault mitigation. The transient fault mitigation is done by the partial dynamic reconfiguration. The mitigation of a certain number of permanent faults is based on using a specific fault tolerant architecture occupying less resources than the previosly used one and excluding the faulty part of the FPGA from further use. This inovative technique is based on the precompiled configurations stored in an external memory. To reduce the required space for a partial bitstream the relocation technique is used.

### Abstrakt

Tato práce popisuje navrženou metodologii pro návrh systémů odolných proti poruchám v FPGA schopnou ochránit systém před projevy přechodných a trvalých poruch. Oprava přechodné poruchy je prováděna částečnou dynamickou rekonfigurací. Oprava omezeného počtu trvalých poruch je založena na použití odolných architektur využívajících menší množství zdrojů než předchozí použitá architektura. Vadná část FPGA tak není dále využívána. Tato technika je založena na použití předkompilovaných konfigurací uložených v externí paměti. Pro snížení paměťových nároků pro uložení konfiguračních bitových posloupností je použita technika relokace.

## Keywords

fault tolerant system design, partial reconfiguration, design methodology, FPGA.

### Klíčová slova

návrh systémů odolných proti poruchám, částečná rekonfigurace, metodika návrhu, spolehlivost, FPGA.

### Reference

MIČULKA, Lukáš. Methodology for Fault Tolerant Systems Design into Limited Implementation Area in FPGA. Brno, 2017. PhD thesis. Brno University of Technology, Faculty of Information Technology. Supervisor Doc. Ing. Zdeněk Kotásek, CSc.

## Methodology for Fault Tolerant Systems Design into Limited Implementation Area in FPGA

## Declaration

Hereby I declare that this PhD thesis was prepared as an original author's work under the supervision of associate professor Zdeněk Kotásek. All the relevant information sources, which were used during preparation of this thesis, are properly cited and included in the list of references.

Lukáš Mičulka August 29, 2017

## Acknowledgements

I would like to thank my supervisor for his professional guidance, his help and expert advices.

# Contents

| 1        | Intr           | oduction    |                                                    | <b>4</b>  |

|----------|----------------|-------------|----------------------------------------------------|-----------|

|          | 1.1            | Preface .   |                                                    | 4         |

|          | 1.2            | Structure   | of thesis                                          | 6         |

| <b>2</b> | Con            | nmon kno    |                                                    | 7         |

|          | 2.1            | Digital sys | stems                                              | 7         |

|          |                |             | xed logic devices                                  | 8         |

|          |                | 2.1.2 Pr    | ogrammable logic devices                           | 9         |

|          | 2.2            | FPGA .      |                                                    | 10        |

|          |                | 2.2.1 FP    | PGA structure                                      | 10        |

|          |                | 2.2.2 Sto   | oring bitstream configuration                      | 11        |

|          |                | 2.2.3 Xil   | linx Virtex family                                 | 12        |

|          |                | 2.2.4 FP    | PGA reconfiguration                                | 13        |

|          |                | 2.2.5 FP    | PGA design synthesis and implementation            | 15        |

|          |                |             | sign workflow with partial dynamic reconfiguration | 17        |

|          |                |             | onfiguration bitstream structure                   | 18        |

|          | 2.3            |             | digital systems                                    | 19        |

|          |                | 2.3.1 Te    | rms                                                | 19        |

|          |                |             | ult classification                                 | 20        |

|          |                | 2.3.3 Fa    | ults in FPGA                                       | 21        |

|          | 2.4            |             | ility of systems                                   | 22        |

|          |                |             | eliability                                         | 24        |

|          |                |             | ailability                                         | 26        |

|          |                |             | fety                                               | 26        |

|          |                |             | aintainability                                     | 27        |

|          |                |             | stem dependability analysis                        | 27        |

|          |                |             | ppendable system design                            | 29        |

|          |                |             | Freedom C                                          |           |

| 3        | $\mathbf{Rel}$ | ated areas  |                                                    | <b>31</b> |

|          | 3.1            | Fault tole  | rant systems                                       | 31        |

|          |                | 3.1.1 Sta   | atic fault tolerance                               | 32        |

|          |                | 3.1.2 Dy    | vnamic fault tolerance                             | 33        |

|          | 3.2            | Fault dete  | ection and localization techniques                 | 33        |

|          |                | 3.2.1 Re    | eplication and concurrent error detection          | 35        |

|          |                | 3.2.2 Of    | f-line testing                                     | 36        |

|          |                |             | tstream readback                                   | 37        |

|          |                | 3.2.4 Ro    | oving STAR                                         | 37        |

|          |                |             | mmary                                              | 39        |

|          | 3.3           | Transient fault mitigation                                                                   | 40        |

|----------|---------------|----------------------------------------------------------------------------------------------|-----------|

|          |               |                                                                                              | 40        |

|          |               | 0                                                                                            | 41        |

|          | 3.4           |                                                                                              | 42        |

|          | 0.1           |                                                                                              | 43        |

|          |               |                                                                                              | 44        |

|          |               |                                                                                              | 46        |

|          |               |                                                                                              |           |

|          | 0 <b>-</b>    |                                                                                              | 46        |

|          | 3.5           | Fault injection techniques                                                                   | 47        |

| <b>4</b> | Mo            |                                                                                              | <b>49</b> |

|          | 4.1           |                                                                                              | 49        |

|          | 4.2           | Goals of the research                                                                        | 50        |

| <b>5</b> | $\mathbf{Me}$ | thodology for fault tolerant system design into limited implementation                       |           |

|          | area          | a in FPGA                                                                                    | <b>53</b> |

|          | 5.1           | Methodology basic principles                                                                 | 53        |

|          |               | 5.1.1 System design based on the methodology                                                 | 54        |

|          |               | 5.1.2 Structure of fault tolerant system under design - basic principles                     | 55        |

|          |               | 5.1.3 Generations of alternative FT architecture configurations                              | 56        |

|          |               | 5.1.4 Reducing the number of configuration bitstreams via bitstream relo-                    | 00        |

|          |               | cation technique                                                                             | 57        |

|          |               | 5.1.5 Synchronization issues                                                                 | 58        |

|          | 5.2           | Generic partial dynamic reconfiguration controller                                           | 59        |

|          | 0.2           |                                                                                              | 59<br>60  |

|          |               | 5.2.1 The design goals of GPDRC                                                              |           |

|          |               | 5.2.2 GPDRC unit design                                                                      | 60        |

|          |               | 5.2.3 Implementing GPDRC unit as fault tolerant                                              | 62        |

|          | 5.3           | Fault mitigation procedure                                                                   | 62        |

|          | 5.4           | Summary                                                                                      | 65        |

| 6        |               | sign of fault tolerant architecture by means of developed methodology                        |           |

|          | priı          |                                                                                              | 66        |

|          | 6.1           | Prerequisities                                                                               | 66        |

|          |               | 6.1.1 PRM isolation $\ldots$                                                                 | 66        |

|          |               | 6.1.2 Bitstream relocation technique                                                         | 67        |

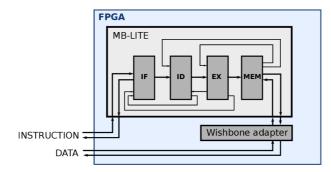

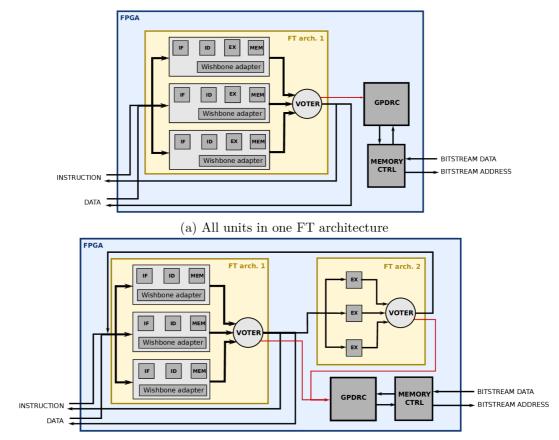

|          | 6.2           | Fault tolerant architectures design                                                          | 71        |

|          |               | 6.2.1 System design partitioning                                                             | 71        |

|          |               | 6.2.2 Selection of the degradation strategy for recovering from permanent                    |           |

|          |               | faults                                                                                       | 72        |

|          |               | 6.2.3 The allocation of implementation area for FT architectures                             | 73        |

|          |               | 6.2.4 The instantiation of GPDRC                                                             | 74        |

|          | 6.3           | Design tool for automatic generation of fault tolerant architectures                         | 74        |

|          | 0.5           | -                                                                                            | 75        |

|          |               | •                                                                                            |           |

|          |               | 6.3.2 Outputs                                                                                | 75        |

|          | <u> </u>      | 6.3.3 The process of FT architecture generation                                              | 75        |

|          | 6.4           | The implementation of generated FT architectures $\ldots \ldots \ldots \ldots \ldots \ldots$ | 78        |

|          | 6.5           | Summary                                                                                      | 79        |

|          |               |                                                                                              |           |

7 Implementation and experimental results

|                        | 7.1 Implementation of GPDRC |          |                                                                           |     |

|------------------------|-----------------------------|----------|---------------------------------------------------------------------------|-----|

|                        |                             | 7.1.1    | Generic implementation of GPDRC and its scaling                           | 81  |

|                        |                             | 7.1.2    | The reconfiguration time of PRM                                           | 82  |

|                        | 7.2                         | Evalua   | ation of hardware overhead of FT architectures developed to secure a      |     |

|                        |                             | given j  | part of system                                                            | 83  |

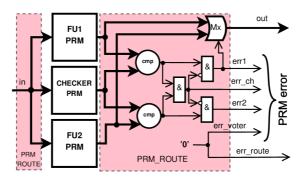

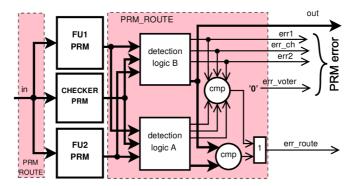

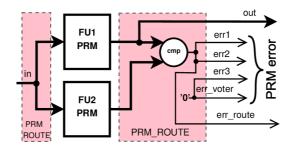

|                        |                             | 7.2.1    | FT Architecture of Generation 0                                           | 84  |

|                        |                             | 7.2.2    | FT Architecture of Generation 1                                           | 84  |

|                        |                             | 7.2.3    | Non-FT Architecture of Generation 2                                       | 85  |

|                        |                             | 7.2.4    | Evaluation of resource overhead                                           | 86  |

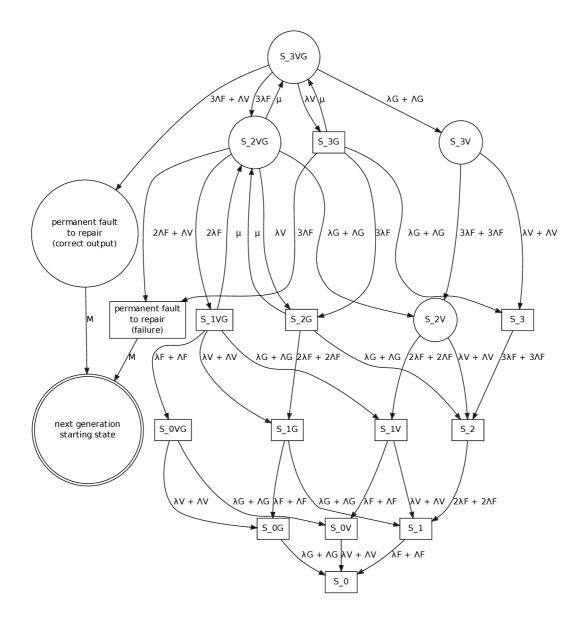

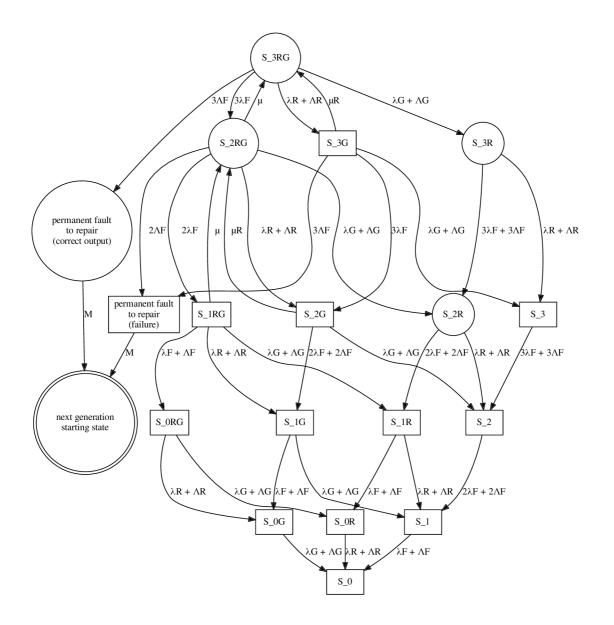

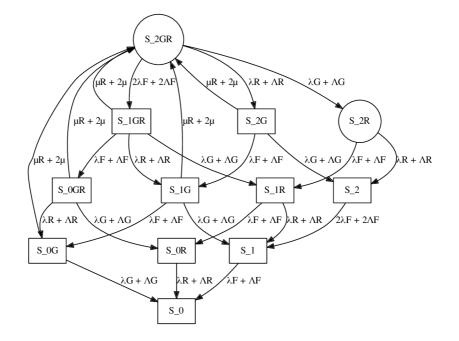

|                        |                             | 7.2.5    | Modelling reliability of proposed FT architectures                        | 86  |

|                        | 7.3                         | Impler   | nentation results of different approaches to the partitioning of original |     |

|                        |                             | system   | 1                                                                         | 91  |

|                        | 7.4                         | SEU t    | esting platform for the evaluation of FT system design by means of        |     |

| methodology principles |                             |          |                                                                           | 93  |

|                        |                             | 7.4.1    | The implemented test and evaluation equipment                             | 93  |

|                        |                             | 7.4.2    | Process of SEU faults injection                                           | 95  |

|                        |                             | 7.4.3    | Experimental results of GPDRC transient fault mitigation process .        | 96  |

|                        |                             | 7.4.4    | Testing and evaluating recovery from permanent fault occurrence           | 97  |

|                        | 7.5                         | Summ     | ary                                                                       | 98  |

| 8                      | Con                         | clusio   | ns                                                                        | 99  |

|                        | 8.1                         | Benefi   | ts of this research                                                       | 99  |

|                        | 8.2                         | Possib   | le enhancements of methodology                                            | 100 |

|                        |                             | 8.2.1    | Bitstream compression                                                     | 100 |

|                        |                             | 8.2.2    | Adoption of isolation design flow                                         | 101 |

|                        |                             | 8.2.3    | Other possible enhancements                                               | 102 |

| $\mathbf{A}$           | Aut                         | hor's j  | publications                                                              | 117 |

| в                      | Pub                         | olicatio | ons cited by other authors                                                | 119 |

## Chapter 1

## Introduction

This chapter brings a brief introduction to the topic of this thesis. It is focused on fault tolerant aspects of electronic devices and it is describing the methodology for fault tolerant system design developed specially for Field Programmable Gate Arrays (FPGA). Before the methodology is proposed in the following chapters, contemporary state of the knowledge in this topic and known approaches for solving issues connected with it are discussed.

#### 1.1 Preface

The progress in manufacturing electronic devices mainly stands on shrinking its parts such as chips and transistors. The Moore's law says that every two years the power of new computer chips will be doubled. Although this idea was formed in 1965 it withstanded as the truth for 50 years. In these days when the shrinking of integrated circuits achieves the 14-nm resolution (half-node shrink) [42], it is clear that the law will be void very early.

The scaling of transistors to such small sizes provides high performance, low power and also lower costs per unit but has also very strong drawbacks. From the system dependability viewpoint, the rapid downsizing of circuitry brings increased defect rates because the wires and devices made of few atoms and bonds are more susceptible to the occurrence of defective parts. These small devices are also very fragile on overstress and other environmental influences during operational lifetime. Additionally, small changes inside fabric caused by these factors can lead to large impact on device performance. It also brings bigger susceptibility to transient upsets. Small nodes use less charge to hold state or data and can be easily altered and upset by noise from outside environment such as radiation.

This implies the motivation to make electronic devices dependable even in very harsh environmental conditions. This is very recent topic. Besides others, it is deeply connected with space exploration. In 2016, the spacecraft from NASA New Frontiers mission came to the orbit of one of Jupiter's months, Juno. This mission is specific also because of its high demands to electronic devices of spacecraft. The radiation in radiation belts of this planet is much stronger then on the Earth's orbit [8]. The electronic devices in spacecraft has to be hardened against such a dose of radiation but it has to be also made fault tolerant to be able to survive the time of mission even if some fault occurs. As an example of its increased dependability, Juno spacecraft's data handling system is based on RAD750 processor from BAE Systems company which is designed to accommodate as much single event effects as possible to survive them for at least 15 years without intervention from Earth [51]. The loose of money in case of unsuccessful mission will be very big and repeating of mission will be time-demanding because the flight to Juno's orbit takes almost 5 years.

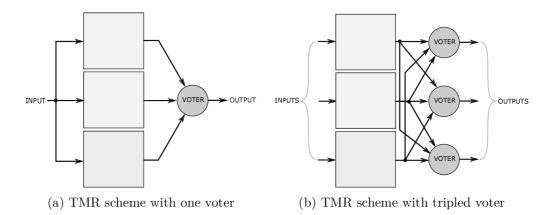

It is clear now, that one of the key system indicators is its dependability. It is an integrated measure consisting of several attributes such as the availability and relibility of system, its maintainability and durability and also its safety and security. All together it expresses the ability of system to produce outputs that can justifiably be trusted. To increase the dependability of system, several mechanism can be adopted. One of the most popular approaches is Fault Tolerant (FT) system design which enables a system to continue its intended operation when some part of the system fails. The operation after the fault occurrence can be at a reduced level, but it should not fail completely. Many FT techniques use hardware redundancy in order to reduce the probability of failure. By replicating the desired circuitry and comparing the results, fault in one or more replicated system units can be detected and reported or the fault mitigation process of faulty unit can be triggered.

Nowadays, developers implementing a particular system can select from various electronic devices. There are many fabrics starting from simple integrated circuits, universal purpose microprocessors, custom chips or programmable microcontrollers and more complex logic devices available on the market. For rapid prototyping and implementing systems consisting of small number of units, the FPGA technology became very popular and frequently used. They provide high logic density and possibility to easily upgrade the implemented designs in order to comply with the latest standards or to modify the function or the structure of implemented system. Another benefit of FPGA design in comparison with custom chips is their relatively short design cycle supported by the possibility of using existing low cost design tools. These benefits together result in low non-recurring engineering costs (NRE) for FPGA design. On the other side, their drawback is their vulnerability to radiation effects [61]. This mainly concerns SRAM-based FPGAs which are becoming increasingly popular for many applications due to their high-throughput capabilities and relatively low cost. The use of fault tolerant system design can be the solution to overcome their higher rate of fault occurrence.

The ability of FPGA to be configured many times also brings new possibilities from the perspective of system fault tolerance. When the system in FPGA is affected by fault, the reconfiguration can be used to overcome its effects. Partial dynamic reconfiguration capable to reconfigure only some parts of implemented system while the others can run without interruption and also to change their layout and connections in FPGA can be used to implement the new advanced fault localization and mitigation methods. This flexibility allows the use of same FPGA for multiple missions without the need of replacement. When some resources of FPGA are permanently damaged, the custom circuit designs can be created to avoid these resources and the implemented application can continue to run further in the same piece of FPGA. With this approach, we can achieve very good dependability and extend the operational time of the system in harsh environmental conditions.

The aim of this work is to propose alternative methodology for fault tolerant design into FPGA. This methodology can be used in systems with limited redundant area where no spare resources can be activated during the system lifetime, only the resources dedicated at the system design time can be utilized. To mitigate the faults which will appear during the system operation the partial dynamic reconfiguration of FPGA will be used. The methodology will focus on recovering from errors caused by transient and also several independently appearing permanent faults. The SEU faults will be simulated by injecting faults into configuration memory of FPGA. In the end of this work the hardware overhead of this solution is evaluated and the quality of the design of secured system is tested.

#### **1.2** Structure of thesis

The introduction to the topic of fault tolerant system design in FPGAs and brief motivation is described in the first chapter. The second chapter will focus on the presention of current technologies which can be used for electronic device implementation together with their benefits and known drawbacks. This chapter also presents the problem of system dependentiability and its impact on system operational lifetime and introduces the concept of fault tolerance of system. The introduction to typical problems in the field of fault tolerant system design and known approaches for coping with them are described in the third chapter. This chapter includes many known techniques, starting with the fault tolerant techniques which can be used universally for all typical fabrics of which electronic devices can be made through to special techniques for SRAM-based FPGAs. The motivation for the research in this topic together with the goals of research are described in the fourth chapter. The fifth chapter is focused on the description of the proposed methodology. At the beginning, the key parts of methodology are presented. The way, how the original system has to be modified to extend its operational lifetime is described. The following sections include the description of utilizing the FPGA features such as partial dynamic reconfiguration to achieve this. The methodology involves specific FT architecture design. The design of these architectures based on the user requirements on dependability indicators and occupied resources on chip can be automated. The FT architecture design together with developed tool for its automated design and implementation is the content of chapter six. In the seventh chapter, the experimental results and their evaluation are presented. In the last chapter of thesis, the obtained results are summarized and the benefits of research are stated. It includes also the possible ways for the subsequent research orientation in this area.

## Chapter 2

## Common knowledge

In this chapter, the digital systems technologies and concept of fault tolerance will be presented.

#### 2.1 Digital systems

The circuit implementing certain function can be designed using two basic approaches - as an analog or a digital system. While the analog systems use continuous set of input and output values, the digital system is based on the use of finite number of discrete values. Usually, two values are used - logical one and logical zero. These two approaches are often mixed in real systems. While the analog part of the system can be used for processing the signal on system input the digital part is performing the computation. Although the first mass-produced electronic devices were analog, during the last decades the digital system became more popular. The main drawback of analog design is its susceptibility to noise where small change in the signal can cause a significant change in the information present in the signal and can cause the information to be lost. Since digital signals take on one of only two different values, a disturbance would have to be about one-half the magnitude of the digital signal to cause an error. This property of digital circuits can be exploited to make signal processing noise-resistant. With proper techniques such as securing and detection codes the corrupted digital signal can be easily reconstructed [43].

Digital systems mostly use signals with 2-level logic. It means that voltage value on signal should be assignable one of two logical values according to their tolerance intervals stated by the manufacturer of digital circuit. Two possible implementations of logical values then exist:

- In *positive logic* the logical one is represented by higher voltage and logical zero by lower voltage.

- In *negative logic* the logical one is represented by lower voltage and logical zero by higher voltage.

In 2-level logic the voltage values between lower voltage tolerance interval and higher voltage tolerance interval represent undefined or forbidden values. This undefined values can cause problems in digital circuit since the implemented functions are defined only for two possible logical values (zero and one) on input signals. For other values on inputs the output will be undefined. Signals with two levels can be used in Boolean logic for digital circuit design or analysis. The basic building blocks for digital systems are gates implementing

basic Boolean functions such as negation (NOT), conjunction (AND), disjunction (OR) and exclusive disjunction (XOR). These blocks transform the input vector of binary values to output vector of binary values. The complex digital systems can be built by connecting these simple gates.

Other types of digital circuits using 3-level logic gates with the third logical value of high impedance [21] or more levelled logic exist (e.g. [1]). New gates can be built also with polymorphic electronics where the gates can implement different functions according to the state of environment (temperature, power supply voltage, light) [54].

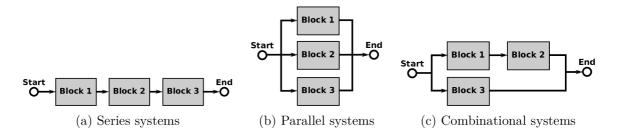

The digital circuit can be split into two classes:

- Combinational logic refers to the circuits the output of which is a function of the present values of the inputs only. Combinational logic circuits do not contain any memory elements and thus when the inputs are changed, the information about the previous inputs is lost. The behaviour of combinational circuits is described by the set of output functions.

- Sequential logic refers to the circuits the outputs of which are also dependent upon past inputs and outputs to them. Thus they implement some form of memory. They consist of two parts. The function is implemented by combinational logic and its outputs are stored in registers. The values in these memory elements are called state variables and can be used in the subsequent cycles of computation. The behaviour of sequential circuit is described by the set of next-state functions and the set of output functions.

Sequential circuits can be divided according to the way in which the circuit changes its output.

- Asynchronous sequential circuits change their state (and outputs) immediately when input vector changes. The state time of this circuit depends only on the internal logic circuit delays. As an example, asynchronous counter can serve.

- Synchronous sequential circuits use the synchronisation signal usually called clock signal. The input vector is sampled just with the change of clock signal. The concept of the global clock signal for all units in the system can be used or several independent clock signals can exist.

In complex digital systems, both combinational and sequential subsystems can be identified. Last decades brought still the growing effort of creating an integrated circuit (IC) by combining millions of gates and billions of transistors into a single chip. This process is known as Very Large Scale Integration (VLSI). It is a structured design flow that enables a great number of transistors to sit together and work on a single microchip by saving microchip area.

According to requirements on system reconfiguration we can distinguish between two approaches: fixed logic devices for specific applications and programmable logic devices.

#### 2.1.1 Fixed logic devices

For a specific usage in some applications, the Application Specific Integrated Circuit (ASIC) can be developed. These types of circuits stand on the opposite side to the usage of circuit for general purpose such as microcontrollers or other programmable logic devices. The ASICs have fixed configuration of gates and interconnections and they perform one function

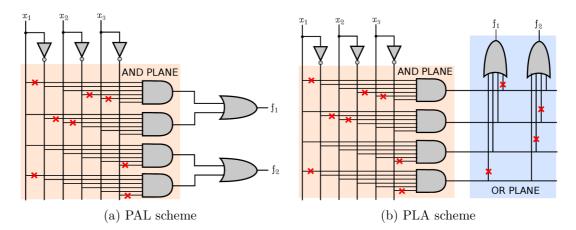

Figure 2.1: Simple programmable logic devices

or a set of functions forever. Once they are manufactured, they cannot be changed. The time required to go from design to prototypes and to a final manufacturing run can be several months depending on the complexity of the device. Every error in design phase or change of requirements can cause the necessity of developing a new design. Specific design is often not reusable in other circuit designs. On the other hand, ASIC can be very well optimized to satisfy requirements of specific application (for timing, space, cost, etc.).

#### 2.1.2 Programmable logic devices

A Programmable Logic Device (PLD) is an integrated circuit with internal logic gates and interconnects. These gates can be connected to obtain the required logic configuration. The circuit can be configured by the end user to realize various designs. Programming of such a device often involves placing the chip into a special programming unit, but modern chips can be often configured in-system which means that its configuration can be modified directly in application where this chip is used. Another (more modern) term for PLD used in literature is Field-Programmable Device (FPD).

The term PLD includes several specific concepts of reconfigurable devices:

- *Simple PLD (SPLD)* is the simplest, smallest and least-expensive form of programmable logic devices.

- Programmable Logic Array (PLA) is a small PLD which can realize a sum-ofproduct functions by implementing them using a set of input inverters, ANDgates and OR-gates. Both planes, AND-plane and OR-plane can be programmed to realize a function (see Figure 2.1b).

- Programmable Array Logic (PAL) is a small PLD that has the same components as PLA with the difference in fixed OR-plane (see Figure 2.1a).

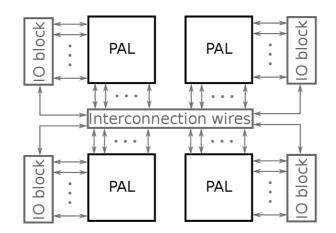

- Complex PLD (CPLD) consists of an arrangement of multiple SPLD-like blocks on a single chip (see Figure 2.2).

- *Field-Programmable Gate Array (FPGA)* is a PLD featuring a general structure that allows very high logic capacity. While CPLDs offer logic resources with a wide number of inputs (AND planes), FPGAs have more narrow logic resources with higher ratio of flip-flops to logic resources.

Figure 2.2: CPLD scheme

### 2.2 FPGA

The semiconductor industry makes a huge progress in last decades. From the first expansion when the transistor was introduced over the spread of integrated circuits to the era of ASICs the evolution of electronics was driven forward in order to get the fastest, smallest and cheapest system implementations. In parallel with fixed logic devices, the programmable logic devices have been developed with the beginning of 1970's. This approach started to play bigger role with the introduction of field-programmable gate arrays in late 1980's. The first FPGA (XC2064) was constructed by Ross Freeman in 1985. The FPGA chip spread across all industries is now driven by the fact that FPGAs combine the best parts of ASICs and processor-based systems. FPGAs can reach up to hardware-timed speed and reliability, but they do not require so big effort and expenses to create custom ASIC design.

The application in FPGA is defined by the configuration memory which determines the function of its blocks and also how these blocks are connected together. This configuration can be programmed after manufacturing, there are some one-time programmable FPGAs available, but the dominant types are SRAM-based which can be reprogrammed as the design evolves. The most of FPGA market is divided between Xilinx and Altera company. In 2015, they together occupied more than 85% of it [44].

#### 2.2.1 FPGA structure

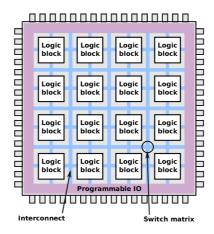

FPGAs are programmable logic devices that are based around a matrix of configurable logic blocks (CLBs) connected via programmable interconnects (see Figure 2.3). The application can be implemented by designing configuration for the matrix of CLBs (configure their implemented functions) and interconnection between them.

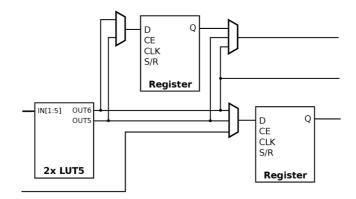

The configurable logic block is the core of the logic structure of FPGAs. The logic blocks within a CLB reside slices that consist of look-up tables (LUTs), carry chains, and registers. These slices can be configured to perform logical functions, arithmetic functions, memory functions, and shift register functions. Their stucture differs in construction between differt families of FPGAs. The structure of CLB from Xilinx Virtex 7 FPGA family is shown in Figure 2.4. The function of CLB is determined by its configuration which is a small part of overall configuration bitstream. The first FPGA XC2064 contained only 64 configurable logic blocks, each of them consisting of two three-input lookup tables. Nowadays, in high

Figure 2.3: FPGA architecture

end FPGAs there are hundreds of thousands of CLBs on single chip with four six-input LUTs.

FPGAs are reffered to as the coarse-grained architectures because besides the configurable matrix of CLBs they also include different types of resources implementing frequently used system functions. These resources are reffered to as hard blocks and they are added to FPGA to avoid the need to implement these units in CLBs and also due to fact that they can be optimized to give better performance and spare some logic on the chip. Typical examples of these hard blocks in FPGAs are Block RAM memories (BRAMs), Digital Signalling Processor (DSPs) units, high speed I/O blocks (IOBs), clocking manager modules such as Digital Clock Managers (DCMs) in Xilinx FPGAs, communication modules (Ethernet, RS232), etc.

The matrix of CLBs is connected with outer environment by programmable I/O blocks. They provide the interface between package pins and the internal configurable logic. They can be used for enhanced source-synchronous interfacing. With this, the optimizations such as clock dividers, data serializers/deserializers, per-bit deskew for input and output signals, dedicated I/O and local clocking resources become available [67]. Signals from the input of FPGA travel through the global routing network and are processed in the CLBs or other hard blocks. Processed signals are then routed back to the IOB as an output or routed to another destination for further processing. The Programmable Interconnect Points (PIPs) provide the routing paths used to connect the inputs and outputs of IOBs and CLBs into logic networks. A PIP is a CMOS transistor switch that can be configured to be turned on or off.

#### 2.2.2 Storing bitstream configuration

Configuration bitstream can be stored in FPGA using various technologies:

• SRAM-based FPGAs use the SRAM memory cells based on array of latches to store configuration data for CLBs and other resources settings. They are popular due to their high throughput and ability to be reconfigured many times. They are also usually cheaper option to other types of memory. Their drawback is the fact that this memory is volatile and thus the configuration has to be loaded again to FPGA when it is powered on. Modern SRAM-based FPGAs have highest densities, but consume a lot of power and need an external non-volatile memory to store configuration bit-

Figure 2.4: LUT and flip-flops connections inside CLB (Xilinx Virtex 7)

stream. This can be done by two different approaches. When master mode is used, the FPGA itself reads configuration data from an external source (ie. flash memory). In the slave mode some external controller is used to load the configuration from external bitstream memory to SRAM memory in FPGA. Frequently some dedicated configuration interface or boundary-scan (JTAG) interface is used to load the configuration into FPGA's configuration memory. SRAM-based FPGAs include most chips of Virtex and Spartan families from Xilinx and Stratix and Cyclone families from Altera.

Some SRAM-based FPGAs can be equipped with an internal flash memory. This nonvolatile memory can be used to store the configuration when the FPGA is not powered and thus this FPGA does not need any external configuration memory. In addition, there can be more stored configurations from which the current one is chosen during the FPGA startup. This approach can be used to prevent unauthorized bitstream copying. This can be found for example in Spartan-3AN FPGAs from Xilinx [64].

- Flash-based FPGAs use flash memory as a primary resource for configuration storage. There is no SRAM memory to hold configuration data in FPGA. This technology has an advantage of being less power consumptive. Flash-based FPGAs are also more tolerant to radiation effects and due to their volatility they also can be a solution to prevent unauthorized bitstream copying. To flash-based FPGAs belongs families such as Igloo and ProASIC3 manufactured by Actel [4] [5].

- Antifuse-based FPGAs are different from the previous types since they can be programmed only once. After manufacturing the antifuse FPGA is not set by any configuration. The function of CLBs and other blocks and the interconnection is set permamently when the configuration is loaded to FPGA and the antifuse is burned. After this moment, the antifuse-based FPGA cannot be reconfigured. As an example of these FPGAs the Axcelerator family manufactured by Actel can be mentioned [62].

#### 2.2.3 Xilinx Virtex family

Virtex is high-performance family of FPGA from Xilinx company. They are SRAM-based FPGAs and they can offer a great number of logic blocks together with the variety of built-in hard macros and can be used for high-performance applications. During the last two decades this family evolved with the shrinking node size enabling to add more logic to single chip. The comparison of number of resources available in different Virtex families

can be seen in able 2.1. Virtex families are further divided into subfamilies according to their desired application. According to it, they have different row and column count in their matrix of CLBs and different variety of hard macro resources. The LXT subfamily is designed for advanced logic applications, SXT for signal processing, TXT systems with double density for advanced serial connectivity and FXT for embedded systems.

| FPGA family | Technology<br>[nm] | Slices<br>[#]  | Distibuted RAM<br>[Kb] | Block RAM<br>[Kb] | DSPs<br>[#] |

|-------------|--------------------|----------------|------------------------|-------------------|-------------|

|             | L ]                |                |                        |                   |             |

| Virtex 4    | 90                 | 5472 - 63168   | 86 - 1392              | 648 - 9936        | 32 - 512    |

| Virtex 5    | 64                 | 3120 - 51840   | 210 - 3420             | 936 - 18576       | 24 - 1056   |

| Virtex 6    | 40                 | 11640 - 118560 | 1045 - 8280            | 5616 - 38304      | 288 - 2016  |

| Virtex 7    | 28                 | 51000 - 178000 | 4388 - 17700           | 28620 - 50760     | 1260 - 2520 |

Table 2.1: The comparison of Virtex FPGA families

In this research, FPGA XC5VSX50T from Virtex 5 SXT subfamily was mainly used for design implementation. This subfamily contains CLBs based on 6-input LUT, 36 Kbit dualport BRAM modules which can be also configured as two independent 18 Kbit dual-port RAM blocks and in addition these BRAMs can be connected in cascade to form a larger memory block. There is also a possibility to utilize cascadable embedded DSP48E slices with two's complement multipliers and 48-bit adder/subtracter/accumulator for parallel computing or to use each of DSP slices to bitwise logical functions. The CLB is divided into two different slices, the first type is referred to as SLICEL and has only capability to implement logic function and the second type SLICEM can be used as a memory and implement 32-bit shift register or 64-bit distributed RAM. The maximal operational frequency of FPGAs from this family is 550 MHz.

#### 2.2.4 FPGA reconfiguration

A considerable part of the FPGA (in terms of its area) is used for configuration memory which defines the implemented hardware circuitry (application) in FPGA. It contains the configuration of CLBs, IOBs, DSPs, BRAMs and other resources and also the routing between these blocks. The process of loading the configuration bitstream through reconfiguration interface to the configuration memory is called reconfiguration of the FPGA.

Depending on the structure of reconfigurable device, we can divide reconfiguration according to its granularity. The granularity of reconfiguration is defined as the size of the smallest block of reconfigurable device which can be addresed by mapping tools. Finegrained architecture offers greater flexibility for the implementation of design. The drawback of using these architectures can be the increase of power, area and delay because of greater quantity of routing. Corse-gained architecture uses bigger configurable blocks which can be optimised for its intended use and are typically oriented on word-width datapaths. This can reduce the area, time and routing requirements and the reconfiguration time. The drawback can be seen in possible inefficient utilisation of resources such as in case when the operands width of implemented function unit does not meet with the building block of reconfigurable architecture. Also the implementation of design into coarse-grained architecture is usually more difficult due to the need of sufficient number of specific building blocks. Typical FPGA combines these approaches together by using the array of CLBs with interconnection matrix and specific hard blocks (DSPs, BRAMs, etc.).

The important measure of reconfiguration is the deployment time. This means the time needed to finish this process and bring the FPGA application back into running mode. The

deployment time depends at most on the size of configuration bitstream and the width of datapath between the bitstream storage and reconfiguration interface. Typical time for reconfiguration of entire medium sized FPGAs such as Virtex 5 SXT 50 FPGA is several milliseconds. Several ways how to burst the process of reconfiguration exists. These include the partial reconfiguration of just a small portion of FPGA which has to be changed or the use of compressed configuration bitstream.

In modern FPGAs, several different types of reconfiguration can be identified:

- *Full reconfiguration* is the process of changing configuration of all resources in device. While the full reconfiguration process takes place, the device is running only in idle mode. The implemented application begins to run immediately after this process is finished. Typically, the full reconfiguration is done after power-up of device.

- *Partial reconfiguration* is the process of changing a portion of reconfigurable hardware circuitry while the rest of design is not changed. Just the partial configuration bitstream is written to configuration memory. Partial reconfiguration can be divided according to its influence on the run of application in FPGA:

- Partial static reconfiguration process stops the running application (circuitry) even if only a part of it is changed. The application in device is brought up after this process is completed.

- Partial dynamic reconfiguration (PDR) process changes a portion of implemented circuitry without any intervention to the rest of it. This requires a special FPGA design flow where each part of FPGA allowing PDR has to be encapsulated by adding special macros on buses going inside or outside from this part to isolate it from the unchanged (static) part.

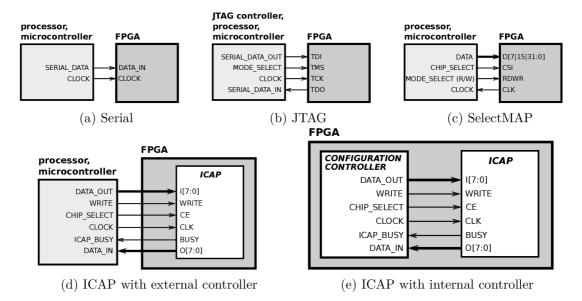

FPGA can be configured via different configuration interfaces. Xilinx FPGAs from Virtex family offer the following interfaces:

- Serial Peripheral Interface (SPI) is an external configuration interface of FPGA containing only two single bit signals (clock and data). The FPGA is configured by loading single bit of data per clock cycle. This interface is typically used for devices in a serial daisy chain or in case when single device is configured by an external microprocessor or CPLD. The connection of configuration controller and FPGA is shown in Figure 2.5a.

- *Byte-wide Peripheral Interface* (BPI) is similar to SPI with one difference, data signal is 8-bit or its multiplies wide.

- JTAG (Joint Test Action Group) is external interface based on serial data transfer. It is primarily used for testing and debugging purposes defined by IEEE standard 1149.1. It contains a Test Access Port (TAP) and boundary-scan architecture. In programmable devices such as FPGA, it can be used for in-system programming (configuration). Several devices can be connected in daisy chain and then they can be configured at once. This interface has bigger priority than others. When the JTAG controller is loading data serially on Test ClocK (TCLK) signal edge the run of other interfaces is stopped. The connection between JTAG controller (or other device implementing its function) and FPGA is shown in Figure 2.5b.

Figure 2.5: The configuration interfaces of FPGA

- SelectMap is external configuration interface which supports bidirectional communication with FPGA device by an 8-bit, 16-bit, or 32-bit data bus. It can be used either for configuration of device or for bitstream readback from device. Data bus width is automatically detected. There are three possible modes of configuration: singledevice, multiple devices connected as daisy-chain where each device can be configured by different bitstream and multiple devices connected in parallel where every devices are configured by the same bitstream. FPGA and configuration controller connected via SelectMAP is shown in Figure 2.5c.

- *ICAP* (Internal Configuration Access Port) is a fast internal parallel interface. The ICAP interface is a subset of the SelectMAP interface and thus they cannot be used simultaneously. The process of configuration of device and its bitstream readback is essentially the same as with the use of SelectMAP. Since ICAP provides ability of partial self-reconfiguration of FPGA the care must be taken during reconfiguration to avoid the change of reconfiguration controller and all circuitry performing the reconfiguration process. These parts of FPGA should be made static (not dynamically reconfigurable). Thus, the ICAP cannot be used for full reconfiguration of FPGA and it is designated to perform partial dynamic reconfigurations.

When implementing the FPGA design with PDR ability, the ICAP primitive can be instantiated in FPGA and it can be driven by reconfiguration controller which will read the partial bitstream from non-volatile memory and transfer it to ICAP interface during PDR process. This controller can be located in different fabric as shown in Figure 2.5d or it can be instantiated in the same FPGA as shown in Figure 2.5e.

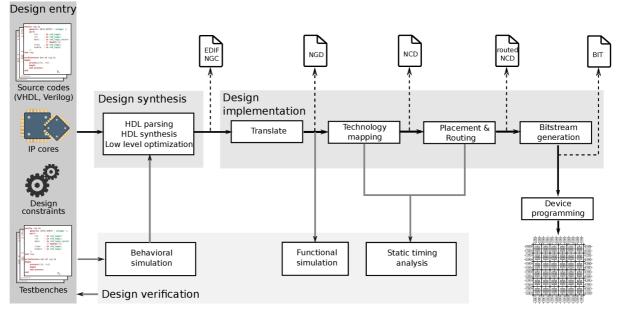

#### 2.2.5 FPGA design synthesis and implementation

To implement the digital system into FPGA the series of steps are needed. These steps can be grouped to design entry and its synthesis and implementation. These steps can be done separately but modern advanced design tools such as Xilinx ISE offer the possibility to do all these steps in one development environment.

At the beginning, the system description has to be specified in some programming language or some visual editor. To simplify this process, special Hardware Definiton Languages (HDL) were introduced. They accent the parallelism in digital circuits and they offer the possibility to specify the system by its behaviour and structure. VHDL and Verilog belong to most known HDLs and they are used as an open standards of Institute of Electrical and Electronics Engineers (IEEE) to describe the digital circuits on different levels and for simulation purposes. They can be used for digital system design not only for FPGAs but also for CPLDs. The common level of abstraction in HDL is Register Transfer Level (RTL). It is based on the premise that synchronous systems can be described as a set of registers which are connected between themselves and with inputs and outputs by combinational logic.

As the optional step after the design entry in HDL, the simulation of design can be run in some simulation tool such as ModelSim or ISim and it can uncover the design faults or timing limitations. A set of testbenches is needed to perform the simulation.

After successful simulation, the design synthesis is performed. This process converts the HDL input to netlist files which describe the system as a set of logical gates and their connections. The synthesis is consisted of several steps. After parsing of HDL file, the synthesis tool tries to infer specific design building blocks (ie. MUXes, RAMs, adders, etc.) for which it is able to create efficient technology implementations. The next step is Finite State Machine (FSM) recognition. When some FSM is identified in the design, the most efficient encoding algorithm for its implementation can be chosen according to the specified optimization goal (i.e. area, speed). The synthesis tool also tries to reduce the amount of inferred macros and share some resources which can lead to a reduction of the area as well as the increase in the clock frequency. Finally, the low level optimization is made including implementation of macros, timing optimization, technology mapping and register replication. The output of synthesis are files with netlists described most often by Electronic Design Interchange Format (EDIF) or some vendor specific file format such as NGC from Xilinx. This file can also contain the contraints specified by designer which will be used in further steps of design implementation. In constraints file, the designer can specify timing, placement, and other design requirements.

Some design tools such as Xilinx ISE also offer the possibility to add to system design pre-synthetised macros which are optimized for its purpose (memories, bus controllers, etc.) and can be also customized (bus widths, memory sizes, etc.). These macros can be added as an additional input to the synthesis tool and synthetised together with the HDL sources.

When the design is synthetised it has to be implemented to specific FPGA. This means that the logical design is converted into a physical file format that can be downloaded to the selected target FPGA. The implementation can be customized by setting custom goals and strategies in constraints file which are taken into account by implementation tool. Adding constraints can cause the situation that the implementation tool will not be able to implement design due to insufficient number of resources in specified FPGA and timing or routing issues.

The implementation of design consists of several consecutive steps. These steps are often done as a batch by the design tool.

• The *translate* process merges all netlist files from synthesis together with design constraints and create Native Generic Database (NGD) file. This file contains the logical design reduced to FPGA primitives.

- The *map* process is mapping the logic primitives from previous step into available resources on the target FPGA such as CLBs and IOBs. The output design is a Native Circuit Description (NCD) file that physically represents the design mapped to the components of FPGA.

- The *Place And Route* (PAR) process takes as an input a mapped NCD file and it places and routes the design. An NCD file with routing prepared for bitstream generation is created as an output of this step.

- The *bitstream generation* process encodes the NCD file with routing into configuration bitstream for the target FPGA. The output bitstream can be directly used for target FPGA reconfiguration.

The FPGA design workflow used by Xilinx ISE tool is show in Figure 2.6.

Figure 2.6: Design workflow by Xilinx ISE tool

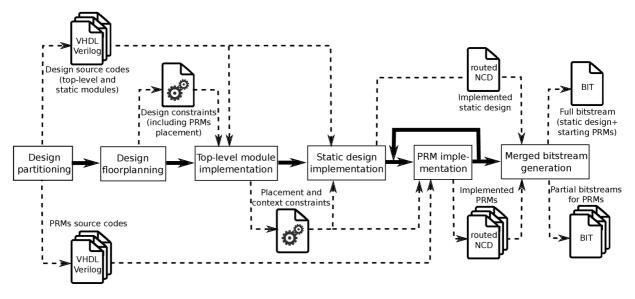

#### 2.2.6 Design workflow with partial dynamic reconfiguration

This paragraph describes the changes to standard design workflow when PDR is used. It is shown in Figure 2.7.

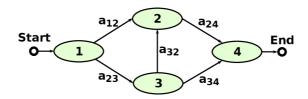

In Xilinx design workflow, the hierarchical design must be strictly used. This means the design has to be partitioned into modules which create hierarchical structure where on the top of hierarchy is one top-level module. In this module, the static and dynamic components can be identified. While design floorplanning, the Partial Reconfiguration Regions (PRRs) for each Partial Reconfiguration Module (PRM) have to be determined. There can be more PRMs assigned to one PRR enabling the dynamic change of implemented circuitry in FPGA. The size of PRR and its shape is limited according to FPGA architecture structure. Typically, the FPGA is divided into several tiles containing the same number and type of resources and the same relative position of resources in tile. PRR can consist of one or more of these tiles.

The implementation of design using PDR begins with top-level module which consists of static modules and PRMs. While implementing top-level design, the PRMs are instantiated as black-boxes. On the boundary between PRMs and static part of design, the logic for isolating these modules during PDR is added. Previously, Xilinx FPGAs were using the bus macros for this purpose. Bus macro is interface consisting of two LUTs applied to each single signal. The first LUT is placed in PRM next to its boundary and the second is place next to it but outside (in the area neigbouring with this PRM). Nowadays, the proxy logic is used [66]. Proxy logic is using single LUT for each signal and it is placed automatically by implementation tool. When top-level module is implemented with PRMs instantiated as black-boxes, constraints for static part and PRMs are determined and full design with chosen startup PRMs is implemented. In the next phase, each PRM is implemented in turn. The MAP and PAR process is constrained by one or several constraint files. The last phase is merging of each PRM created with static design. Their interfacing correctness is verified and partial reconfiguration bitstreams are created. Finally, the full configuration bitstream which will be used after power-up of FPGA is created.

Figure 2.7: Design workflow with PDR by Xilinx

#### 2.2.7 Configuration bitstream structure

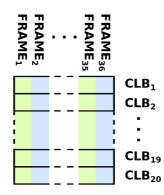

The configuration bitstream contains the necessary data for configuration of FPGA resources, i.e. definition of routing between components via setting the programmable interconnect points, enabling of flip/flops or LUTs inside CLBs, definition of LUT functions, etc. The configuration data of Xilinx FPGAs is arranged into configuration frames. One frame is the smallest unit of the configuration which can be addressed and handled by the reconfiguration interface of FPGA and its internal reconfiguration logic. The size of one configuration frame varies according to FPGA family, in Virtex 5 FPGAs family the size is 1312 bits and it is formed by 41 32-bit words [67].

As the single frame configures (partially) 20 CLBs located in one FPGA column at once, the smallest possible PRM which can be created must contains multiples of these 20 CLB columns. To configure these 20 CLB completely, the set of 36 frames is needed (see Figure 2.8).

Figure 2.8: The configuration of the smallest possible PRM by configuration frames

The complete configuration bitstream can be divided into three parts.

- The *header* is composed of the mixture of synchronizing words, dummy words and 32-bit commands used to initialize the reconfiguration process by setting internal registers. The main goal is to prepare the FPGA to receive the subsequent configuration data organized in frames. These commands include the initialization of Cyclic Redundancy Check (CRC), setting the configuration and control options, setting the Frame Address Register (FAR) with the address of the first configuration frame. At the end of header there is the write configuration command starting the process of loading configuration frames.

- The *configuration data* is consisted of the bulk of configuration frames. Due to the fact that the frames are typically organized to configure consecutive blocks of resources, the frame address is automatically incremented when the next frame is recognized.

- The *footer* is used to issue the commands to finish the reconfiguration (i.e. CRC) and prepare the FPGA for the start (i.e. the reset of flip-flops).

The mapping between the bits in the configuration bitstream and the specific FPGA resource is typically not documented by the manufacturer. This relation is not needed for the standard system design flow in FPGA but it makes some task difficult such as precise fault injection via bitstream manipulation [50].

#### 2.3 Faults in digital systems

Very fast scaling of technology in last decades has an adverse impact on the reliability of components for digital systems. An increasing error susceptibility for disturbances from the operational environment can be identified but the components also become more vulnerable to permanent faults. Faults occur in a digital system in all phases of its existence - from the design and fabrication phase through the whole lifetime.

#### 2.3.1 Terms

In this paragraph the difference between the terms fault, failure and error is presented.

• A *fault* is a difference in hardware configuration between correctly configured system and its current state. If there is no difference, fault is not present.

- An *error* in a system is a deviation from the required operation of system or subsystem which causes the difference between actual processed data and expected correct data. The reason of error occurrence is fault presence in the system.

- A *failure* of the system means that it is not producing correct outputs and thus the system is working with the behaviour which differs from the required one. A failure is caused by an error.

Not every fault has to manifest itself necessarily by an error which can be detected. Errors that are present in a system but not detected are *latent errors*.

#### 2.3.2 Fault classification

Faults in digital systems can be classified according to their time of occurence:

- *Design faults* are present in the system from the beginning of its lifetime. They can be inherited from the existing system on which the new one is built, created by human designer or by design tool. These faults are present in every piece of final system.

- Fabrication faults can be present in the final solution due to an imperfect manufacturing process (i.e. short-circuits, opens, incorrect transistor threshold voltage, improper doping profiles, mask alignment errors, poor encapsulation in VLSI circuits etc.). Accurate identification of fabrication defects is important in improving the manufacturing yield.

- *Operational faults* are caused by external disturbance during the digital system lifetime. The sources of these faults can be operator mistakes, environmental extremes, electromagnetic interference and wear-out failures when the product exceeds its design lifetime.

Faults in digital systems are usually classified according to their duration:

- Transient faults appear in the system for a short time, they are mostly caused by random environmental disturbance such as radiation, pollution, humidity, temperature, pressure, vibration, power supply fluctuations, electromagnetic interference, static electrical discharges, ground loops etc. The physical resource is not damaged. These faults are not correlated with each other and it is nearly not possible to detect them due to their hardly predictable influence on the system behavior.

- *Permanent faults* affect the functional behavior of a system permanently. They refer to a physical damage of system resource. This resource cannot be used any more without physical repair or replacement. The error caused by permanent fault is also called hard error.

The permanent faults can arise as a result of various physical phenomenons, such as:

- Time Dependent Dielectric Breakdown (TDDB) is the result of long-time application of relatively low electric field. It is an opposite to immediate breakdown which is caused by strong electric field. TDDB comes with reduction in gate oxide thickness. The charges are trapped in oxide that creates electric field. The charge flow through the oxide results in a breakdown after some time.

- *Electro-mitigation* is causing permanent failure of interconnect. It develops voids in metal line due to heavy current densities over time period.

- Hot Carrier Effects are parasitic effects at the drain side of channel and they are caused by hot carriers traveling with saturation velocity. It is attributed by slow creation of traps at the oxide surface. Their impact is the change of the transistors threshold voltages which consequently affects the power and performance of the device.

The permanent fault can manifest as permanent logical value 1 or 0 on signal which is called stuck-at fault. Another manifestation can be short-circuit between two or more signals, delayed propagation of signal through the circuit compared to specification or delayed level transition from logical 0 to 1 or inversely.

• Intermittent faults appear, disappear, and reappear repeatedly. They are difficult to predict, but their effects are highly correlated. Most intermittent faults are caused by the optimistic design or manufacturing not counting with all circumstances which can affect its run. The system works well most of the time, but fails under atypical environmental conditions.

#### 2.3.3 Faults in FPGA

All common faults of digital systems can also occur in FPGAs. There are also other specific faults which can appear in specific FPGA resources such as configuration memory. Most of the modern FPGAs are based on SRAM which is vulnerable to radiation. Alpha-particles as the part of the radiation is the main reason of transient faults presence in FPGA. Errors caused by transient faults are frequently called soft errors.

Very often we are faced with two types of faults:

- Single-Event Upset (SEU) causes a random change in the state of a digital memory element (or other sequential element) by an ionizing particle that collided with this element. SEU can be very critical in case of SRAM-based FPGAs and can lead to undesirable change of function implementation. The system can be turned to correct operation by correcting the attacked element to its proper state. The probability of the SEU for one memory cell is extremely small for typical conditions on earth. But with increasing memory size or exposure in harsh environment the probability can considerably increase. This can become a real problem for example in the space or aircraft designs.

- Single-Event Transition (SET) causes one or more voltage pulses (i.e. glitches) on signals which can be then propagated through the circuit. There is no need to correct this erroneous state due to its short and temporary existence.

In ASICs, SEU faults are considered as transient. If they hit combinatorial logic, the error on the output lasts only until the next value is processed by the logic. In case they hit sequential logic, the errors exists in storage cell until next value is written into it.

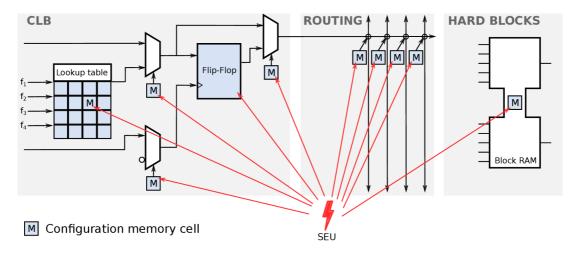

The variety of effects in FPGAs after SEU occurence is bigger as shown in Figure 2.9. In FPGAs, the combinational and sequential logic of implemented circuit is set by the values of configuration memory cells. The combinational logic of final circuit is implemented by LUTs and routing settings. The SEU occurence in LUT changes its implemented function. In routing settings, the impact of SEU can be the change in the connection of logic gate

output or input to interconnection matrix. Both faults can be restored by reconfiguration of FPGA by the original configuration bitstream. The sequential logic of final circuit can be implemented by flip-flops in CLBs or by hard blocks such as Block RAMs. The effect of SEU on flip-flops is transient. With the next write operation to memory cell implemented by flip-flop the error disappears. When the SEU fault occurs in Block RAM cell, the reconfiguration of FPGA is needed to restore its state [28].

Figure 2.9: Bits in configuration memory and resources of FPGA sensitive to SEUs (Xilinx Virtex FPGA family) [28]

In this work, the fault in configuration memory is considered as transient in case it can be corrected by reconfiguration of FPGA with using the original configuration bitstream and restoring its state by synchronization process. If the reconfiguration of FPGA does not correct the fault, it is considered as permanent fault.

#### 2.4 Dependability of systems

The dependability is the ability of a system to deliver its intended level of service to its users [6]. In other words, the dependability of system (service) can be expressed as the system ability to work without failures at least for the given period and without more severe failures than it is acceptable. With the fact that the computing becomes common in all parts of human life, its dependability plays an important role in all its applications.

The system dependability is an integrated measure consisting of several attributes and it cannot be counted as a single number. It can be evaluated from the availability and reliability parameters of the system, its maintainability, safety and security and other adjacent attributes such as repairability or durability. To summarise, the dependability expresses the ability of system to produce outputs that can justifiably be trusted.

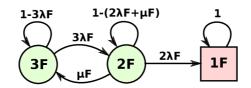

To be able to evaluate dependability attributes, some system fault model has to be adopted. The most frequently used model is using only two states. At the given time the system (component) is either working properly or it is faulty and producing incorrect outputs. The system state can change as the time evolves and this change is done instantly. The change from a functioning to a failed state is referred to as failure and the change from failed state to the functioning state is referred to as repair [25].

The systems can be divided according to their survivability of occured faults to repairable and non-repairable ones. Survivability in this context means that the system can be used again to produce the correct outputs after fault occurence (not necessarily immediately, time for fault mitigation may be needed). The non-repairable system will stay after the first fault occurence in failed state forever. The repairable system can be brought from failed state to functioning state when repair process is completed (if it is possible). It is assumed that the repair process will bring the failed system back to the state where it will produce correct outputs and it will be able to recover from the same variety of possible faults as in the beginning of its lifetime.

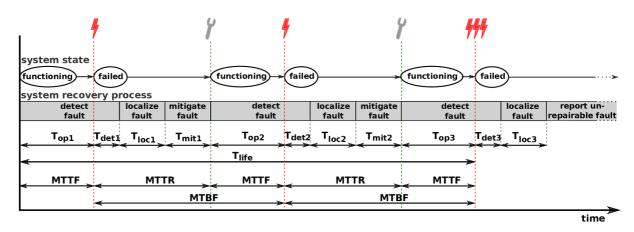

The changing of system states according to fault occurences and their repairs is shown in Figure 2.10. The lifetime of system  $(T_{life})$  describes the time from the first run of system to the moment when unrepairable fault (or faults) occurs. System operational time  $(T_{op})$ is reffered to as the time for which the system is working properly. For the non-repairable system we can state that the operational time before the first and only one fault occurence  $T_{op1}$  is equal to system lifetime  $T_{life}$ . When the system is affected by fault the time needed to its detection and localization by system test equipment should be assumed before fault mitigation is started. If Figure 2.10, the time needed to detect fault is denoted as  $T_{det}$ , time needed for fault localization as  $T_{loc}$  and fault mitigation time as as  $T_{mit}$ . The time needed for system repair consists of these 3 parts.

To simplify the evaluation of system dependability, several dependability statistic indicators have been introduced.

*Mean Time To Failure* (MTTF) is the expected (mean) time for a system to fail. It is a statistical value and the length of the observation interval for the calculation of MTTF must be infinite. This parameter can be evaluated as the average of all operational time periods (2.1).

$$MTTF = \frac{1}{n} \sum_{i=1}^{n} T_{opi}$$

(2.1)

Failure intensity  $(\lambda)$  shows the mean frequency of system failures. It can be derived from MTTF indicator (2.2).

$$\lambda = \frac{1}{MTTF} \tag{2.2}$$

Mean Time To Repair (MTTR) is the expected (mean) time for a system to be repaired. This can be evaluated as the average of all repair time periods (2.3).

$$MTTR = \frac{1}{n} \sum_{i=1}^{n} T_{deti} + T_{loci} + T_{miti}$$

(2.3)

Repair intensity  $(\mu)$  shows the mean frequency of system repairs. It can be derived from MTTR indicator (2.4).

$$\lambda = \frac{1}{MTTR} \tag{2.4}$$

Mean Time Between Failures (MTBF) is the mean elapsed time between inherent failures of a system (2.5).

$$MTBF = MTTF + MTTR \tag{2.5}$$

Figure 2.10: The chain of system states during its lifetime

#### 2.4.1 Reliability

The reliability R(t) of a system at time t is the probability that the system operates without a failure in the interval [0, t] under given operational conditions. The correct operation of system at time 0 is a premise. In other words, the reliability can be understood as an ability to continuously deliver correct service and meet requirements of implemented function during the given time period. This correct service ends in the moment of failure occurence. High reliability means that long time interval elapses before the first system failure occurs.

Since the reliability can be expressed as the probability of system run without failures before or at time t, we can define a random variable T as the time to failure and then express it by formula 2.6.

$$R(t) = P(T > t) \tag{2.6}$$

As the opposite to the reliability which expresses the probability of success, the unreliability Q(t) of a system at time t can be defined. It expresses the probability that the system will fail in the interval [0, t]. Again, the correct operation of system at time 0 is a premise. The reliability and the unreliability are related as shown in 2.7.

$$Q(t) = 1 - R(t) = P(T \le t)$$

(2.7)

Reliability is a function of time but the specification of time period can vary according to the system under consideration. The time of correct operation can be specified in time units such as hours, days or years or it can be stated for example as the number of correctly processed outputs until a fault can appear.

To model the reliability of (non-repairable) system, an exponential distribution is frequently used (2.8). There is also the possibility of using other distributions to model system reliability but this typically requires more detailed information on the system and a more detailed analysis. For most situations the exponential distribution is adequate.

$$R(t) = e^{-\mu t} \tag{2.8}$$

When the reliability function of system R(t) is known, the failure probability Q(t) (the unreliability of system) can be evaluated (2.7) and used to derive the failure density function f(t) (2.9). The failure density function f(t) is defined as the probability per unit of time

that the first failure of system will occur at time t. The correct operation of system at time 0 is a premise. Besides others, this density function can be used to determine the probability of failure occurence within time interval bounded by time  $t_0$  and  $t_1$  as shown at 2.10.

$$f(t) = \frac{dQ}{dt} = \mu e^{-\mu t} \tag{2.9}$$

$$Q(t_0 \to t_1) = \int_{t_0}^{t_1} f(t)dt = \mu \int_{t_0}^{t_1} e^{-\mu t}dt = e^{-\mu t_0} - e^{-\mu t_1}$$

(2.10)

In practice, the failure rate function is used to describe the reliability of system. The failure rate  $\lambda(t)$  is defined as the probability per unit time that the failure of system will occur at time t, given that the system was correctly operating at time 0 and has survived to time t. To define failure rate for the repairable system, this premise can be extended as the systems that do not need to survive in original state, but then they have to be repaired to fully operating state at time t.

$$\lambda(t) = \frac{f(t)}{R(t)} = \frac{f(t)}{1 - Q(t)}$$

(2.11)

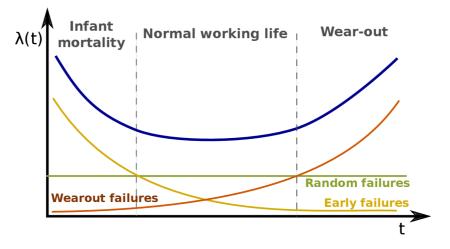

To evaluate the failure rate function  $\lambda(t)$ , the failure density function f(t) can be used (2.11). In practice, the failure rate is often measured by observing the correct operation of a system. Due to fact, that the failures do not occur frequently, it is often measured using many identical copies of a component or system. As the failure rate of a system depends on time, it can vary a lot over the life cycle of the system. It is often reported, that the failure rate has the shape of bathtub curve as shown in Figure 2.11.

Figure 2.11: The failure rate of a system during its lifetime

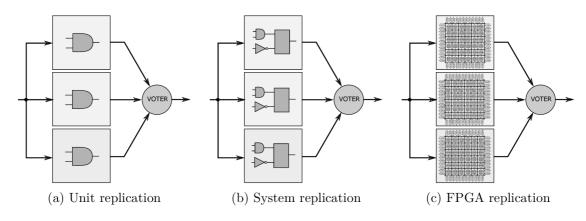

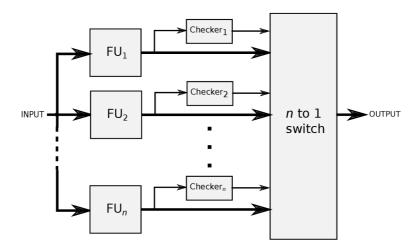

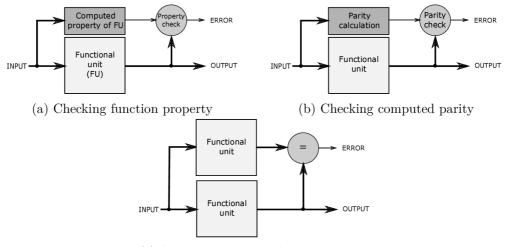

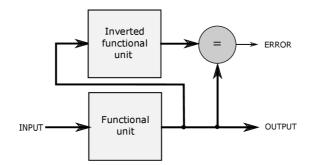

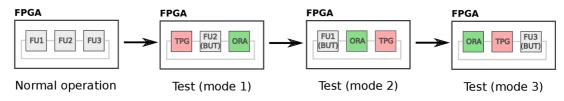

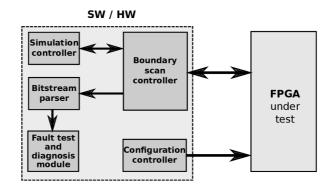

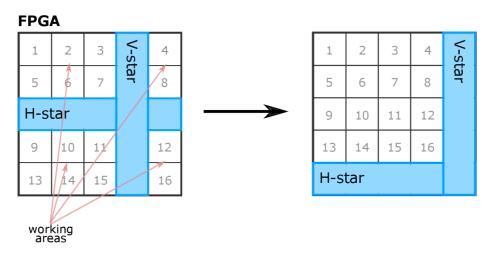

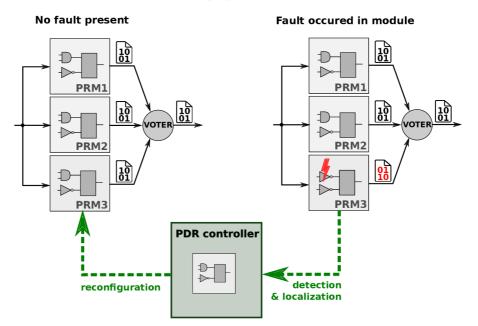

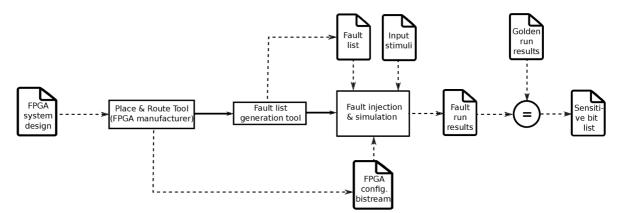

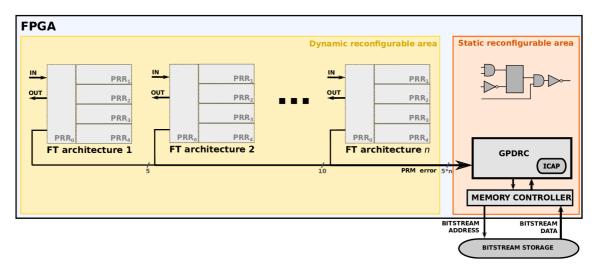

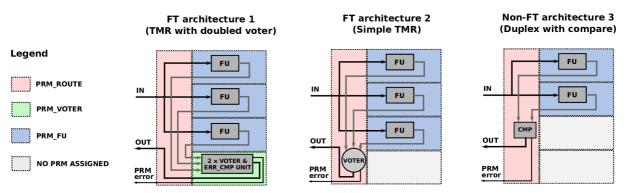

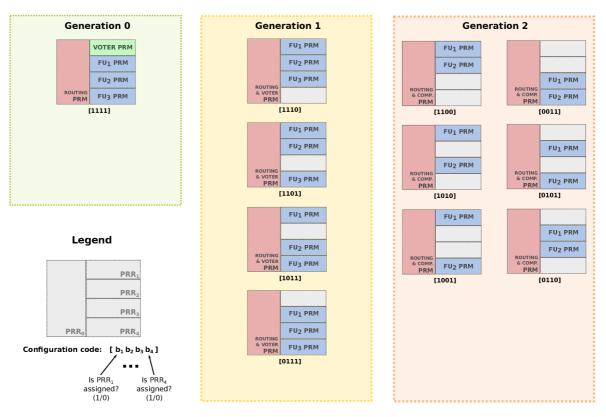

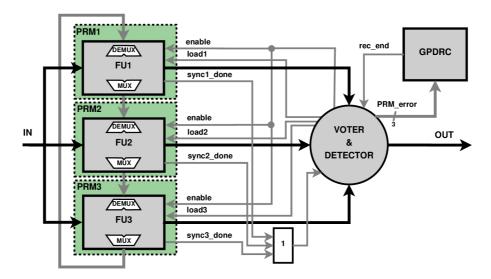

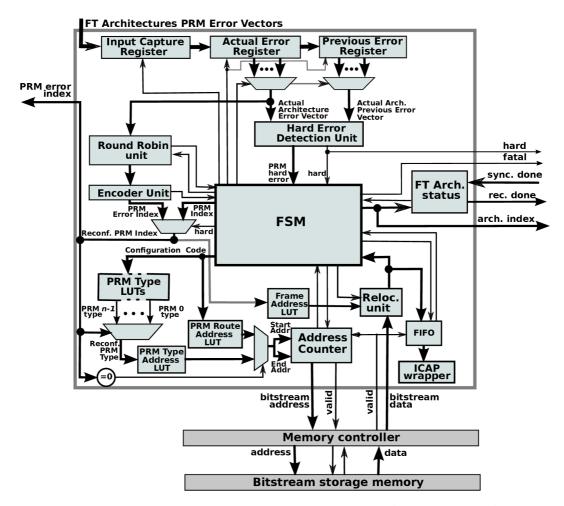

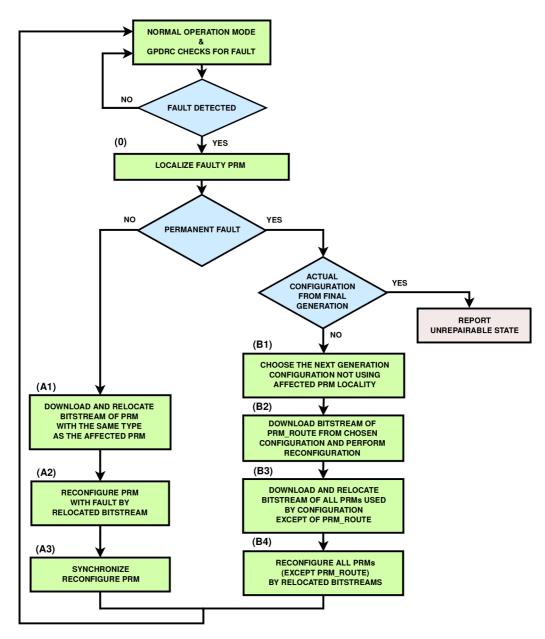

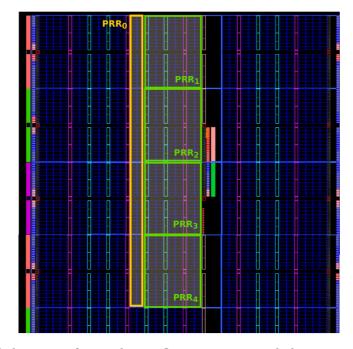

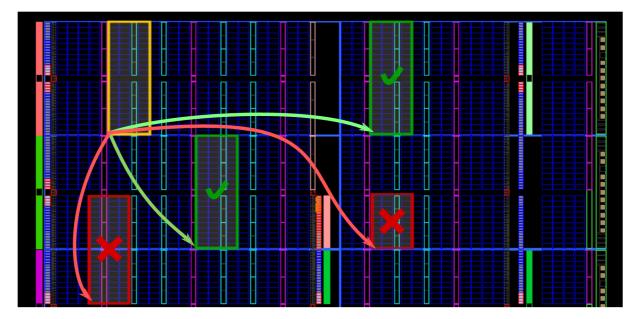

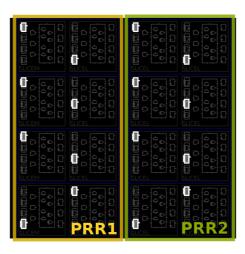

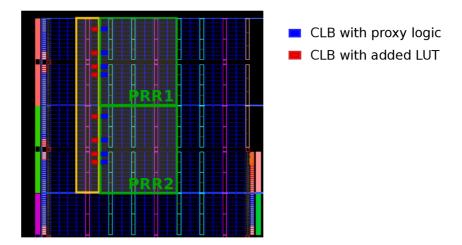

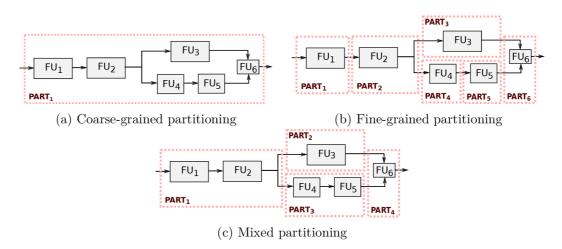

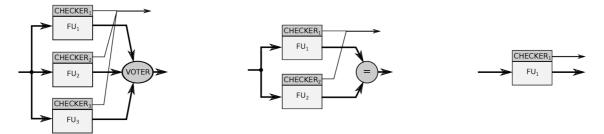

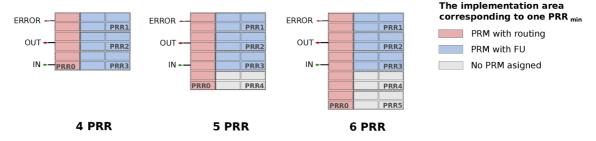

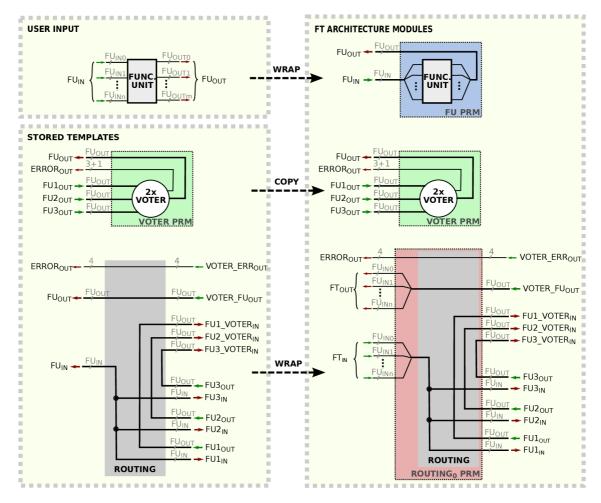

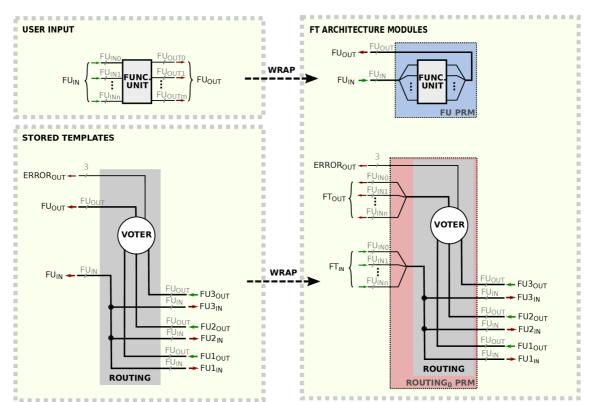

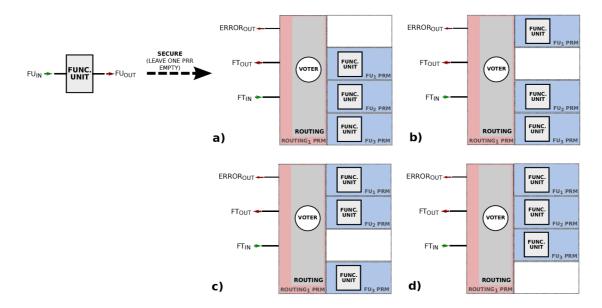

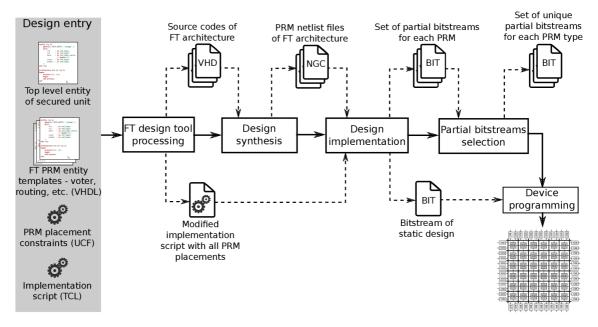

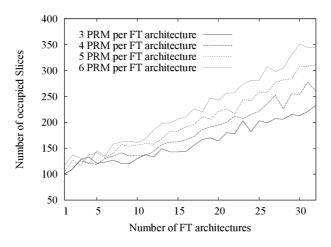

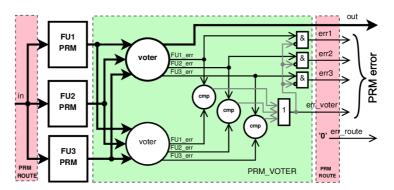

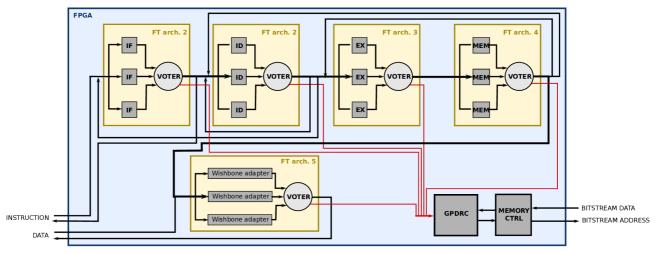

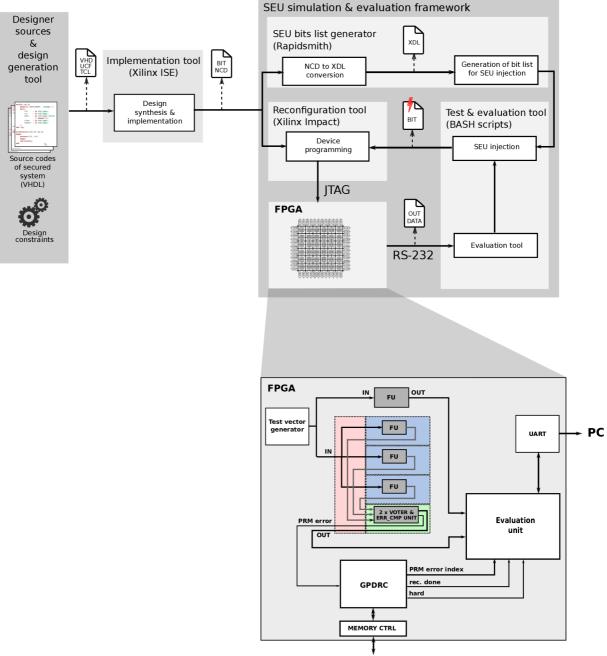

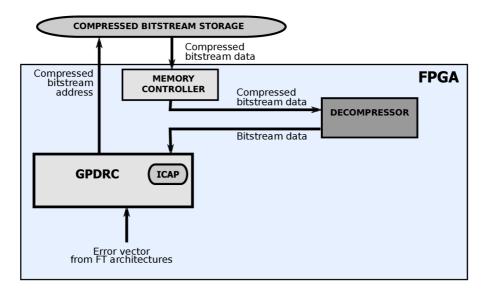

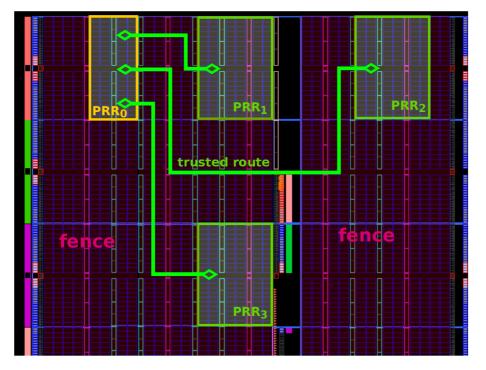

At the beginning of system lifetime, there is a high failure rate which is decreasing in time. This period is often called infant mortality or wear-in mode. Failures occuring during this period are typically caused by a variety of factors such as the occurence of defective parts, defects in materials, damages in handling, out of manufacturing tolerance, etc. To avoid this situation, manufacturers frequently perform burn-in process of the product in their factory to avoid such situations when failures from wear-in mode will happen in customer premises. The mitigation of these failures includes design improvement, care in materials selection and tightened production quality control.