## BRNO UNIVERSITY OF TECHNOLOGY

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

DEPARTMENT OF INTELLIGENT SYSTEMS ÚSTAV INTELIGENTNÍCH SYSTÉMŮ

## ANALYSIS OF ATTACKS ON (MICRO)CHIPS AND DE-VELOPMENT OF ENHANCEMENT OF THEIR ROBUST-NESS/SECURITY

ANALÝZA ÚTOKŮ NA (MIKRO)ČIPY A NÁVRH ZVÝŠENÍ JEJICH ODOLNOSTI/BEZPEČNOSTI

**EXTENDED ABSTRACT OF DOCTORAL THESIS** ROZŠÍŘENÝ ABSTRAKT DISERTAČNÍ PRÁCE

Ing. DOMINIK MALČÍK

AUTHOR AUTOR PRÁCE

SUPERVISOR prof. Ing., Dipl.-Ing. MARTIN DRAHANSKÝ, Ph.D. ŠKOLITEL

**BRNO 2019**

## Abstract

Nowadays, microchips are used virtually everywhere, from simple home devices to confidential military equipment. In many scenarios, sensitive data is being processed by these devices. For example, in the case of electronic personal documents, fingerprints, facial images, and personal data are processed by the chip; and in some cases also iris images. Auditing proclaimed functions and a level of security of such microchips is becoming a valued service. In this doctoral thesis, we present an experimentally proven process for the microscopic analysis of chips, feasible in a low-cost setup. The described process was demonstrated on a chip acquired from the Czech biometric passport—from extracting the chip out of the plastic card up to analysis of the acquired microscopic images. We investigated and evaluated various potentially viable methods for logic element recognition; without the employment of machine-learning. Additionally, hardware-oriented attacks are discussed and followed by proposals for countermeasures leading to the hindering of microscopic analysis.

## Abstrakt

S využitím mikročipů se dnes setkáváme prakticky na denní bázi, od jednoduchých zařízení pro domácí použití až po utajované vojenské vybavení. V mnoha případech navíc svěřujeme těmto zařízením velmi citlivá data, jako i v případě elektronických dokladů – otisky prstů, fotografie obličeje, osobní data; a v některých případech například i obraz oční duhovky. Ověření deklarované funkčnosti a míry zabezpečení takových mikročipů se tak stává žádanou službou. V rámci této disertační práce prezentujeme experimentálně ověřený proces mikroskopické analýzy mikročipů proveditelný v nízkonákladovém režimu. Popsaný proces jsme poté demonstrovali na čipu z českého biometrického pasu – od získání čipu z plastové karty až po jeho analýzu na základě získaných mikroskopických snímků. V rámci analýzy jsme prozkoumali a porovnali různé metody bez strojového učení potenciálně využitelné k rozpoznávání logických elementů. Dále jsme provedli zhodnocení aktuálních hardwarově orientovaných útoků na mikročipy. V návaznosti na toto zhodnocení jsme navrhli možná protiopatření zaměřená primárně na ztížení procesu mikroskopické analýzy.

## Keywords

Microchip, chip, chip package, deprocessing, dry etching, wet etching, security analysis of chips, microscopic analysis, SmartMX, MIFARE Classic.

## Klíčová slova

Mikročip, čip, pouzdro čipu, deprocesing, plasmatické leptání, chemické leptání, bezpečnostní analýza čipů, mikroskopická analýza, SmartMX, MIFARE Classic.

## Reference

MALČÍK, Dominik. Analysis of attacks on (micro)chips and development of enhancement of their robustness/security. Brno, 2019. Extended abstract of doctoral thesis. Brno University of Technology, Faculty of Information Technology. Supervisor prof. Ing., Dipl.-Ing. Martin Drahanský, Ph.D.

## Contents

| 1                | $\mathbf{Intr}$ | oduction 3                                                                                                                                               |  |  |  |  |

|------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                  | 1.1             | Motivation                                                                                                                                               |  |  |  |  |

|                  | 1.2             | Thesis Contribution                                                                                                                                      |  |  |  |  |

|                  | 1.3             | Thesis Organization                                                                                                                                      |  |  |  |  |

| 2 Research Goals |                 |                                                                                                                                                          |  |  |  |  |

| 3                | Mic             | roscopic Analysis 6                                                                                                                                      |  |  |  |  |

|                  | 3.1             | Obtaining Chips from Plastic Cards                                                                                                                       |  |  |  |  |

|                  | 3.2             | Chip Decapsulation                                                                                                                                       |  |  |  |  |

|                  |                 | 3.2.1 Chemical Approach for Removal of Plastic Packages                                                                                                  |  |  |  |  |

|                  |                 | 3.2.2 Grinding and Polishing of Plastic Packages                                                                                                         |  |  |  |  |

|                  | 3.3             | Chip Deprocessing                                                                                                                                        |  |  |  |  |

|                  |                 | 3.3.1 Cross-Section Analysis                                                                                                                             |  |  |  |  |

|                  |                 | 3.3.2 Chemical Deprocessing                                                                                                                              |  |  |  |  |

|                  | 3.4             | Layers Scanning 11                                                                                                                                       |  |  |  |  |

|                  |                 | 3.4.1 Processed Chips 11                                                                                                                                 |  |  |  |  |

|                  | 3.5             | Analysis of The Images                                                                                                                                   |  |  |  |  |

| <b>4</b>         | Ana             | lysis of The Czech Biometric Passport Chip 13                                                                                                            |  |  |  |  |

|                  | 4.1             | Extraction and Decapsulation                                                                                                                             |  |  |  |  |

|                  | 4.2             | Deprocessing $\ldots \ldots 14$                 |  |  |  |  |

|                  |                 | 4.2.1 Cross-Section Analysis                                                                                                                             |  |  |  |  |

|                  |                 | 4.2.2 Removing Layers $\ldots \ldots 14$ |  |  |  |  |

|                  | 4.3             | Image Scanning                                                                                                                                           |  |  |  |  |

|                  | 4.4             | Image Stitching                                                                                                                                          |  |  |  |  |

|                  | 4.5             | Analysis                                                                                                                                                 |  |  |  |  |

|                  |                 | 4.5.1 Bond Pads Identification                                                                                                                           |  |  |  |  |

|                  |                 | 4.5.2 Chip Segments Identification                                                                                                                       |  |  |  |  |

| <b>5</b>         | $\mathbf{Chi}$  | p Security Improvements 20                                                                                                                               |  |  |  |  |

|                  | 5.1             | Reverse Engineering Countermeasures                                                                                                                      |  |  |  |  |

|                  | 5.2             | Complex Integration and Camouflaging                                                                                                                     |  |  |  |  |

|                  |                 | 5.2.1 Heterogeneous Integration                                                                                                                          |  |  |  |  |

|                  |                 | 5.2.2 Cell Camouflaging 21                                                                                                                               |  |  |  |  |

|                  |                 | 5.2.3 3D Integration with Dummy Dies                                                                                                                     |  |  |  |  |

|                  | 5.3             | Active Tamper Detection                                                                                                                                  |  |  |  |  |

|                  |                 | 5.3.1 Active Tamper Detection with Active Memory Protection 22                                                                                           |  |  |  |  |

|    | $5.4 \\ 5.5 \\ 5.6 \\ 5.7$ | Active Defense Against Microprobing    Active Defense Against Microprobing      Disabling Backside Observations    Account of the second secon | 24<br>24<br>24<br>25<br>25 |

|----|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 6  | Soft                       | ware tools for Microscopic Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                         |

|    | 6.1                        | Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26                         |

|    | 6.2                        | Template Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                         |

|    |                            | 6.2.1 Template Matching Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28                         |

|    | 6.3                        | Feature Descriptors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28                         |

|    |                            | 6.3.1 Feature Descriptors Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                         |

|    | 6.4                        | Shape Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30                         |

|    |                            | 6.4.1 Shape Matching Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32                         |

|    | 6.5                        | Summary and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32                         |

| 7  | <b>Con</b><br>7.1          | nclusion<br>Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>33</b><br>34            |

| Bi | bliog                      | graphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36                         |

| А  | Rel                        | evant Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>45</b>                  |

|    | A.1                        | Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45                         |

|    |                            | A.1.1 Conferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                         |

|    |                            | A.1.2 Journals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45                         |

|    |                            | A.1.3 Submitted Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45                         |

| в  | Cur                        | riculum Vitae                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46                         |

| Б  | B.1                        | Education                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                         |

|    | B.1<br>B.2                 | Conferences, Summer Schools, Presentations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46                         |

|    | B.2<br>B.3                 | Projects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47                         |

|    | В.4                        | Teaching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47                         |

|    | B.5                        | Work Experience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48                         |

## Introduction

### 1.1 Motivation

Nowadays, many different types of chips are used virtually everywhere in the real world. There exist various incentives why one would like to see what is under the hood of a chip. Starting with QA departments of the chip producers, continuing over competition scanning, up to security auditing (i.e., auditing a device that was proclaimed secure). Such investigations are available in the market; however, these are mostly available in the commercial sector. The companies providing these services are keeping their know-how concealed. In the academic sphere, we are witnessing rather isolated attempts of such analyses scattered among various departments than a coherent work. We would like to contribute to the knowledge and capabilities maintained in academia with the mapping of the microscopic analysis in detail and, of course, with providing additional value to the status quo.

A few decades back, the chips were rather simple, and actually not that small. Observations, and even understanding of such devices, were possible with not much effort, i.e., we have decapsulated and deprocessed a single chip containing only four NAND cells. Analyses of these uncomplicated devices requires just an optical microscope and a few hours of work in a lab. On the contrary, dealing with contemporary chips used in biometric passports is a completely different challenge (and we have to admit that there are even more advanced chips, e.g., conventional CPUs, GPUs). The growing integration density and increasing die area result in the enormous complexity of the devices. Thus, it is impossible to apply manual only approaches. Moreover, the equipment capable of dealing with such advanced devices is very costly and thus not always available to low-cost attackers, as we are.

## **1.2** Thesis Contribution

Our focus laid mainly in the area of microscopic analysis of the microchips. We had to manage the whole process of chips decapsulation and deprocessing in order to get to the dies we wanted to investigate. Thus, the contributions of this thesis are broader than just a single topic. We truly believe that this thesis will help other institutions that want to tackle microscopic analysis of chips to manage the process based on the very detailed instructions and processes we present in this thesis. We believe that the main contributions are:

- A detailed description of methodologies for obtaining, decapsulation and deprocessing of the chips including improvement of the process of obtaining chips from thermoplastic compounds—plastic cards used for wrapping smartcard chips.

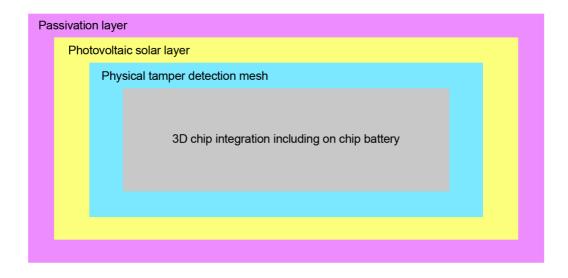

- Proposals for security improvements of the chips, focused primarily on hindering microscopic analysis. Techniques like 3D integration, MEMS, or battery-backed security fuses are presented in this thesis.

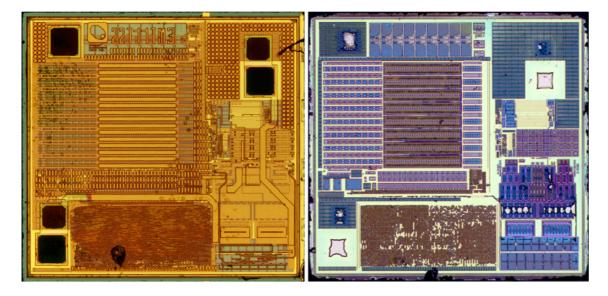

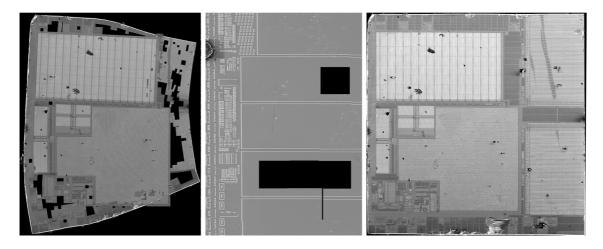

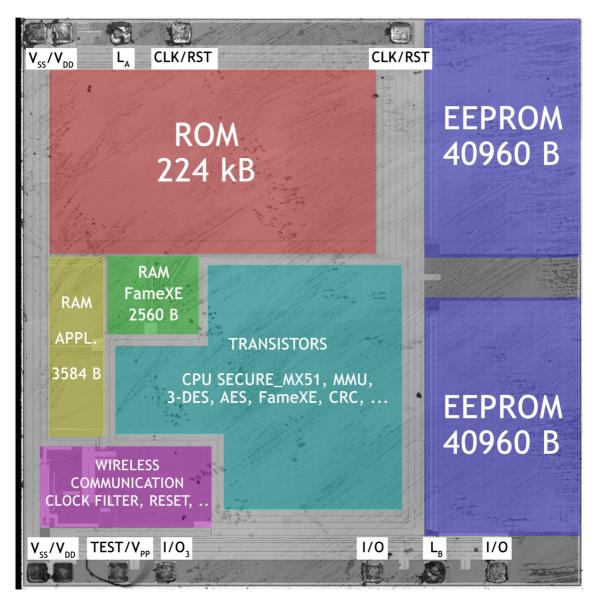

- Analysis of a chip belonging to the SmartMX family (used in biometric passports, ID cards, etc.) performed in a low-cost setup. Although not having regular access to needed equipment, we were able to completely analyze the chip construction—described in detail in this thesis, partially deprocess it and analyze the gained specimens.

- The comparison of methods that are not commonly used for processing of the chip silicon layer images without the employment of typically used machine-learning methods. Such an approach removes the need for complex training and verification data sets.

## 1.3 Thesis Organization

The text of this extended abstract consists of seven chapters. Chapter 2 states the research goals for the doctoral thesis. The analysis of microchips used in the e-documents is presented in detail in Chapter 3. Chapter 4 is devoted to the analysis of the Czech biometric passport chip. Possible attacks are discussed, and security enhancements are proposed in Chapter 5. Comparison of various methods potentially usable for logic elements recognition without the employment of learning approaches is presented in Chapter 6. Finally, Chapter 7 provides a final summary of the work with a conclusion and future work proposals.

## **Research Goals**

This doctoral thesis is focused on microscopic analysis of chips in general, and subsequently on all stages—decapsulation; deprocessing; image acquisition; image postprocessing; and analysis. The main goals of the doctoral thesis are:

- Microscopic analysis process:

- Decapsulation of chips.

- Deprocessing of chips.

- Acquisition of the layers with the use of microscopes.

- Analysis—manual analysis and computer-aided analysis.

- Performing microscopic analysis of the Czech biometric passport chip.

- Overview of feasible hardware attacks on microchips.

- Proposals for chips' security improvements.

One of the aims of this doctoral thesis is to prepare a precise methodology usable for microscopic analysis. It will require inter-disciplinary work, including regular visits to chemical and QA laboratories. Within the thesis, we plan to perform the experiments on our own as far as possible. This will enable us to describe the processes in detail in order to provide a proven approach to the microscopic analysis. After creating the methodologies for decapsulation and deprocessing that are feasible in our low-cost setup, the methodologies will be verified by repeated experiments on various chips—first, we intend to use very simple chips in classic packages, and then move on to smartcard chips, e.g., MIFARE Classic, MIFARE Ultralight, and MIFARE DESfire. The microscopic analysis methodology will be completed with an image acquisition process performed with appropriate microscopy, processing of the acquired images, and the image analysis supported by software or algorithmic approaches.

The next aim is to perform microscopic analysis of the chips used in Czech biometric passport implementation. These chips are still in practical use—traveling with Czech citizens virtually all around the globe.

Furthermore, based on the research and knowledge that will be gained while carrying out the experiments and during the theoretical study of available attack scenarios, we will propose possible improvements to the chips' security. This section will primarily aim at hardware-oriented attacks related to microscopic analysis.

## **Microscopic Analysis**

In this chapter, we will go through the whole process of microscopic analysis as we did in our experiments. We will deal with all parts from obtaining the chips up to the final analysis of the acquired images. All of these steps have to be mastered in order to be able to succeed with microscopic analysis performed from scratch<sup>1</sup>.

## 3.1 Obtaining Chips from Plastic Cards

Many RFID chips and security-oriented chips are stored in plastic cards. This is also the case for biometric passports or other personal documents. First, parts of the plastic cards with the chips inside have to be cut out from the rest of the plastic cards (see Fig. 3.1). Then, extraction of the encapsulated chips from the plastic cover is carried out. In the early stages, we used only acetone bath in a beaker at normal room temperature. The extraction took several minutes or even tens of minutes. The plastic card was slowly becoming pliable, and it was possible to peel the plastic layers off one after another. We improved the process with the use of a boiling nest (displayed in Fig. 3.1). The time of extraction got shortened to 1–3 minutes per piece. We heated the acetone to its boiling temperature (slightly above 50 °C), the plastic compound was then almost immediately removable. We highly recommend using plastic gloves.

### 3.2 Chip Decapsulation

For the purpose of chips decapsulation, two main approaches are commonly presented etching and grinding (sometimes stated as polishing). Both are specific, and it is always felicitous to have the capability of performing both. There are several books dealing especially with the chip packages and the related topics, e.g., [73], [17], [78], [8].

It can be said, very briefly, that there are three main types of common chip packages with respect to their material—metal, ceramic and plastic. The most important category for us is the plastic one. These packages are widely used (also because of their low price) and are often suitable for most of the ordinary integrated circuits.

We decided to follow the mainstream packages in this thesis, the plastic packages. The effective approach of obtaining bare chips out of plastic packages with the use of sulphuric and nitric acids was performed within the scope of the Brno University of Technology in cooperation with Faculty of Chemistry and is described herein. [50]

<sup>&</sup>lt;sup>1</sup>This was exactly our scenario, building all the knowledge at our faculty completely from scratch.

Figure 3.1: Left: Boiling nest with acetone bath. Middle: Two beakers with acids with the decapsulation process is progress in the left one. Right: The result of the decapsulation process—bare chips on their original pads. (Source: author's work.)

#### 3.2.1 Chemical Approach for Removal of Plastic Packages

The chemical approach is usually more convenient compared to the other ways of removing plastic packages, because of its simplicity, low time requirements, low price and availability of the chemicals involved. The fact is also that the chemicals are chosen in a manner that they react only with the plastic compounds—the danger of damaging the sample surface is then minimal because the surface of the chip is protected by a passivation layer. There exist different variants of the chemical approach that make use of the same acids, but mostly in a different step order or acids ratio [16]. However, some of them are totally dissimilar, i.e., another technique that is based on using resin instead of acids (briefly described in [67]). It has a significant drawback—it takes a lot of time. In fact, it is not recommended to follow this approach in a chemical lab, because resin vapors can foul up the exhaust. Moreover, the temperature of resin during the etching process should be really high, approx. 350 °C. This temperature may cause serious damage to the chips. On the other hand, the use of dangerous acids is completely avoided in this scenario. [50], [77], [76], [47]

As mentioned above, in our case, there is a need for cooperation with a chemical facility, because we cannot avoid working with chemicals. Let us assume that all the next steps take place in a properly-equipped chemical laboratory. At least a fume cupboard, a chemical sink, and personal protective equipment should be available for the etching process. Passed safety training is also a must. It is strongly recommended to proceed very cautiously while observing the chemical laboratory rules to avoid any injuries or damage to the laboratory equipment or to the chips.

#### The Ratio of Nitric Acid to Sulphuric Acid

Prior to the beginning of the etching itself, it has to be decided what is expected as a result. According to our needs, the correct ratio of the acids mixture has to be chosen. The result is affected not only by the ratio of the acid, but also by the time duration of the active etching (the time period when the specimen is inside the acid bath) and also by the temperature of the acids. The ratio is always stated as nitric acid to sulphuric acid (the recommended approx. temperature is mentioned in brackets) [49]. Length of active etching has to be determined experimentally for each type of package.

- 5:1–3:1 (ca. 90–94 °C)—preservation of wire bonds from the lead frame to the chip.

- 2:1–1:1 (ca. 90–94 °C)—faster, cheaper, and a more aggressive decapsulation.

- 0:1 (up to ca. 270 °C)—to etch very resistant molding compounds, very aggressive.

#### Whole-Package Decapsulation Process.

First, four beakers should be prepared. Two beakers should be half-filled with the acids in the correct ratio (see Chapter 3.2.1). The third beaker should be half-filled with acetone, and the last one with demineralized water. The cooker must be placed into a fume cupboard because of the production of dangerous vapors. Other recommended equipment should be placed nearby the fume cupboard or even inside if there is enough room for all the items. Only the beakers with acids need to be placed on the cooker in order to reach the desired working temperature. The other steps of the whole process should take place out of the cooker.

The major etching should be performed in the first beaker with the acids. The acids will become non-transparent soon due to the presence of etched molding compounds. The recommendation is to inspect the level of decapsulation during the process often periodically. When the process is almost complete, it is better to use the second beaker with the transparent acids to do the fine etching. It is necessary to monitor the progress permanently at this point. The transparent acid is ideal for this purpose. We do not recommend leaving the specimens in the acid bath longer than is necessary—the lower layers could be damaged by the acid because these layers are usually not protected along the chip edges and thus so-called underetching can occur.

When the chip is bared, it should be washed in the beaker with acetone. In cases where the chip surface is bigger than 5 mm<sup>2</sup>, we recommend using demineralized water first, acetone and demineralized water again due to safety reasons—a bigger amount of the acid left on the chip can react with acetone. Then, the specimen should be rinsed with flowing demineralized water, and it should be put inside another beaker with demineralized water afterward. The beaker with the demineralized water and the chip or with more chips, as the case may be, should be placed into an ultrasonic cleaner for up to two minutes in the case where there is only one chip in the beaker or for ca. thirty seconds in the case when there are more chips in that beaker. With little exaggeration, the chips act as emery paper to each other. Then a final check should take place. If everything seems to be alright, the chips should be dried with filter paper or nitrogen flow. If there is any problem with the cleanliness of the chip surface or similar, the entire process can be repeated [49].

#### **Etching of Specific Packaging Part**

A useful approach for some use cases is to etch out only a specific part of the chip package. The entire chip is preserved, and hence, it can be attached to other components as usually. Because of the manual dosing of acid drops to the specific area via a dropper, this process is more demanding. First, a little hollow is made in the surface of the chip, approx. in the center of the area designated for etching. Then, the drops of sulphuric acid are manually applied to the chosen location. Nitric acid is mostly not used in this approach. There has to be a short period of inactivity between the applications of the acid drops to allow reaction with the surface. [49]

#### 3.2.2 Grinding and Polishing of Plastic Packages

The grinding and polishing approach is suitable in cases where we cannot apply the chemicals, or the chip package allows the use of a grinder with its advantages, i.e., the chip is placed deeper in the package and there is a gap above the chip—in that case the wirebonds can be easily preserved also with use of grinder. It is necessary to proceed cautiously to avoid contact of the grinder with the surface of the chip or with wirebonds. For this reason, it is recommended to use an X-ray to inspect the starting situation and then the current level of decapsulation periodically. [50], [77], [76], [47]

### 3.3 Chip Deprocessing

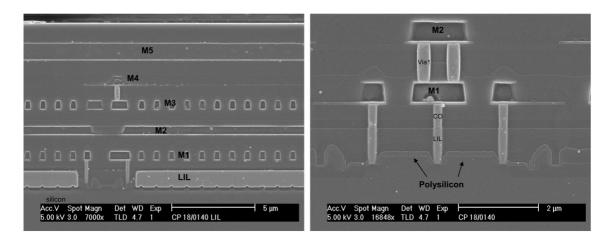

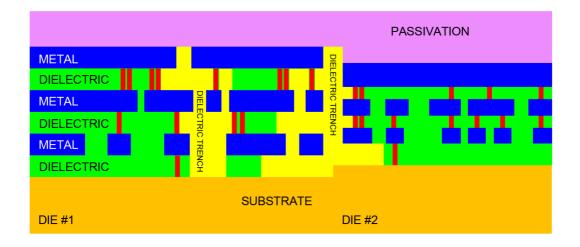

Each conventional chip is a composition of different oxide and metal layers above one transistor layer that is formed on the silicon substrate. Nowadays, we can also encounter various 2.5D or 3D layouts, these are way beyond our capabilities, and thus, we focus on conventional layouts in this thesis. The layers across producers are made of various compounds with respect to the desired functionality and needed properties of the whole layout.

The chip deprocessing (delayering) involves three main techniques: dry etching (plasma etching), wet etching (using different types of chemicals) and polishing. In any case, the best practice is to start with a cross-section analysis, including the thickness of layers measurement and materials analysis. Only after the information is harvested from the cross-section analysis, the correct procedure can be created and carried out.

Although a suitable chemical procedure can be found for each layer, it is sometimes not possible to choose wet etching because of the high risk of damaging other layers, i.e., an underetching problem. In these cases, it is still possible to make progress with a special grinder (capable of parallel polishing) and a decent level of skillfulness. Unfortunately, we were unable to reach such a special grinder within our partners. [51]

#### 3.3.1 Cross-Section Analysis

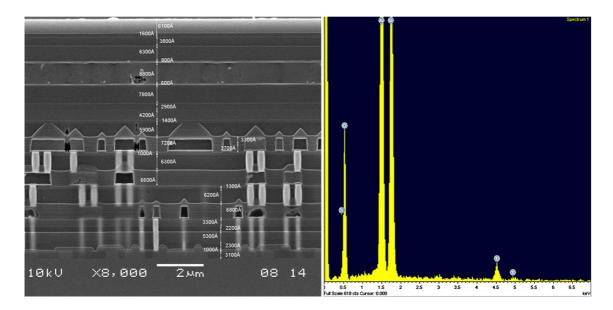

Virtually all laboratory grinder may be suitable for preparation of a specimen cross-section. It is convenient to prepare more cross-sections of one chip type always in a different position in order to gain more information about that chip. When the results are satisfactory, we use an electron microscope to observe the layers in more detail (displayed in Fig. 3.2).

Displaying cross-section immediately after grinding provides the image with hard-todistinguish borders of some layers and low distinction among these layers. Thus, to make the observability better, there are various etchants used for finishing the sample before scanning. For oxide layers,  $NH_4F$ ,  $CH_3COOH$ ,  $H_2O$ , and HF can be used; for diffusion semiconductor layers,  $HNO_3$  and HF can be used [84]. Recent FIB devices (i.e., TESCAN FERA3) allow for some limited use of this wet etching directly in-situ, however only with some of the chemicals supported.

After the cross-section is made, the next step is to employ one of the spectrometric techniques to acquire the elements' composition. For example, an electron microscope equipped with an X-ray detector can provide such information—see Fig. 3.2. A precise

Figure 3.2: Left: Detailed cross-section of NXP P5CD080 V0B chip with measurements of layers given in Angstrom units (1 Å = 0.1 nm). Right: Energy-dispersive X-ray spectroscopy (EDX) of a top layer of NXP P5CD080 V0B chip. (Source: author's work.)

deprocessing procedure can be prepared according to the composition and thickness of each layer.

#### 3.3.2 Chemical Deprocessing

For the complete process, it is necessary to have at least two specimens of the chip. At least one specimen is needed for the cross-section analysis and the second one for the main deprocessing. The second chip can be deprocessed according to the information gained from the first step. After removal of each layer, we have to acquire images of the layer with an appropriate microscope before we proceed to remove the next one. However, we strongly recommend preparing more samples than just two. Performing such analysis with only the two samples is not very common and not likely to be successful in real-life. The recommendation is to proceed with ten or more samples, to be able to prepare each sample to a different level of deprocessing—one with preserved passivation, one with removed passivation, one with a removed first metal layer, etc. [51]

#### **Deprocessing of Common Layers**

With the outcome of the cross-section analysis, an exact sequence of steps can be prepared in order to get to the coveted deprocessed chip. The form of the whole decomposition process naturally depends on our objectives. Usually, pictures of bare transistors and interconnections are desired. [51]

#### Passivation

The very first layer on the top of the chips is mostly a passivation layer—a kind of protection against mechanical and electromagnetic effects of the environment. To remove this layer, it is recommended to use plasma etching, so-called dry etching. The whole process takes about 45 minutes with old plasma etcher TESLA 214 VT

that was available at our disposal. The actual plasma etching lasts only 4 minutes out of the mentioned time period. The rest of the time is devoted to preparing conditions necessary for performing this procedure.

#### Conductive compounds

Conductive layers that are made of aluminum compounds can be taken away by the application of *phosphoric acid etching mixture*, *PEWS* 765-140-57-36<sup>2</sup>. The recommended working temperature is 50 °C; the common time of the bath should be from 2 to 6 minutes, depending on the layer thickness. There exist also other commercial etchants designated for etching conductive layers, i.e., KMG Mix attaque phosphorique (mix of acetic acid, nitric acid and phosphoric acid), recommended working temperature is also around 50 °C. More of such commercial products can be found in the market.

#### Dielectric compounds

A special chemical mixture is also available for removing oxide compounds—insulating material. Precisely, the mixture consists of ammonium fluoride and hydrofluoric acid in ratio 7:1. The working temperature is 30 °C; the common time of the bath should be from 2 to 6 minutes.

#### Deprocessing a chip down to silicon

To deprocess a chip completely down to silicon, there exists one reliable method employing hydrofluoric acid (HF), 50% concentration. It is usually used at ambient temperature. The HF acid reacts with metals and also with oxides. This acid is not selective and is often used just for this purpose to remove all layers above the silicon. Duration of the etching depends on the chip composition and the amount of material above the silicon. [20]

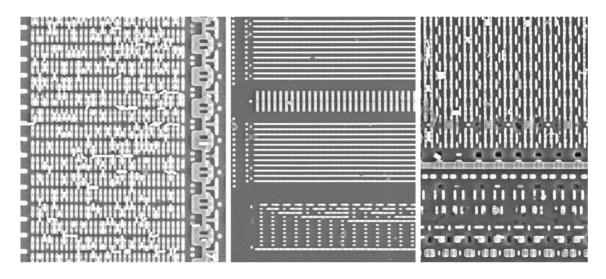

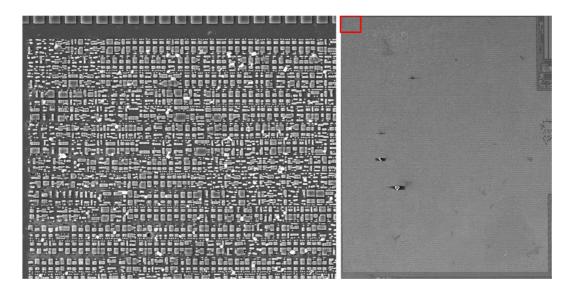

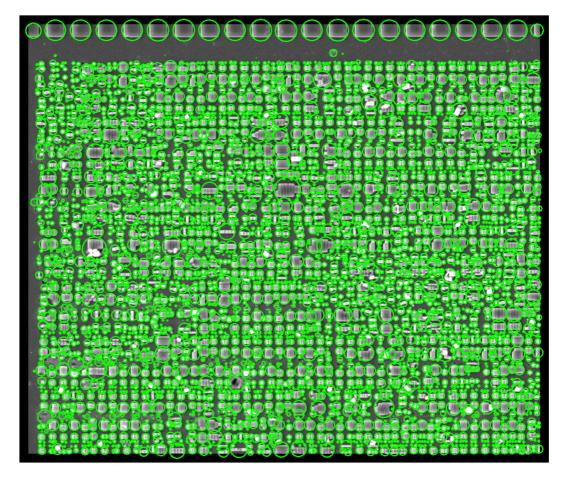

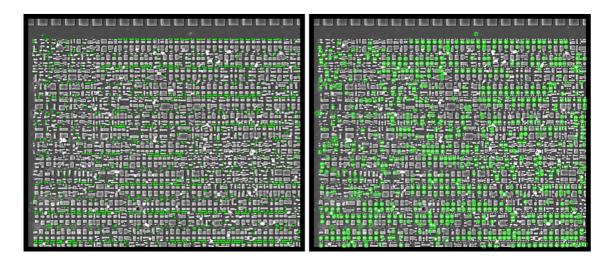

### 3.4 Layers Scanning