# **BRNO UNIVERSITY OF TECHNOLOGY**

Faculty of Electrical Engineering and Communication

# LOW VOLTAGE CURRENT-CONVEYORS DESIGN TECHNIQUES

## **DISSERTATION THESIS**

AUTHOR Issa Eldbib, MSc.

SUPERVISOR prof. Ing. Jaromír Brzobohatý, CSc.

Brno 2008

# LICENČNÍ SMLOUVA POSKYTOVANÁ K VÝKONU PRÁVA UŽÍT ŠKOLNÍ DÍLO

uzavřená mezi smluvními stranami:

| 1. Pan/pani   | mána a m¥iimani:                   | Logo Eldhib                                 |

|---------------|------------------------------------|---------------------------------------------|

|               | méno a příjmení:<br>Bytem:         | Issa Eldbib<br>Brno, Czech Republic         |

| Ν             | Narozen/a (datum a místo)          | : 27.01.1968, Sabha, Libya                  |

|               |                                    | a                                           |

| 2. Vysoké učo | ení technické v Brně               |                                             |

|               | Faculty of Electrical E            | ngineering and Communication                |

|               | se sídlem <b>Údolní 244/5</b> .    | 3, CZ-60200 Brno, Czech Republic            |

|               | jejímž jménem jedná na             | základě písemného pověření děkanem fakulty: |

|               | Prof. Ing. Radimír Vrba            | ı, CSc.                                     |

|               |                                    | Článek 1                                    |

|               |                                    | Specifikace školního díla                   |

|               |                                    |                                             |

| 1. Předměten  | m této smlouvy je vysokoš          | kolská kvalifikační práce (VŠKP):           |

|               | ⊠ disertační práce                 |                                             |

|               | □ bakalářská práce                 |                                             |

|               | □ diplomová práce                  |                                             |

|               | □ jiná práce, jejíž druh           | je specifikován jako                        |

|               |                                    |                                             |

|               | (dále jen VŠKP nebo dí             | lo)                                         |

| Název VŠKP    | : LOW VOLTAGE CU                   | URRENT-CONVEYORS DESIGN TECHNIQUES          |

| Vedoucí/ ško  | litel VŠKP: <b>prof. Ing. Ja</b> i | romír Brzobobatý. CSc                       |

| . Padadi dito | ,                                  |                                             |

| Í Leta        | <b>D</b> ( )                       | CM' and a december                          |

| Ústav:        | Department of                      | f Microelectronics                          |

VŠKP odevzdal autor nabyvateli v\*:

☑ elektronické formě – počet exemplářů 1

- 2. Autor prohlašuje, že vytvořil samostatnou vlastní tvůrčí činností dílo shora popsané a specifikované. Autor dále prohlašuje, že při zpracovávání díla se sám nedostal do rozporu s autorským zákonem a předpisy souvisejícími a že je dílo dílem původním.

- 3. Dílo je chráněno jako dílo dle autorského zákona v platném znění.

- 4. Autor potvrzuje, že listinná a elektronická verze díla je identická.

#### Článek 2

#### Udělení licenčního oprávnění

- 1. Autor touto smlouvou poskytuje nabyvateli oprávnění (licenci) k výkonu práva uvedené dílo nevýdělečně užít, archivovat a zpřístupnit ke studijním, výukovým a výzkumným účelům včetně pořizovaní výpisů, opisů a rozmnoženin.

- 2. Licence je poskytována celosvětově, pro celou dobu trvání autorských a majetkových práv k dílu.

- 3. Autor souhlasí se zveřejněním díla v databázi přístupné v mezinárodní síti

- $\hfill\Box$ ihned po uzavření této smlouvy

- □ 1 rok po uzavření této smlouvy

- □ 3 roky po uzavření této smlouvy

- □ 5 let po uzavření této smlouvy

- $\hfill\Box$  10 let po uzavření této smlouvy

- (z důvodu utajení v něm obsažených informací)

- 4. Nevýdělečné zveřejňování díla nabyvatelem v souladu s ustanovením § 47b zákona č. 111/ 1998 Sb., v platném znění, nevyžaduje licenci a nabyvatel je k němu povinen a oprávněn ze zákona.

<sup>\*</sup> hodící se zaškrtněte

#### Článek 3

#### Závěrečná stanovení

- 1. Smlouva je sepsána ve pět vyhotoveních s platností originálu, přičemž po jednom vyhotovení obdrží autor a nabyvatel, další vyhotovení je vloženo do VŠKP.

- 2. Vztahy mezi smluvními stranami vzniklé a neupravené touto smlouvou se řídí autorským zákonem, občanským zákoníkem, vysokoškolským zákonem, zákonem o archivnictví, v platném znění a popř. dalšími právními předpisy.

- 3. Licenční smlouva byla uzavřena na základě svobodné a pravé vůle smluvních stran, s plným porozuměním jejímu textu i důsledkům, nikoliv v tísni a za nápadně nevýhodných podmínek.

- 4. Licenční smlouva nabývá platnosti a účinnosti dnem jejího podpisu oběma smluvními stranami.

| V Brně dne: |           |

|-------------|-----------|

|             |           |

|             |           |

|             |           |

| Autor       | Nabyvatel |

#### **ABSTRACT**

This thesis work discusses the low-voltage current-mode CCII analog circuits and their various aspects. The need of high speed, high performance, low power circuits because of the advent of the portable electronic and mobile communication systems and difficulties faced in achieving that in today, this need for high performance LV circuits give encourages the analog designers to look for new circuit architectures, and new LV techniques.

Self cascode and bulk-driven techniques can help to produce efficient LV circuits with reduced power supply restrictions are explained, some of the basic building blocks such as current mirrors, differential pairs structures capable to operate in LV are explored and discussed. The basic device level techniques also play important role in the design of smarter and efficient circuits; some of those techniques have also been discussed here.

Designing CCII using low voltage techniques is the core part in this thesis, their advantages are discussed here and a comparison with the conventional mode circuits has been presented, The principle and the implementation of the most common CCII-based operational amplifier circuits has been described.

#### **KEYWORDS**

Low Voltage Current Conveyor, Bulk-Driven Mosfet, Self Cascode Mosfet, Bulk-Driven Current Conveyor, self cascode current conveyor, Current Conveyor Based Filters.

## **PROHLÁŠENÍ**

Prohlašuji, že svou disertační práci na téma "LOW VOLTAGE CURRENT-CONVEYORS DESIGN TECHNIQUES" jsem vypracoval samostatně pod vedením vedoucího disertační práce a s použitím odborné literatury a dalších informačních zdrojů, které jsou všechny citovány v práci a uvedeny v seznamu literatury na konci práce.

Jako autor uvedené disertační práce dále prohlašuji, že v souvislosti s vytvořením této disertační práce jsem neporušil autorská práva třetích osob, zejména jsem nezasáhl nedovoleným způsobem do cizích autorských práv osobnostních a jsem si plně vědom následků porušení ustanovení § 11 a následujících autorského zákona č. 121/2000 Sb., včetně možných trestněprávních důsledků vyplývajících z ustanovení § 152 trestního zákona č. 140/1961 Sb."

| V Brně dne |                 |

|------------|-----------------|

|            |                 |

|            | (podpis autora) |

# **Acknowledgements**

I would like to express my appreciation to all those whom have made this thesis a reality. My greatest appreciation and thanks goes out to my supervisor, Prof. Jaromír Brzobohatý Ph.D, MSc for the support and advice given throughout the years of the research. I would also like to thank Prof. Vladislav Musil, Ph.D, MSc, for his guidance and time for reviewing the thesis. My appreciation goes out also to everyone from the Microelectronics Department.

## **List of Abbreviations**

CC Current Conveyor

CCI First Generation Current Conveyor

CCII Second Generation Current Conveyor

CCIII Third Generation Current Conveyor

CCCII Current Controlled Current Conveyor

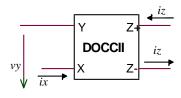

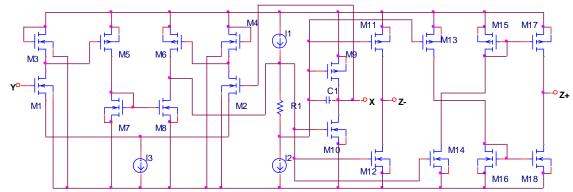

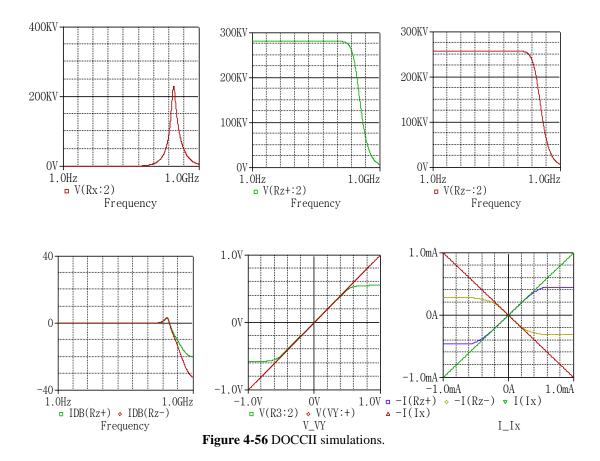

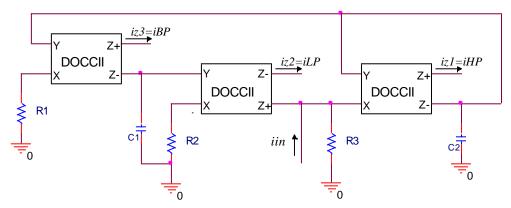

DOCC Dual Output Current Conveyor

CGCCII Current Gain Controlled Conveyor

**DVCCII** Differential Voltage Current Conveyors

FDCCII Fully Differential Current Conveyors

N Network

Na Adjoint Network

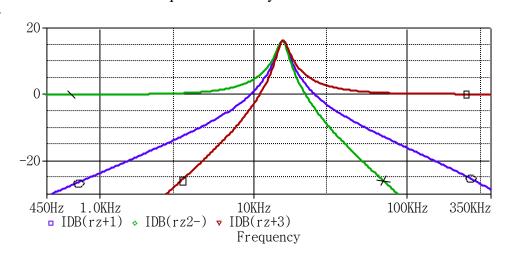

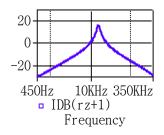

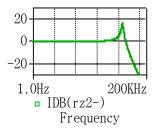

*LP* Low-Pass

HP High-Pass

BP Band-Pass

OTA Operational Transconductance Amplifier

# List of symbols

| BW         | Bandwidth [Hz]                                            |

|------------|-----------------------------------------------------------|

| C          | Capacitance [F]                                           |

| $C_{BD}$   | Bulk-drain capacitance [F]                                |

| $C_{BS}$   | Bulk-source capacitance [F]                               |

| $C_{GB}$   | Gate-bulk capacitance [F]                                 |

| $C_{GD}$   | Gate-drain capacitance [F]                                |

| $C_{GS}$   | Gate-source capacitance [F]                               |

| $C_{OX}$   | Thin oxide capacitance per unit area [F.m <sup>-2</sup> ] |

| $C_{GB0}$  | Gate-bulk capacitance [F.m <sup>-1</sup> ]                |

| $C_{GD0}$  | Gate-drain overlap capacitance [F.m <sup>-1</sup> ]       |

| $C_{GS0}$  | Gate-source overlap capacitance [F.m <sup>-1</sup> ]      |

| $C_L$      | Load capacitor [F]                                        |

| CMR        | Common mode range [V]                                     |

| CMRR       | Common mode rejection ratio [dB]                          |

| f          | Frequency [Hz]                                            |

| $f_T$      | Unity gain frequency [Hz]                                 |

| GBW        | Gain-bandwidth product[Hz]                                |

| $g_m$      | Gate transconductance [S]                                 |

| $g_{mb}$   | Bulk transconductance [S]                                 |

| γ          | Bulk threshold parameter [V <sup>1/2</sup> ]              |

| I          | Current [A]                                               |

| $I_B$      | Bulk current [A]                                          |

| $I_D$      | Drain current [A]                                         |

| Ix         | X node current (input current), [A]                       |

| <b>I</b> z | Z node current (output current) [A]                       |

| k          | Boltzmann's constant [J.K <sup>-1</sup> ]                 |

| K          | Transconductance parameter [A.V <sup>-2</sup> ]           |

| L          | Channel length [m]                                        |

| $L_D$      | Lateral diffusion [m]                                     |

| λ          | Channel length modulation coefficient [V <sup>-1</sup> ]  |

| R          | Resistance $[\Omega]$                                     |

| rx         | $X$ node impedance[ $\Omega$ ]                            |

|            |                                                           |

rx

rz Z node impedance[ $\Omega$ ] ry Y node impedance[ $\Omega$ ]

ro Output resistance  $[\Omega]$

$V_{DD}$  Positive supply voltage [V]

$V_{BS}$  Bulk-source voltage [V]  $V_{DS}$  Drain-source voltage [V]

$V_{dsat}$  Saturation voltage [V]  $V_{GS}$  Gate-source voltage [V]

$V_T$  Threshold voltage [V]

$V_{T0}$  Threshold voltage at  $V_{BS}=0$  [V]

$V_{SS}$  Negative supply voltage [V]

vy Y node voltage (input voltage) [V]

vx X node voltage [V]

W Channel width [m]

# List of figures

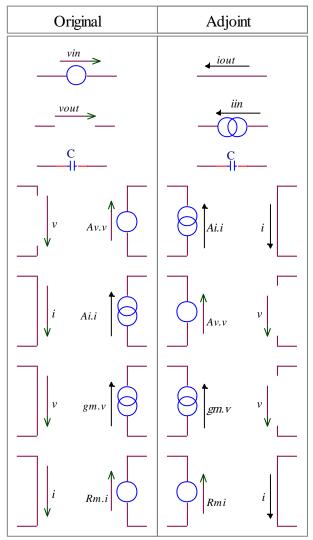

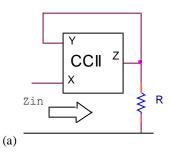

| Figure 1-1 Inter-reciprocal networks N and Na                                       | 2                |

|-------------------------------------------------------------------------------------|------------------|

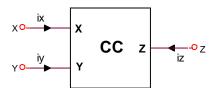

| Figure 1-2 Current conveyor symbol.                                                 | 4                |

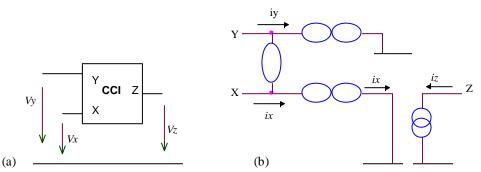

| Figure 2-1: a) The first generation current-conveyor symbol and its signal definiti | ons. b) Nullator |

| norator CCI complete scheme.                                                        |                  |

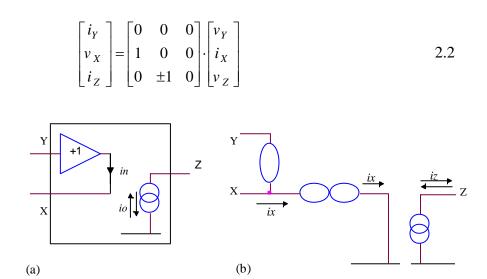

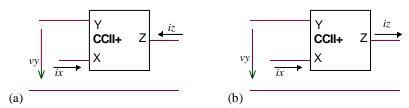

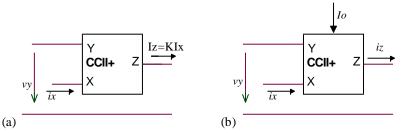

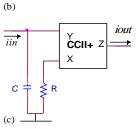

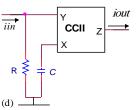

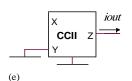

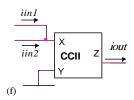

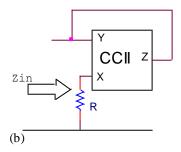

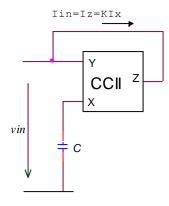

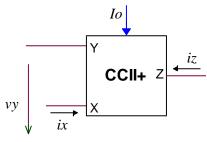

| Figure 2-2: a) The principle of the second generation current conveyor: CCII+,iz=   | ix. CCII-,-iz=ix |

| b) Nullator-norator CCII complete scheme                                            |                  |

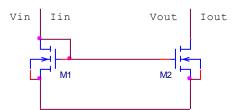

| Figure 2-3 Positive and negative CCII basic blocks.                                 |                  |

| Figure 2-4 Dual output CCII basic block.                                            |                  |

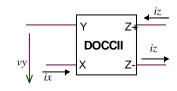

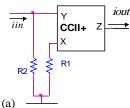

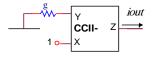

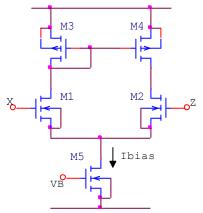

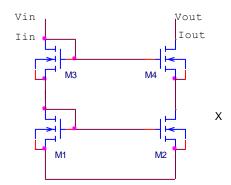

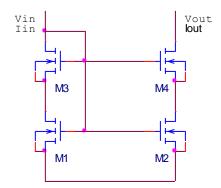

| Figure 2-5 Class A CCIIs a) CCII- b) CCII+                                          | 9                |

| Figure 2-6 Class AB CCIIs: a) CCII+ and b) CCII-                                    | 10               |

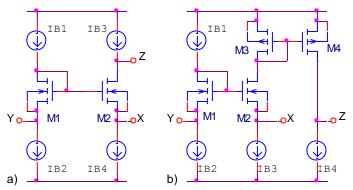

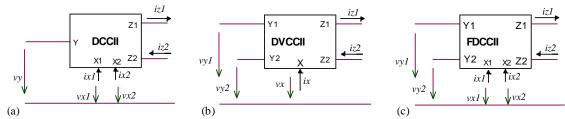

| Figure 2-7 a) CGCCII basic block, b) CCCII basic block                              |                  |

| Figure 2-8 DCCII, DVCCII and FDCCII basic blocks                                    |                  |

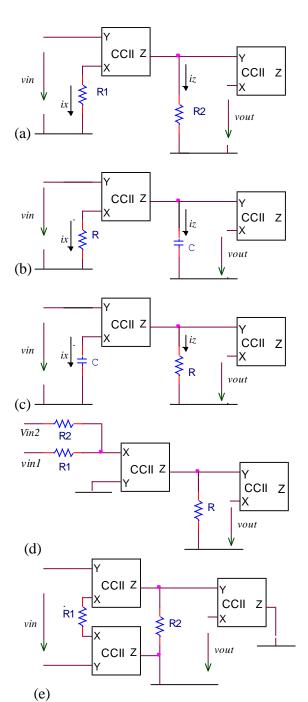

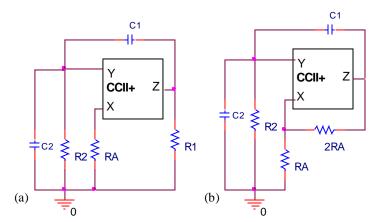

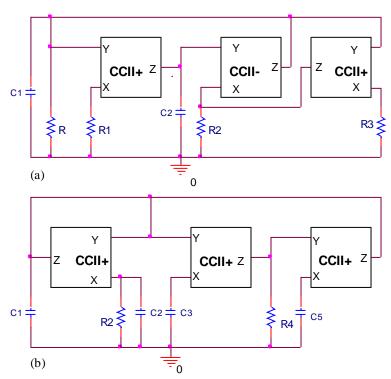

| Figure 2-13 CCII-based Wien oscillators                                             | 14               |

| Figure 2-14CCII-based oscillators using passive components grounded                 | 14               |

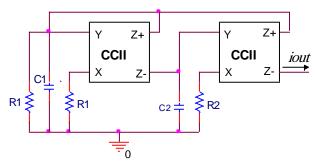

| Figure 2-15 Dual output CCII-based oscillators.                                     | 15               |

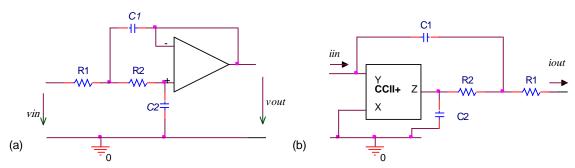

| Figure 2-16 Sallen-key low pass filter implementations. (a) Voltage-mode filter     | using an op      |

| amp. b) Current-mode filter using a current-conveyor CCII.                          | 16               |

| Figure 2-17 a) nMOS current mirror. b) small signal equivalent circuit              | 17               |

| Figure 2-18 a) Current mirror used for. b) Class AB CCII based on                   |                  |

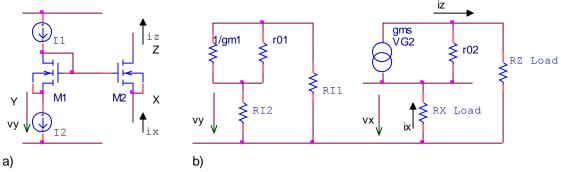

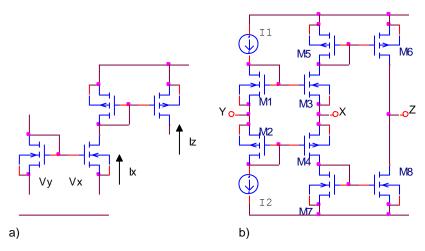

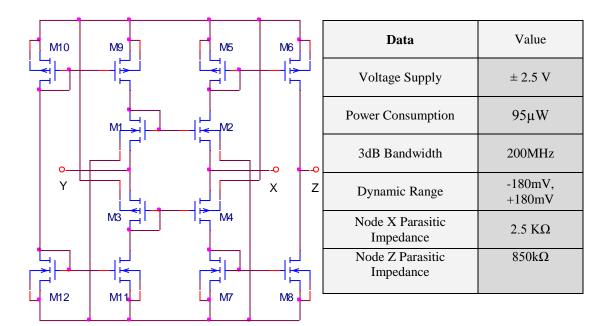

| Figure 2-19 CCII based CM characteristics                                           |                  |

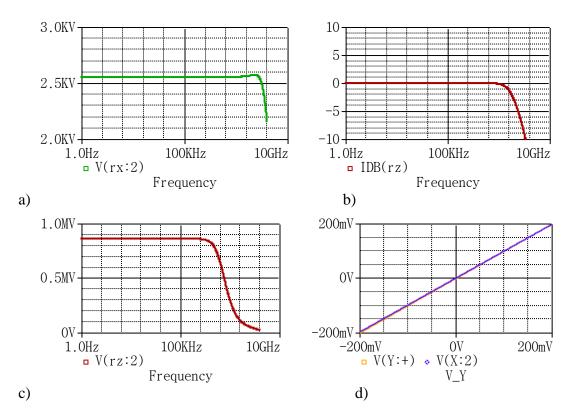

| Figure 2-20 CCII-based CM simulation a): input resistance rx, b): current transfer  |                  |

| Output resistance rz, d): Y node X node voltages                                    |                  |

| Figure 2-21 Differential pair.                                                      | 21               |

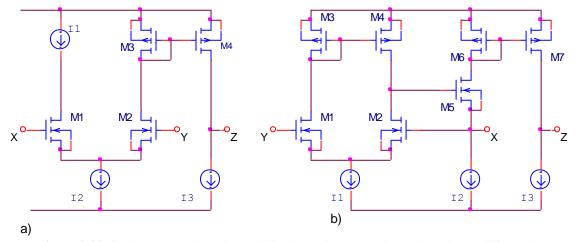

| Figure 2-22 a) Class A CCII based on a differential pair. b) Improved CCII base     |                  |

| differential pair                                                                   |                  |

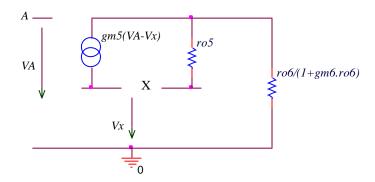

| Figure 2-23 small analysis equivalent circuit                                       |                  |

| Figure 2-24 a) CCII based on diff. pair. b) Class AB CCII based on diff. pair       |                  |

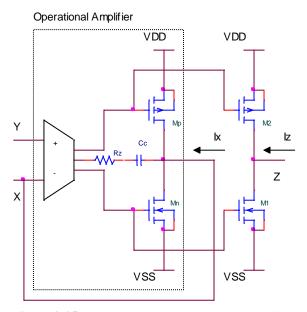

| Figure 2-25 CCII based on an operational amplifier                                  |                  |

| Figure 2-26 CCII- based on the Miller compenstaed operational amplifier             |                  |

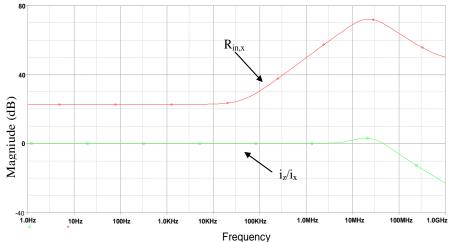

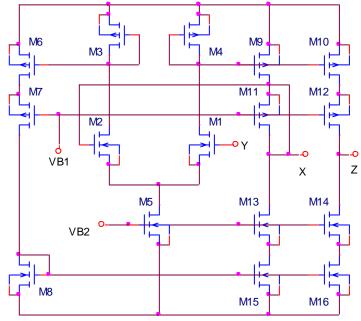

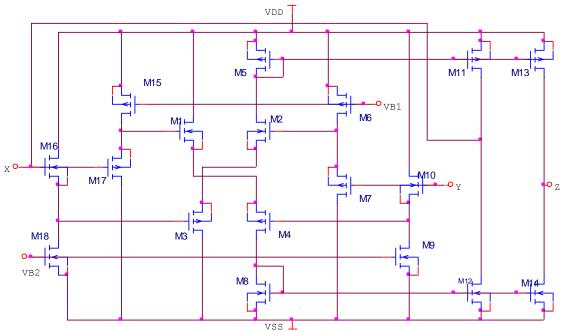

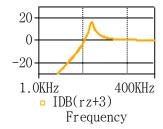

| Figure 2-27 simulation of iz/ix and rin,x, in dB is normalized to 1 ohm             |                  |

| Figure 2-28 The push pull op amp.                                                   |                  |

| Figure 2-29 The cascode output op amp.                                              |                  |

| Figure 2-30 The class AB op amp                                                     |                  |

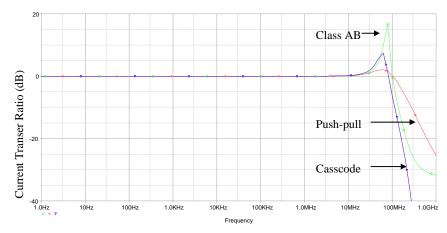

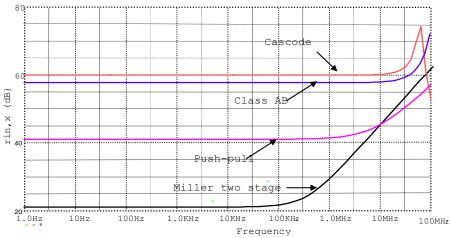

| Figure 2-31 Transfer function for class AB, output cascode, push-pull.              |                  |

| Figure 2-32 The X terminal input resistance for the Miller Compensated two-stag     |                  |

| Push-pull and cascode output. Note rx in dB is normalized to 1 ohm.                 |                  |

| Figure 2-33 Class AB CCII with improved biasing.                                    |                  |

| Figure 2-34 Class AB CCII with improved biasing simulations.                        |                  |

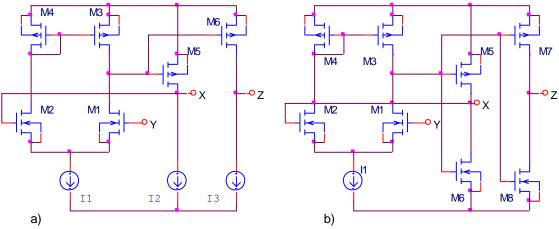

| Figure 2-35 Class AB CCII based on p-type differential pair                         |                  |

| Figure 2-36 Class AB CCII based on p-type differential pair                         |                  |

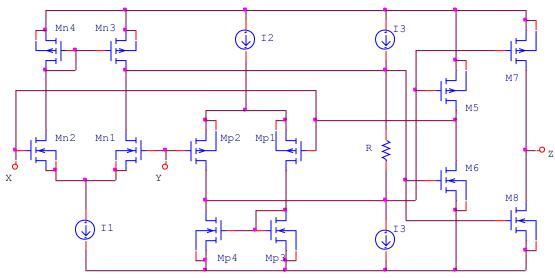

| Figure 2-37 LV rail to rail OTA based CCII.                                         | 29               |

| Figure 2-38 LV rail to rail OTA based CCII simulation                               |                  |

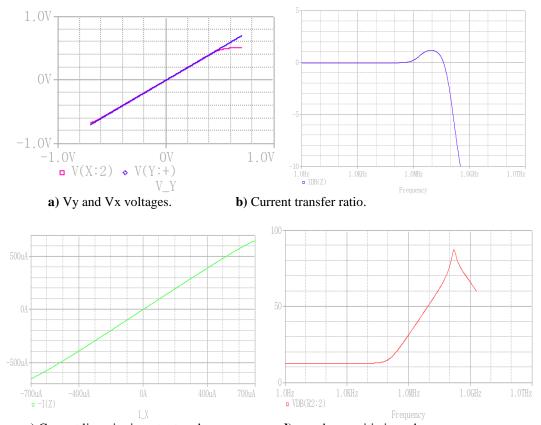

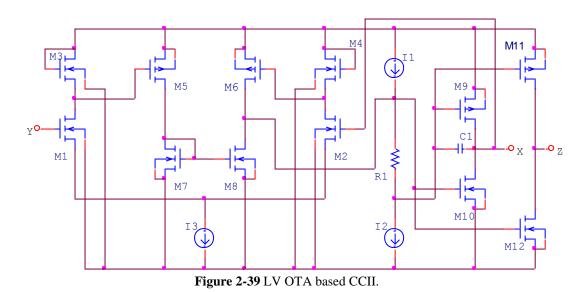

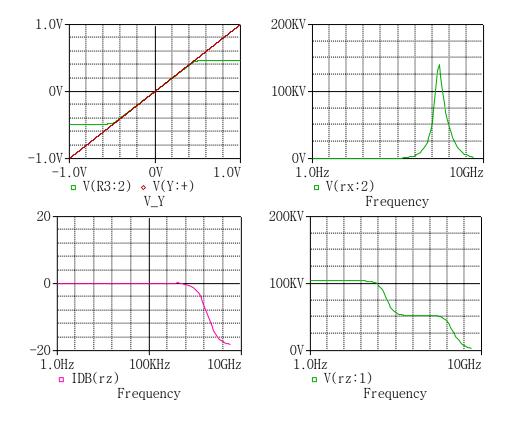

| Figure 2-39 LV OTA based CCII.                                                      |                  |

| Figure 2-40 LV OTA based CCII simulations.                                          |                  |

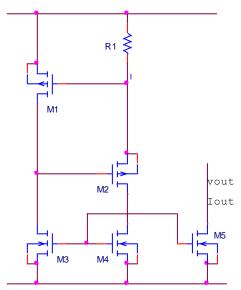

| Figure 4-1 nMOS current mirror                                                      | 33               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Figure 4-3 Low voltage cascaded current mirror.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

| Figure 4-4 Low voltage current source (independent from supply voltage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                 |

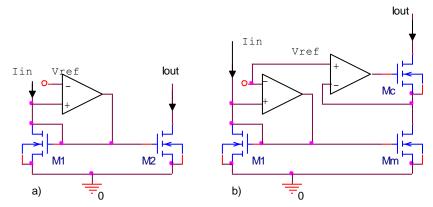

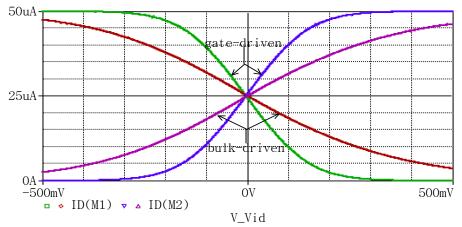

| Figure 4-5 a) active input current mir b) active input regulted cascode current mir.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36                                                 |

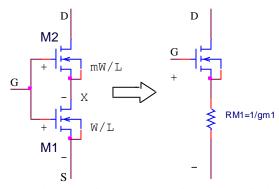

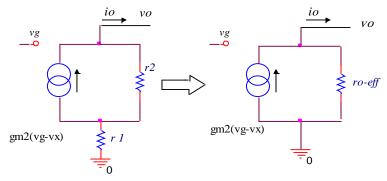

| Figure 4-6 Simple-Cascode composite NMOS transistor and equivalent simple tran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                 |

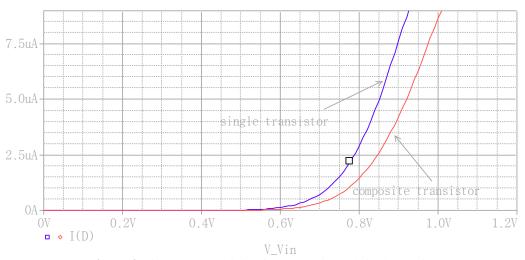

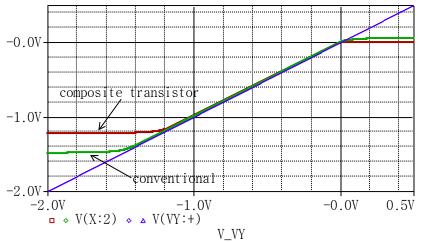

| Figure 4-7 Input characteristics for composite and single transistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

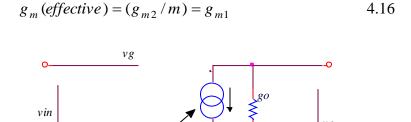

| Figure 4-8 Small signal equivalent circuit of the composite trnsistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

| Figure 4-9 The equivalent output impedance of the composite transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

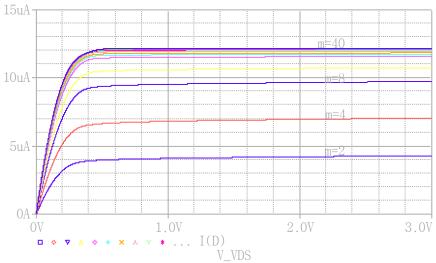

| Figure 4-10 " m" varying effect on the ouput characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

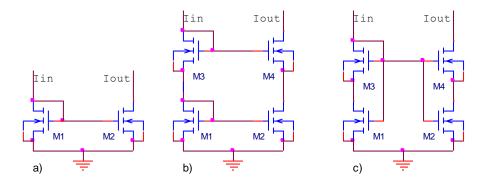

| Figure 4-11 a) simple current mir. b) cascode current mir c) self cascode current n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

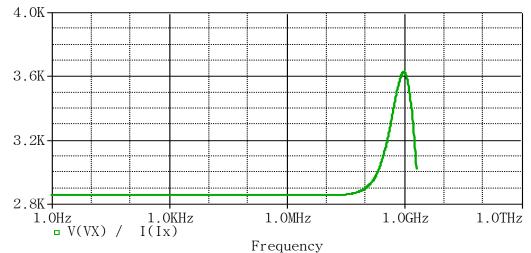

| Figure 4-12 Input impedance for composite and conventional CM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

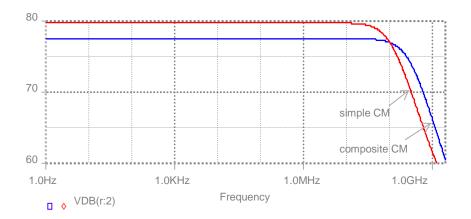

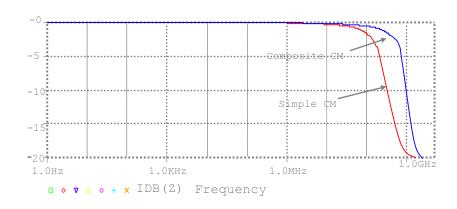

| Figure 4-13 Current mirror AC simulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

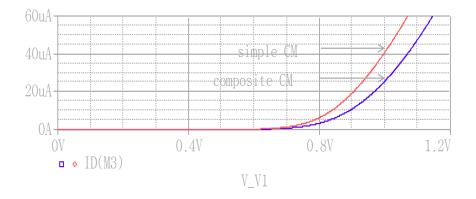

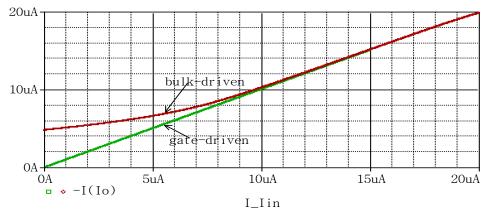

| Figure 4-14 Input voltage vs input current characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <del>4</del> 1                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

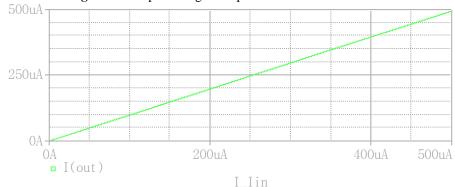

| Figure 4-15 DC simulation for Iin and Iout self cascode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

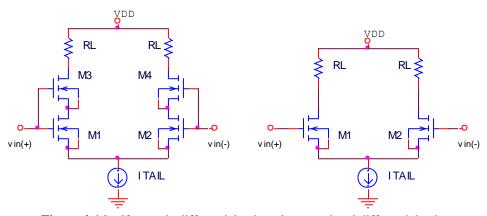

| Figure 4-16 Self cascode differential pair and conventional differential pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

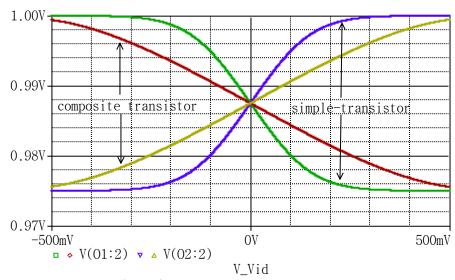

| Figure 4-17 Input voltage vs output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |

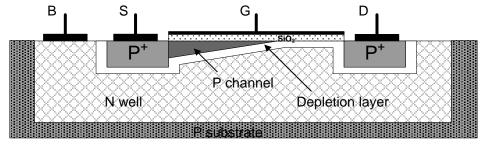

| Figure 4-18 Cross section of p-channel MOSFET in N-well CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

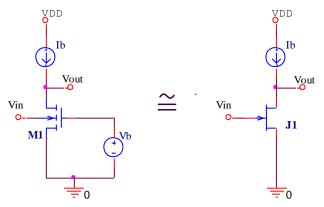

| Figure 4-19 Similarity between Bulk-driven NMOS transistor and junction field eff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

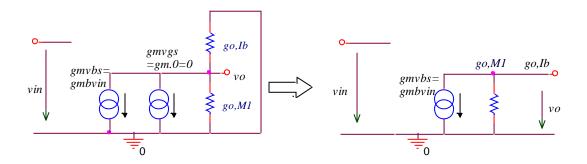

| Figure 4-20 Small signal equivalent circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

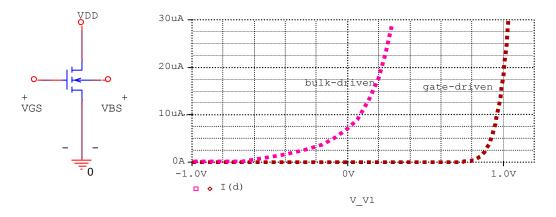

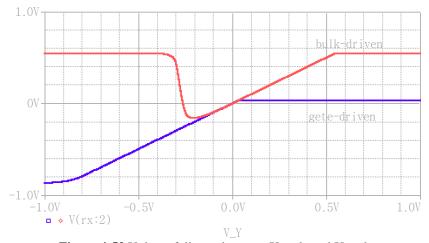

| Figure 4-21 ID vs Vbs or Vgs of bulk driven-conventional gate driven MOS trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |

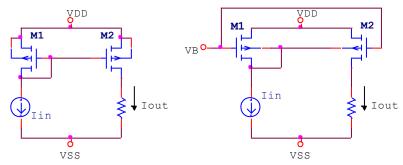

| Figure 4-22 Simple current mirror: a) Bulk-driven, b) Gate-driven                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47                                                 |

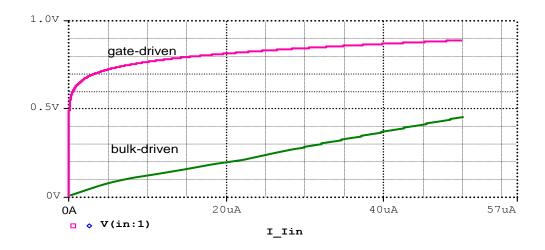

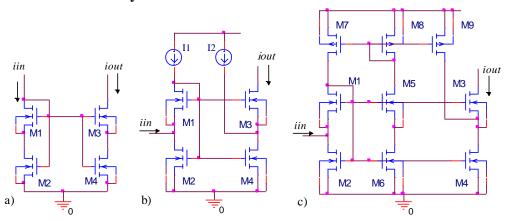

| Figure 4-23 Input voltage vs. input current characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47                                                 |

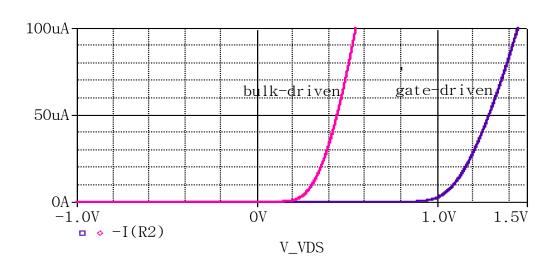

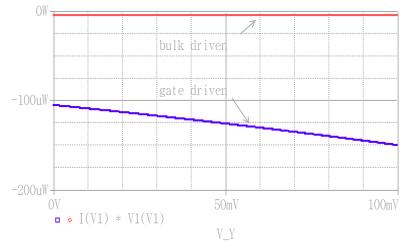

| Figure 4-24 Voltage vs output current characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47                                                 |

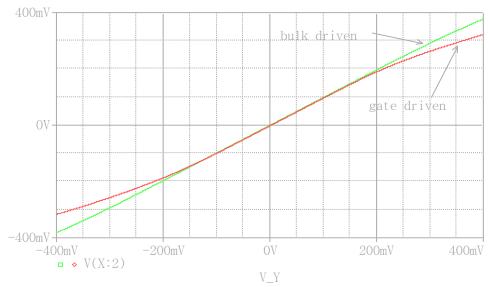

| Figure 4-25 Input output transfer characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

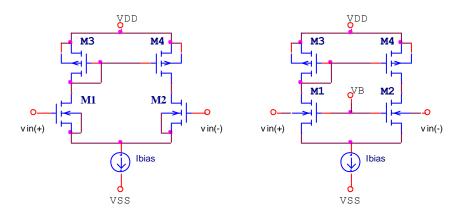

| Figure 4-26 Conventional differential pair and bulk driven differential pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |

| Figure 4-27 Drain currents vs differential input voltage, bulk driven compared with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

| differential pair.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·····+7                                            |

| Figure 4-28 Low voltage cascaded current mirror a) self cascode, b) low voltage in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

| Figure 4-28 Low voltage cascaded current mirror a) self cascode. b) low voltage in output impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | put. c) high                                       |

| output impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | put. c) high<br>50                                 |

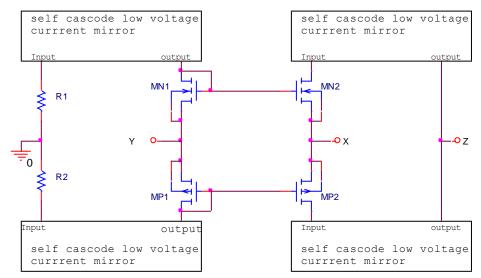

| output impedance. Figure 4-29 CCII based low voltage self cascode current mirror.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | put. c) high<br>50<br>50                           |

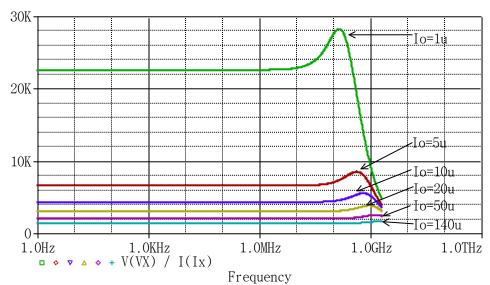

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | put. c) high<br>50<br>50<br>51                     |

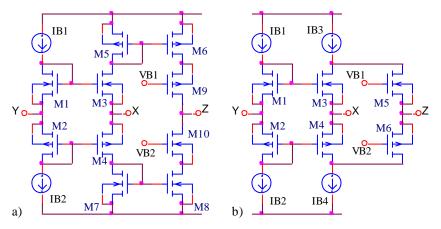

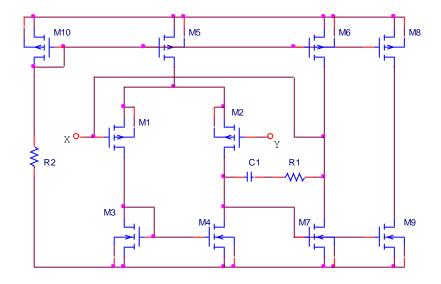

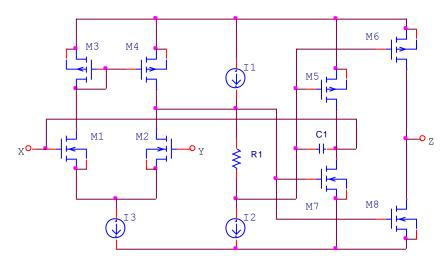

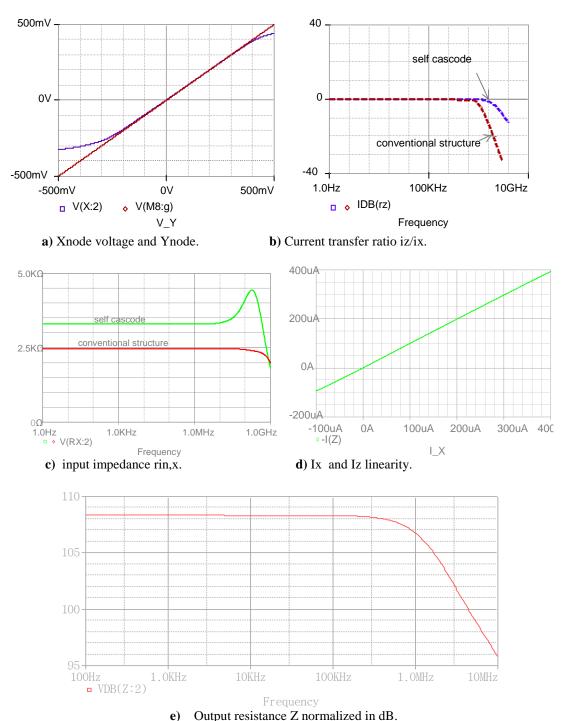

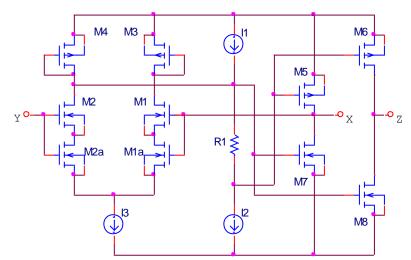

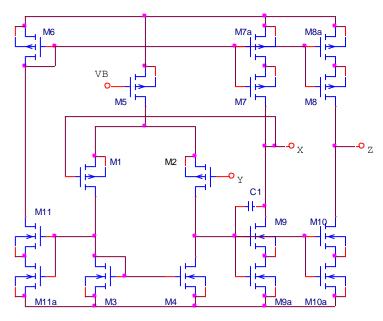

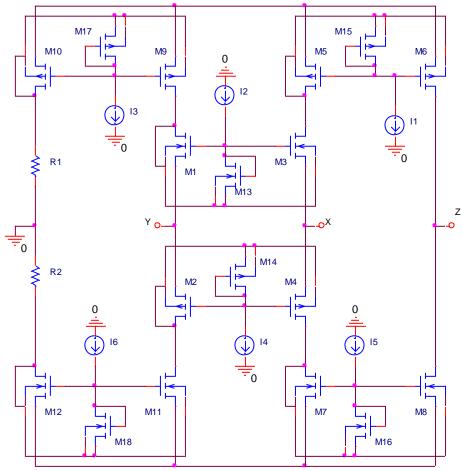

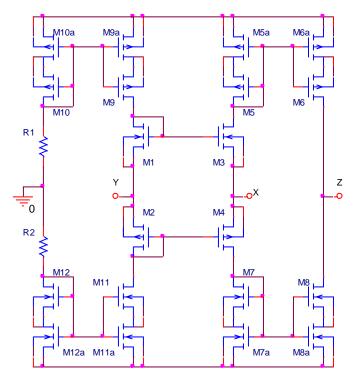

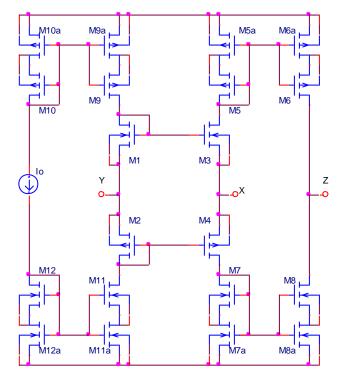

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | put. c) high<br>50<br>51<br>52                     |

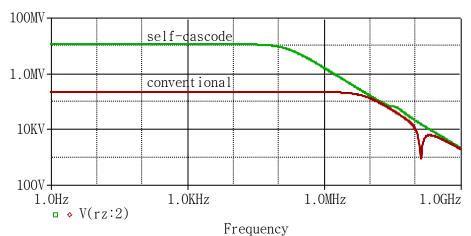

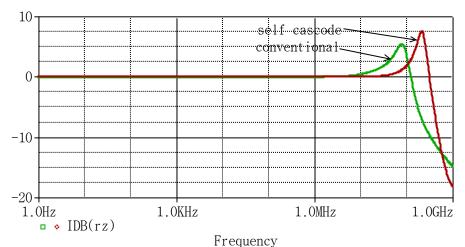

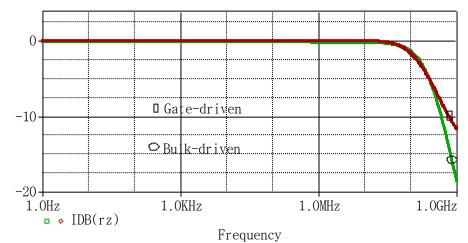

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | put. c) high<br>50<br>51<br>52<br>53               |

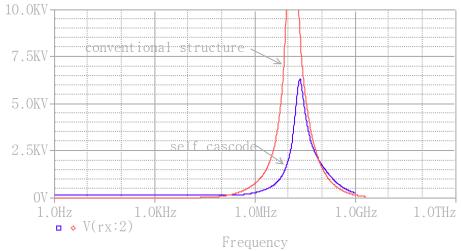

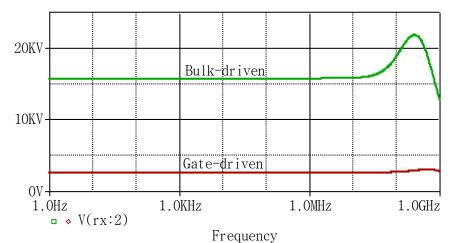

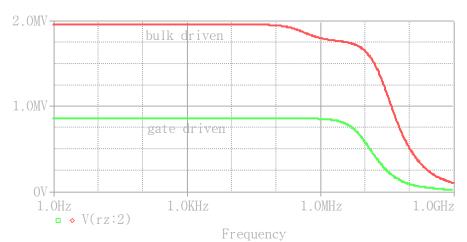

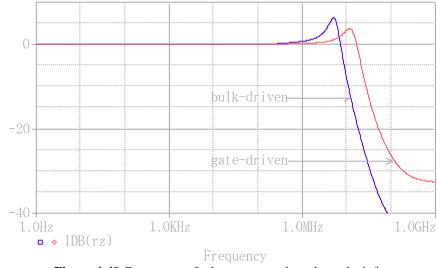

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | put. c) high<br>50<br>51<br>52<br>53               |

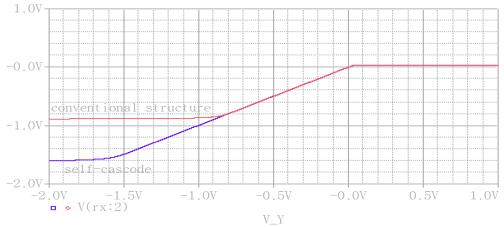

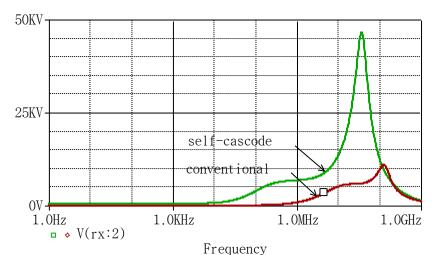

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | put. c) high<br>50<br>51<br>52<br>53<br>53         |

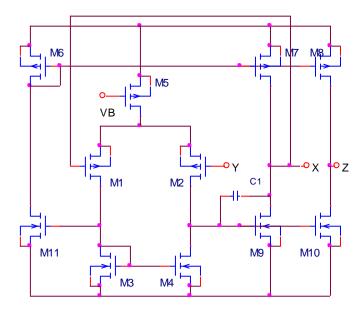

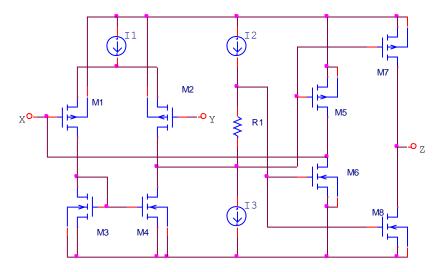

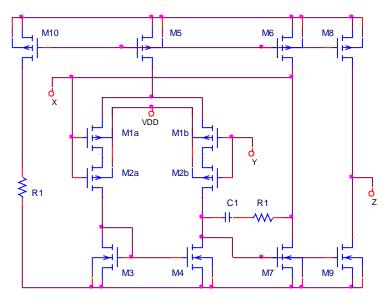

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | put. c) high<br>50<br>51<br>52<br>53<br>53<br>54   |

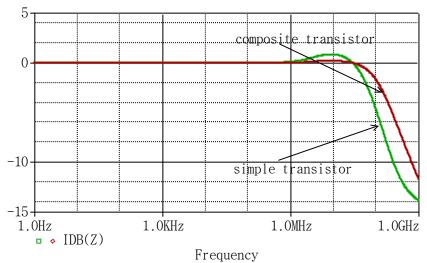

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | put. c) high505152535454                           |

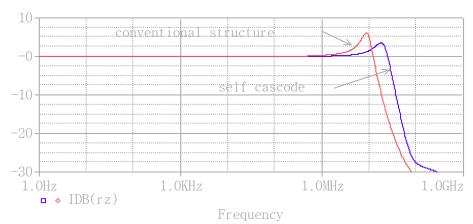

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | put. c) high5051525353545455                       |

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.  Figure 4-38 z node parasitic impedance for conventional and self cascode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | put. c) high505152535354545555                     |

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.  Figure 4-38 z node parasitic impedance for conventional and self cascode.  Figure 4-39 Current transfer iz/ix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | put. c) high505152535454555556                     |

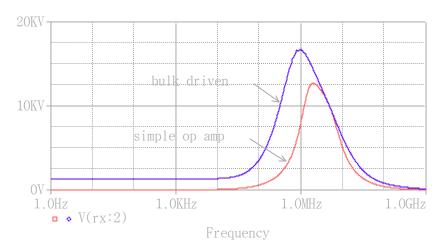

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.  Figure 4-38 z node parasitic impedance for conventional and self cascode.  Figure 4-39 Current transfer iz/ix.  Figure 4-40 x node parasitic impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | put. c) high50515253535455555555                   |

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.  Figure 4-38 z node parasitic impedance for conventional and self cascode.  Figure 4-39 Current transfer iz/ix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | put. c) high50515253535455555555                   |

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.  Figure 4-38 z node parasitic impedance for conventional and self cascode.  Figure 4-39 Current transfer iz/ix.  Figure 4-40 x node parasitic impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | put. c) high50515253545455555555                   |

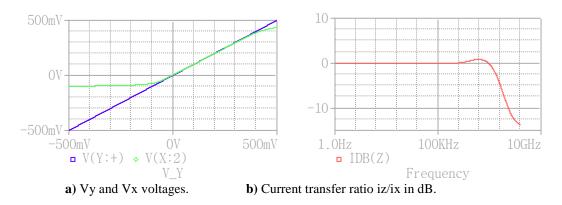

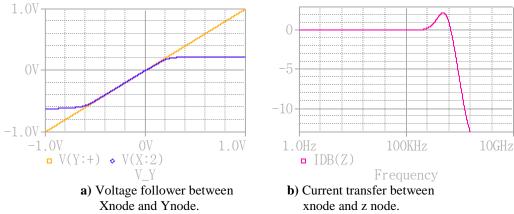

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.  Figure 4-38 z node parasitic impedance for conventional and self cascode.  Figure 4-39 Current transfer iz/ix.  Figure 4-40 x node parasitic impedance.  Figure 4-41 Voltage follower between Y node and X node.                                                                                                                                                                                                                                                                                                                                                                                                                      | put. c) high5051525354545555555758                 |

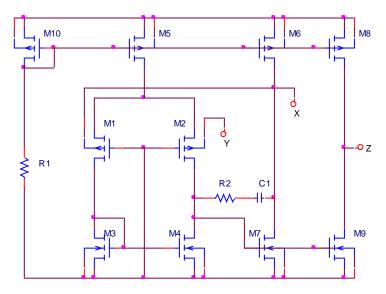

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp  Figure 4-38 z node parasitic impedance for conventional and self cascode.  Figure 4-39 Current transfer iz/ix.  Figure 4-40 x node parasitic impedance.  Figure 4-41 Voltage follower between Y node and X node.  Figure 4-42 CCII based LV bulk-driven CM.                                                                                                                                                                                                                                                                                                                                                                            | put. c) high50515253535455555555565757             |

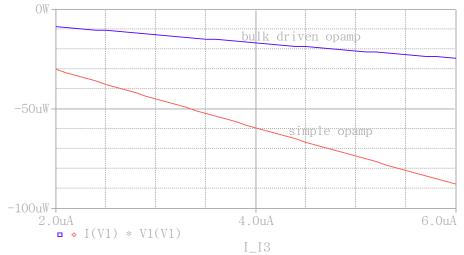

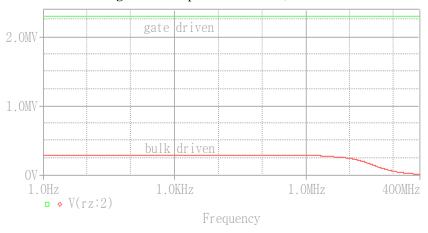

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.  Figure 4-38 z node parasitic impedance for conventional and self cascode.  Figure 4-39 Current transfer iz/ix.  Figure 4-40 x node parasitic impedance.  Figure 4-41 Voltage follower between Y node and X node.  Figure 4-42 CCII based LV bulk-driven CM.  Figure 4-43 Current transfer function iz/ix.  Figure 4-44 x node parasitic impedance.                                                                                                                                                                                                                                                                                    | put. c) high5051525354545555555657575860           |

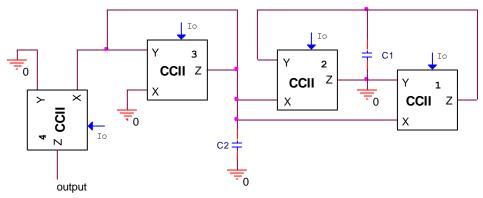

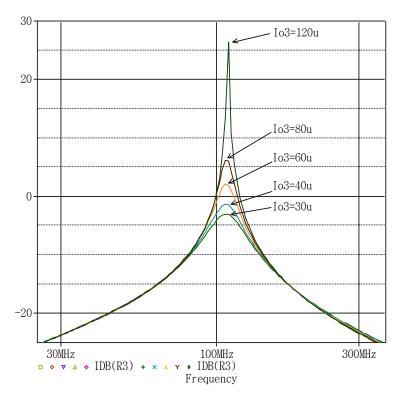

| output impedance.  Figure 4-29 CCII based low voltage self cascode current mirror.  Figure 4-30 CCII based low voltage self cascode current mirror simualation.  Figure 4-31 self cascode CCII based miller compensated op amp.  Figure 4-32 Current transfer for conventional and self cascode.  Figure 4-33 x node impedance for conventional and self cascode.  Figure 4-34 X node and Y node voltages.  Figure 4-35 CCII Self cascode OTA.  Figure 4-36 Current transfer iz/ix.  Figure 4-37 Self cascode output push pull Op. Amp.  Figure 4-38 z node parasitic impedance for conventional and self cascode.  Figure 4-39 Current transfer iz/ix.  Figure 4-40 x node parasitic impedance.  Figure 4-41 Voltage follower between Y node and X node.  Figure 4-42 CCII based LV bulk-driven CM.  Figure 4-43 Current transfer function iz/ix.  Figure 4-44 x node parasitic impedance.  Figure 4-45 z node parasitic impedance.                                                                                                                                                                                                                                           | put. c) high5051525354545555565657586060           |