# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

# **DEPARTMENT OF RADIO ELECTRONICS**

ÚSTAV RADIOELEKTRONIKY

# PORTABLE DIGITALLY CONTROLLED FUNCTION GENERATOR

PŘENOSNÝ ČÍSLICOVĚ OVLÁDANÝ GENERÁTOR FUNKCÍ

## **BACHELOR'S THESIS**

BAKALÁŘSKÁ PRÁCE

AUTHOR Daniel Graf

**AUTOR PRÁCE**

SUPERVISOR Ing. Ondřej

VEDOUCÍ PRÁCE Kolář

**BRNO 2024**

# **Bachelor's Thesis**

#### Bachelor's study program Electronics and Communication Technologies

Department of Radio Electronics

ID: 240616 Student: **Daniel Graf**

Year of Academic year: 2023/24 study:

TITLE OF THESIS:

#### Portable digitally controlled function generator

#### **INSTRUCTION:**

Design a digitally controlled function generator capable of generating at least three types of waveforms (e.g., sinusoidal, triangular, square). The device should feature a physical user interface (e.g., buttons, rotary encoder, display) and be controllable from a computer for automated measurements. Enable switching between low impedance and 50-ohm output modes. The entire device will be powered by a rechargeable battery with an integrated charging circuit.

Build, program the necessary firmware and test the finished device.

Measure frequency characteristics - amplitude of the output signal for several predefined settings, signal waveform distortions, output impedance, and load characteristics for various configurations. Evaluate the device's quality based on the determined parameters.

#### RECOMMENDED LITERATURE:

[1] HOROWITZ, Paul a Winfield HILL, 2015. The art of electronics. Third edition. New York, NY: Cambridge University Press. ISBN 978-0-521-80926-9.

[2] SKŘIVÁNEK, Vojtěch, 2022. Programujeme STM32: zdolejte jednočipy profesionálů. 2. vydání. TZ-one. ISBN 978-80-7539-131-5.

Deadline for 27.5.2024 Date of project 16.2.2024

specification: submission:

Supervisor: Ing. Ondřej Kolář

doc. Ing. Lucie Hudcová, Ph.D. Chair of study program board

#### WARNING:

The author of the Bachelor's Thesis claims that by creating this thesis he/she did not infringe the rights of third persons and the personal and/or property rights of third persons were not subjected to derogatory treatment. The author is fully aware of the legal consequences of an infringement of provisions as per Section 11 and following of Act No 121/2000 Coll. on copyright and rights related to copyright and on amendments to some other laws (the Copyright Act) in the wording of subsequent directives including the possible criminal consequences as resulting from provisions of Part 2, Chapter VI, Article 4 of Criminal Code 40/2009 Coll.

#### **ABSTRACT**

This bachelor thesis is devoted to designing a printed circuit board and constructing of portable digitally controlled function generator using AD9833 direct digital synthesis integrated circuit. The generator is capable of generating three waveforms (harmonic, triangle and square), switching between output impedance modes (50  $\Omega$  and HighZ), generating waveforms with frequency up to 12.5 MHz. The device is also capable of amplitude and DC offset adjustments. Theoretical part includes the procedure of designing the device and explains the intended functionality. Choosing suitable battery cells, microcontrollers, basic direct digital synthesis theory or design of an analog backend for amplitude and DC offset adjustments are described. Hardware design part includes explanation how individual parts were chosen, which problems occurred and how they were solved, how the user interface is implemented and how the software was programmed for this application which allows user to control the generator through a computer with a serial terminal thanks to the SCPI protocol which was programmed as a part of the software. The Measurements chapter deals with not only results of individual measurements, but also with solving complications which occurred due to a design mistake of the PCB. The chapter contains circuit diagrams, measurement charts and tables, evaluation of the measurement and comparison of the results of the device with commercial variants available on the market.

### **KEYWORDS**

Function generator, portable, digitally controlled, MCU, SCPI protocol

#### **ABSTRAKT**

Tato bakalářská práce se věnuje návrhu desky plošných spojů a sestrojení přenosného digitálně ovládaného funkčního generátoru při využití AD9833 integrovaného obvodu přímé digitální syntézy. Generátor je schopný generovat tři typy výstupních průběhů (harmonický průběh, trojúhelník a obdélník), přepínat mezi výstupní impedancí (módy  $50 \Omega$  a HighZ), generovat průběhy do frekvence až do 12,5 MHz. Zařízení také umožňuje změny amplitudy a přidávání DC offsetu. V teoretické části je popsán postup, kterým bylo zařízení navrženo a jakým způsobem bylo zamýšleno, aby zařízení fungovalo. Popsán je výběr vhodných bateriových článků pro takové zařízení, výběr vhodného mikrokontroleru, základy teorie přímé digitální syntézy nebo návrh analogového konce pro nastavení amplitudy a DC offsetu. Aplikační část již popisuje, které součástky byly vybrány, které problémy se vyskytly a jakým způsobem byly problémy vyřešeny, jakým způsobem je provedeno ovládání, rozhraní zařízení a jak byl naprogramován software pro tuto aplikaci, která umožnuje ovládání zařízení pomocí počítače přes sériový terminál díky naprogramovanému SCPI protokolu. Kapitola Měření se zaobírá nejen výsledky jednotlivých měření, ale také řešením komplikací, které se objevily kvůli chybě v návrhu desky plošných spojů. V této kapitole jsou uvedeny schémata, grafy a tabulky výsledků měření, zhodnocení měření a následovné porovnání výsledků zařízení s komerčními možnostmi na trhu.

# KLÍČOVÁ SLOVA

Funkční generátor, přenosný, digitálně ovládaný, MCU, SCPI protokol

# **Author's Declaration**

| Author:                                                                                                                                                                                                                                                                                   | Daniel Graf                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Author's ID:                                                                                                                                                                                                                                                                              | 240616                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Paper type:                                                                                                                                                                                                                                                                               | Bachelor's Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Academic year:                                                                                                                                                                                                                                                                            | 2023/24                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Topic:                                                                                                                                                                                                                                                                                    | Portable digitally controlled function generator                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| and using exclusively the technical refithe paper and listed in the comprehent As the author, I furthermore declare I have not infringed any copyright or villa In this context, I am fully aware of the Copyright Act No. 121/2000 Coll. of the of rights related to intellectual proper | rindependently, under the guidance of the advisor erences and other sources of information cited in sive bibliography at the end of the paper.  that, with respect to the creation of this paper, olated anyone's personal and/or ownership rights. It consequences of breaking Regulation § 11 of the ne Czech Republic, as amended, and of any breach rety or introduced within amendments to relevant Act or the Criminal Code, Act No. 40/2009 Coll. d VI, Part 4. |  |  |

| 5                                                                                                                                                                                                                                                                                         | author's signature*                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

<sup>\*</sup>The author signs only in the printed version.

| ACKNOWLEDGEMENT                                                                                                                |                         |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| I would like to thank the advisor of my thesis, Ing. Ondřej Ko<br>ments, advice and his time spent making sure my work is done |                         |

|                                                                                                                                | the best possible way.  |

|                                                                                                                                | ene best possible way.  |

|                                                                                                                                | ene sest possible way.  |

|                                                                                                                                | ene sest possible wey.  |

|                                                                                                                                | cine sest possible wey. |

|                                                                                                                                |                         |

# **Contents**

| 1 | The        | ory                | 1                        | 9              |

|---|------------|--------------------|--------------------------|----------------|

|   | 1.1        | Freque             | ency synthesis           | 19             |

|   |            | 1.1.1              | Phase locked loop        | 19             |

|   |            | 1.1.2              | Direct digital synthesis | 21             |

|   | 1.2        | Power              | Supply                   | 22             |

|   |            | 1.2.1              | Portable power           | 22             |

|   | 1.3        | Switch             | n mode power supplies    | 25             |

|   |            | 1.3.1              | Buck Converters          | 25             |

|   |            | 1.3.2              | Boost Converters         | 26             |

|   |            | 1.3.3              | Buck-boost topologies    | 26             |

|   |            | 1.3.4              | Inverting charge pump    | 27             |

|   | 1.4        | Opera              | tional Amplifiers        | 28             |

|   | 1.5        | Comm               | nunication               | 31             |

|   |            | 1.5.1              | UART                     | 31             |

|   |            | 1.5.2              | USB CDC                  | 32             |

|   |            | 1.5.3              | I2C                      | 33             |

|   |            | 1.5.4              | SPI                      | 34             |

|   |            | 1.5.5              | SCPI                     | 35             |

| 2 | Нэг        | dwara              | ho design                | 37             |

| _ | 2.1        |                    | 4 4051811                | 37             |

|   | 2.1        | 2.1.1              |                          | 37             |

|   | 2.2        |                    | Commenced Perspectation  | 42             |

|   | 2.2        | 2.2.1              |                          | 42             |

|   |            | 2.2.2              |                          | 43             |

|   | 2.3        |                    |                          | 43             |

|   | 2.4        |                    |                          | 45             |

|   |            | 2.4.1              |                          | 45             |

| 3 | Sof        | turono             | & UI overview            | 47             |

| J |            |                    |                          |                |

|   | 2.1        | TIT                | 4                        | 47             |

|   | 3.1        |                    |                          | 47 $49$        |

|   | 3.1<br>3.2 | Softwa             | are                      | 49             |

|   |            | Softwa 3.2.1       | are                      | 49<br>49       |

|   |            | Softwa 3.2.1 3.2.2 | are                      | 49<br>49<br>51 |

|   |            | Softwa 3.2.1       | are                      | 49<br>49       |

|                        |       | 3.2.6 SCPI                                                                            |

|------------------------|-------|---------------------------------------------------------------------------------------|

| 4                      | Mea   | surements                                                                             |

|                        | 4.1   | AD9833 DDS base characteristics                                                       |

|                        | 4.2   | Analog backend characteristics                                                        |

|                        |       | 4.2.1  Comparison of the amplitude vs. frequency dependence                           |

|                        | 4.3   | Output impedance                                                                      |

|                        |       | 4.3.1 Formula & calculation                                                           |

|                        | 4.4   | Harmonic Distortion                                                                   |

|                        | 4.5   | Conclusion of the measurements                                                        |

| Co                     | onclu | sion                                                                                  |

| Bi                     | bliog | raphy                                                                                 |

| $\mathbf{S}\mathbf{y}$ | mbo   | ls and abbreviations                                                                  |

| Li                     | st of | appendices                                                                            |

| ${f A}$                | Mea   | asurement charts                                                                      |

|                        | A.1   | AD9833 DDS base characteristics                                                       |

|                        | A.2   | Analog backend characteristics                                                        |

|                        |       | A.2.1 HighZ output impedance mode                                                     |

|                        |       | A.2.2 $50\Omega$ output impedance mode                                                |

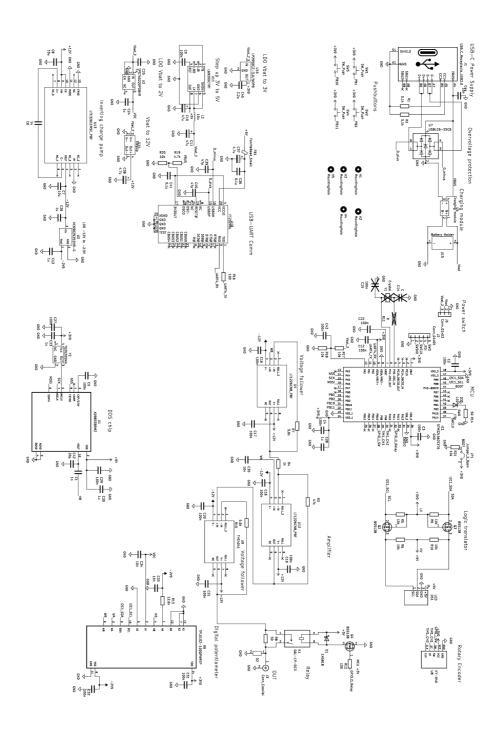

| В                      | Full  | circuit scheme                                                                        |

|                        | B.1   | Main PCB                                                                              |

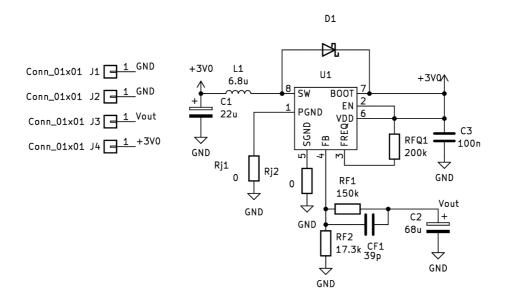

|                        | B.2   | +12 V Step up Module $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ |

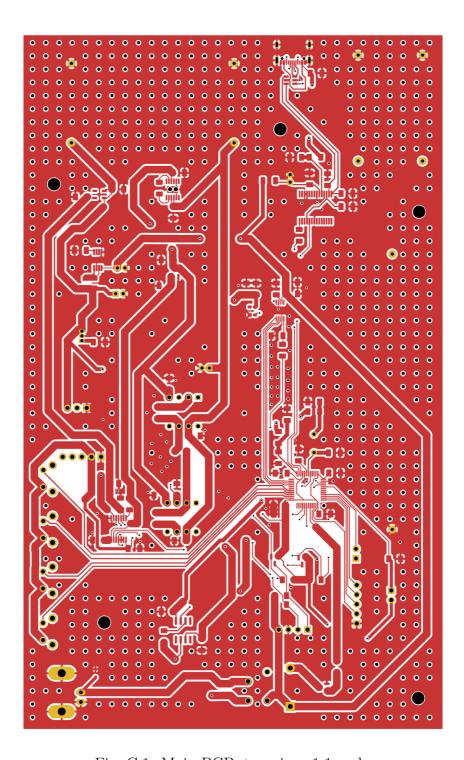

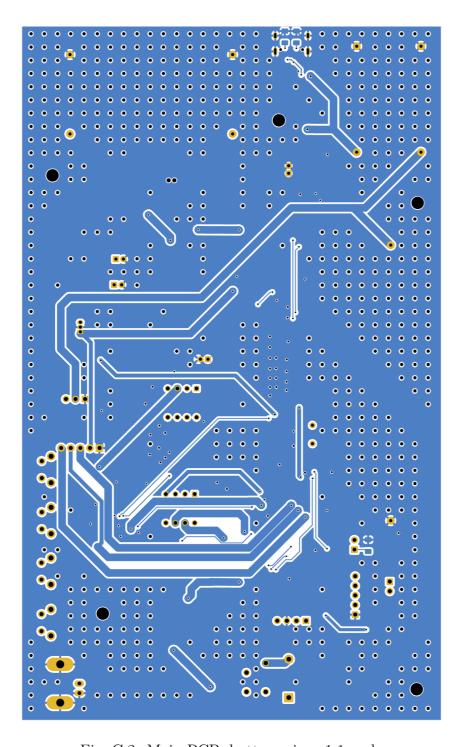

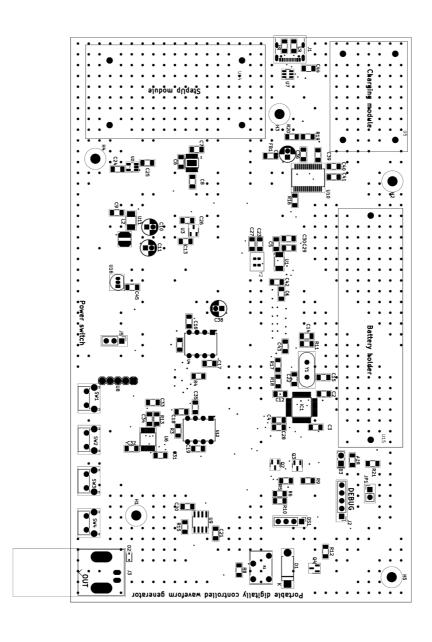

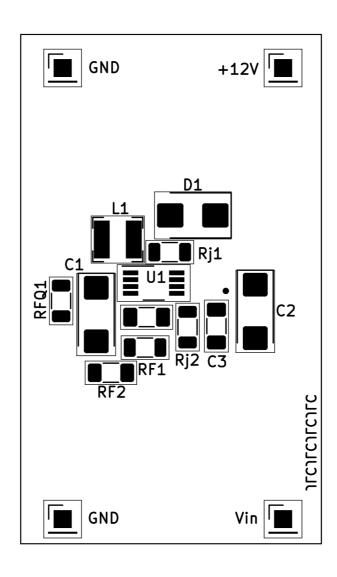

| $\mathbf{C}$           | PCI   | B preview                                                                             |

|                        | C.1   | Main PCB top view                                                                     |

|                        | C.2   | Main PCB bottom view                                                                  |

|                        | C.3   | Main PCB assembly plan                                                                |

|                        | C.4   | $+12\mathrm{V}$ Step up module top view                                               |

|                        | C.5   | $+12\mathrm{V}$ Step up module bottom view                                            |

|                        | C.6   | $+12\mathrm{V}$ Step up module assembly plan                                          |

|                        | C.7   | Construction of device                                                                |

|                        |       | C.7.1 Inside view                                                                     |

|                        |       | C.7.2 Front view                                                                      |

|                        |       | C.7.3 Side view                                                                       |

# List of Figures

| 1.1  | Phase frequency detector scheme [2]                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Basic block scheme of a DDS[1] $\dots \dots \dots$ |

| 1.3  | Battery discharge curves [1]                                                                                                                       |

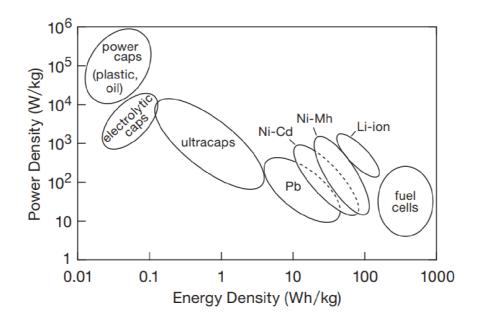

| 1.4  | Comparison of the amount of power to energy density $[1]$                                                                                          |

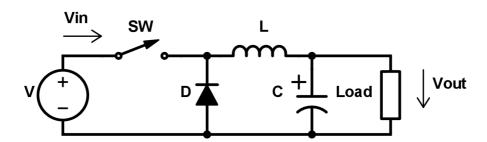

| 1.5  | Scheme with basic buck converter topology                                                                                                          |

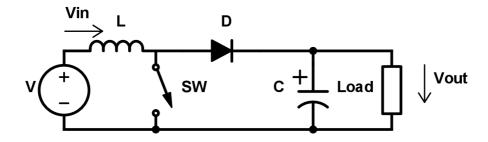

| 1.6  | Scheme with basic boost converter topology                                                                                                         |

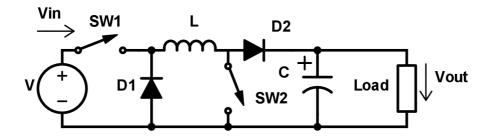

| 1.7  | Scheme with basic buck-boost converter topology                                                                                                    |

| 1.8  | Scheme with basic inverting charge pump topology [17]                                                                                              |

| 1.9  | Default schematic symbol of an operational amplifier                                                                                               |

| 1.10 | Schematic of an inverting op-amp circuit                                                                                                           |

| 1.11 | Schematic of an inverting op-amp circuit with variable offset $\dots 29$                                                                           |

| 1.12 | Schematic of a non-inverting op-amp circuit                                                                                                        |

| 1.13 | Schematic of a voltage follower op-amp circuit                                                                                                     |

| 1.14 | UART wiring diagram                                                                                                                                |

| 1.15 | UART timing diagram [16]                                                                                                                           |

| 1.16 | I2C timing diagram [1]                                                                                                                             |

| 1.17 | I2C transfer diagram [14]                                                                                                                          |

| 1.18 | SPI transfer diagram [14]                                                                                                                          |

| 2.1  | Communication block scheme                                                                                                                         |

| 2.2  | USB-UART Bridge wiring [12]                                                                                                                        |

| 2.3  | MOSFET logic level shifter [15]                                                                                                                    |

| 2.4  | Analog waveform generation                                                                                                                         |

| 2.5  | Operational amplifier connection                                                                                                                   |

| 2.6  | Power distribution & consumption block scheme                                                                                                      |

| 3.1  | Front panel layout                                                                                                                                 |

| 3.2  | LCD UI layout                                                                                                                                      |

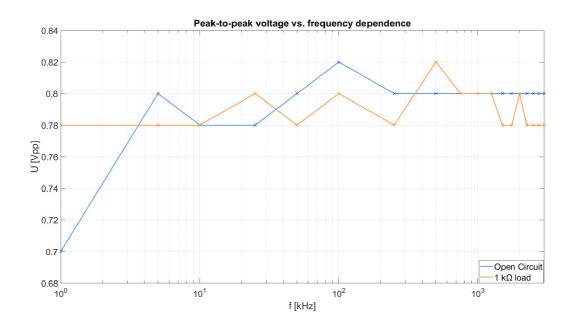

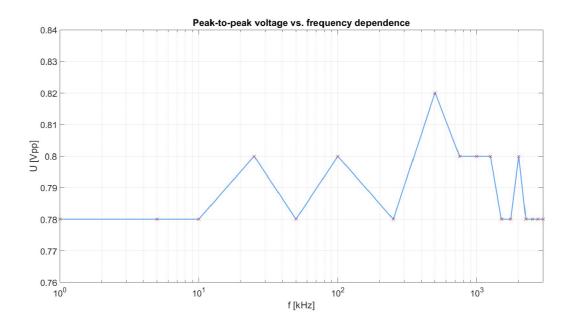

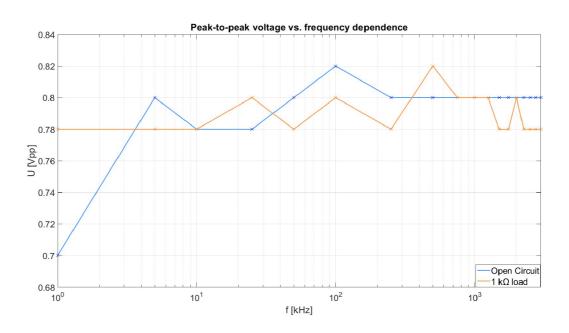

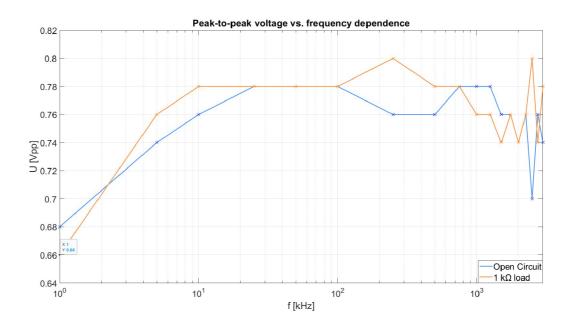

| 4.1  | Peak-to-peak voltage vs. frequency chart for sine waveform, open                                                                                   |

|      | circuit and $1 \mathrm{k}\Omega$ load                                                                                                              |

| 4.2  | Circuit diagram of the analog backend                                                                                                              |

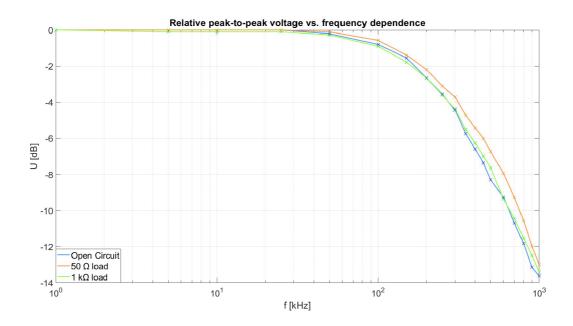

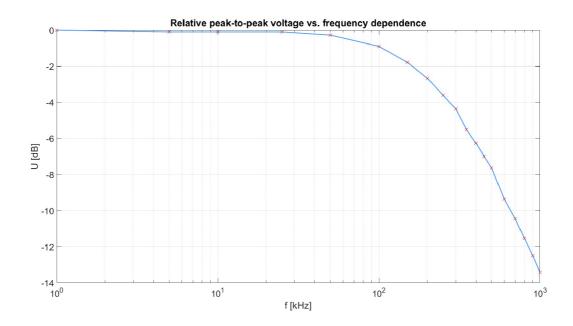

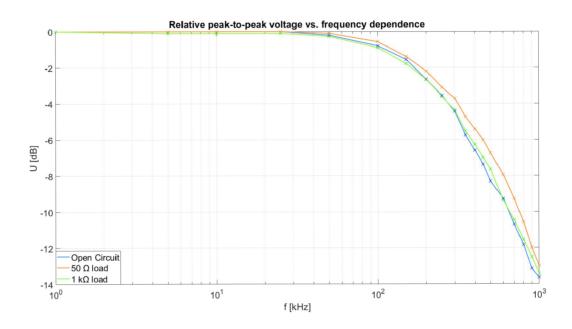

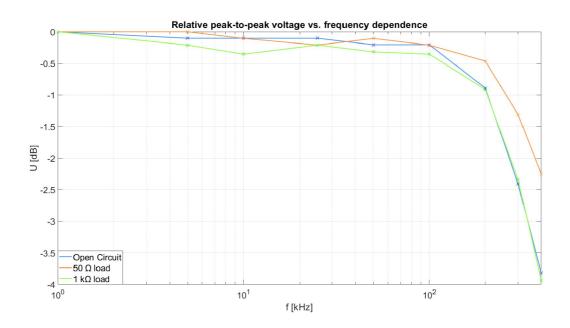

| 4.3  | Relative peak-to-peak voltage vs. frequency dependence of analog                                                                                   |

|      | backend for sine wave, open circuit, $50\Omega$ and 1 k $\Omega$ loads, set voltage                                                                |

|      | $2.5\mathrm{V_{pp}}$                                                                                                                               |

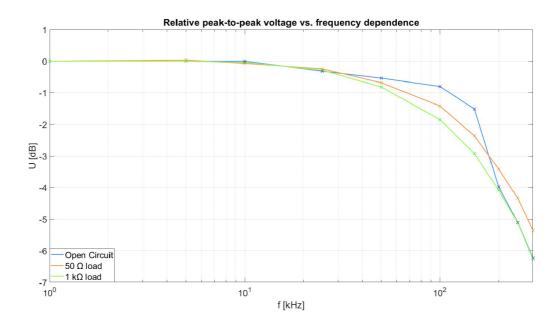

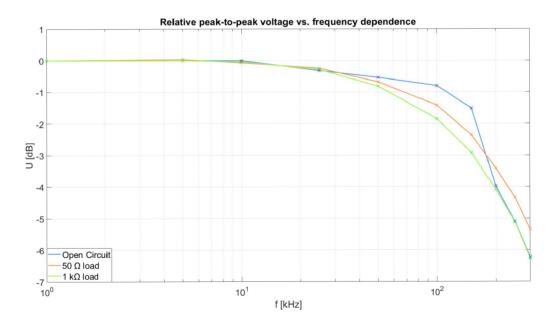

| 4.4  | Relative peak-to-peak voltage vs. frequency dependence of analog                                                                                   |

|      | backend for triangle wave, open circuit, $50\Omega$ and $1~\mathrm{k}\Omega$ loads, set                                                            |

|      | voltage $2.5 \mathrm{V}_{\mathrm{pp}}$                                                                                                             |

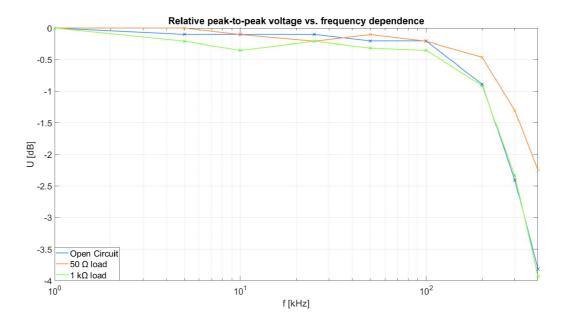

| 4.5  | Relative peak-to-peak voltage vs. frequency dependence of analog                             |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | backend for square wave, open circuit, $50\Omega$ and $1~\mathrm{k}\Omega$ loads, set volt-  |    |

|      | age $2.5\mathrm{V_{pp}}$                                                                     | 61 |

| 4.6  | Peak-to-peak voltage vs. frequency dependence of AD9833 for sine                             |    |

|      | wave, $1k\Omega$ load                                                                        | 62 |

| 4.7  | Relative peak-to-peak voltage vs. frequency dependence of analog                             |    |

|      | backend for sine wave, $1k\Omega$ load, set voltage $2.5 V_{pp}$                             | 63 |

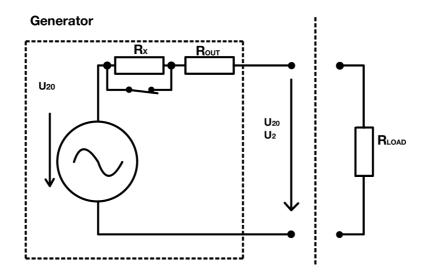

| 4.8  | Circuit diagram for output impedance measurement                                             | 64 |

| 4.9  | Distortion example of the square wave                                                        | 68 |

| 4.10 | Distortion example of the triangle wave                                                      | 68 |

| A.1  | Peak-to-peak voltage vs. frequency chart for sine waveform, open                             |    |

|      | circuit and $1k\Omega$ load $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 81 |

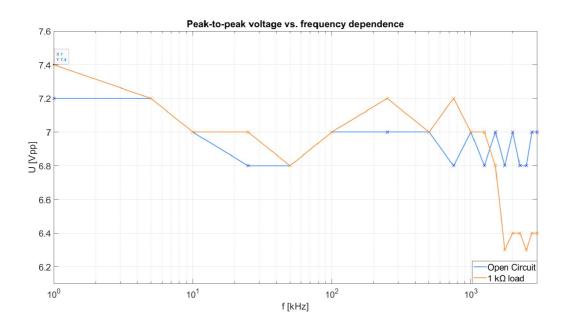

| A.2  | Peak-to-peak voltage vs. frequency chart for triangle waveform, open                         |    |

|      | circuit and $1k\Omega$ load $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$          | 81 |

| A.3  | Peak-to-peak voltage vs. frequency chart for square waveform, open                           |    |

|      | circuit and $1k\Omega$ load $\hdots$                                                         | 82 |

| A.4  | Relative peak-to-peak voltage vs. frequency chart for sine waveform,                         |    |

|      | open circuit, $50\Omega$ and $1k\Omega$ loads, set voltage $2.5V_{\rm pp}$ $\ \ .$           | 83 |

| A.5  | Relative peak-to-peak voltage vs. frequency chart for triangle wave-                         |    |

|      | form, open circuit, $50\Omega$ and $1k\Omega$ loads, set voltage $2.5V_{\rm pp}$             | 83 |

| A.6  | Relative peak-to-peak voltage vs. frequency chart for square wave-                           |    |

|      | form, open circuit, $50\Omega$ and $1k\Omega$ loads, set voltage $2.5V_{\rm pp}$             | 84 |

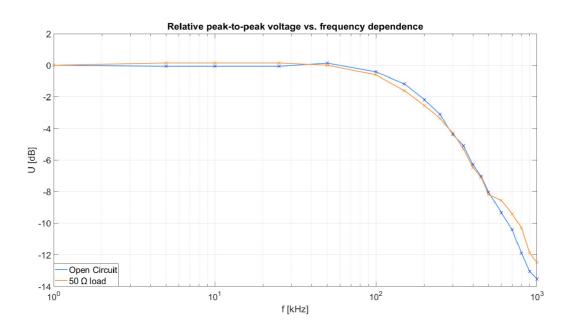

| A.7  | Relative peak-to-peak voltage vs. frequency chart for sine waveform,                         |    |

|      | open circuit and $50\Omega$ load, set voltage $2.5\mathrm{V_{pp}}$                           | 85 |

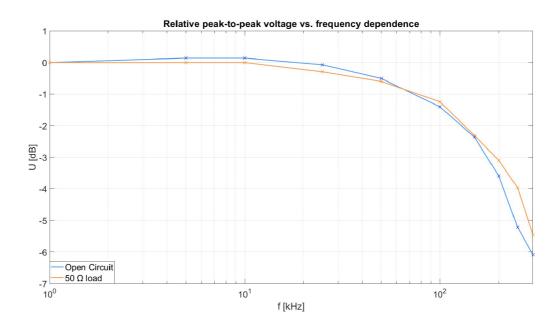

| A.8  | Relative peak-to-peak voltage vs. frequency chart for triangle wave-                         |    |

|      | form, open circuit and $50\Omega$ load, set voltage $2.5V_{pp}$                              | 85 |

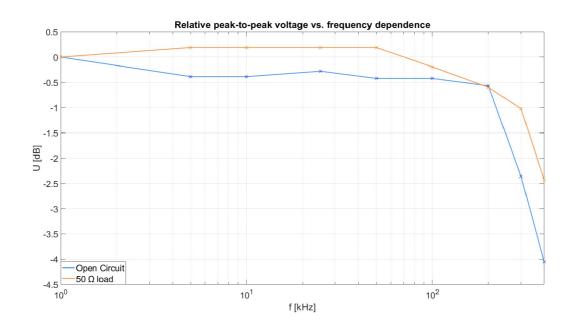

| A.9  | Relative peak-to-peak voltage vs. frequency chart for square wave-                           |    |

|      | form, open circuit and $50\Omega$ load, set voltage $2.5\mathrm{V}_\mathrm{pp}$              | 86 |

| C.1  | Main PCB, top view, 1:1 scale                                                                | 89 |

| C.2  | Main PCB, bottom view, 1:1 scale                                                             | 90 |

| C.3  | +12 V Step up module, top PCB view, 1:1 scale                                                | 92 |

| C.4  | +12 V Step up module, bottom PCB view, 1:1 scale                                             | 92 |

| C.5  | Inside view of the generator                                                                 | 94 |

| C.6  | Front view of the generator, power ON                                                        | 95 |

| C.7  | Front view of the generator, power OFF                                                       | 95 |

| C.8  | Side view of the generator                                                                   | 96 |

|      |                                                                                              |    |

# **List of Tables**

| 2.1 | A comparison between ATMega328P, STM32L562 and STM32F411                       |    |

|-----|--------------------------------------------------------------------------------|----|

|     | MCUs                                                                           | 37 |

| 4.1 | Harmonic distortion measurement table                                          | 66 |

| 4.2 | Total harmonic distortion measurement table for frequency of $100\mathrm{kHz}$ | 67 |

| 4.3 | Total harmonic distortion measurement table for frequency of $1\mathrm{MHz}$   | 67 |

| 4.4 | Total harmonic distortion measurement table for frequency of $3\mathrm{MHz}$   | 67 |

| 4.5 | A comparison between the constructed device and JDS6600 arbitrary              |    |

|     | waveform generator [13]                                                        | 69 |

# Listings

| 3.1 | Sample code for ADC evaluation                | 49 |

|-----|-----------------------------------------------|----|

| 3.2 | Sample code for ADC bug correction            | 50 |

| 3.3 | Sample code for rotary encoder                | 51 |

| 3.4 | Sample code for button debouncing function    | 52 |

| 3.5 | Sample code for createAmplitudeArray function | 54 |

| 3.6 | Sample code for findClosest function          | 54 |

| 3.7 | Sample code for SCPI protocol function        | 55 |

# Introduction

Function generator is one of basic pieces of laboratory equipment together with power supplies. Generators are generally used to observe a behavior of an electronic circuit under different conditions (frequency, amplitude, waveform types). The most basic generators usually offer three voltage waveforms (sine, triangle and PWM). More advanced generators which are referred to as arbitrary waveform generators (AWGs) offer generation of user defined waveforms.

The goal of this bachelor thesis was to design a portable digitally controlled function generator, it's corresponding printed circuit board and to program a software which should contain both physical user interface (buttons, rotary encoder, LCD) as well as some kind of communication protocol which would allow user to control the device through a serial terminal on a computer.

In the first part of the thesis, basic building blocks which were used are described on theoretical level. Second part contains more detailed explanation on how or why different components were chosen and are being used. The generator is able to generate at 3 waveform types (harmonic-sine, triangular and PWM-square), output impedance analog lever switches between output impedance modes ( $50\,\Omega$  and HighZ). The user interface of the generator consists of a rotary encoder which is used for frequency setting, two analog potentiometers for adjustments of amplitude and DC offset. Buttons are used to fine adjust the frequency and to switch between waveforms. Information about frequency, current waveform and position at which the frequency value will get adjusted is being displayed on 16x2 LCD panel. The whole device is powered by single battery cell which is rechargeable through one of the USB-C connectors. The second other USB-C connector is used for communication between the device and a computer for automatic measurement purposes.

# 1 Theory

# 1.1 Frequency synthesis

Stable, constant frequency is the key to success in certain applications such as in communication systems where choosing and maintaining certain frequency is crucial to ensure that the system will work in the best possible way and the transmission will have the least amount of distortion for example. Tunable frequency is required in such applications as function generators. Frequency adjustment can be done in several ways. The first is direct digital synthesis (DDS) and the second one is phase locked loop (PLL). Both are digital "mixed signal" techniques.

# 1.1.1 Phase locked loop

Phase locked loop or PLL for short chips can be found in telecommunication devices where they are used to set operating frequency, in local oscillators (LOs) or vector network analyzers (VNAs). PLL chips can transform a set frequency provided by a reference oscillator with for example set 10 MHz frequency into a different frequency with the help of a microcontroller (MCU). The way PLL chip operates is it takes a reference frequency  $f_{ref}$  from a reference oscillator and changes it into a new frequency  $f_{out} = \frac{n}{r} f_{ref}$ , where n and r are integers. It is very similar to a frequency divider where  $f_{out} = f_{ref}/N$ . By choosing both n and r integers we can basically create oscillator of any frequency. [1] [2]

#### **Phase Frequency Detector**

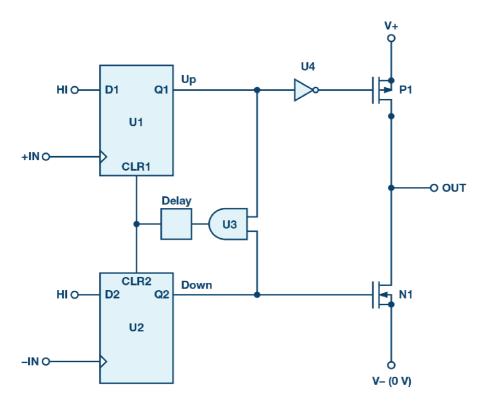

The working principle of every PLL is comparing phase of a reference signal  $F_{ref}$  to the phase of adjustable feedback signal  $F_0$ , this operation is done by the phase frequency detector (PFD), in case where frequency and phase of the output signal  $F_0$  matches the phase and frequency of  $F_{ref}$ , we get into so called steady-state where the PLL is locked. PFD shown in figure below uses two D-type flip flops to compare the reference signal  $F_{ref}$  at +IN with the feedback signal at -IN. Each flip flop output enables either positive or negative current source which together create the charge pump. If the +IN input is at higher frequency than the -IN input, the charge pump starts to pump current high. This current flowing through the low pass filter will resolve in voltage controlled oscillator (VCO) changing its frequency to match the frequency at -IN with the frequency at +IN. If -IN frequency is higher than the +IN, the exact opposite happens. [2]

Fig. 1.1: Phase frequency detector scheme [2]

# 1.1.2 Direct digital synthesis

Direct digital synthesis, DDS for short is a way of making analog waveforms using digital circuits. Sine, triangle or square waveforms are created from time—varying digital signal and then converting it with a digital to analog conveter (DAC) to analog form. Main advantage of DDS devices compared to analog ones is the switching speed and wide spectrum of frequencies where the analog devices would simply fail to operate or they would have significant distortion. Working principle of DDS is saving numerical values for sine and cosine arguments which are equally spaced and then recalling them in sequence with high speed, converting them with a DAC and thus creating a desired waveform. Nowadays single-chip DDS ICs are able to provide high resolution and accuracy waveforms while also being inexpensive. [3]

#### Components of a DDS device

The main components of a DDS device are phase accumulator, phase-to-amplitude converter and a DAC.

Fig. 1.2: Basic block scheme of a DDS[1]

As shown above in figure 1.2 DDS devices work with a sine ROM which stores  $2^n$  values of the sine wave within 360° cycle. The ROM itself is driven by a phase register which accumulates steps of phase based off of the frequency tuning word (FTW). At each clock tick the phase advances by  $\Delta\phi = (360^{\circ}/2^n) \cdot \text{FTW}$ , which results in frequency  $f_{out} = FTW \cdot f_{clk}/2^n$ , any extra phase is carried forward from cycle to cycle. Overall, DDS chips give you the freedom to choose frequency, amplitude and even phase modulation with extreme precision. [1] [3]

# 1.2 Power Supply

Generally speaking power supply is a device that provides variable voltage after being plugged in the mains voltage which then provides power to electronic circuits or devices. For such portable projects as the one described further in this thesis, though the most sufficient solution is to power the device with some sort of portable power. Nowadays power cells or batteries are able to provide enough power and their durability has increased over the years significantly but there are still some issues tied with them.

# 1.2.1 Portable power

Portable power comes in form of power cells or batteries. Batteries can be divided based on their recharging capabilities to primary and secondary ones. Primary batteries come pre-charged and when discharged, they need to be completely replaced. The secondary batteries are designed to be rechargeable, the amount of charge(life) cycles varies but its usually from 200 to 1000 times, for example the Samsung 18650 battery's data sheet states that after 500 charge cycles, the battery's capacity should remain above 60% rated discharge capacity [4].

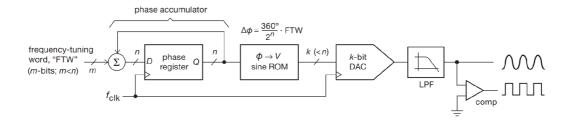

Another way how batteries can be categorized is by their chemical composition. In the primary section there usually are alkaline (Zn/MnO<sub>2</sub>) or silver (Zn/Ag<sub>2</sub>O) batteries. From the family of lithium type batteries there are multiple options such as Li/MnO<sub>2</sub>, Li/FeS<sub>2</sub> or Li/SOCl<sub>2</sub> cells. The advantages of lithium batteries are higher single cell terminal voltage (~3 V), higher energy density and flatter discharge curves, as can be seen in figure 1.3. Family of secondary batteries contains lithium-ion (Li-ion), nickel metal-hydride "NiMH" or lead-acid "Pb-acid" cells. Li-ion batteries are light and they have the highest energy density 1.4 together with charge retention.

Li-ion batteries have some issues tied with them as well such as charging. Recharging of those batteries has to be done more carefully as overcharge or overcurrent could lead to an explosion, that is why charging is done through external charging modules which can be bought as premade printed circuit boards (PCBs) which monitor charging current, battery voltage and battery temperature the whole time so the chance of battery explosion is minimal. Li-ion batteries are used in modern electronics (notebooks, tablets, phones etc.). Common batteries that are freely available in basically any store are nickel metal-hydrid power cells which in early days struggled with really fast self discharge rates (approximately 30% per month)

but nowadays they do not have such issue as the low self discharge (LSD) rates have improved. [1]

Fig. 1.3: Battery discharge curves [1]

Fig. 1.4: Comparison of the amount of power to energy density [1]

#### Primary batteries (non-rechargeable)

- Alkaline (Zn/MnO<sub>2</sub>) Cheap, widely available 1.5 V/cell AA, excellent shelf life, sloping discharges

- Lithium (Li/MnO<sub>2</sub>) High energy density, 3 V/cell AA, excellent shell life, flat discharges

- Lithium (Li/FeS<sub>2</sub>) Extraordinary shelf life up to 90 % after 15 years, excellent low-temperature performance, flat discharge

- Lithium (Li/SOCl<sub>2</sub>) Extraordinary low-temperature performance up to  $55^{\circ}$ , excellent shelf life, very flat discharge rate but dependent on  $I_{load}$

- Silver (Zn/Ag<sub>2</sub>O) Button cells, very flat discharge in the first 3/4 of charge

- Zinc-air ( $ZnO_2$ ) High energy density, flat discharge but once the seal gets removed it has a short life span

#### Secondary batteries (rechargeable)

- Lithium-ion (Li-ion) Popular, high energy density, 3.6 V/cell, flat and very low self-discharge, safety issues

- Nickel metal-hydride (NiMH) Cheap, popular, AA/9V packages with 1.2V/cell, flat discharge

- Lead-acid (Pb-acid) High current due to low  $R_{int}$ , flat discharge, moderate self discharge 1.4 [1]

# 1.3 Switch mode power supplies

Often one power supply is not enough as different components require different voltages to operate, which means additional step up or step down circuits are required. The easiest way how to step down with voltage is to use a voltage regulator such as LM78XX series which is a linear regulator but issue with such conversion is a very small efficiency because the regulator converts the excess voltage to heat which is less than ideal when working with batteries as power supplies. Another way how to step up or down voltages is using buck, boost or buck-boost together converters which can be bough as self-contained modules. This type of converters are called switch mode power supplies (SMPS) as they use a switch, usually a MOSFET together with pulse width modulation signal (PWM) to cause rapid switching of the MOSFET. Both topologies use the ability of an inductor to store energy.

## 1.3.1 Buck Converters

Buck converters are circuits where  $V_{out}$  is less than  $V_{in}$ , as can be seen in Figure 1.5 below. The way it works is that when switch is closed  $V_{out} - V_{in}$  is applied across the coil therefore magnetic field energy raises and is stored in the coil. As soon as the switch opens,  $V_{out} - V_{diode}$  voltage is applied and the coil continues to deliver current in the same direction as coils can not change the direction of the current suddenly. The capacitor on the output smooths out voltage ripple which would occur otherwise. The output voltage value depends on the duty cycle therefore  $V_{out} = DV_{in}$ , D is the duty cycle calculated as  $D = t_{on}/T$ , where the T is the switching period  $T = t_{on} + t_{off}$  [1]

Fig. 1.5: Scheme with basic buck converter topology

## 1.3.2 Boost Converters

Boost converters are the opposite of buck converters  $(V_{out}>V_{in})$ , see Figure 1.6 below. Operation of this circuit is very simple as well. When the switch is closed, the coil starts to accumulate energy in form of magnetic field, once the switch opens, the inductor maintains the current and therefore the current flows through the diode and charges the capacitor. Output voltage therefore is  $V_{out} = \frac{1}{1-D}V_{in}$ ,  $D = t_{on}/T$ , where the T is the switching period $(T = t_{on} + t_{off})$  [1]

Fig. 1.6: Scheme with basic boost converter topology

# 1.3.3 Buck-boost topologies

Combining the two circuits mentioned above into one creates the buck-boost topology circuit which is able to either increase or decrease output voltage. As can be seen in Figure 1.7 below, only one excessive capacitor needs to get removed and the two coils are replaced by one.

Fig. 1.7: Scheme with basic buck-boost converter topology

# 1.3.4 Inverting charge pump

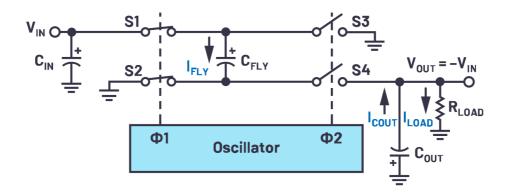

Negative voltages are often required when working for with operational amplifiers, circuits which are able to convert positive voltages to negative ones are called inverting charge pumps. The operation principle can be divided to two phases  $\phi 1$  and  $\phi 2$  that can be seen in the Figure 1.8 below. In the first phase switches S1 and S2 are closed while switches S3 and S4 remain opened. Positive input voltage starts the charging process of  $C_{FLY}$ . After certain period of time when  $C_{FLY}$  is charged, the second phase begins. Switches S1 & S2 are opened resulting in input voltage being disconnected and switches S3 & S4 are closed.  $C_{FLY}$  is discharged and reversed polarity of GND and output results in negative output voltage. After the discharge process phase 1 begins.

Fig. 1.8: Scheme with basic inverting charge pump topology [17]

# 1.4 Operational Amplifiers

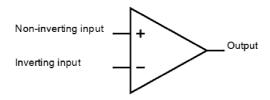

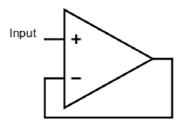

Operational amplifiers (Op-amps) are one of the most used integrated circuits (ICs) as they are basically building blocks in any analog circuit, schematic symbol can be seen in Figure 1.9 below. Operational amplifiers are DC-coupled differential amplifiers with high gain values. The impedance characteristics of any operational amplifier are very high (infinite in ideal case) input impedance and very small (zero) output impedance. Any op-amp will always try its best to equalize the difference between the inverting and non-inverting input. The maximum output voltage is limited to the power supply  $(-12\,\mathrm{V},\,+12\,\mathrm{V}...)$  but sometimes due to the imperfections of the components the limit is lower. Operational amplifiers which can swing across their whole power supply voltage range are called rail-to-rail op-amps.

Fig. 1.9: Default schematic symbol of an operational amplifier

#### **Inverting op-amp**

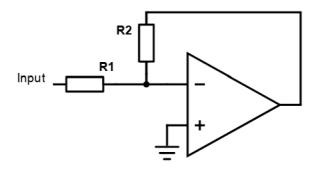

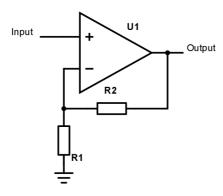

One of the most used op-amp circuits is inverting amplifier which amplifies the signal and turns the phase by 180°. Creation of an inverting op-amp can done with two resistors together with an operational amplifier as seen in Figure 1.10 below. The two resistors set the gain of an inverting op-amp. Having a resistor R1 on the input and a resistor R2 in the inverting feedback loop will create a voltage divider which sets the voltage gain of the amplifier i.e. the ration of the resistor in the feedback loop and the resistor on the input sets the gain which can be calculated as  $G = -\frac{R2}{R1}$ .

Fig. 1.10: Schematic of an inverting op-amp circuit

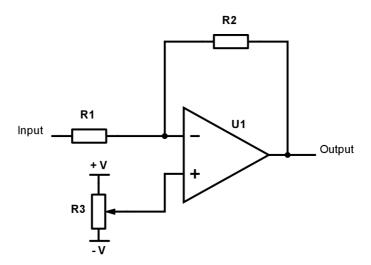

In some scenarios removal of an offset voltage is required because of compensating for component's imperfections or because of the need to add or remove the offset. All that is required is adding a potentiometer to the non-inverting input as seen in Figure 1.11 below. Powering the potentiometer by some reference voltage gives us two voltage rails between which we can choose the offset. The voltage powering the potentiometer does not have to be the same voltage powering the op-amp, actually it may be even more convenient to use lower supply voltage for the potentiometer because using lower voltage makes it more precise and therefore easier to use. The reason for this is the fact that the offset voltage made at potentiometer gets amplified with the same gain as the input signal. Added DC voltage together with input signal's amplitude must not exceed op-amps power supply voltage levels as the signal would get immediately distorted.

Fig. 1.11: Schematic of an inverting op-amp circuit with variable offset

#### Non-inverting op-amp

Non-inverting amplifier is another amplifying circuit which can be created with an op-amp and two resistors. The closed feedback loop is connected to the inverting input and grounded while the input signal is connected to the non-inverting input as seen in Figure 1.12 below. The gain can be calculated as  $G = 1 + \frac{R^2}{R^1}$

Fig. 1.12: Schematic of a non-inverting op-amp circuit

### Voltage follower

Impedance characteristics of an op-amp are also looked up at while creating a voltage follower also known as a buffer which is essentially a non-inverting amplifier circuit where  $R_{in} = \infty$  and  $R_{out} = 0$ , such values ensure that the current draw is minimal while maintaining the voltage and this can be used in various applications such as impedance matching. Sometimes an additional resistor may be connected in the closed loop shown in Figure 1.13 to ensure stability.

Fig. 1.13: Schematic of a voltage follower op-amp circuit

# 1.5 Communication

### 1.5.1 **UART**

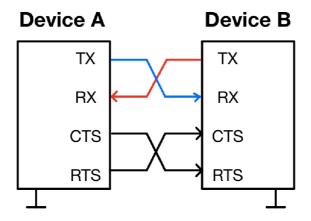

UART, also known as universal asynchronous receiver/transmitter was one of the earliest serial interfaces used for data exchange between two devices point-to-point. Only two wires are required for the data transfer – Tx and Rx), sometimes control flow signals are used such as RTS and CTS but they are not required for smooth operation. The only condition that has to be met between sender and receiver is the baud rate, which is the number of symbols transmitted per second. Both transmitter and receiver baud rates have to be set to the same value, common UART baud rates are 4800, 9600, 19200...1151200. According to the ability to transmit or receive data UART can be divided as:

Simplex – data can be only sent or received

Half-duplex – data can be sent or received but only one at a time

Full-duplex – data can be sent and received at one time simultaneously

Fig. 1.14: UART wiring diagram

UART can work in multiple frame structure modes (7E2, 8N1). The first number represents the number of data bits, the letter E/N represents even parity<sup>1</sup> or no parity and the last number represents the number of stop bits. The serial transmission is little endian meaning the least significant bit (LSB) is transmitted first.

<sup>&</sup>lt;sup>1</sup>Even parity– The number of 1 bits needs to be even and vice versa for the odd parity

| Start Bit | Data Frame         | Parity Bits    | Stop Bits     |

|-----------|--------------------|----------------|---------------|

| (1 bit)   | (5 to 9 Data Bits) | ( 0 to 1 bit ) | (1 to 2 bits) |

Fig. 1.15: UART timing diagram [16]

## 1.5.2 USB CDC

Universal Serial Bus Communication Device Class, also known as USB CDC is a protocol which is used in USB communication where devices need to transfer/receive data. It is also possible to have multiple interfaces rather than one. The class can be used with devices that used previously serial COM port or UART. Since the class is capable of creating VCOM (Virtual Communication Port) it means software can be easily modified to support this protocol. Variety of platforms support USB CDC and therefore it fits all sorts of application where wired communication between devices is needed. [18], [19]

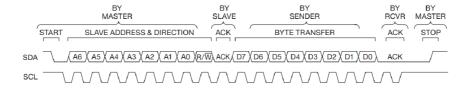

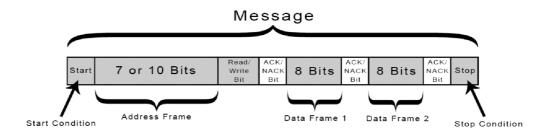

## 1.5.3 I2C

I2C stands for inter-integrated circuit which is two-wire synchronous bi-directional, half-duplex and short distance serial bus communication. The two wires which are used are serial clock (SCL) and serial data (SDA). Compared to SPI, I2C has the advantage in terms of connectivity as the master can operate with multiple slave devices without the need to use some of select signal. By default both signal lines are connected with a pull-up resistors until the start of communication begins and start condition is generated. Start condition is generated by pulling SCL down and then data on SDA line are transferred. After a data transfer a stop condition is generated by letting SDA from 0 to 1 after SCL being pulled from 0 to 1 and remaining high. This process can be seen in Figure 1.16 below.

Fig. 1.16: I2C timing diagram [1]

Transfer diagram can be seen in figure 1.17 below.

Fig. 1.17: I2C transfer diagram [14]

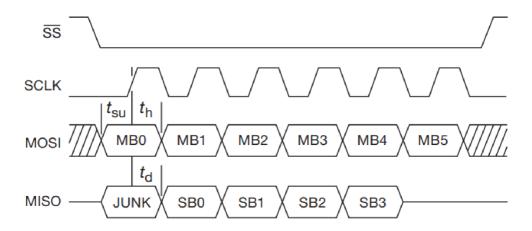

# 1.5.4 SPI

Serial peripheral interface (SPI) is a master-slave communication protocol between a MCU and peripheral IC's such as sensors, GPS modules etc. Working principle is very similar to I2C with the main difference being an additional wires to SDA and SCL. MOSI (Master out, slave in) is used to send data from the MCU to modules, MISO (Master in, slave out) wire transmits data from connected module to the MCU and SS (Slave select) wire being used to select with which module the communication will be established. The advantage of SPI communication compared to I2C is the support of higher clock frequencies. Timing diagram can be seen in figure 1.18 below.

Fig. 1.18: SPI transfer diagram [14]

## 1.5.5 SCPI

Standard Commands for Programmable Instruments, known as SCPI is a communication protocol used in field of electronic measurement instruments. The protocol unifies sets of commands and syntax across different brands of manufacturers such as Agilent, Rohde & Schwarz or Tektronix. [1]. Each command has usually a second or third parameter which is always separated by a colon, in case where multiple commands are written in the same line they must be separated by a semicolon. Some commands resolve in an answer from an instrument, this type of commands must be followed by a question mark. Example commands are listed below, the protocol itself is not case sensitive.

#### Examples of commands

OUTPUT:START - Sets the instrument's output on

FREQ:500 - Sets the instrument's output signal frequency to 500 Hz

MEASURE: VOLTAGE: DC? - Asks the instrument to measure DC voltage and re-

# 2 Hardware design

## 2.1 Microcontroller

Generator operation and control is designed to be done with the help of a micro-controller. For a portable project as this one the most important characteristic in addition to basic specifications such as flash and RAM memory, communication peripherals, internal oscillators which was looked for was low power demand, power efficiency and operating voltage. Two main contenders to choose from were AT-Mega328P microcontroller which is commonly used in Arduino boards and STM32 L5 series MCU used in STMicroelectronics NUCLEO boards. As will be mentioned later in the thesis, final design utilizes STM32F411 MCU. Comparison of the individual microcontrollers can be found in the Table 2.1 below.

| ATMega328P                                   | STM32L562                          | STM32F411 BlackPill     |  |

|----------------------------------------------|------------------------------------|-------------------------|--|

| Op. voltage 1.8 - 5.5 V                      | 1.71 - 3.6 V                       | 1.7 - 3.6 V             |  |

| Power con. 8 mA @5V                          | Power con. : $106 \mu\text{A/MHz}$ | Power con. : 100 µA/MHz |  |

| 32 KB Flash                                  | up to 512 KB Flash                 | up to 512 KB Flash      |  |

| 2 KB SRAM                                    | KB SRAM 256 KB SRAM                |                         |  |

| UART                                         | 6x USART                           | 3x USART                |  |

| 1x I2C 4x I2C                                |                                    | 3x I2C                  |  |

| 1x SPI 3x SPI                                |                                    | 5x SPI                  |  |

| 2 8-bit, 1 16-bit timers   16 timers         |                                    | 11 timers               |  |

| 8 MHz oscillator 4 to 48 MHz oscillator 25 N |                                    | 25 MHz oscillator       |  |

Tab. 2.1: A comparison between ATMega328P, STM32L562 and STM32F411 MCUs [9], [10], [11]

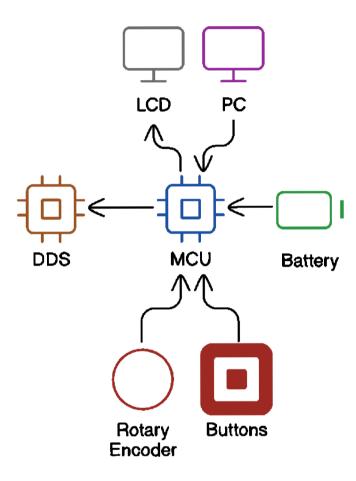

## 2.1.1 Connected peripherals

These components are connected to the MCU:

- Rotary encoder Rotary encoder KY-040 is connected to provide easy control of frequency setting

- **DDS chip** AD9833 programmable waveform generator IC is connected to the MCU which will set the output characteristics by writing into the IC through the SPI bus

- LCD display A 16x2 LCD is connected to the MCU and will display current output waveform, amplitude, frequency and impedance mode.

- **Push-buttons** Push-buttons are used for efficient control of the generator and choosing output impedance mode

- Battery cell Battery cell is connected to the MCU for battery state tracking purposes

Peripherals are connected as shown in the block scheme in Figure 2.1 below.

Fig. 2.1: Communication block scheme

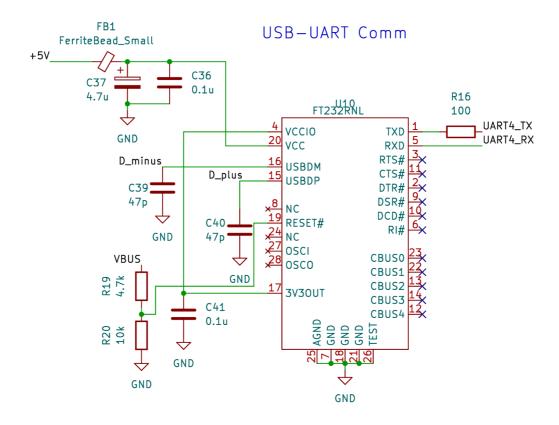

#### **UART**

For automatic measurements the generator can be connected to a PC via UART. The working principle of the UART communication is explained more in detail in the theory chapter 1.5.1. By default the USB-C connector has 2 mirrored data pins D+ and D- that can not be used for the UART communication without suitable converter. The conversion of data lines D+ and D- to UART data lines is done through USB-UART bridge, for this particular application the USB-UART FTDI's IC FT232RNL is used. Since the IC operates at 3.3 V whereas the MCU at 3 V, to make sure the MCU will not get damaged a  $100\,\Omega$  resistor is connected in series between breakout board's Tx pin and MCU's Rx pin.

The picture in Figure 2.2 below shows the IC wiring. When the generator is not connected via the USB-C connector, the IC is in sleep mode to prevent possible unwanted data transfers.

Fig. 2.2: USB-UART Bridge wiring [12]

## **SCPI**

As previously mentioned, for automatic measurement the generator uses UART to transfer data from a computer via serial monitor program (i.e. PuTTY).

To make the communication as efficient and clear as possible, SCPI<sup>1</sup> communication protocol is implemented, more theory about the protocol itself can be found in the theory Chapter 1.5.5.

The list of commands available for the generator is shown below.

#### List of commands

## Waveform adjustment:

```

WAVEform: SINE //WAVEFORM or WAVE + SINE/SQUARE/TRIANGLE

```

## Frequency adjustment:

```

FREQuency:500 //FREQUENCY or FREQ + value from 1 to 12.5

```

## Amplitude adjustment:

```

AMPLitude:5 //AMPLITUDE or AMPL + value from 0.12 to 12

Vpp

```

## Offset adjustment:

```

OFFset:2 //OFFSET or OFF + offset value [V]

```

### Output impedance adjustment:

```

RESistance:50 //RESISTANCE or RES + 50 or HighZ

```

### Output adjustment:

```

OUTPut:START //OUTPUT or OUTP + START or STOP

```

## Battery voltage measurement:

```

MEASURE: VOLTAGE: BATTERY? // MEAS: VOLT: BATTERY?

```

<sup>&</sup>lt;sup>1</sup>SCPI – Standard Commands for Programmable Instruments

### I2C

Inter-integrated circuit (I2C) communication protocol is being used in this design to send data to generator's LCD display and two digital potentiometers which are used for amplitude and offset control, more about the I2C can be seen in the theory Chapter 1.5.3

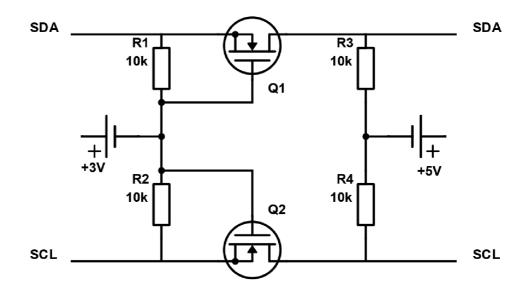

Logic levels Usage of devices that operate at different voltage levels when working with data lines can be problematic as the device operating at higher voltage may damage the device operating at lower voltage. In this project a 5 V powered liquid crystal display (LCD) is going to be used with an MCU that is going to operate 3 V. That is why a MOSFET logic level shifter will be used between the two devices for each data line as shown in Figure 2.3 below. This implementation is sufficient enough to convert logic levels without delay and therefore can be used in this application.

Fig. 2.3: MOSFET logic level shifter [15]

#### SPI

Serial peripheral interface (SPI) is used for communication between the MCU and AD9833 waveform generator IC, more about this communication can be found in the theory chapter, 1.5.4.

## 2.2 Waveform generation

The goal of this bachelor thesis was to design a function generator which would able to generate at least three waveforms, therefore the decision was to create a sine, triangle and PWM generator. Multiple ways exist how to create such waveforms – analog way, DDS or through a MCU using DAC.

## 2.2.1 Analog waveform generation

One way how to create a simple waveform generator is cascading three operational amplifiers as shown in Figure 2.4 below.

The first operational amplifier is an oscillator, it creates a square – PWM signal which can be adjusted in frequency with the pontentiometer. Other two operational amplifiers are connected as integrators, first of them creates a triangle wave from the PWM signal and the last integrates the triangle wave on it's input and thus creates a sine wave.

This solution is very easy to implement, although it's efficiency is not great as the created waveforms are not perfect, can be very distorted, the frequency range is not sufficient enough and amplitude fluctuates with frequency. MCU's ability to create the PWM signal together with the analog method explained above could be also an option but the issues tied with the analog way would remain therefore this way was not found to be suitable solution either.

Fig. 2.4: Analog waveform generation

## 2.2.2 Digital waveform generation

Another option how to create suitable waveforms is to go digital with a direct digital synthesis chip which is able create desired waveforms. Working principle of such chips is explained in detail in the DDS chapter, see Figure 1.1.2.

AD9833 DDS IC was chosen as it is low power, programmable waveform generator capable of producing sine, square and triangular waves, with adjustable output frequency and phase.

### AD9833 Features

- 12.65 mW power consumption AD9833 Features @ 3 V

- 0.1 Hz to 12.5 MHz output frequency range

- Sinusoidal, triangular and square wave outputs

- 3 wire SPI interface

Other important features such as adjustable amplitude and offset are designed to be done through analog part of the circuit with operational amplifiers.

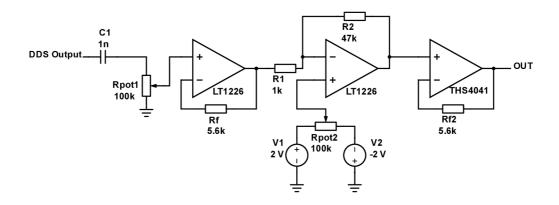

# 2.3 Analog backend

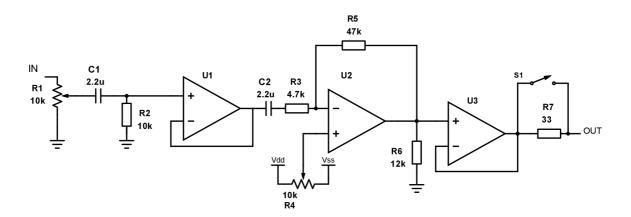

As mentioned before, the AD9833 chip itself does not have the option to tune the output amplitude or offset, that is why an analog part in form of operational amplifiers was required to take care of this problem. Operational amplifiers are connected to the output of the DDS chip in this configuration as in figure 2.5 below. The potentiometers on the image are just referential, real design implements digital potentiometers for more convenient usage.

Fig. 2.5: Operational amplifier connection

## Working principle

The first operational amplifier LT1226, connected as a voltage follower is fed with filtered DDS output waveform and together with the first digital pontentiometer it is designed to work as tunable amplitude attenuator, the reasoning for using this voltage follower is to not put load on the digital potentiometer.

The second operational amplifier, also the LT1226 is in inverting amplifier configuration with the gain of 47. Digital potentiometer connected to its non-inverting input serves as an offset adjuster.

The third operational amplifier THS4041 is connected as a voltage follower because of his characteristics and is used for short circuit protection as it is able to withstand up to 150 mA short circuit current. Both voltage followers have a  $5.6\,\mathrm{k}\Omega$  resistors connected in their feedback as a protection against oscillation which may occur due to fast slew rates of such operational amplifiers.

### Characteristics of chosen operational amplifiers

| LT1226                                                                                                                                             | THS4041                                                                                                                                             | TL071                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>400 V/µs Slew Rate</li> <li>1 mV Maximum off-set voltage</li> <li>2.6 nV/√Hz Input voltage noise</li> <li>1 GHz Gain bandwidth</li> </ul> | <ul> <li>400 V/µs Slew Rate</li> <li>13 mV Maximum offset voltage</li> <li>14 nV/√Hz Input voltage noise</li> <li>165 MHz Gain bandwidth</li> </ul> | <ul> <li>20 V/µs Slew Rate</li> <li>1 mV Maximum offset voltage</li> <li>18 nV/√Hz Input voltage noise</li> <li>5.25 MHz Gain bandwidth</li> </ul> |

[6], [5], [7]

## 2.4 Power supply

The portability of the project depended on finding a suitable power supply, either a battery or a power cell. After all needs for this project were considered, an idea of using a battery with a battery management system (BMS) was found to be unnecessary. Samsung's Lithium- ion 18650 3500 mAh cell was chosen for this project as it fits all requirements such as nominal voltage and capacity, detailed characteristics are shown below.

## 18650 Cell specifications[4]

- 3500 mAh capacity

- 3.6 V nominal voltage

- 1 A charging current

- 1 year self-discharge time (-20 25 °C)

As described in chapter 1.2 about power cells, Lithium-ion batteries require a special treatment when they are getting charged because they can easily overheat and explode. That is why a charging module with TP4056 chip was used to protect the power cell from overcharging or charging with overcurrent and therefore minimizing the risk of damaging the cell.

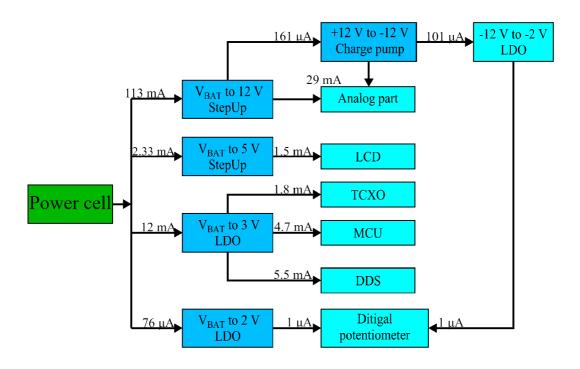

## 2.4.1 Power distribution & consumption

The designed circuit consists of parts which require different voltage levels than the one provided by the battery, multiple voltage converters are used to convert  $\pm$  3.6 V provided by the battery.

### List of used converters

$\mathbf{LP2950CZ}$  LDO  $V_{BAT}$  to  $3\,V$

**TPS7A02** LDO  $V_{BAT}$  to 2 V

**XC6902** LDO -12 V to -2.5 V

**L6920DC** Step up  $V_{BAT}$  to 5 V

**LM2621** Step up 5 V to 12 V

LTC3261 Inverting charge pump -12 V to 12 V

#### **Power consumption**

Figure 2.6 below shows connection between different converters and parts which they supply together with their power consumption.

Fig. 2.6: Power distribution & consumption block scheme

The summation of above listed power consumption is 127.406 mA with some elements being excluded such as relay, electrostatic discharge (ESD) protection or USB-UART bridge which will be either used randomly or only when connected to an external power supply therefore the expected power consumption should not exceed 130 mA.

Considering using 3500 mAh cell and assuming maximum of 130 mA current consumption, the estimated battery life can be calculated with this formula considering no load being on the output.

As can be seen on the figure 2.6, the chosen step up module is not ideal for this application as it's current consumption is way above other component's current consumption.

Pleas note, that his block scheme is for the initial design only, final design had to be adjusted and the power consumption increased to 0.7 A.

# 3 Software & UI overview

A brief showcase of the overall mechanical & graphical user interface (UI) will be explained in the first part of this chapter. Second part of the chapter will go through the software where snippets of code will get explained into detail.

## 3.1 UI

The user interface consists of a rotary encoder and rotary buttons, push buttons, LCD, battery warning LED and the main switch. Overall layout can be seen in the Figure 3.1 below.

Fig. 3.1: Front panel layout

#### Rotary encoder

The rotary encoder is positioned on the far left on the top next to the LCD panel. By turning the rotary encoder the frequency can be adjusted. Current frequency setting can be seen in the first line of the LCD.

### Rotary buttons

Below the rotary encoder positioned on the top, two rotary buttons are located. Those rotary buttons are two potentiometers which are used for the amplitude and DC offset adjustments. The button on the left serves as an amplitude adjuster and the on on the right is used for DS offset adjustment.

#### Arrow left and arrow right buttons $\leftarrow \rightarrow$

The two arrow buttons are used to fine adjust frequency. Each press either increments or decrements the order of magnitude of the frequency and corresponding position is displayed on the LCD panel as is showcased in Section 3.2.3.

### Waveform button

Waveform button (WV) is used to switch between each waveform type (SINE, TRIANGLE or SQUARE). The information about current waveform setting is displayed on the second line of the LCD as can be seen in the Figure 3.1 above.

## Impedance button

The impedance lever switch button is used to toggle between 50  $\Omega$  and HighZ impedance modes.

### **LED** indicator

LED indicator is located on the front panel to indicate the state of the battery. Software is programmed for the the LED to light up when the battery reaches  $\pm$  10 % of it's capacity.

## 3.2 Software

In this section an overall structure and working principle of the software will be displayed, in some cases code blocks will be shown and explained into detail.

### 3.2.1 ADC

Analog to digital converter peripheral is used to convert the battery cell voltage in purpose of tracking the remaining battery cell capacity. The ADC is initialized in the interrupt mode as it is the most suitable way for this application.

```

//Get ADC value

void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef* hadc

{

adc_value = HAL_ADC_GetValue(&hadc1);

}

//ADC voltage calculation

float adc_voltage(uint32_t adc_value)

{

float reference = 3.0;

float batteryVoltage = ((adc_value / 4095.0) *

reference) * 2;

if (batteryVoltage <= 3.5)</pre>

{

HAL_GPIO_WritePin(GPIOA, GPIO_PIN_6,

GPIO_PIN_SET);

}

else

{

HAL_GPIO_WritePin(GPIOA, GPIO_PIN_6,

GPIO_PIN_RESET);

return batteryVoltage;

}

```

Listing 3.1: Sample code for ADC evaluation

The block of code shown in Listing 3.1 listed above shows the process of converting the digital voltage value to analog voltage. First, the digital value gets repeatedly read by the HAL ADC ConvCpltCallback function. Then the voltage gets converted

in the adc\_voltage function which also sets the value where the battery LED indicator should light up. Because of the Li-Ion battery discharge curve characteristic, an exact battery percentage is not possible to be tracked in this application and the battery LED indicator is programmed to light up when 10 - 15% of battery capacity is remaining.

When using STM32 Cube IDE software, version 1.15.0 a bug was found. Due to the bug the ADC does not get set into sequential conversion mode despite choosing this method in the graphical MX UI. The voltage at the ADC channel gets scanned only once when being powered up. This bug can be worked around by manually rewriting the auto-generated ADC setup code as can be seen in Listing 3.2 below.

```

static void MX_ADC1_Init(void)

{

//AUTO GENERATED CODE

...

hadc1.Init.EOCSelection = ADC_EOC_SINGLE_CONV; //->

hadc1.Init.EOCSelection = ADC_EOC_SEQ_CONV; //

CubeMX bug correction

...

}

```

Listing 3.2: Sample code for ADC bug correction

After rewriting this line of code, the ADC starts to work in the continuous conversion mode and reads voltage values but the main program taking care of the generator's functionality gets halted and does not respond to any interactions, because of this the low battery LED indicator was not implemented.

## 3.2.2 Mechanical UI

## Rotary encoder

The rotary encoder is intended for adjustment of multiple parameters and therefore tracking only it's value would not be effective and potential overflows could be problematic. For this purposes the rotation direction is tracked instead and every tick gets registered as can be seen in the Listing 3.3 below.

```

// Rotary encoder

void RotaryEncoderUpdate(void) //Track rotation

{

encoderValue=TIM1->CNT;

if(encoderValue != encoderValueOld)

{

if(encoderValue > encoderValueOld)

{

direction = 1;

}

else

{

direction = -1;

}

encoderValueOld=encoderValue;

}

}

```

Listing 3.3: Sample code for rotary encoder

#### **Buttons**

Button interfaces are very effective but because of contact imperfections, bounces happen. In such scenarios the button press is registered multiple times and causes incorrect tracking. To ensure the button presses are tracked correctly, debounce functions are implemented. Debouncing can be done in various ways and the approach may vary depending on the usage since in some scenarios simple delay function is sufficient. For this particular case a different approach was chosen as halting the MCU processes after each button press is not efficient. Code snippet listed below in the Listing 3.4 shows the implementation of Debounce function which is used.

```

void Debounce(void) //Debounce function

{

static uint16_t debounce = 0x0000;

uint32_t currentTime = HAL_GetTick();

static uint32_t lastUpdate = 0;

if ((currentTime - lastUpdate) >= DEBOUNCE_TIME)

{

debounce <<= 1;

if (HAL_GPIO_ReadPin(GPIOB,GPIO_PIN_2) ==

GPIO_PIN_RESET)

{

debounce \mid = 0x0001;

}

lastUpdate = currentTime;

if (debounce == 0x7FFF)

//BUTTON ACTION

}

}

}

```

Listing 3.4: Sample code for button debouncing function

If button is not pressed, the 16-bit register debounce is full of zeros (0x0000). With each tick the value is being shifted to the left by 1 position. In case where a button press occurs the debounce register gets bit OR'd with a singular 1 (0x001). A button press gets registered in case where the button is held down long enough for the bounce register to get gradually filled up with ones. As soon as the register

gets filled up to contain the hexadecimal value 0x7FFF, the button press function gets executed and an additional 5 ms debounce delay starts to ensure a successful debounce.

### 3.2.3 LCD

Library for interfacing with the 16x2 LCD panel was taken from Controllerstech website [20]. In the Figure 3.2 shown below, the LCD UI is displayed. The panel displays information of current waveform, frequency and increment value by which the frequency value will get incremented or decremented with each rotary encoder click.

Fig. 3.2: LCD UI layout

### 3.2.4 AD9833

Interactions between the MCU and the AD9833 DDS IC are possible due to a library which was taken from Mr. Vitech [21].

## 3.2.5 Amplitude and DC offset adjustment

The software for amplitude and DC offset (later in the text only offset) adjustment was created before the project had to be converted into analog adjustments only. The amplitude and offset were supposed to be adjusted by two channel digital potentiometer. Adjustment functions work around tracking the current position of wipers of the digital potentiometer. With SCPI in mind, a functions called createAmplitudeArray and findClosest were created to ensure the correct amplitude value would get set based on the input of an user.

Code snippet of the createAmplitudeArray function can be found in the Listing 3.5 bellow. With  $390.25 \Omega$  steps of the digital potentiometer in mind, the created array gets populated by all possible voltage values.

```

#define AMPLITUDESTEP 0.12

void createAmplitudeArray(float* amplitudeArray)

{

for (int i = 0; i < 101; i++)

{

amplitudeArray[i] = i * AMPLITUDESTEP;

}

}</pre>

```

Listing 3.5: Sample code for createAmplitudeArray function

Function findClosest which is showcased in Listing 3.6 takes the user input from the serial terminal and searches for the closest value which would then get selected.

```

typedef struct {

size_t position;

float value;

} ClosestResult;

ClosestResult findClosest(float* array, size_t size,

float target) {

ClosestResult result;

result.position = 0;

result.value = array[0];

float minDelta = fabsf(target - result.value);

for (size_t i = 1; i < size; i++) {</pre>

float delta = fabsf(target - array[i]);

if (delta < minDelta) {</pre>

result.position = i;

result.value = array[i];

minDelta = delta;

}

}

return result;

}

```

Listing 3.6: Sample code for findClosest function

## 3.2.6 SCPI

Standard Commands for Programmable Instruments communication protocol was programmed with intentions to allow users to interact with the device through a serial terminal such as PuTTY or Termite which use virtual communication ports (VCOM). Originally the device was designed to use UART for communication but the onboard MCU was not used in the final design. A development board BlackPill with STM32F411 MCU was used together with USB CDC protocol instead. More information about those types of communications can be found in Sections 1.5.1 and 1.5.2.