# VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

BRNO UNIVERSITY OF TECHNOLOGY

FAKULTA INFORMAČNÍCH TECHNOLOGIÍ ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

FACULTY OF INFORMATION TECHNOLOGY DEPARTMENT OF COMPUTER SYSTEMS

# METODY AKCELERACE EVOLUČNÍHO NÁVRHU ČÍSLICOVÝCH OBVODŮ

ACCELERATION METHODS FOR EVOLUTIONARY DESIGN OF DIGITAL CIRCUITS

DISERTAČNÍ PRÁCE

PHD THESIS

**AUTOR PRÁCE**

Ing. ZDENĚK VAŠÍČEK

**AUTHOR**

VEDOUCÍ PRÁCE

Prof. Ing. LUKÁŠ SEKANINA, Ph.D.

**SUPERVISOR**

**BRNO 2012**

#### Abstrakt

Ačkoliv můžeme v literatuře nalézt řadu příkladů prezentujících evoluční návrh jakožto zajímavou a slibnou alternativu k tradičním návrhovým technikám používaným v oblasti číslicových obvodů, praktické nasazení je často problematické zejména v důsledku tzv. problému škálovatelnosti, který se projevuje např. tak, že evoluční algoritmus je schopen poskytovat uspokojivé výsledky pouze pro malé instance řešeného problému. Vážný problém představuje tzv. problém škálovatelnosti evaluace fitness funkce, který je markantní zejména v oblasti syntézy kombinačních obvodů, kde doba potřebná pro ohodnocení kandidátního řešení typicky roste exponenciálně se zvyšujícím se počtem primárních vstupů.

Tato disertační práce se zabývá návrhem několika metod umožňujících redukovat problem škálovatelnosti evaluace v oblasti evolučního návrhu a optimalizace číslicových systémů. Cílem je pomocí několika případových studií ukázat, že s využitím vhodných akceleračních technik jsou evoluční techniky schopny automaticky navrhovat inovativní/kompetitivní řešení praktických problémů.

Aby bylo možné redukovat problém škálovatelnosti v oblasti evolučního návrhu číslicových filtrů, byl navržen doménově specifický akcelerátor na bázi FPGA. Tato problematika reprezentuje případ, kdy je nutné ohodnotit velké množství trénovacích dat a současně provést mnoho generací. Pomocí navrženého akcelerátoru se podařilo objevit efektivní implementace různých nelineárních obrazových filtrů. S využitím evolučně navržených filtrů byl vytvořen robustní nelineární filtr implusního šumu, který je chráněn užitným vzorem. Navržený filtr vykazuje v porovnání s konvenčními řešeními vysokou kvalitu filtrace a nízkou implementační cenu.

Spojením evolučního návrhu a technik známých z oblasti formální verifikace se podařilo vytvořit systém umožňující výrazně redukovat problém škálovatelnosti evoluční syntézy kombinačních obvodů na úrovni hradel. Navržená metoda dovoluje produkovat komplexní a přesto kvalitní řešení, která jsou schopna konkurovat komerčním nástrojům pro logickou syntézu. Navržený algoritmus byl experimentálně ověřen na sadě několika benchmarkových obvodů včetně tzv. obtížně syntetizovatelných obvodů, kde dosahoval v průměru o 25% lepších výsledků než dostupné akademické i komerční nástroje.

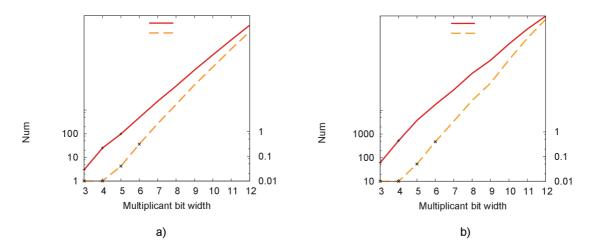

Poslední doménou, kterou se práce zabývá, je akcelerace evolučního návrhu lineárních systémů. Na příkladu evolučního návrhu násobiček s vícenásobnými konstantními koeficienty bylo ukázáno, že čas potřebný k evaluaci kandidátního řešení lze výrazně redukovat (defacto na ohodocení jediného testovacího vektoru), je-li brán v potaz charakter řešeného problému (v tomto případě linearita).

## Klíčová slova

návrh číslicových obvodů, evoluční optimalizace, evoluční návrh, násobička s konstantními koeficienty, filtrace obrazu, nelineární filtr, optimalizace kombinačních obvodů, FPGA akcelerace

# Citace

Zdeněk Vašíček: Acceleration Methods for Evolutionary Design of Digital Circuits, disertační práce, Ústav počítačových systémů, FIT VUT v Brně, Brno, CZ, 2012

## Abstract

Although many examples showing the merits of evolutionary design over conventional design techniques utilized in the field of digital circuits design have been published, the evolutionary approaches are usually hardly applicable in practice due to the various so-called scalability problems. The scalability problem represents a general problem that refers to a situation in which the evolutionary algorithm is able to provide a solution to a small problem instances only. For example, the scalability of evaluation of a candidate digital circuit represents a serious issue because the time needed to evaluate a candidate solution grows exponentially with the increasing number of primary inputs.

In this thesis, the scalability problem of evaluation of a candidate digital circuit is addressed. Three different approaches to overcoming this problem are proposed. Our goal is to demonstrate that the evolutionary design approach can produce interesting and human competitive solutions when the problem of scalability is reduced and thus a sufficient number of generations can be utilized.

In order to increase the performance of the evolutionary design of image filters, a domain specific FPGA-based accelerator has been designed. The evolutionary design of image filters is a kind of regression problem which requires to evaluate a large number of training vectors as well as generations in order to find a satisfactory solution. By means of the proposed FPGA accelerator, very efficient nonlinear image filters have been discovered. One of the discovered implementations of an impulse noise filter consisting of four evolutionary designed filters is protected by the Czech utility model.

A different approach has been introduced in the area of logic synthesis. A method combining formal verification techniques with evolutionary design that allows a significant acceleration of the fitness evaluation procedure was proposed. The proposed system can produce complex and simultaneously innovative designs, overcoming thus the major bottleneck of the evolutionary synthesis at gate level. The proposed method has been evaluated using a set of benchmark circuits and compared with conventional academia as well as commercial synthesis tools. In comparison with the conventional synthesis tools, the average improvement in terms of the number of gates provided by our system is approximately 25%.

Finally, the problem of the multiple constant multiplier design, which belongs to the class of problems where a candidate solution can be perfectly evaluated in a short time, has been investigated. We have demonstrated that there exists a class of circuits that can be evaluated efficiently if a domain knowledge is utilized (in this case the linearity of components).

# **Keywords**

digital circuit design, evolutionary optimization, evolutionary design, multiplier with constant coefficients, image filtering, nonlinear filter, optimization of combinational circuits, FPGA acceleration

# Bibliographic citation

Zdeněk Vašíček: Acceleration Methods for Evolutionary Design of Digital Circuits, PhD thesis, Department of Computer Systems, FIT BUT, Brno, CZ, 2012

# Acceleration Methods for Evolutionary Design of Digital Circuits

## Prohlášení

Prohlašuji, že jsem tuto disertační práci vypracoval samostatně pod vedením Prof. Ing. Lukáše Sekaniny, Ph.D., a že jsem uvedl všechny literární prameny, ze kterých jsem v průběhu své práce čerpal.

Zdeněk Vašíček 9. března 2012

## Poděkování

Na tomto místě bych rád poděkoval všem, kteří přispěli k tomu, že tato práce vznikla. Především mému vedoucímu disertační práce Prof. Ing. Lukáši Sekaninovi, Ph.D. za řadu podnětných diskuzí týkajících se tématu disertační práce, metodické vedení a spolupráci při výzkumu. Dále děkuji všem spolupracovníkům za vstřícnost a spolupráci při řešení jednotlivých částí disertační práce. V neposlední řadě bych rád poděkoval svým rodičům, ženě a všem blízkým za podporu během studia i psaní této práce.

Výsledky této práce vznikly za podpory Grantové agentury české republiky a Ministerstva školství, mládeže a tělovýchovy v rámci projektů: Matematické a inženýrské metody pro vývoj spolehlivých a bezpečných paralelních a distribuovaných počítačových systémů, GAČR, GD102/09/H042, 2009-2012, Návrh a obvodová realizace zařízení pro automatické generování patentovatelných invencí, GAČR, GA102/07/0850, 2007-2009, Natural computing na nekonvenčních platformách, GAČR, GP103/10/1517, 2010-2013, Výzkum informačních technologií z hlediska bezpečnosti, CEZ MŠMT, MSM0021630528, 2007-2013.

Tato práce vznikla jako školní dílo na Vysokém učení technickém v Brně, Fakultě informačních technologií. Práce je chráněna autorským zákonem a její užití bez udělení oprávnění autorem je nezákonné, s výjimkou zákonem definovaných případů.

<sup>©</sup> Zdeněk Vašíček, 2012.

# Contents

| 1           | $\mathbf{Intr}$ | roduction 1 |                                                                      |    |  |  |

|-------------|-----------------|-------------|----------------------------------------------------------------------|----|--|--|

|             | 1.1             | Goals       | of the Thesis                                                        | 3  |  |  |

| <b>2</b>    | Froi            | m Evo       | lutionary Algorithms to Evolvable Hardware                           | 5  |  |  |

|             | 2.1             | Evolut      | tionary Algorithms                                                   | 5  |  |  |

|             |                 | 2.1.1       | Genetic Algorithms                                                   | 6  |  |  |

|             |                 | 2.1.2       | Genetic Programming                                                  | 7  |  |  |

|             |                 | 2.1.3       | Evolutionary Strategies                                              | 8  |  |  |

|             |                 | 2.1.4       | Evolutionary Programming                                             | 8  |  |  |

|             |                 | 2.1.5       | Cartesian Genetic Programming                                        | 8  |  |  |

|             | 2.2             | Recon       | figurable Devices                                                    | 11 |  |  |

|             |                 | 2.2.1       | Reconfigurability and Its Benefits                                   | 11 |  |  |

|             |                 | 2.2.2       | Digital Reconfigurable Devices                                       | 11 |  |  |

|             |                 | 2.2.3       | Analog Reconfigurable Devices                                        | 14 |  |  |

|             | 2.3             | Evolva      | able Hardware                                                        | 16 |  |  |

|             |                 | 2.3.1       | Basic Principle of EHW                                               | 16 |  |  |

|             |                 | 2.3.2       | Evaluation of Candidate Circuits                                     | 17 |  |  |

|             |                 | 2.3.3       | Evolvable Hardware as Design Tool                                    | 18 |  |  |

| 3           | Evo             | lution      | ary Design of Analog and Digital Circuits                            | 19 |  |  |

|             | 3.1             | Evolut      | tionary Design of Analog Circuits                                    | 20 |  |  |

|             |                 | 3.1.1       | Synthesis of Analog Circuits Using GP                                | 20 |  |  |

|             | 3.2             | Evolut      | tionary Design of Digital Circuits                                   | 22 |  |  |

|             |                 | 3.2.1       | Transistor Level Representation                                      | 22 |  |  |

|             |                 | 3.2.2       | Gate Level Representation                                            | 24 |  |  |

|             |                 | 3.2.3       | Function-level representation                                        | 31 |  |  |

|             | 3.3             | Practi      | cal Aspects of the Evolutionary Design of Digital Circuits using CGP | 35 |  |  |

|             |                 | 3.3.1       | Simulators for Circuit Evolution                                     | 35 |  |  |

|             |                 | 3.3.2       | Performance Improvement Using Parallel Simulation                    | 40 |  |  |

|             |                 | 3.3.3       | Effcient Calculation of Fitness Value                                | 41 |  |  |

|             | 3.4             | Curre       | nt Problems of Evolutionary Design                                   | 42 |  |  |

|             |                 | 3.4.1       | Scalability of Representation                                        | 42 |  |  |

|             |                 | 3.4.2       | Scalability of Fitness Evaluation                                    | 44 |  |  |

| 2.5 Summary |                 |             |                                                                      |    |  |  |

| 4 | Evo | lutionary Synthesis of Linear Transforms                                 | 49  |

|---|-----|--------------------------------------------------------------------------|-----|

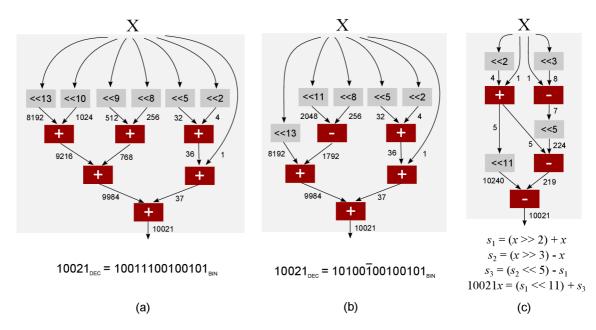

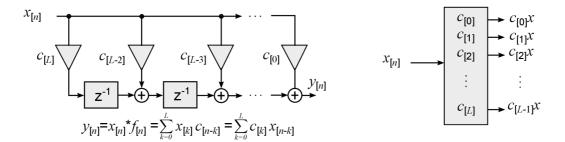

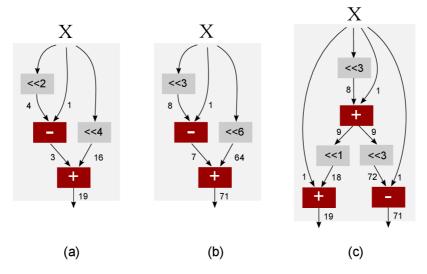

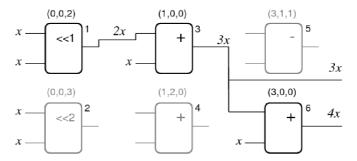

|   | 4.1 | Theoretical Background                                                   | 50  |

|   |     | 4.1.1 Single Constant Multiplication                                     | 50  |

|   |     | 4.1.2 Multiple Constant Multiplication                                   | 53  |

|   | 4.2 | Proposed Method                                                          | 55  |

|   | 4.3 | Results                                                                  | 56  |

|   | 4.4 | Summary                                                                  | 58  |

| 5 | Evo | lutionary Synthesis of Complex Combinational Circuits                    | 59  |

|   | 5.1 | Theoretical Background                                                   | 59  |

|   |     | 5.1.1 Boolean Satisfiability                                             | 60  |

|   |     | 5.1.2 Combinational Equivalence Checking                                 | 60  |

|   |     | 5.1.3 Conventional Logic Synthesis                                       | 66  |

|   | 5.2 | Proposed Method                                                          | 68  |

|   |     | 5.2.1 Formal Verification in Fitness Function                            | 69  |

|   |     | 5.2.2 Time of Candidate Circuit Evaluation                               | 70  |

|   |     | 5.2.3 CGP-Specific Performance Improvement Techniques                    | 72  |

|   | 5.3 | Evaluation of the Proposed Method                                        | 73  |

|   |     | 5.3.1 Population Size                                                    | 74  |

|   |     | 5.3.2 Mutation Rate and Topology of CGP encoding                         | 74  |

|   |     | 5.3.3 Seeding the Initial Population                                     | 75  |

|   |     | 5.3.4 Parity Benchmarks                                                  | 75  |

|   |     | 5.3.5 LGSynth93 Benchmarks                                               | 76  |

|   | 5.4 | Improved Equivalence Checking                                            | 77  |

|   |     | 5.4.1 Time of Candidate Circuit Evaluation                               | 80  |

|   |     | 5.4.2 LGSynth93 Benchmarks                                               | 81  |

|   | 5.5 | Experimental Evaluation and Comparison with Conventional Synthesis       | 81  |

|   |     | 5.5.1 Synthesis of LGSynth93 Benchmarks                                  | 81  |

|   |     | 5.5.2 Synthesis of Conventionally Hard to Synthesize Circuits            | 82  |

|   | 5.6 | Summary                                                                  | 87  |

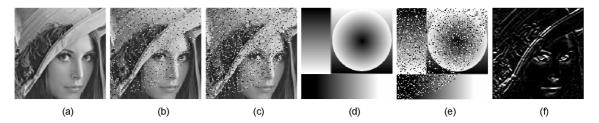

| 6 | Evo | lutionary design of nonlinear image filters                              | 89  |

|   | 6.1 | Theoretical Background                                                   | 90  |

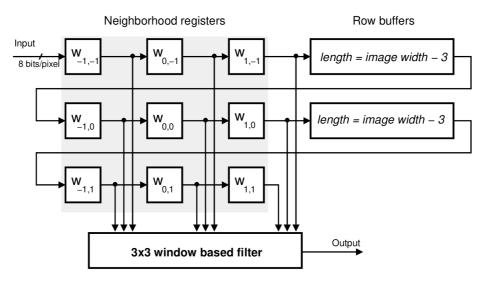

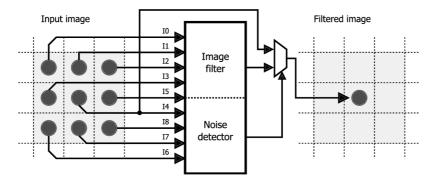

|   |     | 6.1.1 Image Filters and Sliding Window Function                          | 90  |

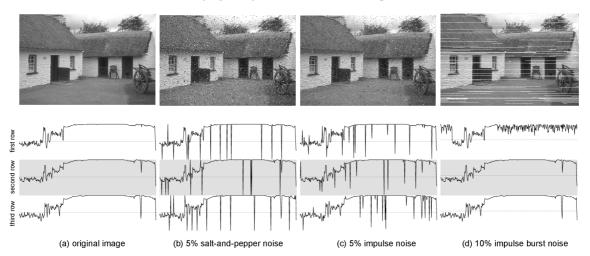

|   |     | 6.1.2 Impulse Noise                                                      | 91  |

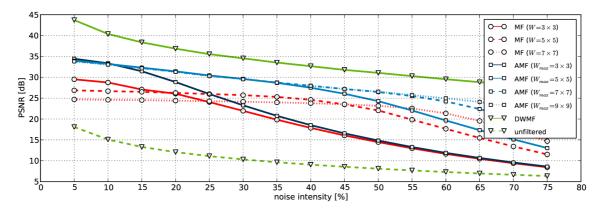

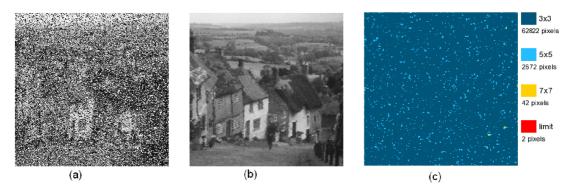

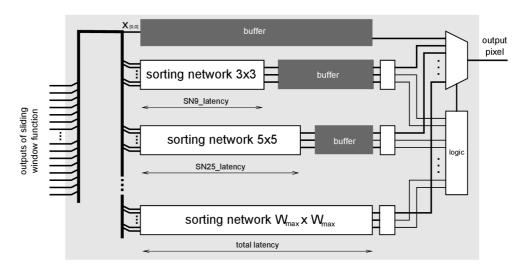

|   |     | 6.1.3 Nonlinear Impulse Noise Filters                                    | 93  |

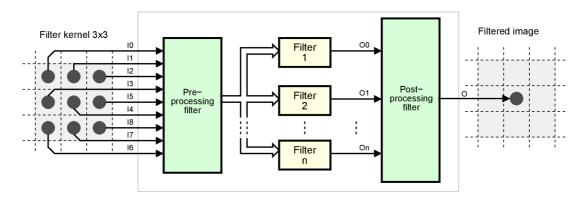

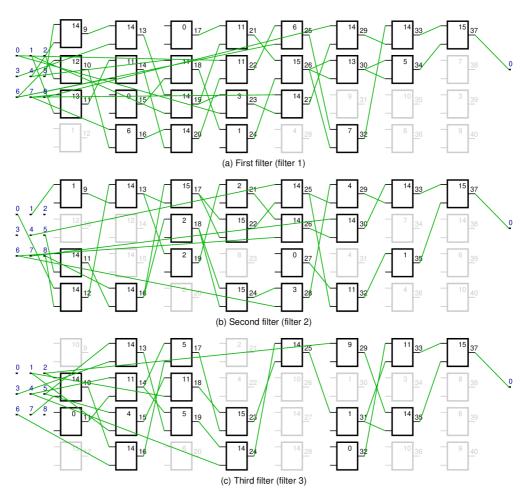

|   | 6.2 | Evolutionary Design of Image Filters using CGP                           | 101 |

|   |     | 6.2.1 Encoding of a Candidate Filter                                     | 102 |

|   |     | 6.2.2 Fitness Function                                                   | 103 |

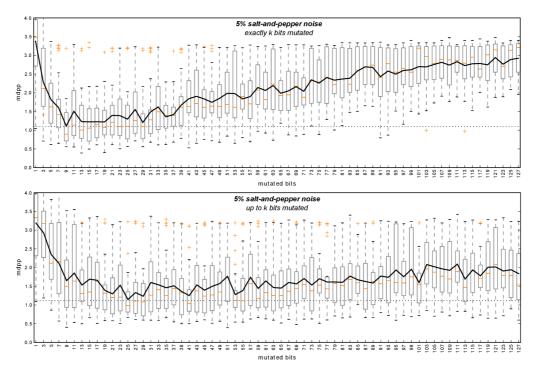

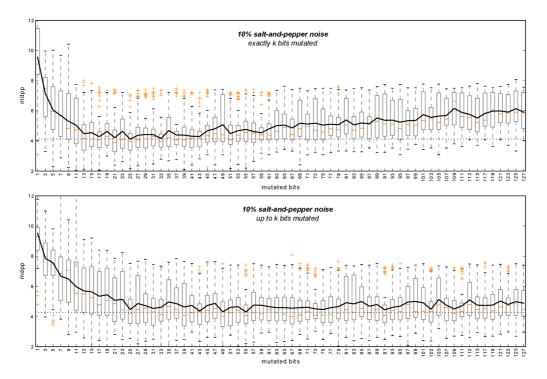

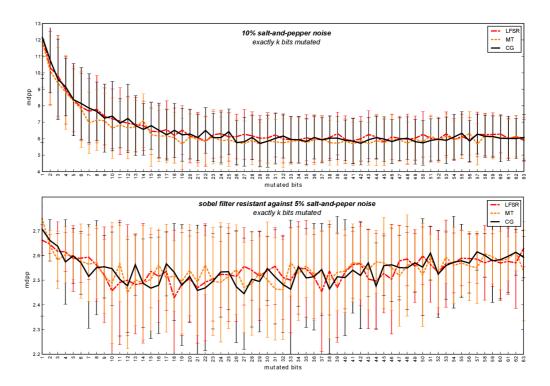

|   | 6.3 | Experimental Results                                                     | 104 |

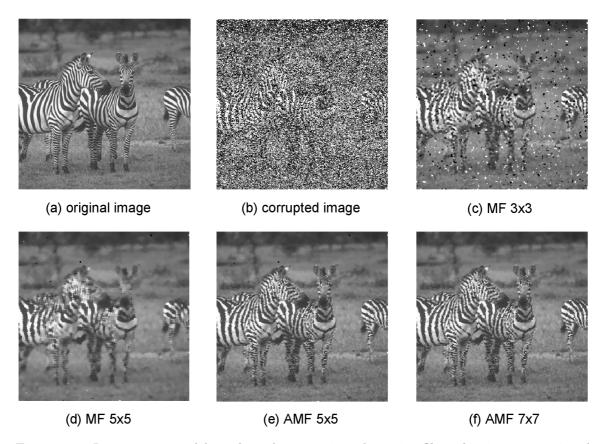

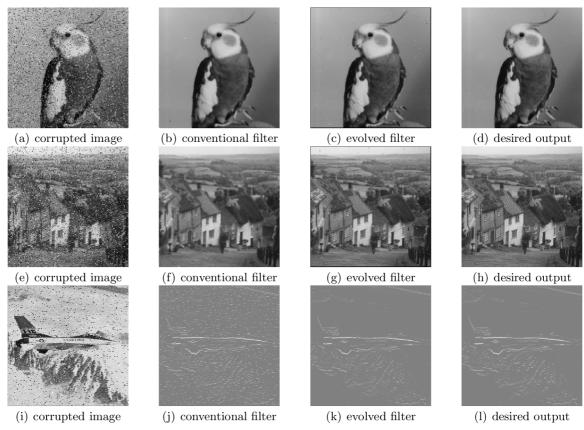

|   |     | 6.3.1 Salt-and-pepper Noise Filters and Noise-Resistant Edge Detectors . | 104 |

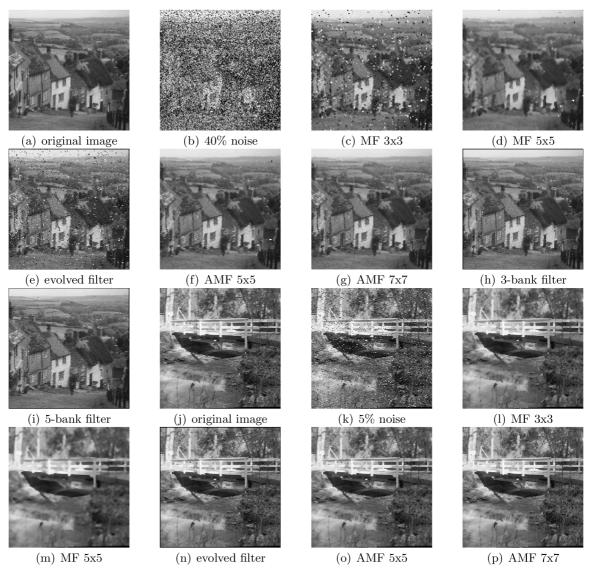

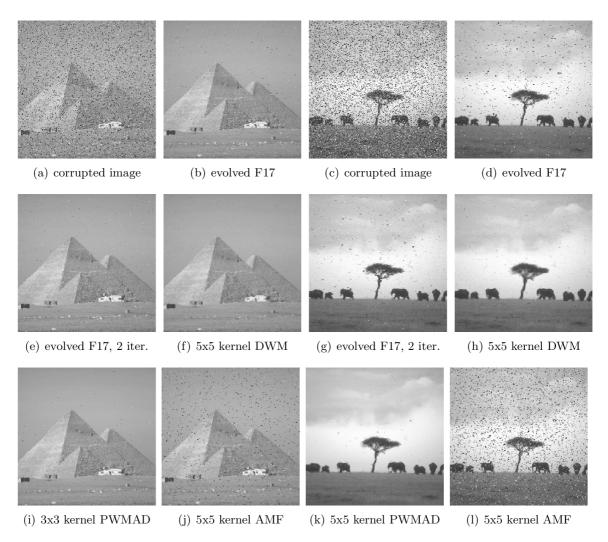

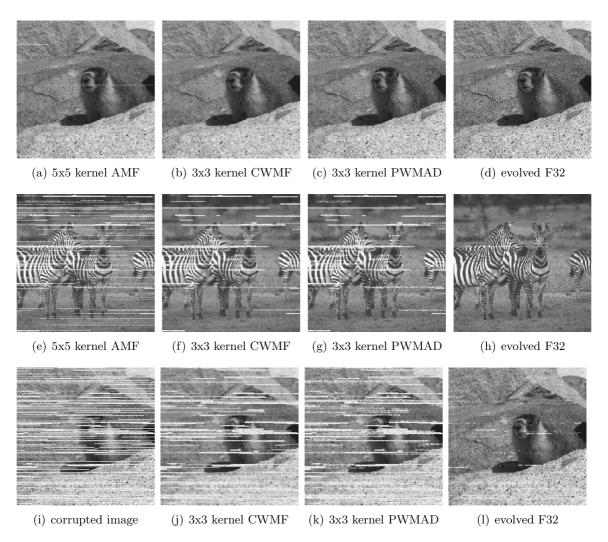

|   |     | 6.3.2 Evolutionary Design of Robust Salt-and-pepper Noise Filter         | 107 |

|   |     | 6.3.3 Evolutionary Design of Switching Filters                           | 112 |

|   | 6.4 | Summary                                                                  | 121 |

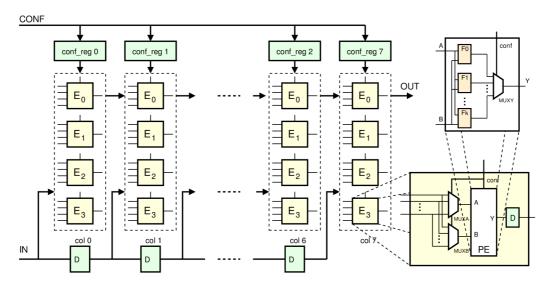

| 7 | $\mathbf{Har}$ | $\mathbf{dware}$ | Accelerator of Cartesian Genetic Programming | 123 |

|---|----------------|------------------|----------------------------------------------|-----|

|   | 7.1            | Target           | FPGA Platform                                | 124 |

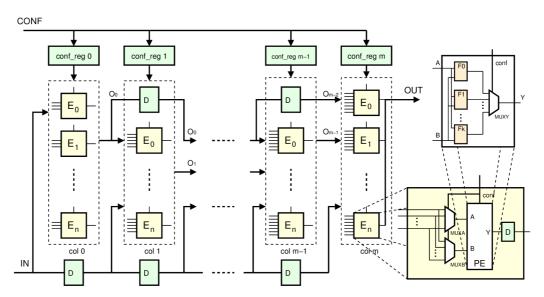

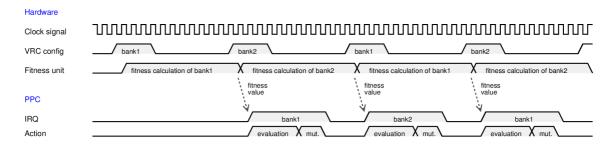

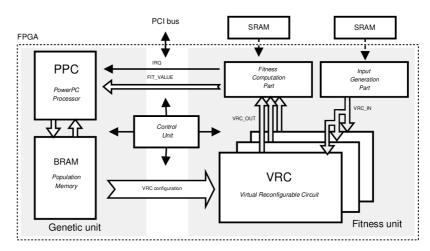

|   | 7.2            | CGP              | Accelerator with a Single Fitness Unit       | 125 |

|   |                | 7.2.1            | Architecture Overview                        | 126 |

|   |                | 7.2.2            | Genetic Unit                                 | 127 |

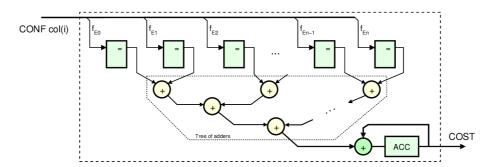

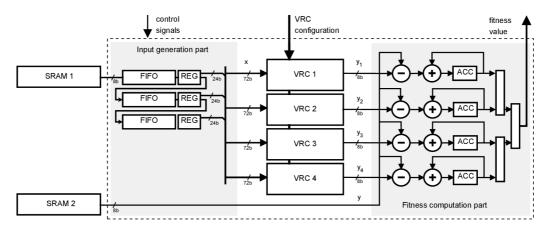

|   |                | 7.2.3            | Fitness Unit                                 | 128 |

|   |                | 7.2.4            | VRC for Symbolic Regression Problems         | 128 |

|   |                | 7.2.5            | VRC for Logic Expressions                    | 129 |

|   | 7.3            | Exper            | imental Evaluation                           | 130 |

|   |                | 7.3.1            | Theoretical Performance                      | 130 |

|   |                | 7.3.2            | Evolution of Image Filters                   | 130 |

|   |                | 7.3.3            | Evolution of Digital Circuits                | 135 |

|   | 7.4            | CGP.             | Accelerator with Multiple Fitness Units      | 137 |

|   |                | 7.4.1            | Fitness Unit                                 | 138 |

|   |                | 7.4.2            | Genetic Unit                                 | 139 |

|   | 7.5            | Exper            | imental Evaluation                           | 140 |

|   |                | 7.5.1            | Theoretical Performance                      | 140 |

|   |                | 7.5.2            | Results of Synthesis                         | 141 |

|   |                | 7.5.3            | Evolution of image filters                   | 142 |

|   | 7.6            | Summ             | nary                                         | 143 |

| 8 | Cor            | clusio           | ns                                           | 145 |

# Chapter 1

# Introduction

The electronic manufacturing industry, especially electronic circuit production, is an area that has gone through a substantial development in the recent fifty years. In the second half of the 20th century, innovations in electronic computer systems made the personal computer a reality. Each new generation of computers was cheaper to purchase, more powerful and easier to operate. Thus the computers shortly became universal computing machines that spread not only among the scientific community but also among the common users. The progress achieved by the 21st century causes the electronic products had transformed the way that people live, work, and communicate. A common cellular phone has been superseded with the devices having the performance comparable with the personal computers and the personal computers are gradually replaced with very popular portable devices.

Comparing the current requirements to the requirements formulated a few years ago, significantly more complex circuits and behaviors are demanded today. This demand is caused by the relentless improvements of the available technologies. While the current advance is driven mainly by the necessity to minimize the overall power consumption of the produced systems, in the 1990s the goal was a relative simple – doubling of the performance of the computer systems and keeping up with the Moore's law. The current situation is much complicated and requires discovering and applying new approaches as the power consumption requirements are generally in contrast with the performance requirements.

One of the main bottlenecks that has been identified by scientific community is a low efficiency of circuit design [54]. Traditional circuit design methodologies rely on rules and design techniques that have been developed over many decades. However, the need for human input to the increasingly complex design process means that the circuit design has to be simplified by imposing greater and greater abstraction to the design space. An example of this approach is the introduction of the hardware description languages. This abstraction allows designers to significantly reduce the time needed to design and produce the intended system. On the other hand, it also results in waste of potential circuit behavior since the conventional design methodologies do not offer too many ways to benefit from the physical dynamics available from the silicon medium [175].

One of crucial parts of the design process is the efficient logic synthesis and optimization. As a part of computer theory, the logic synthesis and optimization have been developed for more than 50 years. Despite the fact that the logic synthesis and optimization are

considered to be very difficult problems, many companies provide commercial tools that allow processing even the systems of the contemporary complexity in a reasonable time. However, the recent work in the area of conventional synthesis has shown that the available synthesis algorithms produce solutions that are far from optimum for many circuit classes [35].

In the beginning of nineties, a new field applying evolutionary techniques to hardware design and synthesis has been established. This field is referred to as Evolvable Hardware [65]. The evolvable hardware draws inspiration from three main fields – biology, computer science and electronic engineering. The aim is to provide (1) electronic systems exhibiting a degree of self-adaptive and self-repair behavior and/or (2) a robust design approach that could even replace a human designer in some cases. Typical application domains include design of digital circuits, analog circuits, antennas, optical systems and MEMS [107, 78, 83].

In the context of the circuit design, the evolvable hardware is very attractive approach as it provides another option to the traditional design methodology – to use evolution to design circuits for us. Moreover, the key strength of the evolvable hardware approach is that it can be applied for designing of the circuits that cannot be fully specified a priori, but where the desired behavior is known. In fact, the search-based approaches seem to be the only viable option in this case. Another often emphasized advantage of this approach is that the circuits can be adopted for a particular environment.

During the last two decades, the evolvable hardware community has demonstrated that very efficient (and sometimes also patentable) implementations of physical designs can be obtained using evolutionary computation. For example, John Koza, the pioneer of the field, dealing primarily with the evolutionary design of analog circuits, has reported tens of human-competitive results in various areas of science and technology. The results were obtained automatically using evolutionary techniques, in particular using genetic programming [102] that has mainly been adopted for analog circuit design [121, 38]. In case of digital logic synthesis, the evolutionary synthesis has also led to several innovative designs [127, 9, 164]; however the obtained results belong to the category of relatively small circuits.

Although the evolutionary design has been shown to be a promising and general-purpose design method, there exist several problems that make the evolutionary approach problematic in some applications [69]. The scalability problem has been identified as one of the most difficult problems the researchers are faced with in the evolvable hardware field. The scalability problem means such situation in which the evolutionary algorithm is able to provide a solution to a small problem instance; however, only unsatisfactory or even none solutions can be obtained for larger problem instances in a reasonable time. Another problem related to this issue is enormous computational power which evolutionary algorithms usually need for obtaining innovative results for some applications.

The scalability problem can primarily be seen from two perspectives: scalability of representation and scalability of fitness evaluation. From the viewpoint of the scalability of representation, the problem is that long chromosomes (a set of genes which defines a candidate solution) which are usually required to represent complex solutions imply large search spaces that are typically difficult to search. Another issue is the scalability of fitness evaluation, i.e. the problem that complex candidate solutions might require a lot of time to be evaluated. For example, in the case of the evolutionary design of combinational circuits,

the evaluation time of a candidate circuit grows exponentially with the increasing number of inputs (assuming that  $2^n$  test vectors are generated for n-input circuit). This represents the main weakness of the evolutionary approach. It also causes that real-world applications of evolutionary circuit design are not able to compete with conventional design.

#### 1.1 Goals of the Thesis

It will be argued in this thesis that the fitness scalability issue can be eliminated by seeking for new sophisticated evaluation methods. We will solely deal with evolvable hardware as the method for automated design, i.e. the scenario in which the evolutionary algorithm is used only in the design phase of a product. The thesis postulates two main objectives.

The **first goal** is to propose problem-specific methods that will allow designers to reduce the scalability problem in the area of digital system design. As the scalability problem represents a general problem, we will consider only a very narrow but important subarea – the scalability of evaluation of a candidate digital circuit.

The **second goal** is to evaluate the impact of the proposed methods and show that by means of the proposed methods it is possible to evolve innovative solutions in various problem domains. In the context of evolutionary circuit design, we mean by the term innovative that a solution exhibits better features with respect to existing designs of the same category.

## Thesis Organization

The thesis is organized as follows. The first two chapters contain theoretical background that outlines the basic concepts and ideas utilized in the following chapters. In addition to that, this introductory part also clarifies the motivation of this work. The next three chapters contain three case studies that demonstrate three approaches to elimination of the scalability problem of evolutionary circuit design. Finally, an evolutionary platform designed to accelerate the evolutionary design of digital circuits is introduced. To be more specific:

Chapter 2 provides the necessary background of evolvable hardware which represents the essential concept tightly connected with this thesis. This overview covers the principles and basic concepts of evolutionary algorithms. The chapter is divided into three sections. The first section contains a description of relevant evolutionary techniques, especially Cartesian Genetic Programming that have been utilized in the experiments. The next section summarizes reconfigurable devices that have been used in the evolvable hardware field. The last section comprises of a literature survey of evolvable hardware which represents the research area in which the presented thesis belongs to.

Chapter 3 is devoted to the evolutionary design of digital and analog circuits. The first two sections contain a summary of the electronic circuits designed at various levels of abstraction that have been published in literature. The goal of this chapter is to make an insight to the complexity of the design problems that have been solved so far. The next section discusses the practical aspects of the evolutionary design of digital circuits

by means of Cartesian Genetic Programming. In the third section, the shortcomings and bottlenecks of the evolutionary design are discussed. This part deals with the issue of scalability of evolutionary design and the approaches that have been proposed to mitigate or even remove various scalability problems.

The first case study, which is presented in Chapter 4, deals with the evolutionary design of linear transforms. We have identified a class of problems for which a candidate solution can be perfectly evaluated in a very short time. This chapter is divided into four sections. The first section covers the theoretical background related to the linear transforms in general, and multiple constant multiplier blocks in particular. The next three sections contain the description of the proposed method and experimental evaluation of this method.

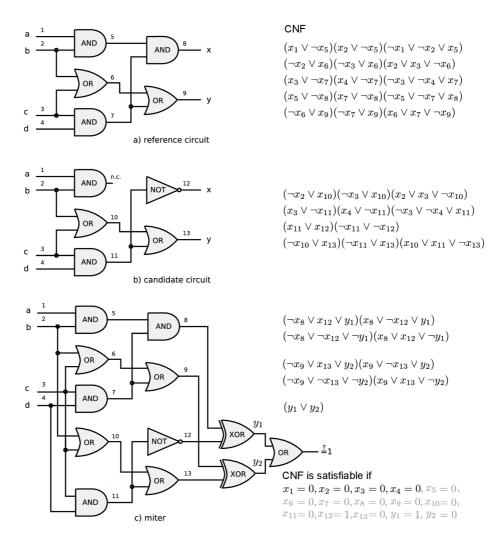

In Chapter 5, the second case study related to the evolutionary synthesis of complex digital circuits is introduced. The goal of this chapter is to present a new approach to the fitness function implementation which is based on a formal verification algorithm. The proposed method significantly eliminates the scalability problem of fitness function evaluation which has been known from the very beginning of digital evolvable hardware. This part is divided into five sections. The first section describes the problem of combinational equivalence checking and the process of conventional logic synthesis. The proposed method followed by its extensive experimental evaluation is described in the second and third section respectively. The fourth and fifth section describe the improved version of the proposed approach and its evaluation using a set of real-world benchmark circuits.

The case study devoted to the evolutionary design of nonlinear image filters is presented in Chapter 6. This chapter consists of three sections. The first section defines the problem to be solved and introduces the necessary theoretical background connected with the filtration of impulse noise. The second section discusses the evolutionary design of image filters using Cartesian Genetic Programming. Finally, experimental results are summarized in the last section.

A common feature of Chapters 4–6 is that firstly the discussed problem is introduced. Afterwards, the proposed evolutionary design approach followed by experimental evaluation is given. Finally, the obtained results are presented and summarized. The introduction includes not only the description of the problem, but also an overview of the best-known conventional methods that are usually utilized to solve a given problem.

Chapter 7 describes a new hardware accelerator for Cartesian Genetic Programming implemented using FPGA. Two types of application-specific accelerators are in fact proposed. The first one is devoted for symbolic regression problems over the fixed point representation. The second one is designed for evolution of logic circuits.

Chapter 8 summarizes the results obtained in this thesis and outlines directions for the future research.

# Chapter 2

# From Evolutionary Algorithms to Evolvable Hardware

The purpose of this chapter is briefly introduce the key concepts behind the evolutionary algorithms, reconfigurable devices and evolvable hardware.

## 2.1 Evolutionary Algorithms

Several decades ago, researchers started to explore how some ideas taken from nature could be employed for solving hard computing problems. Evolutionary algorithms inspired by biological evolution represent one of the most successful examples.

The evolutionary algorithms (EAs) [11] are stochastic search algorithms inspired by Darwin's theory of evolution. The common feature of evolutionary algorithms is that they utilize mechanisms that are inspired by principles of biological evolution, namely reproduction, mutation, recombination and selection. In contrast with common search algorithms, such as random search or hill climbing, the EAs are population-based algorithms. It means that they work with more candidate solutions (i.e. individuals) in the same time. By a candidate solution we mean a point in the search space, the space that contains all possible considered solutions to a given problem.

Every new population is formed using genetic operators such crossover and mutation and through a selection pressure. The selection pressure together with the *fitness function*, sometime referred to as objective function, is responsible for guiding the evolution towards better areas of the search space. The guidance is received from the fitness function that assigns so called fitness value to each candidate solution. The fitness value indicates how well a candidate solution fulfills the problem objective; in other words, it indicates how a particular candidate solution meets the specification. A better fitness value implies a greater chance that a candidate solution will remain for a longer while and produce offspring, which inherit parental genetic information. A well-designed evolutionary algorithm should converge to a population containing desired solutions.

Each member of the population (i.e. a candidate solution) consists of a string of parameters, so called genes. This string is usually referred to as an individual or chromosome. A particular value of a gene in chromosome is called allele. Thus, the alleles are the small-

est information units in a chromosome. In nature, alleles exist pair wise, whereas in the evolutionary algorithms, an allele is usually represented by only one symbol. Because the objects in the search space can generally represent arbitrary structure (a vector of real values, digital circuit, antenna, and so on), we distinguish between a search space (or genotype space) and representation space (phenotype space). While the fitness function is applied to evaluate phenotypes, the genetic operators manipulate with genotypes. A small change in the genotype should produce a small change in the phenotype otherwise the evolutionary algorithm is not efficient [15].

The evolutionary algorithms are traditionally divided into four distinct branches: genetic algorithm [62], genetic programming [100], evolutionary strategies [156] and evolutionary programming [55]. The algorithms mainly differ in the mechanism of the candidate solutions encoding, implementation of the evolutionary operators applied to the candidate solutions and finally, utilized search strategy that guides the EA through the search space.

#### 2.1.1 Genetic Algorithms

Genetic algorithm (GA) was introduced by John Holland in 1973 and made famous by David Goldberg [62, 82].

Researchers have proposed many different variants of genetic algorithms in the literature. For the illustration, we will use the traditional simple genetic algorithm (the simplest form of GA) defined by Goldberg. This canonical algorithm uses two genetic operators, crossover as the main operator and mutation which serves only as background noise. The structure of a canonical genetic algorithm, as it has been described by David Goldberg in [62], is captured in the following pseudo code.

```

randomly create initial population P(t)

while (termination condition is false)

evaluate each individual in P(t)

if acceptable solution found then

break

reproduce individuals according to their fitnesses into mating pool

(higher fitness implies more copies of individual in mating pool)

t = t + 1

while P(t) is not filled with new offspring do

randomly take two individuals from mating pool

use probabilistic random crossover to generate two offspring

apply probabilistic random mutation to the offspring

place offspring into population P(t)

```

Algorithm 2.1: Canonical Genetic Algorithm

The simple genetic algorithm uses a population of individuals having the constant size. The individuals are encoded using a vector (or string) of fixed size. GA traditionally operates with binary, integer, real-valued or character-based string. The genetic operators such

as one-point, uniform or n-point crossover are directly applied to the genotypes. In many implementations, crossover produces two new offspring from two parents by exchanging substrings. The mutation operator slightly changes the genotype of an individual.

The basic functionality of a traditional simple GA is relatively simple. After randomly creating and evaluating an initial population, the algorithm iteratively creates new generations. New generations are created by recombining the selected highly fit individuals using a crossover operator and applying mutation to the obtained offspring. Crossover is often used about 70% of the time to generate offspring, for the remaining 30% offspring are simply clones of their parents. Mutations occur rarely and usually modify value of a randomly selected gene of the individual. The selection is typically implemented as a probabilistic operator that is based solely on the fitness value. The genetic algorithm terminates when a sufficient solution is found or a given time limit (or a given number of generations) is exhausted.

For practical problems, the simple genetic algorithm is often considered as a basis for many enhancements, including: heuristic generation of the initial population, multi-point or more complicated crossover, elitism preserving the best individual for the next generation, more realistic selection, etc.

#### 2.1.2 Genetic Programming

Genetic Programming (GP) was introduced by John Koza in late eighties as an extension to genetic algorithms in order to enrich the chromosome representation [100, 101, 105, 107]. Instead of fixed-length strings, GP evolves pieces of code written over a specified alphabet consisting of a set of functions and a set of terminals. The chromosome encoding can be directly executed by the system or compiled (interpreted) to produce a machine executable code. Genetic programming allows automatic programming and program induction (i.e. automatically developing of computer programs). Unlike genetic algorithms, genetic programming does not distinguish between phenotype and genotype. As genetic programming is able to effectively evolve symbolic expressions, the problem of symbolic regression became the most popular application of GP.

The evolved programs are usually represented either as tree structures or in a linear form using a list of machine-language instructions. Similarly to the GA, crossover is considered as a major genetic operator. A typical crossover interchanges randomly chosen subtrees of parents' trees without the disruption of the syntax. A typical mutation, another genetic operator, selects a random subtree and replaces it with a randomly generated one. Selection is typically implemented as a probabilistic operator, using the relative fitness, which determines the selection probability of an individual.

In order to improve the efficiency in GP, John Koza introduced the concept of automatically defined functions (ADFs) [101]. Automatically defined functions enable genetic programming to define useful and reusable subroutines (subtrees) dynamically during evolution. According to the obtained results, genetic programming with ADFs produces solutions that are simpler and smaller than the solutions obtained without automatically defined functions.

The GP representation has also its own pitfalls. An evolved program may contain

segments which do not alter the result of the program execution when they are removed from it. A typical trivial example is the expression  $x = x \cdot 1 + 0$  where the addition as well as the multiplication represent redundant operations that can be omitted. The redundant segments are referred to as introns. Another well-known issue of GP is that the program size can grow uncontrollably until it reaches the tree-depth maximum, while the fitness remains unchanged. This effect is called a bloat. These pitfalls and their relations are discussed, for example, in [8, 12].

#### 2.1.3 Evolutionary Strategies

Evolutionary strategies proposed by Bienert, Rechenberg and Schwefel have been developed for optimization purposes in industrial applications [156, 11]. Similarly to the genetic programming, evolutionary strategies do not distinguish between a genotype and phenotype. Each individual is represented as a real-valued vector. Evolution strategies use primarily mutation and selection. Unlike the previous approaches, the mutation operator, which mutates each vector element, is considered as a major genetic operator. Mutation aggregates a normal-distributed random variable and a preselected standard deviation value which are applied on every gene of a candidate vector.

The simplest evolutionary strategy operates on a population of size of two consisting of the current solution (parent) and the result of its mutation (offspring). The selection strategy is strictly deterministic. Only if the offspring's fitness is at least as good as the parent's one, it becomes the parent of the next generation. Otherwise the offspring is disregarded. This basic strategy is known as a (1 + 1)-ES. More generally,  $\lambda$  offspring can be generated. The strategy in which the offspring compete with  $\mu$  parents is called  $(\mu + \lambda)$ -ES. Another selection scenario  $(\mu, \lambda)$ -ES picks the best  $\mu$  individuals from the both child and parent populations. In the simplified (1,1)-ES variant, the offspring becomes the parent of the next generation while the current parent is always disregarded.

#### 2.1.4 Evolutionary Programming

Evolutionary programming was introduced by Lawrence Fogel in sixties in order to use simulated evolution as a learning process [56, 55]. He has used the evolutionary programming for the design of finite state machines working as predictors. Evolutionary programming exhibits a number of similarities with evolutionary strategies and is becoming harder to distinguish from that paradigm. Important features of advanced evolutionary programming systems typically include a problem-specific representation, self-adaptation and tournament selection. Mutation operator is considered as the only genetic operator, crossover or similar recombination operators are not usually used at all. The search space and the representation space are not distinguished explicitly.

#### 2.1.5 Cartesian Genetic Programming

Cartesian genetic programming (CGP), introduced by Julian Miller and Peter Thomson in 2000, is a variant of genetic programming where the genotype is represented as a list of integers that are mapped to directed oriented graphs rather than trees [131]. The motivation

for this representation came from the previous analysis covering the effectiveness of this approach in learning Boolean functions where the CGP has been proved to be considerably more efficient than any other variant of GP.

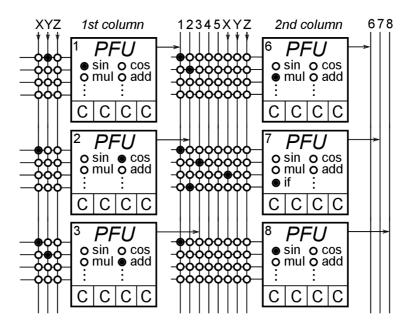

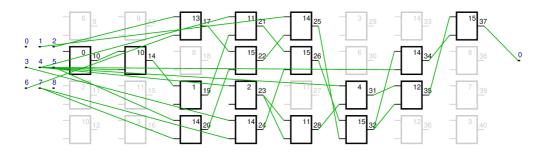

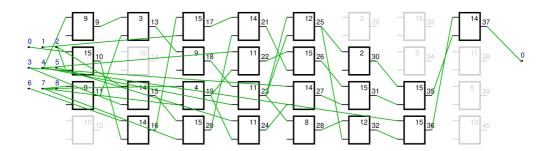

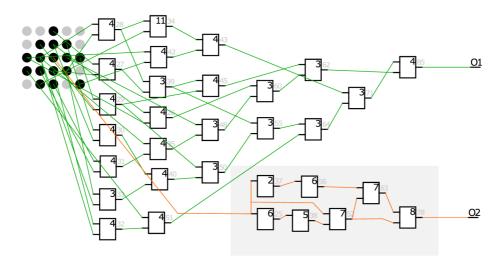

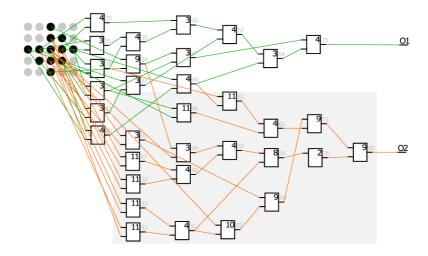

Cartesian genetic programming encodes a candidate solution (typically a circuit or a program) using an array consisting of  $n_c \times n_r$  programmable nodes. The  $n_c$  parameter determines the number of columns whereas  $n_r$  determines the number of rows. Each programmable node has the fixed number of inputs,  $n_{ei}$ , and outputs  $n_{eo}$ ; in most cases  $n_{ei} = 2$  and  $n_{eo} = 1$ . The main feature of CGP is that all the parameters including the number of programmable nodes, node inputs and outputs and program inputs,  $n_i$ , and program outputs,  $n_o$ , are fixed. Each node input can be connected either to the output of a node placed in the previous l columns or to one of the program inputs. The parameter l (referred to as l-back parameter) defines the level of connectivity and thus reduces or extends the search space. For example, if l=1 only neighboring columns may be connected; if  $n_r=1$  and  $n_c=l$ , full connectivity is enabled. Because of the complicated evaluation, feedback is not allowed in the standard version of CGP. Each node can be programmed to perform one of  $n_{ei}$ -input functions defined in the set  $\Gamma$ . Let  $n_f = |\Gamma|$ . Thus, every individual can be encoded using  $n_c \times n_r \times (n_{ei} + n_{eo}) + n_o$  integers.

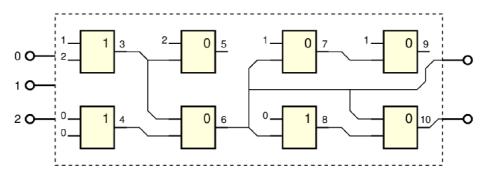

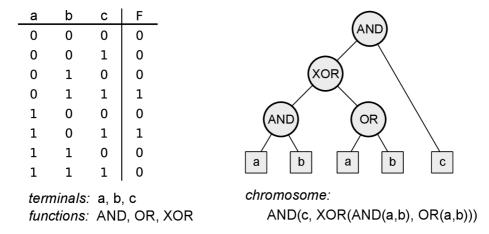

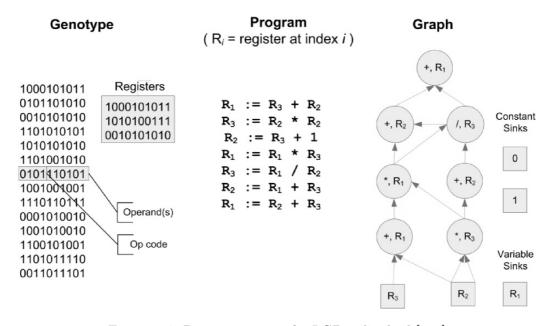

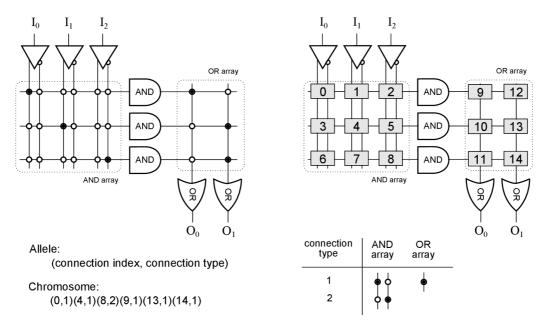

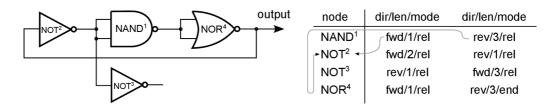

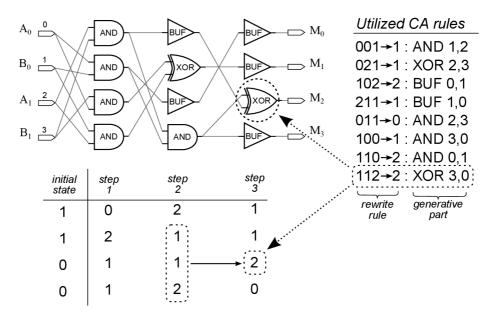

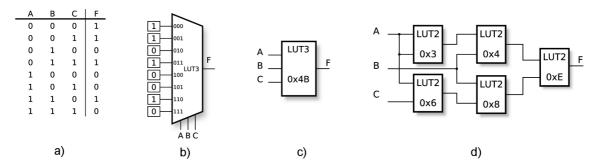

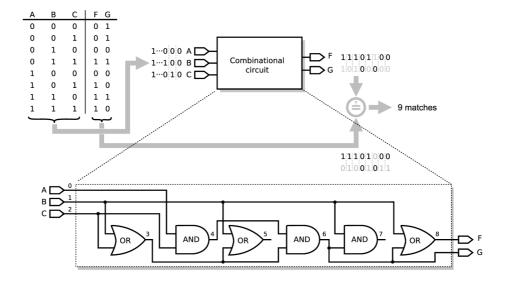

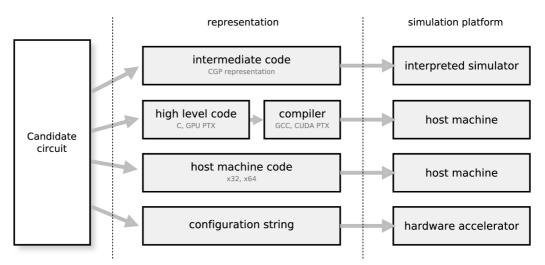

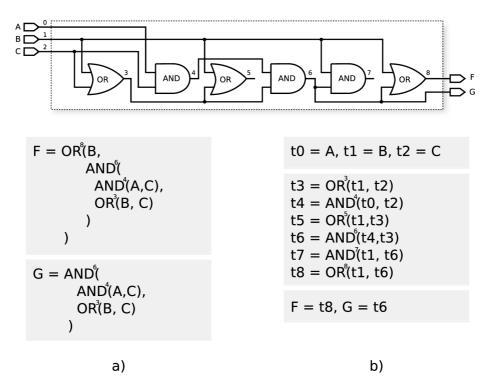

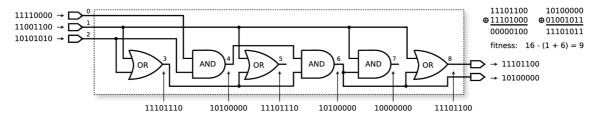

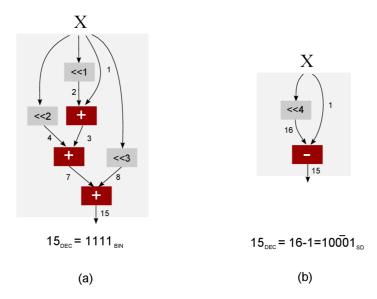

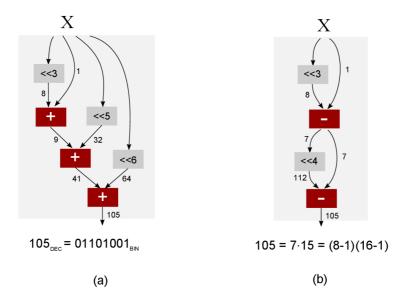

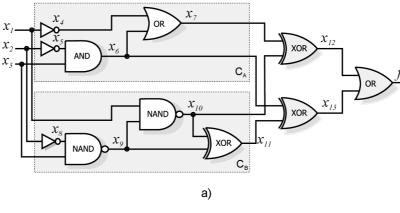

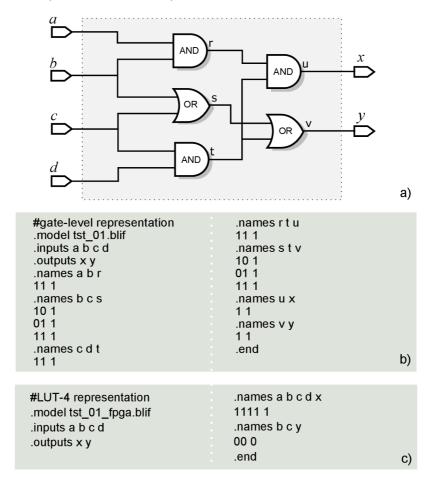

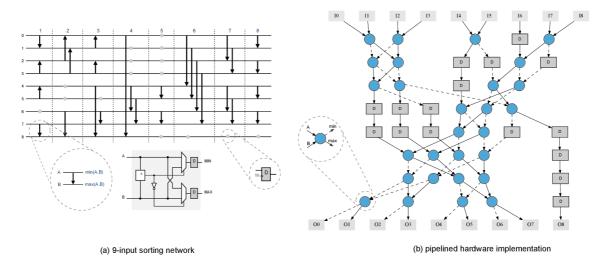

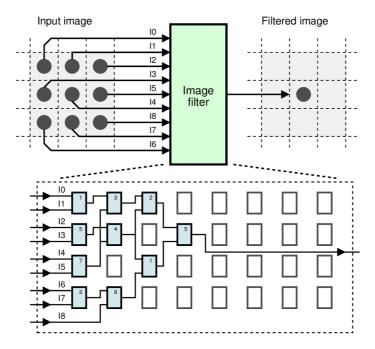

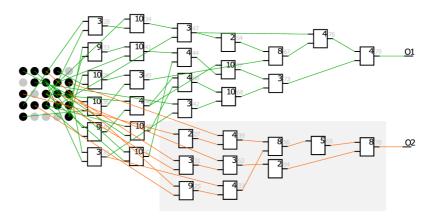

Figure 2.2: Example of a candidate circuit encoded using CGP with the following parameters:  $n_c = 4$ ,  $n_r = 2$ ,  $n_i = 3$ ,  $n_o = 2$ , l = 2,  $n_{ei} = 2$ ,  $n_{eo} = 1$ ,  $\Gamma = \{\text{AND (0), OR(1), XOR (3)}\}$ . Chromosome: 1, 2, 1, 0, 0, 1, 2, 3, 0, 3, 4, 0, 1, 6, 0, 0, 6, 1, 1,3, 0, 6, 8, 0, 6, 10. Functions of elements are typed in bold. The first 24 integers encode the interconnection of the CGP elements and function of each element. The last two integers indicate the output of the circuit. Elements 5, 7 and 9 are not utilized.

Figure 2.2 shows a digital circuit encoded using CGP representation. The figure also demonstrates the main feature of CGP encoding – while the genotype (i.e. chromosome) is of fixed length, the phenotype is of variable length depending on the number of unexpressed genes. In this example, three nodes do not contribute to the phenotype. The utilized representation also significantly reduces the bloat which is inevitable in GP [126]. This fact has been confirmed by Miller in [129] who claimed that it cannot occur in the genotype just because it is bounded.

Due to the presence of redundancy, there are many genotypes that are mapped to identical phenotypes. The simplest form of redundancy is caused by the presence of genes or nodes that are inactive. These genes influence neither the phenotype nor the fitness value. This kind of redundancy is very high at the beginning of the evolution as many nodes are

not connected in the early populations. With the increasing number of generations, the node redundancy gradually reduces to a level that is determined by the average number of nodes required to obtain a satisfactory solution and the maximum allowed number of nodes [131].

The phenomenon indicating the presence of genotypes with the same fitness is often referred to as neutrality. The role of neutrality has been investigated in detail in several papers [198, 129, 34]. For example, it was discovered that the most evolvable representations occur when the chromosome is extremely large and contains over ninety percent of inactive genes [129]. On contrary, it has been also shown that for some specific problems, the neutrality based search is not the best approach [34].

In CGP, the search is performed using a mutation-based evolutionary strategy  $(1 + \lambda)$ -ES that does not utilize crossover as it has been discussed in the previous chapters. The influence of the crossover operator has been intensively studied in literature, however, it has been confirmed that crossover does not improve the search [128, 183]. CGP operates with the population of  $1 + \lambda$  individuals, where  $\lambda$  is typically from 1 to 15. In case of the evolutionary design, the initial population is usually generated randomly whereas in case of the evolutionary optimization the initial population can be constructed by means of mapping of a known conventional solution to the CGP representation.

The search strategy works as follows. The initial population has to be evaluated using a fitness function and the fittest individual becomes the new parent. Then, every new population consists of the best individual of the previous population and its  $\lambda$  mutated offspring. The offspring are created by a point mutation operator which modifies m randomly selected genes of the parental individual where m is a user-defined value. The mutation operator usually modifies up to 5% of genes of the chromosome. The implementation of the mutation operator has to ensure that the modifications are legal and lead to a valid phenotype. The moment the population is created, the fitness value of each offspring is calculated. The fittest individual in the population is selected and forms the new parent. In case when two or more individuals have received the same fitness score, the individual which has not served as the parent in the previous population has to be selected as the new parent. This strategy is important because it ensures the diversity of population and allows so called neutral search [129]. The evolution is terminated when the maximum number of generations is exhausted.

The CGP became the routinely used approach in the area of evolutionary-based digital circuit synthesis and optimization. The main advantage of CGP is that it generates very compact solutions, i.e. it can effectively reduce the total number of gates in the case of circuit evolution [127]. Even if the CGP was originally defined for gate-level evolution, it can easily be extended for function-level evolution [157]. CGP has been successfully utilized in many applications [125, 91, 131, 127, 182, 157, 4, 57, 186, 223]. In addition to the standard CGP, several extensions have been proposed in recent years; for example, self-modifying CGP [74], modular CGP [188, 92], developmental CGP [164] or multi-chromosome CGP [204]. Some authors have also utilized CGP with a relative encoding of the solution instead of the absolute encoding introduced by Miller [70].

## 2.2 Reconfigurable Devices

In recent years, we could observe a boom in the area of reconfigurable devices and reconfigurable computing [181]. In comparison to fixed architectures, the structure and parameters of reconfigurable chips can be modified by writing configuration data to the configuration memory. The reconfigurable devices usually consist of configurable blocks whose functions and interconnections are controlled by the configuration bitstream. While the first programmable devices such as Programmable Logic Arrays (PLAs) used hundreds of bits to store the configuration and relatively simple reconfigurable structure, recent devices such as Field Programmable Gate Arrays (FPGAs) require tens of megabytes to store their configuration bitstream. Due to its potential to accelerate a wide variety of applications, reconfigurable computing has become a subject of intensive research. Its key feature is the ability to perform computations in hardware to increase performance, while retaining much of the flexibility of a software solution.

The possibility of reconfiguration is typical for digital architectures. However, reconfigurable devices are now available in the areas of analog circuits, antennas, mirrors, molecular electronics and others. This short survey introduces the concept and basic principles behind the FPGAs as well as other reconfigurable devices that have been used in the evolvable hardware field.

#### 2.2.1 Reconfigurability and Its Benefits

There are several reasons for using reconfigurable hardware. The reconfiguration can extend the lifespan of a system due to the possibility to update the firmware. For example, when a new driver or peripheral device is introduced to a system, existing hardware could have a problem to communicate with it. However, if the system is implemented in a reconfigurable chip, the hardware can be updated by simple reprogramming the configuration memory. In this case, the reconfiguration is performed occasionally and only when the application is suspended.

Another common scenario is to use a reconfigurable chip in order to increase the functional density. The goal is to perform a complex task on a small chip and thus reduce the power consumption, size or weight of the application, even reduce the cost. The application has to be divided into modules whose configurations alternate on the chip. The reconfiguration is performed dynamically at runtime.

The reconfigurability also gives the chance to create an adaptive hardware. In this case, the goal is to dynamically create electronic circuits that are optimized for a given task, time and location of the chip.

And finally, the typical reason why reconfigurable devices are used is shortening the design time. Creating a configuration for a reconfigurable device usually takes much less time than building a new application-specific chip.

#### 2.2.2 Digital Reconfigurable Devices

In order to control the routing among the configurable blocks, a kind of configurable switch matrix is used. To establish the routing on a reconfigurable chip, a passgate structure is typically employed. Modern digital reconfigurable devices such as Xilinx FPGAs contain a rich routing fabric consisting of millions of routing choice points. The configuration bits directly control the configurable switches, selection signals of multiplexers, contents of lookup tables (LUTs) and some bits used as control signals for computational unit. A single chip can implement many different functions depending on its configuration. The main disadvantage of this approach is that the circuitry established in order to allow the configurability occupies a considerable area on the chip and make the whole system slower in comparison with application specific integrated circuits. Since the FPGAs represent the mainstream in the area of digital reconfigurable devices, we will restrict ourselves to these devices only.

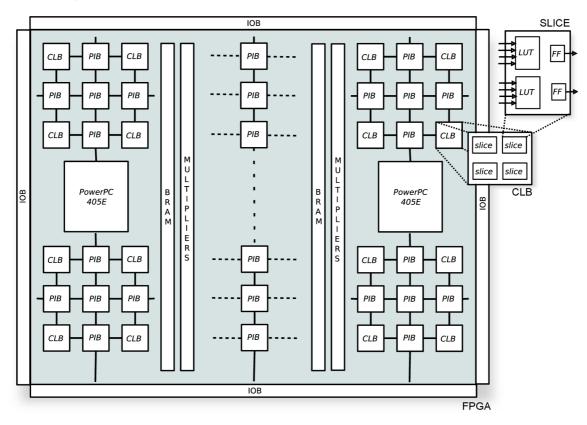

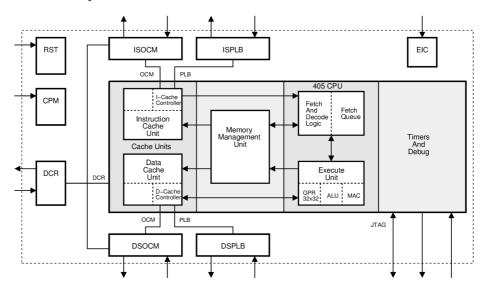

Figure 2.3: The hierarchical architecture of FPGA Virtex II Pro which contains two PowerPC processors, embedded multipliers and memories.

#### Field Programmable Gate Arrays

Figure 2.3 shows a typical architecture of a modern Xilinx FPGA [192]. FPGA consists of a two-dimensional array of reconfigurable resources that include configurable logic blocks (CLB), programmable interconnect blocks (PIB) and reconfigurable I/O blocks (IOB). The configuration bitstream configuring all these elements is stored in the configuration SRAM memory. A CLB consists of several smaller elements referred to as slices. Each slice contains two function generators implemented using k-bit LUTs, flip-flops and some additional logic. The number of bits k is usually between 3 and 6 depending on the FPGA family. Each

function generator can be programmed into one of the three modes. In the first mode, it can implement a combinational function. In the second mode, it can implement a fast k-bit shift register. And finally, the last mode enables to configure the LUT as a fast synchronous RAM with the total capacity of  $2^k$  bits.

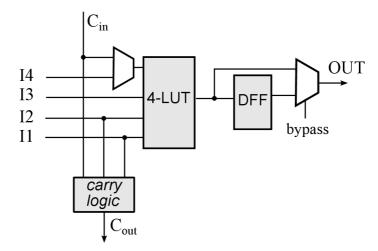

A typical structure of an FPGA logic block consisting of 4-input LUTs is depicted in Figure 2.4. While the LUTs provide some kind of generic logic, the flip-flops can be used for pipelining, registers, stateholding functions for Finite State Machines, or any other situations where clocking is required. Note that the flip-flops typically include programmable set/reset lines and clock signals. These signals may come from global signals routed on special resources, or could be routed via the standard interconnect structures from another input or logic block. The fast carry logic is a special resource provided in the cell to speed up carry-based computations, such as addition, parity, wide bit-wise operations, and other functions. These resources bypass the general routing structure in order to directly connect neighboring CLBs in the same column. Since there are very few routing choices in the carry chain, and thus less delay on the computation, the inclusion of these resources can significantly speed up the carry-based computations.

Figure 2.4: A typical structure of an FPGA logic block.

The FPGAs differ in the amount and type of resources available on the chip. The most advanced FPGAs based on 6-input lookup tables contain more than 100 thousands CLBs and integrate, in addition to CLBs, various embedded hard cores such as SRAM memories, fast multipliers, gigabit interfaces, PCI interfaces or even processors (PowerPC or ARM). Because the existence of these cores has been identified as important to designers in the past, it is reasonable to integrate them as hard cores on the chip instead of implementing them using CLBs and other resources. Current FPGAs can compete with application specific integrated circuits (ASICs) in many domains, for example, in applications of advanced signal processing or embedded systems.

Most FPGAs support a dynamic partial reconfiguration which means that some parts of the FPGA can be reconfigured while remaining parts of the FPGA are performing some computation. As it will be mentioned later, the possibility of the partial reconfiguration is crucial for evolvable hardware. FPGAs can be configured either externally or internally. In

the case of external reconfiguration, the configuration bit stream is copied to the configuration memory from an external memory, typically FLASH. The internal reconfiguration is available in Xilinx Virtex FPGAs via the Internal Configuration Access Port (ICAP) which allows for reading and modifying the FPGA configurations by circuits created directly in the same FPGA.

The goal of digital circuit design is to provide such implementation of a target circuit which satisfies the user specification and which is available in a reasonable time. As the conventional circuit design process with FPGAs is very similar to programming, the resultant system can be obtained relatively quickly. Designer has to describe the circuit structure or behavior using a hardware description language (such as VHDL, Verilog, Catapult C, etc.). Then, the source code is automatically transformed into the configuration bit stream for a particular FPGA. The transformation, which includes the synthesis, placement and routing is performed by CAD tools. This process can be constrained using various requirements, e.g. the maximum delay of the circuit can be specified. Also, it is possible to simulate intermediate results of the transformation, modify the original source code when needed and optimize the design.

In most cases, the format of the configuration bit stream is not fully documented for the designer. The reason is that the manufacturers protect their know-how and prevent the designers from potentially dangerous attempts to configure the FPGA without a CAD tool. In case of Xilinx chips, the only exception was the XC6200 family which is nowadays obsolete. The XC6200 family was very popular as it allowed to carry out intrinsic EHW experiments at the lowest possible level of abstraction. Comparing to the modern FPGAs, the basic building block of XC6200 was very simple as it contained several 2-input multiplexers instead of lookup tables. Thus, each programmable logic element could be programmed to implement a common 2-input Boolean functions such as AND, OR, XOR, etc. or 2-input multiplexer.

#### 2.2.3 Analog Reconfigurable Devices

Reconfigurable analog circuits allow, in fact, a software control of analog circuits. In comparison with FPGAs, reconfigurable analog circuits contain fewer configurable blocks and operate at lower frequencies. The reconfiguration is usually based either on configurable transistor switches, analog multiplexers, switching capacitors or operational transconductance amplifiers. Reconfigurable analog chips have been introduced much later than FP-GAs. Examples of analog reconfigurable circuits are given in the following sections.

#### Field Programmable Transistor Arrays

Field Programmable Transistor Array (FPTA-2) developed at NASA JPL employs transistor switches to implement the reconfiguration [170]. The FPTA-2 can implement analog, digital and mixed signal circuits. The architecture of the FPTA consists of an 8x8 array of re-configurable cells. Each cell contains a set of transistors and programmable resources, including programmable resistors and static capacitors. The reconfigurable circuitry consists of 14 transistors connected through 44 switches in each cell. In contrast with FPGAs, only several thousands of bits are used to program the whole chip only. The pattern of

interconnection among cells is similar to the one used in commercial FPGAs. Every cell can be interconnected with its northern, southern, eastern and western neighbors.

Another FPTA was developed at the University of Heidelberg [110]. This chip enables developing circuits directly at the transistor level. Designer can select the transistor type (PMOS or NMOS), its parameters such as channel length and size, and interconnection.

#### Field Programmable Analog Arrays

The reconfiguration of Field Programmable Analog Arrays (FPAA) is typically based on either switched capacitors or operational transconductance amplifiers.

Switched capacitors perform the function of configurable resistors. FPAAs use the following principle. A capacitor C is connected between two switches controlled by two signals. The switches are implemented using unipolar transistors and the control signals are non-overlapping clocks. The charge Q over one clock period transferred to the capacitor C is given by equation  $Q = C(V_1 - V_2)$  representing a discrete version of a well-known differential equation. The average current associated to this charge is  $I_a = C(V_1 - V_2)/T$ , where T denotes the clock period. Applying both equations, the value of an equivalent resistor can be calculated as  $R = (V_1 - V_2)/I_a = T/C$ . Thus, the value of a corresponding resistor can be controlled by the switching frequency f = 1/T. In comparison to conventional resistors, switching capacitors are advantageous in terms of linearity, dynamic range, precision and size on the chip. As f can be controlled from software, analog circuits (such as filters and oscillators) can be easily tuned. A disadvantage might be that circuits containing switched capacitors operate in discrete domain, i.e. there is a limit in the possible operation frequency which is determined by f.

The commercially available Anadigm AN221E04 FPAA [5], developed using switching capacitors, is an array of four configurable analog blocks (CAB), each of which containing two operational amplifiers, a comparator, and an 8-bit analog-to-digital converter. The device also contains one programmable lookup table that can be used to store information for the generation of arbitrary waveforms. The table is shared amongst the CABs. The configuration bit stream is stored in SRAM and the maximum switching frequency is 16 MHz.

Another approach to software control of analog circuits is based on operational transconductance amplifiers. A typical operational transconductance amplifier (OTA) produces a current output  $I_o$  that is linearly depending on an input voltage present at both inverting input  $(V_-)$  and non-inverting input  $(V_+)$ . The output current can be expressed as  $I_o = -g_m(V_+ - V_-)$ , where  $g_m$  is the transconductance of the circuit. The transconductance can be predefined using an external biasing current input. Biasing currents for OTAs are generated using D/A converters. Ideally, the circuit has infinite values for both the input and output impedances. OTAs are the main building blocks of continuous time filters in which the transconductance (and thus the frequency characteristics) can be controlled externally.

An example of FPAA which utilizes configurable OTAs is the FPAA developed at the University of Freiburg [76].

#### 2.3 Evolvable Hardware

A massive application of evolutionary principles to hardware design and self-configuration has led to a new concept called Evolvable Hardware (EHW). The growth of this interest has been caused by emerging a new class of programmable devices, in particular FPGAs. The main idea is to accomplish the whole process of circuit design by evolutionary algorithms. Evolvable hardware refers to a hardware that a) has been created using EA or b) embeds a variant of EA in order to either adapt the system to changing environments, or repair the system autonomously during its lifetime. While the first scenario is usually called evolutionary design, only the second approach can be, according to the [201], referred to as evolvable hardware. The evolutionary design uses evolutionary algorithms to evolve a system that meets a predefined specification. EA is employed only in the design phase. In contrast with this approach, the adaptive systems reconfigure a part or whole existing design to repair the faults or adapt to a changed operational environment. Thus the evolutionary algorithm is an integral part of the adaptive system. Although the terminology has been successively evolved, some literature, e.g. [65], does not distinguish between evolutionary hardware design and evolvable hardware.

The field of evolvable hardware originates from the intersection of three sciences: electronic engineering, biology and computer science. EHW belongs to the area of bioinspired hardware which combines the ideas from biology and electronic engineering. Although evolvable hardware as a research area has been established two decades ago, its roots can be traced to the sixties, when Gordon Pask constructed several electrochemical devices having the ability to adaptively construct their own sensors [141]. In addition to that, evolutionary strategies were used to perform parameter optimizations for a variety of electronic designs. The first experiment which explicitly speaks about evolvable hardware was conducted by Higuchi and his team in 1993 [79]. They utilized a genetic algorithm to find a configuration of a simple programmable logic chip (GAL). The aim of this work was to rediscover an implementation of a common 6-input multiplexer only on the basis of a behavioral specification given in the form of truth table. Because the number of reconfigurations of a GAL chip was limited, a GAL simulator calculated the fitness value of each member of population. At the end of evolution, the best solution was verified using a real GAL chip. This experiment demonstrated that the evolutionary approach is able to synthesize an electronic circuit without being explicitly told how to do it. Since that, the evolvable hardware has been successfully applied in many different areas. The following results are usually mentioned as the most successful applications of EHW: evolutionary designed highspeed robust classifiers [77], high-performance high-quality adaptive hardware compression systems based on the predictive coding [153, 154], adaptive fault-tolerant system with autonomous recovery [58], evolutionary designed antennas optimized for space missions [83] or innovative image filters [158].

#### 2.3.1 Basic Principle of EHW

EHW typically utilizes a reconfigurable hardware, particularly programmable logic devices such as FPGAs. The programmable logic devices allow the candidate solutions to be

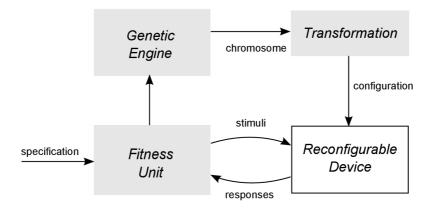

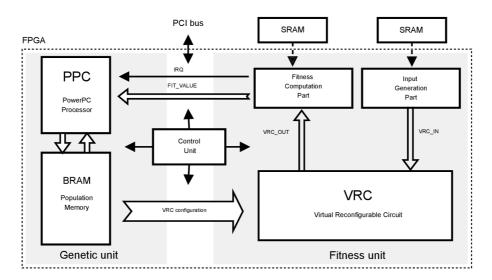

tested in situ which is well suited to embedded applications such as adaptive image filters or adaptive controllers. Figure 2.5 shows the basic principle of the evolvable hardware approach.

Figure 2.5: The basic principle of the evolvable hardware approach.

The objective of evolutionary algorithm is to design a circuit that meets the specification given by designer. In order to evaluate a candidate circuit, a new configuration of a reconfigurable device is created on the basis of the information stored in the corresponding chromosome. This step usually involves some kind of transformation as the chromosome encoding and configuration string can be generally different. The configuration is uploaded into the reconfigurable device and evaluated for a chosen set of input stimuli. The fitness function, which reflects the problem specification, can include behavioral as well as non-behavioral requirements. For example, the correct functionality is a typical behavioral requirement. As a non-behavioral requirement, we can mention the requirement for minimum power consumption or minimum area occupied on the chip. Once the evaluation of the population of candidate circuits is complete, a new population can be produced. That is typically performed by applying genetic operators (such as mutation and crossover) on existing circuit configurations. High-scored candidate circuits have got a higher probability that their genetic material (configuration bitstreams) will be selected for next generations. The process of evolution is terminated when a perfect or satisfactory solution is obtained or when a certain number of generations is evaluated.

#### 2.3.2 Evaluation of Candidate Circuits

Several schemes have been developed for classifying the evolvable hardware, e.g. [65, 177, 200, 81]. In this section, we will focus on one key feature that is usually considered by the mentioned classifications – hardware evaluation process.

Two scenarios are usually applied for evaluation of candidate circuits. Early evolvable hardware experiments used circuit simulators in order to calculate a fitness value of each member of the population. This approach has been known as *extrinsic evolution*. If all candidate solutions are evaluated in reconfigurable hardware, then the approach is called *intrinsic* evolvable hardware. The off-the-shelf FPGAs represent the most popular intrinsic reconfigurable chips due their availability and outstanding performance.

The importance of intrinsic evolution has been recognized by Thompson who has carried out the first intrinsic experiment using FPGA at the lowest level of abstraction possible [175]. The task was to evolve a circuit that discriminates between 1 kHz and 10 kHz signals. Evolution was able to find a very small circuit, i.e. to perform a task that would require human designers to project larger and clocked circuits, or use passive components, such as capacitors and inductors. In fact, evolution used a digital programmable device in the analog mode to perform this task. However, in spite of the high effort of Thompson involving the usage of analog simulators, the nature of some of the mechanisms used by the evolutionary designed circuit has not been completely understood. This is probably caused by the presence of feedbacks that can not be easily simulated, since they are dependent on the propagation delay of each cell. Thompson's impressive results stimulated other scientists to investigate the field of EHW.

#### 2.3.3 Evolvable Hardware as Design Tool

Using evolution to design electronics brings a number of benefits. Some of the most important areas where evolutionary electronics can successfully be applied include: automatic design of low cost hardware, automatic design of hardware systems for poorly specified problems, innovation in poorly understood design spaces, design of adaptive systems, or design of fault tolerant systems. The ability to generate solutions to poorly specified problems can be considered as a form of creativity which is one of the features of evolutionary processes. In case of the adaptive and fault tolerant system, the evolvable hardware is usually used due to its potential of autonomous adaption to changes in its environment (e.g. noise level in case of adaptive image filters, or presence of faults in case of fault-tolerant adaptive systems). The advantageous feature of the evolutionary approach is that it can not be necessary constrained to the well-known topologies that usually prevent from achieving novel solutions.

On the contrary, the evolutionary design approach has some drawbacks. Evolutionary methods are sometimes criticized that they do not produce robust and trustworthy designs. The evolved circuits are usually different from the well-known and proven structures which complicates their analysis and verification. Another discussed problem is enormous computational power which is usually needed for obtaining a satisfactory result. In some real-time applications (e.g. adaptive and fault tolerant systems), slow convergence or even stuck in a local extreme may represent an issue.

# Chapter 3

# Evolutionary Design of Analog and Digital Circuits

After reading the previous chapter, the evolutionary circuit design might seem to be substantially ineffective in comparison with conventional approaches. In many cases it is even true; however, there are applications where the evolutionary design brings a number of benefits unattainable by means of conventional design.

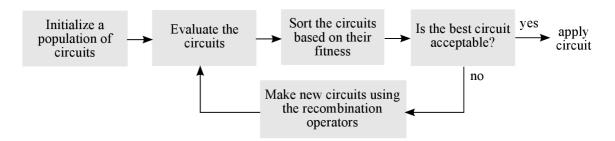

Figure 3.1: The basic principle of the evolutionary design of analog and digital circuits.

The basic principle of the evolutionary design of analog and digital circuits is depicted in Figure 3.1. The evolutionary design approach works as follows. Firstly, a population of initial solutions (circuits) is created. This population is usually generated randomly. Then, the behavior of each circuit is evaluated. In this step, a fitness value determining degree of correspondence with the initial specification is assigned to each circuit. If the fittest solution is acceptable, the algorithm is terminated. Otherwise, the best circuits are combined to generate new circuits and the algorithm continues with evaluation of newly generated circuits. After a number of iterations, the fittest circuit should behave according to the given specification.

This chapter surveys the most important approaches proposed mainly to extrinsic evolutionary design of analog and digital circuits.

## 3.1 Evolutionary Design of Analog Circuits

The first technique of analog circuit design automation has been reported in the seventies [174]. Since that, several other methods have been published, e.g. [75, 139]. Nevertheless, these methods utilized the approaches known from the area of artificial intelligence (e.g. expert systems, some kind of heuristics, or simulated annealing) rather than the evolutionary techniques. In contrast with the evolutionary design, these systems were very limited as they usually restricted the search space to well-known circuit topologies. A typical task was the optimization of a set of parameters. In the first applications dealing with the synthesis of passive filters, evolutionary approaches were used to perform the selection of topologies, or the simple determination of components' values for fixed topologies [67, 84].

The first truly analog circuit evolution was performed by Genetic Programming. The research group led by John Koza published pioneering methods solving this task, where all the steps necessary to design an analog circuit were handled by GP [103]. The objective was to find not only the values of utilized passive components but also the topology of the circuit. The first results published by Koza's team motivated researchers to deeply investigate this area. Tens of competitive analog circuits designed by means of the evolutionary algorithms have been reported up to now [99].

#### 3.1.1 Synthesis of Analog Circuits Using GP

Passive filters are electronic circuits that consist of an arrangement of resistors, capacitors, and inductors. In order to implement an analog filter with required characteristics, one of the known polynomial filter structures might be used. The filters differ in the construction, complexity of corresponding circuit implementation and the parameters of the frequency response. For example, the Butterworth response is the one that is closer to the ideal frequency response. However, the Butterworth filters require more components than the other ones. As there is a wide range of different aspects that has to be considered, the conventional design of analog filters represents a nontrivial task. The main filter characteristics that have to be reflected include: amplitude of the frequency response, phase of the frequency response, group delay, impulse response, and response to the step function.

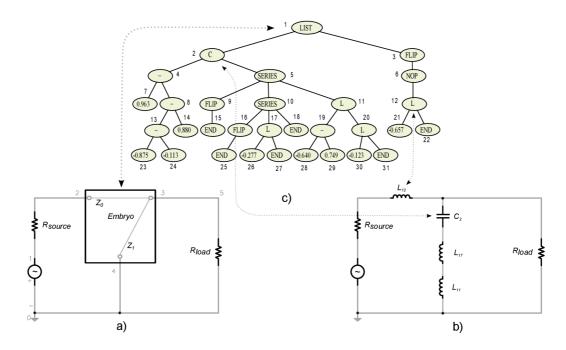

In order to evolve analog circuits, Koza came up with a developmental approach to perform a nontrivial mapping between circuit topologies and tree structures [103]. He used GP to find a tree that encodes a program to build a circuit from an initial circuit called the embryonic circuit. The initial circuit structure contains fixed and modifiable part. The fixed part includes the source resistance, output load, source signal and ground. It other words, it covers the essential features of the target circuit that has to be preserved. The modifiable part usually consists of pieces of wires that can be modified by the instructions encoded in the tree. Figure 3.2 depicts an example of a typical embryonic circuit used in Koza's applications.

The nodes of GP trees can be divided into functional and terminal nodes. The functional nodes may either create a component (component-creating functions) or modify a connection (connection modifying functions). Component-creating functions point to a modifiable part of the circuit, and create a particular component in this part of the circuit. In the

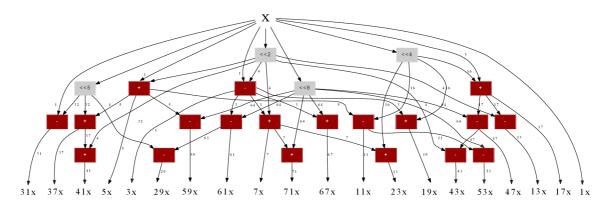

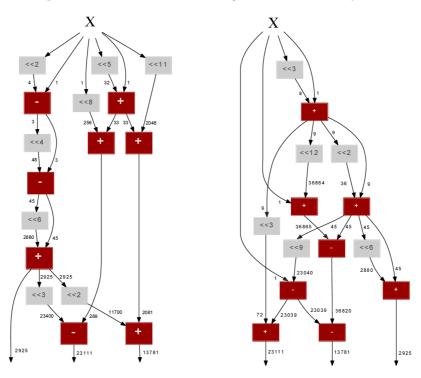

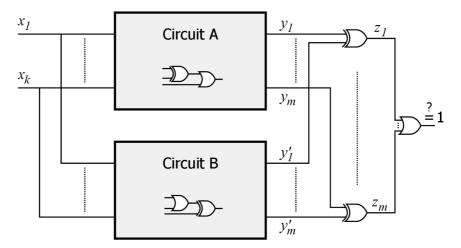

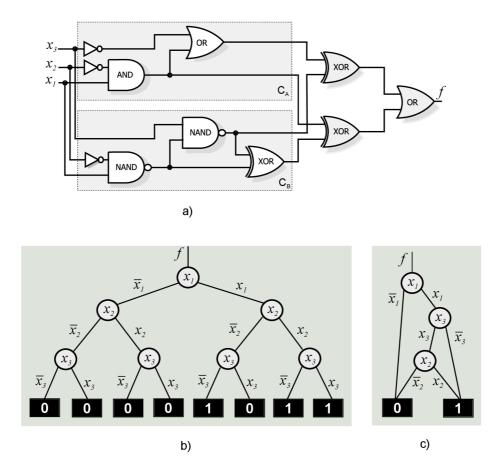

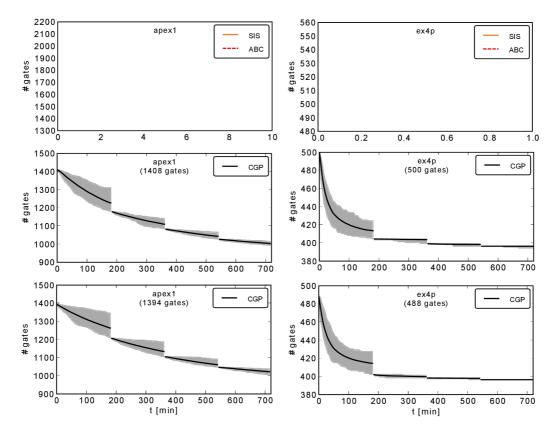

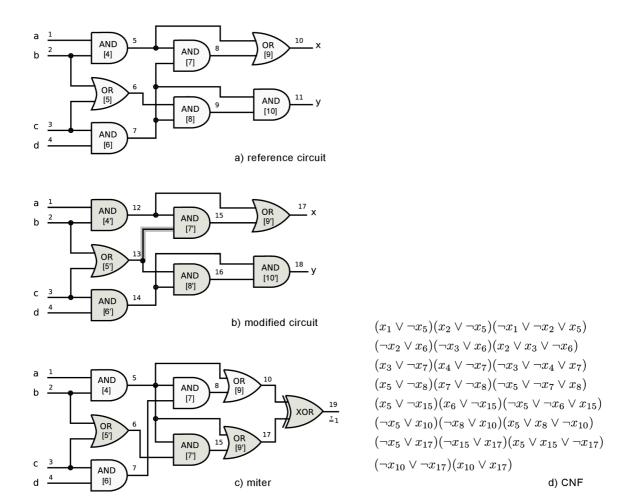

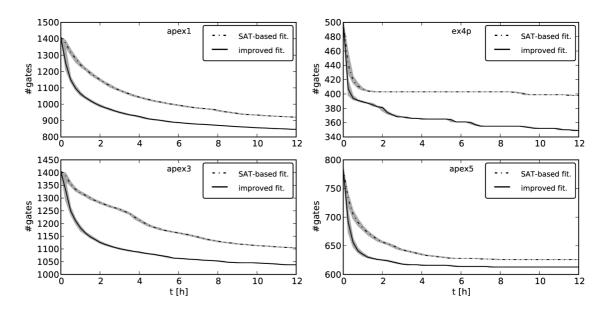

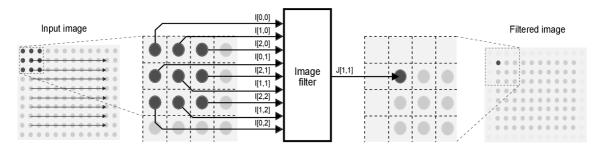

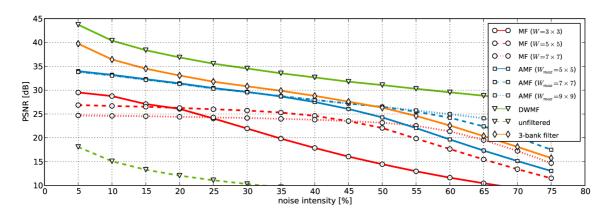

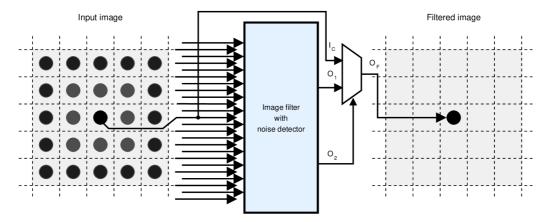

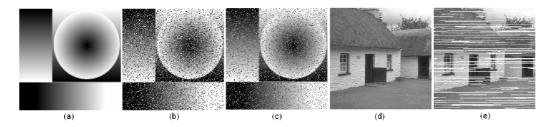

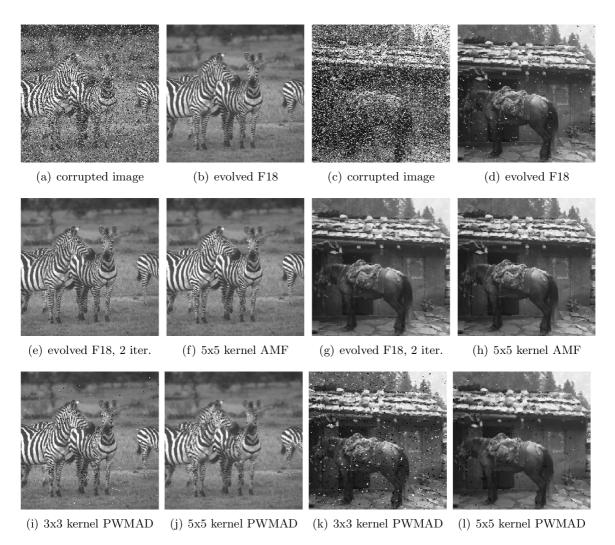

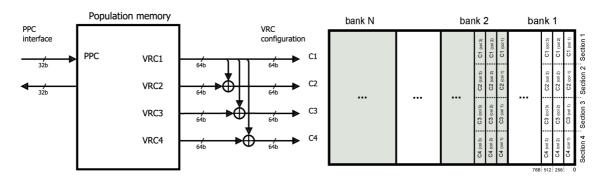

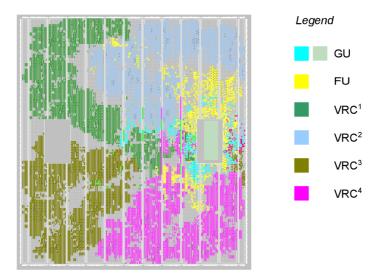

Figure 3.2: a) The initial circuit consisting of two modifiable wires denoted as Z0 and Z1. These wires provide some kind of place holder for inserting additional components. b) The analog circuit that has been created by the application of a candidate program. c) Candidate program encoded using a GP tree [104].